#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), LINbus, SPI, UART/USART       |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                   |

| Data Converters            | A/D 25x12b                                                     |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                             |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f545-iq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F54x

| 22.1. Signal Descriptions             | 215 |

|---------------------------------------|-----|

| 22.2. SPI0 Master Mode Operation      |     |

| 22.3. SPI0 Slave Mode Operation       |     |

| 22.4. SPI0 Interrupt Sources          |     |

| 22.5. Serial Clock Phase and Polarity |     |

| 22.6. SPI Special Function Registers  |     |

| 23. Timers                            |     |

| 23.1. Timer 0 and Timer 1             |     |

| 23.2. Timer 2                         | 237 |

| 23.3. Timer 3                         | 243 |

| 24. Programmable Counter Array        | 249 |

| 24.1. PCA Counter/Timer               |     |

| 24.2. PCA0 Interrupt Sources          |     |

| 24.3. Capture/Compare Modules         |     |

| 24.4. Watchdog Timer Mode             |     |

| 24.5. Register Descriptions for PCA0  |     |

| 25. C2 Interface                      |     |

| 25.1. C2 Interface Registers          |     |

| 25.2. C2 Pin Sharing                  |     |

|                                       |     |

# C8051F54x

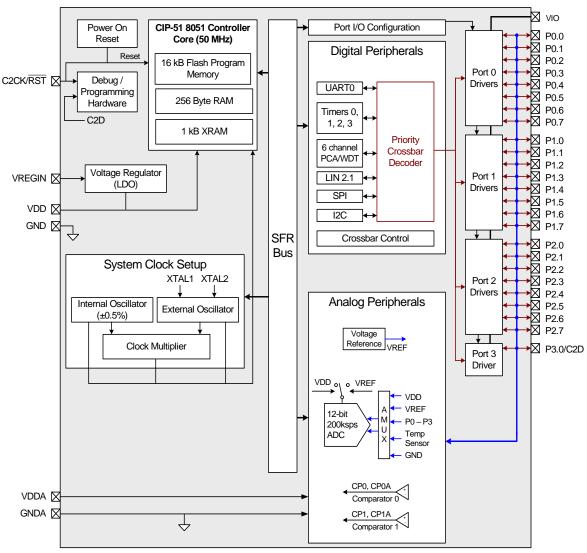

Figure 1.1. C8051F540/1/4/5 Block Diagram

# C8051F54x

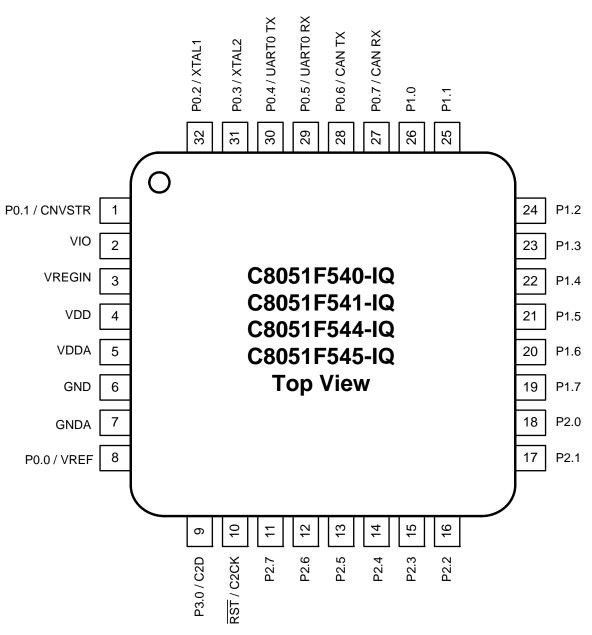

Figure 3.1. QFP-32 Pinout Diagram (Top View)

#### 5.3.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 5.1, Gain Register Definition 5.2, and Gain Register Definition 5.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

| // in 'C':                                                             |                                                                                                                                                                                    |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC0CF  = 0x01;                                                        | // GAINEN = 1                                                                                                                                                                      |

| ADC0H = 0x04;                                                          | // Load the ADC0GNH address                                                                                                                                                        |

| ADC0L = 0x6C;                                                          | // Load the upper byte of 0x6CA to ADC0GNH                                                                                                                                         |

| ADC0H = 0x07;                                                          | // Load the ADC0GNL address                                                                                                                                                        |

| ADC0L = 0xA0;                                                          | // Load the lower nibble of 0x6CA to ADC0GNL                                                                                                                                       |

| ADC0H = 0x08;                                                          | // Load the ADC0GNA address                                                                                                                                                        |

| ADC0L = 0x01;                                                          | // Set the GAINADD bit                                                                                                                                                             |

| ADC0CF &= ~0x01;                                                       | // GAINEN = 0                                                                                                                                                                      |

|                                                                        |                                                                                                                                                                                    |

| ; in assembly                                                          |                                                                                                                                                                                    |

| ORL ADC0CF,#01H                                                        | ; GAINEN = 1                                                                                                                                                                       |

|                                                                        | , •                                                                                                                                                                                |

| MOV ADC0H,#04H                                                         | ; Load the ADC0GNH address                                                                                                                                                         |

| MOV ADC0H,#04H<br>MOV ADC0L,#06CH                                      | ,                                                                                                                                                                                  |

|                                                                        | ; Load the ADC0GNH address                                                                                                                                                         |

| MOV ADC0L,#06CH                                                        | ; Load the ADC0GNH address<br>; Load the upper byte of 0x6CA to ADC0GNH                                                                                                            |

| MOV ADC0L,#06CH<br>MOV ADC0H,#07H                                      | ; Load the ADC0GNH address<br>; Load the upper byte of 0x6CA to ADC0GNH<br>; Load the ADC0GNL address                                                                              |

| MOV ADC0L,#06CH<br>MOV ADC0H,#07H<br>MOV ADC0L,#0A0H                   | ; Load the ADC0GNH address<br>; Load the upper byte of 0x6CA to ADC0GNH<br>; Load the ADC0GNL address<br>; Load the lower nibble of 0x6CA to ADC0GNL                               |

| MOV ADC0L,#06CH<br>MOV ADC0H,#07H<br>MOV ADC0L,#0A0H<br>MOV ADC0H,#08H | ; Load the ADC0GNH address<br>; Load the upper byte of 0x6CA to ADC0GNH<br>; Load the ADC0GNL address<br>; Load the lower nibble of 0x6CA to ADC0GNL<br>; Load the ADC0GNA address |

# SFR Definition 5.7. ADC0CN: ADC0 Control

| Bit   | 7             | 6                                                       | 5                                                                                                                                                                                                                                                                     | 4                 | 3            | 2     |          | 1          | 0                         |  |

|-------|---------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|-------|----------|------------|---------------------------|--|

| Nam   | e AD0EN       | BURSTEN                                                 | AD0INT                                                                                                                                                                                                                                                                | AD0BUSY           | ADOWINT      | AD0LJ | ST       | AD0C       | M[1:0]                    |  |

| Туре  | e R/W         | R/W                                                     | R/W                                                                                                                                                                                                                                                                   | R/W               | R/W          | R/W   |          | R/W        |                           |  |

| Rese  | et 0          | 0                                                       | 0                                                                                                                                                                                                                                                                     | 0                 | 0            | 0     |          | 0 0        |                           |  |

| SFR / | Address = 0xE | 8; SFR Page                                             | = 0x00; Bit                                                                                                                                                                                                                                                           | I<br>-Addressable | e            |       |          |            |                           |  |

| Bit   | Name          | Function                                                |                                                                                                                                                                                                                                                                       |                   |              |       |          |            |                           |  |

| 7     | AD0EN         | ADC0 Enab                                               | le Bit.                                                                                                                                                                                                                                                               |                   |              |       |          |            |                           |  |

|       |               | 0: ADC0 Dis<br>1: ADC0 Ena                              |                                                                                                                                                                                                                                                                       | •                 |              |       | /ersions | 6.         |                           |  |

| 6     | BURSTEN       | ADC0 Burst                                              | Mode Ena                                                                                                                                                                                                                                                              | ble Bit.          |              |       |          |            |                           |  |

|       |               |                                                         | 0: Burst Mode Disabled.<br>1: Burst Mode Enabled.                                                                                                                                                                                                                     |                   |              |       |          |            |                           |  |

| 5     | AD0INT        | ADC0 Conv                                               | ersion Con                                                                                                                                                                                                                                                            | nplete Interr     | upt Flag.    |       |          |            |                           |  |

|       |               |                                                         | <ul><li>0: ADC0 has not completed a data conversion since AD0INT was last cleared.</li><li>1: ADC0 has completed a data conversion.</li></ul>                                                                                                                         |                   |              |       |          |            |                           |  |

| 4     | AD0BUSY       | ADC0 Busy                                               | Bit.                                                                                                                                                                                                                                                                  | Read:             |              |       | Write:   |            |                           |  |

|       |               |                                                         |                                                                                                                                                                                                                                                                       | in prog           | CO conversio |       |          | ates AD    | C0 Conver-<br>[1:0] = 00b |  |

| 3     | AD0WINT       | ADC0 Wind                                               | ow Compa                                                                                                                                                                                                                                                              | re Interrupt      | Flag.        |       |          |            |                           |  |

|       |               | This bit must<br>0: ADC0 Wir<br>cleared.<br>1: ADC0 Wir | ndow Comp                                                                                                                                                                                                                                                             | arison Data       |              |       | ed sinc  | e this fla | g was last                |  |

| 2     | AD0LJST       | ADC0 Left J                                             | ustify Sele                                                                                                                                                                                                                                                           | ct Bit.           |              |       |          |            |                           |  |

|       |               | 1: Data in Al                                           | 0: Data in ADC0H:ADC0L registers is right-justified<br>1: Data in ADC0H:ADC0L registers is left-justified. This option should not be used<br>with a repeat count greater than 1 (when AD0RPT[1:0] is 01b, 10b, or 11b).                                               |                   |              |       |          |            |                           |  |

| 1:0   | AD0CM[1:0]    |                                                         |                                                                                                                                                                                                                                                                       |                   |              |       |          |            |                           |  |

|       |               | 01: ADC0 sta<br>10: ADC0 sta                            | 00: ADC0 start-of-conversion source is write of 1 to AD0BUSY.<br>01: ADC0 start-of-conversion source is overflow of Timer 1.<br>10: ADC0 start-of-conversion source is rising edge of external CNVSTR.<br>11: ADC0 start-of-conversion source is overflow of Timer 2. |                   |              |       |          |            |                           |  |

# SFR Definition 5.9. ADC0GTH: ADC0 Greater-Than Data High Byte

| Bit               | 7             | 6                                                       | 5        | 4 | 3 | 2 | 1 | 0 |  |

|-------------------|---------------|---------------------------------------------------------|----------|---|---|---|---|---|--|

| Name ADC0GTH[7:0] |               |                                                         |          |   |   |   |   |   |  |

| Туре              | ype R/W       |                                                         |          |   |   |   |   |   |  |

| Rese              | et 1          | 1                                                       | 1        | 1 | 1 | 1 | 1 | 1 |  |

| SFR A             | Address = 0xC | 4; SFR Page                                             | e = 0x00 |   |   |   | • |   |  |

| Bit               | Name          | Name Function                                           |          |   |   |   |   |   |  |

| 7:0               | ADC0GTH[7     | COGTH[7:0] ADC0 Greater-Than Data Word High-Order Bits. |          |   |   |   |   |   |  |

# SFR Definition 5.10. ADC0GTL: ADC0 Greater-Than Data Low Byte

| Bit               | 7              | 7 6 5 4 3 2 1 0 |                                             |   |   |   |   |   |  |

|-------------------|----------------|-----------------|---------------------------------------------|---|---|---|---|---|--|

| Name ADC0GTL[7:0] |                |                 |                                             |   |   |   |   |   |  |

| Туре              | 9              | R/W             |                                             |   |   |   |   |   |  |

| Rese              | et 1           | 1               | 1                                           | 1 | 1 | 1 | 1 | 1 |  |

| SFR A             | Address = 0xC3 | 3; SFR Pag      | e = 0x00                                    |   |   |   |   |   |  |

| Bit               | Name           | me Function     |                                             |   |   |   |   |   |  |

| 7:0               | ADC0GTL[7:0    | )] ADC0 G       | ADC0 Greater-Than Data Word Low-Order Bits. |   |   |   |   |   |  |

# SFR Definition 5.11. ADC0LTH: ADC0 Less-Than Data High Byte

| D:4   | -                |               | F                                         |   | 2 | • |   | • |  |

|-------|------------------|---------------|-------------------------------------------|---|---|---|---|---|--|

| Bit   | 1                | 6             | 5                                         | 4 | 3 | 2 | 1 | 0 |  |

| Nam   | ame ADC0LTH[7:0] |               |                                           |   |   |   |   |   |  |

| Туре  | R/W              |               |                                           |   |   |   |   |   |  |

| Rese  | et 0             | 0             | 0                                         | 0 | 0 | 0 | 0 | 0 |  |

| SFR A | Address = 0xC6   | ; SFR Page    | e = 0x00                                  |   |   |   |   |   |  |

| Bit   | Name             | Name Function |                                           |   |   |   |   |   |  |

| 7:0   | ADC0LTH[7:0      | ] ADC0 Le     | ADC0 Less-Than Data Word High-Order Bits. |   |   |   |   |   |  |

### SFR Definition 5.12. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit   | 7                                   | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-------------------------------------|--------------|---|---|---|---|---|---|--|--|

| Name  | 9                                   | ADC0LTL[7:0] |   |   |   |   |   |   |  |  |

| Туре  |                                     | R/W          |   |   |   |   |   |   |  |  |

| Rese  | t 0                                 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A | SFR Address = 0xC5; SFR Page = 0x00 |              |   |   |   |   |   |   |  |  |

| Bit   | Name                                |              |   |   |   |   |   |   |  |  |

| 7:0 | ADC0LTL[7:0] | ADC0 Less-Than Data Word Low-Order Bits. |

|-----|--------------|------------------------------------------|

### 5.4.1. Window Detector In Single-Ended Mode

window for Figure 5.6 shows two example comparisons right-justified data with ADC0LTH:ADC0LTL = 0x0200 (512d) and ADC0GTH:ADC0GTL = 0x0100 (256d). The input voltage can range from 0 to V<sub>REF</sub> x (4095/4096) with respect to GND, and is represented by a 12-bit unsigned integer value. The repeat count is set to one. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0100 < ADC0H:ADC0L < 0x0200). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0100 or ADC0H:ADC0L > 0x0200). Figure 5.7 shows an example using left-justified data with the same comparison values.

### **Table 6.4. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                              | Conditions                                                                            | Min                   | Тур  | Max                   | Units |

|--------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| RST Output Low Voltage                                 | VIO = 5 V; IOL = 70 µA                                                                | —                     | —    | 40                    | mV    |

| RST Input High Voltage                                 |                                                                                       | 0.7 x V <sub>IO</sub> | —    | —                     |       |

| RST Input Low Voltage                                  |                                                                                       | _                     | _    | 0.3 x V <sub>IO</sub> |       |

| RST Input Pullup Current                               | $\overline{\text{RST}}$ = 0.0 V, VIO = 5 V                                            |                       | 49   | 115                   | μA    |

| V <sub>DD</sub> RST Threshold (V <sub>RST-LOW</sub> )  |                                                                                       | 1.65                  | 1.75 | 1.80                  | V     |

| V <sub>DD</sub> RST Threshold (V <sub>RST-HIGH</sub> ) |                                                                                       | 2.25                  | 2.30 | 2.45                  | V     |

| Missing Clock Detector Timeout                         | Time from last system clock rising edge to reset initiation                           |                       |      |                       | μs    |

|                                                        | V <sub>DD</sub> = 2.1 V                                                               | 200                   | 340  | 600                   |       |

|                                                        | V <sub>DD</sub> = 2.5 V                                                               | 200                   | 250  | 600                   |       |

| Reset Time Delay                                       | Delay between release of<br>any reset source and code<br>execution at location 0x0000 | _                     | 155  | 175                   | μs    |

| Minimum RST Low Time to<br>Generate a System Reset     |                                                                                       | 6                     | —    | —                     | μs    |

| V <sub>DD</sub> Monitor Turn-on Time                   |                                                                                       |                       | 60   | 100                   | μs    |

| V <sub>DD</sub> Monitor Supply Current                 |                                                                                       |                       | 1    | 2                     | μA    |

### **Table 6.5. Flash Electrical Characteristics**

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified.

| Parameter        | Conditions                                                           | Min                                | Тур                | Мах    | Units       |  |  |

|------------------|----------------------------------------------------------------------|------------------------------------|--------------------|--------|-------------|--|--|

| Flash Size       | Tlash Size C8051F540/1/2/3                                           |                                    | 16384 <sup>1</sup> |        |             |  |  |

|                  | C8051F544/5/6/7                                                      |                                    | 8192               |        |             |  |  |

| Endurance        |                                                                      | 20 k                               | 150 k              | _      | Erase/Write |  |  |

| Retention        | 125 °C                                                               | 10                                 |                    | —      | Years       |  |  |

| Erase Cycle Time | 25 MHz System Clock                                                  | 28                                 | 30                 | 45     | ms          |  |  |

| Write Cycle Time | 25 MHz System Clock                                                  | 79                                 | 84                 | 125    | μs          |  |  |

| V <sub>DD</sub>  | Write/Erase Operations                                               | V <sub>RST-HIGH</sub> <sup>2</sup> | _                  | _      | V           |  |  |

|                  | h devices, 1024 bytes at addresses the $V_{RST-HIGH}$ specification. | 0x3C00 to 0x3                      | FFF are res        | erved. |             |  |  |

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed.

## SFR Definition 8.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3    | 2       | 1    | 0       |

|-------|-------|--------|--------|--------|------|---------|------|---------|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0H | /P[1:0] | CP0H | /N[1:0] |

| Туре  | R/W   | R      | R/W    | R/W    | R/W  |         | R/   | W       |

| Reset | 0     | 0      | 0      | 0      | 0    | 0       | 0    | 0       |

SFR Address = 0x9A; SFR Page = 0x00

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0–.                                                    |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

# SFR Definition 8.6. CPT1MX: Comparator1 MUX Selection

| Bit   | 7            | 6           | 5           | 4            | 3            | 2            | 1      | 0 |  |

|-------|--------------|-------------|-------------|--------------|--------------|--------------|--------|---|--|

| Nam   | e            | CMX1        | N[3:0]      |              |              | CMX1         | P[3:0] |   |  |

| Туре  | <b>;</b>     | R/          | W           |              | R/W          |              |        |   |  |

| Rese  | et 0         | 1           | 1           | 1            | 0            | 1            | 1      | 1 |  |

| SFR A | ddress = 0x9 | F; SFR Page | = 0x00      |              |              |              |        |   |  |

| Bit   | Name         | Function    |             |              |              |              |        |   |  |

| 7:4   | CMX1N[3:0]   | Comparato   | r1 Negative | Input MUX    | Selection.   |              |        |   |  |

|       |              | 0000:       | P0.         | 1            |              |              |        |   |  |

|       |              | 0001:       | P0.         | 3            |              |              |        |   |  |

|       |              | 0010:       | P0.         | 5            |              |              |        |   |  |

|       |              | 0011:       | P0.         | 7            |              |              |        |   |  |

|       |              | 0100:       | P1.         | 1            |              |              |        |   |  |

|       |              | 0101:       | P1.         | 3            |              |              |        |   |  |

|       |              | 0110:       | P1.         | 5            |              |              |        |   |  |

|       |              | 0111:       | P1.         | 7            |              |              |        |   |  |

|       |              | 1000:       | P2.         | 1            |              |              |        |   |  |

|       |              | 1001:       | P2.         | 3 (only avai | able on 32-p | oin devices) |        |   |  |

|       |              | 1010:       | P2.         | 5 (only avai | able on 32-p | oin devices) |        |   |  |

|       |              | 1011:       | P2.         | 7 (only avai | able on 32-p | oin devices) |        |   |  |

|       |              | 1100–1111:  | Nor         | ne           |              |              |        |   |  |

| 3:0   | CMX1P[3:0]   | Comparato   | r1 Positive | Input MUX    | Selection.   |              |        |   |  |

|       |              | 0000:       | P0.         | 0            |              |              |        |   |  |

|       |              | 0001:       | P0.         | 2            |              |              |        |   |  |

|       |              | 0010:       | P0.         | 4            |              |              |        |   |  |

|       |              | 0011:       | P0.         | 6            |              |              |        |   |  |

|       |              | 0100:       | P1.         | 0            |              |              |        |   |  |

|       |              | 0101:       | P1.         | 2            |              |              |        |   |  |

|       |              | 0110:       | P1.         | 4            |              |              |        |   |  |

|       |              | 0111:       | P1.         | 6            |              |              |        |   |  |

|       |              | 1000:       | P2.         | 0            |              |              |        |   |  |

|       |              | 1001:       | P2.         | 2 (only avai | able on 32-p | oin devices) |        |   |  |

|       |              | 1010:       | P2.         | 4 (only avai | able on 32-p | oin devices) |        |   |  |

|       |              | 1011:       | P2.         | 6 (only avai | able on 32-p | oin devices) |        |   |  |

|       |              | 1100–1111:  | Nor         | ne           |              |              |        |   |  |

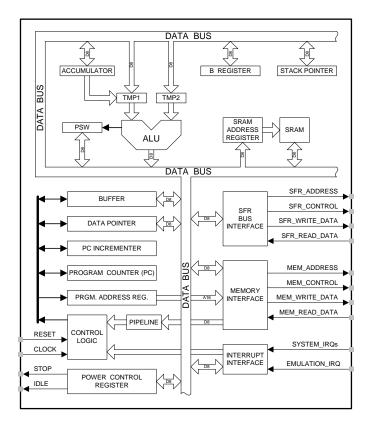

Figure 10.1. CIP-51 Block Diagram

With the CIP-51's maximum system clock at 50 MHz, it has a peak throughput of 50 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire Development Interface (C2).

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources. C2 details can be found in Section "25. C2 Interface" on page 269.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

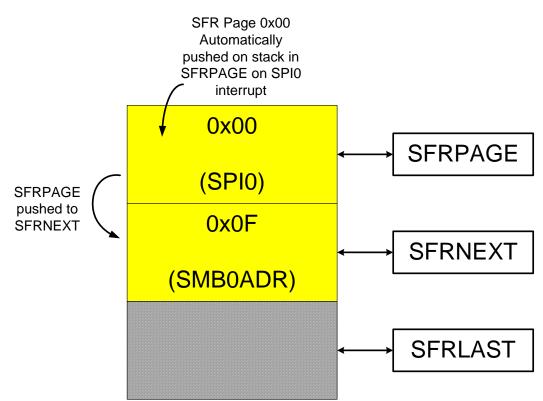

Figure 12.3. SFR Page Stack After SPI0 Interrupt Occurs

While in the SPI0 ISR, a PCA interrupt occurs. Recall the PCA interrupt is configured as a high priority interrupt, while the SPI0 interrupt is configured as a *low* priority interrupt. Thus, the CIP-51 will now vector to the high priority PCA ISR. Upon doing so, the CIP-51 will automatically place the SFR page needed to access the PCA's special function registers into the SFRPAGE register, SFR Page 0x00. The value that was in the SFRPAGE register before the PCA interrupt (SFR Page 0x00 for SPI00) is pushed down the stack into SFRNEXT. Likewise, the value that was in the SFRNEXT register before the PCA interrupt (in this case SFR Page 0x0F for SMB0ADR) is pushed down to the SFRLAST register, the "bottom" of the stack. Note that a value stored in SFRLAST (via a previous software write to the SFRLAST register) will be overwritten. See Figure 12.4.

# SFR Definition 13.1. IE: Interrupt Enable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Туре  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0xA8; Bit-Addressable; SFR Page = All Pages

| Bit | Name  | Function                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EA    | <ul> <li>Enable All Interrupts.</li> <li>Globally enables/disables all interrupts. It overrides individual interrupt mask settings.</li> <li>0: Disable all interrupt sources.</li> <li>1: Enable each interrupt according to its individual mask setting.</li> </ul> |

| 6   | ESPI0 | <ul> <li>Enable Serial Peripheral Interface (SPI0) Interrupt.</li> <li>This bit sets the masking of the SPI0 interrupts.</li> <li>0: Disable all SPI0 interrupts.</li> <li>1: Enable interrupt requests generated by SPI0.</li> </ul>                                 |

| 5   | ET2   | <ul> <li>Enable Timer 2 Interrupt.</li> <li>This bit sets the masking of the Timer 2 interrupt.</li> <li>0: Disable Timer 2 interrupt.</li> <li>1: Enable interrupt requests generated by the TF2L or TF2H flags.</li> </ul>                                          |

| 4   | ES0   | Enable UART0 Interrupt.<br>This bit sets the masking of the UART0 interrupt.<br>0: Disable UART0 interrupt.<br>1: Enable UART0 interrupt.                                                                                                                             |

| 3   | ET1   | <ul> <li>Enable Timer 1 Interrupt.</li> <li>This bit sets the masking of the Timer 1 interrupt.</li> <li>0: Disable all Timer 1 interrupt.</li> <li>1: Enable interrupt requests generated by the TF1 flag.</li> </ul>                                                |

| 2   | EX1   | <ul> <li>Enable External Interrupt 1.</li> <li>This bit sets the masking of External Interrupt 1.</li> <li>0: Disable external interrupt 1.</li> <li>1: Enable interrupt requests generated by the INT1 input.</li> </ul>                                             |

| 1   | ET0   | <ul> <li>Enable Timer 0 Interrupt.</li> <li>This bit sets the masking of the Timer 0 interrupt.</li> <li>0: Disable all Timer 0 interrupt.</li> <li>1: Enable interrupt requests generated by the TF0 flag.</li> </ul>                                                |

| 0   | EX0   | <ul> <li>Enable External Interrupt 0.</li> <li>This bit sets the masking of External Interrupt 0.</li> <li>0: Disable external interrupt 0.</li> <li>1: Enable interrupt requests generated by the INTO input.</li> </ul>                                             |

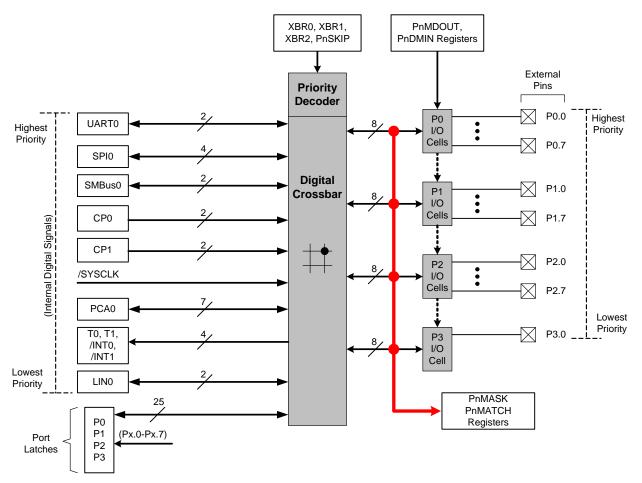

# 18. Port Input/Output

Digital and analog resources are available through 25 (C8051F540/1/4/5) or 18 (C8051F542/3/6/7) I/O pins. Port pins P0.0-P3.0 on the C8051F540/1/4/5 and port pins P0.0-P2.1 on the C8051F542/3/6/7 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources, or assigned to an analog function as shown in Figure 18.3. Port pin P3.0 on the C8051F540/1/4/5 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). Similarly, port pin P2.1 is shared with C2D on the C8051F542/3/6/7. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. The state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 18.3 and Figure 18.4). The registers XBR0, XBR1, XBR2 are defined in SFR Definition 18.1 and SFR Definition 18.2 and are used to select internal digital functions.

The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Table 6.3 on page 51.

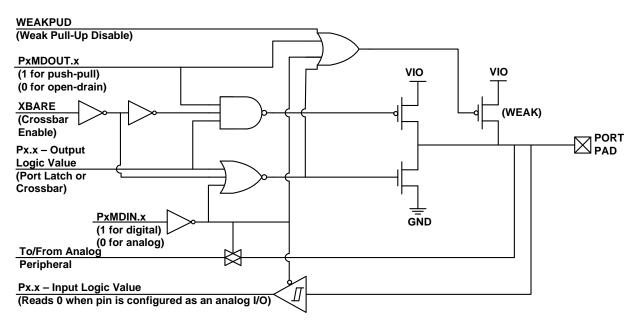

### 18.1. Port I/O Modes of Operation

Port pins P0.0–P3.0 use the Port I/O cell shown in Figure 18.2. Each Port I/O cell can be configured by software for analog I/O or digital I/O using the PnMDIN registers. On reset, all Port I/O cells default to a high impedance state with weak pull-ups enabled until the Crossbar is enabled (XBARE = 1).

### 18.1.1. Port Pins Configured for Analog I/O

Any pins to be used as Comparator or ADC inputs, external oscillator inputs, or VREF should be configured for analog I/O (PnMDIN.n = 0). When a pin is configured for analog I/O, its weak pullup, digital driver, and digital receiver are disabled. Port pins configured for analog I/O will always read back a value of 0.

Configuring pins as analog I/O saves power and isolates the Port pin from digital interference. Port pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended and may result in measurement errors.

### 18.1.2. Port Pins Configured For Digital I/O

Any pins to be used by digital peripherals (UART, SPI, SMBus, etc.), external digital event capture functions, or as GPIO should be configured as digital I/O (PnMDIN.n = 1). For digital I/O pins, one of two output modes (push-pull or open-drain) must be selected using the PnMDOUT registers.

Push-pull outputs (PnMDOUT.n = 1) drive the Port pad to the VIO or GND supply rails based on the output logic value of the Port pin. Open-drain outputs have the high side driver disabled; therefore, they only drive the Port pad to GND when the output logic value is 0 and become high impedance inputs (both high low drivers turned off) when the output logic value is 1.

When a digital I/O cell is placed in the high impedance state, a weak pull-up transistor pulls the Port pad to the VIO supply voltage to ensure the digital input is at a defined logic state. Weak pull-ups are disabled when the I/O cell is driven to GND to minimize power consumption and may be globally disabled by setting WEAKPUD to 1. The user should ensure that digital I/O are always internally or externally pulled or driven to a valid logic state to minimize power consumption. Port pins configured for digital I/O always read back the logic state of the Port pad, regardless of the output logic value of the Port pin.

# LIN Register Definition 19.4. LIN0DTn: LIN0 Data Byte n

| Bit  | 7                                  | 6           | 5               | 4           | 3           | 2            | 1             | 0          |  |

|------|------------------------------------|-------------|-----------------|-------------|-------------|--------------|---------------|------------|--|

| Nam  | e                                  | DATAn[7:0]  |                 |             |             |              |               |            |  |

| Туре | )                                  | R/W         |                 |             |             |              |               |            |  |

| Rese | set 0 0 0 0 0 0 0 0                |             |                 |             |             |              | 0             |            |  |

|      | ct Address: LIN<br>0T6 = 0x05, LIN |             | ,               | ,           | DT3 = 0x02  | , LIN0DT4 =  | 0x03, LIN0[   | DT5 = 0x04 |  |

| Bit  | Name                               |             | Function        |             |             |              |               |            |  |

| 7:0  | DATAn[7:0]                         | LIN Data E  | IN Data Byte n. |             |             |              |               |            |  |

|      |                                    | Serial Data | Byte that is    | received or | transmitted | across the L | IN interface. |            |  |

# LIN Register Definition 19.9. LIN0DIV: LIN0 Divider Register

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | DIVLSB[3:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Indirect Address = 0x0C

| Bit | Name | Function                                                                                                                                                                                                                 |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 |      | LIN Baud Rate Divider Least Significant Bits.<br>The 8 least significant bits for the baud rate divider. The 9th and most significant bit<br>is the DIV9 bit (LIN0MUL.0). The valid range for the divider is 200 to 511. |

## LIN Register Definition 19.10. LIN0MUL: LIN0 Multiplier Register

| Bit   | 7           | 6 | 5 | 4    | 3   | 2 | 1 | 0   |

|-------|-------------|---|---|------|-----|---|---|-----|

| Name  | PRESCL[1:0] |   |   | DIV9 |     |   |   |     |

| Туре  | R/W         |   |   |      | R/W |   |   | R/W |

| Reset | 1           | 1 | 1 | 1    | 1   | 1 | 1 | 1   |

Indirect Address = 0x0D

| Bit | Name        | Function                                                                                                                                       |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | PRESCL[1:0] | LIN Baud Rate Prescaler Bits.                                                                                                                  |

|     |             | These bits are the baud rate prescaler bits.                                                                                                   |

| 5:1 | LINMUL[4:0] | LIN Baud Rate Multiplier Bits.                                                                                                                 |

|     |             | These bits are the baud rate multiplier bits. These bits are not used in slave mode.                                                           |

| 0   | DIV9        | LIN Baud Rate Divider Most Significant Bit.                                                                                                    |

|     |             | The most significant bit of the baud rate divider. The 8 least significant bits are in LIN0DIV. The valid range for the divider is 200 to 511. |

# SFR Definition 20.1. SMB0CF: SMBus Clock/Configuration

| Bit   | 7     | 6   | 5    | 4       | 3      | 2      | 1          | 0 |

|-------|-------|-----|------|---------|--------|--------|------------|---|

| Name  | ENSMB | INH | BUSY | EXTHOLD | SMBTOE | SMBFTE | SMBCS[1:0] |   |

| Туре  | R/W   | R/W | R    | R/W     | R/W    | R/W    | R/W        |   |

| Reset | 0     | 0   | 0    | 0       | 0      | 0      | 0          | 0 |

### SFR Address = 0xC1; SFR Page = 0x00

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                           |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ENSMB      | SMBus Enable.                                                                                                                                                                                                                                                                                                                                      |

|     |            | This bit enables the SMBus interface when set to 1. When enabled, the interface constantly monitors the SDA and SCL pins.                                                                                                                                                                                                                          |

| 6   | INH        | SMBus Slave Inhibit.                                                                                                                                                                                                                                                                                                                               |

|     |            | When this bit is set to logic 1, the SMBus does not generate an interrupt when slave events occur. This effectively removes the SMBus slave from the bus. Master Mode interrupts are not affected.                                                                                                                                                 |

| 5   | BUSY       | SMBus Busy Indicator.                                                                                                                                                                                                                                                                                                                              |

|     |            | This bit is set to logic 1 by hardware when a transfer is in progress. It is cleared to logic 0 when a STOP or free-timeout is sensed.                                                                                                                                                                                                             |

| 4   | EXTHOLD    | SMBus Setup and Hold Time Extension Enable.                                                                                                                                                                                                                                                                                                        |

|     |            | This bit controls the SDA setup and hold times according to Table 20.2.                                                                                                                                                                                                                                                                            |

|     |            | <ul><li>0: SDA Extended Setup and Hold Times disabled.</li><li>1: SDA Extended Setup and Hold Times enabled.</li></ul>                                                                                                                                                                                                                             |

| 3   | SMBTOE     | SMBus SCL Timeout Detection Enable.                                                                                                                                                                                                                                                                                                                |

| 3   | SINIDIOE   | This bit enables SCL low timeout detection. If set to logic 1, the SMBus forces                                                                                                                                                                                                                                                                    |

|     |            | Timer 3 to reload while SCL is high and allows Timer 3 to count when SCL goes low.<br>If Timer 3 is configured to Split Mode, only the High Byte of the timer is held in reload<br>while SCL is high. Timer 3 should be programmed to generate interrupts at 25 ms,<br>and the Timer 3 interrupt service routine should reset SMBus communication. |

| 2   | SMBFTE     | SMBus Free Timeout Detection Enable.                                                                                                                                                                                                                                                                                                               |

|     |            | When this bit is set to logic 1, the bus will be considered free if SCL and SDA remain high for more than 10 SMBus clock source periods.                                                                                                                                                                                                           |

| 1:0 | SMBCS[1:0] | SMBus Clock Source Selection.                                                                                                                                                                                                                                                                                                                      |

|     |            | These two bits select the SMBus clock source, which is used to generate the SMBus                                                                                                                                                                                                                                                                  |

|     |            | bit rate. The selected device should be configured according to Equation 20.1.<br>00: Timer 0 Overflow                                                                                                                                                                                                                                             |

|     |            | 01: Timer 1 Overflow                                                                                                                                                                                                                                                                                                                               |

|     |            | 10:Timer 2 High Byte Overflow                                                                                                                                                                                                                                                                                                                      |

|     |            | 11: Timer 2 Low Byte Overflow                                                                                                                                                                                                                                                                                                                      |

#### 20.4.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic 0, as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

### SFR Definition 20.3. SMB0DAT: SMBus Data

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | SMB0DAT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xC2; SMB0DAT = 0x00

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SMB0DAT[7:0] | SMBus Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |              | The SMB0DAT register contains a byte of data to be transmitted on the SMBus serial interface or a byte that has just been received on the SMBus serial interface. The CPU can read from or write to this register whenever the SI serial interrupt flag (SMB0CN.0) is set to logic 1. The serial data in the register remains stable as long as the SI flag is set. When the SI flag is not set, the system may be in the process of shifting data in/out and the CPU should not attempt to access this register. |

### 20.5. SMBus Transfer Modes

The SMBus interface may be configured to operate as master and/or slave. At any particular time, it will be operating in one of the following four modes: Master Transmitter, Master Receiver, Slave Transmitter, or Slave Receiver. The SMBus interface enters Master Mode any time a START is generated, and remains in Master Mode until it loses an arbitration or generates a STOP. An SMBus interrupt is generated at the end of all SMBus byte frames. As a receiver, the interrupt for an ACK occurs **before** the ACK. As a transmitter, interrupts occur **after** the ACK.

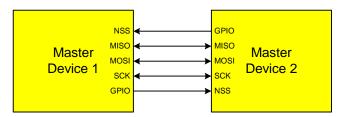

Figure 22.2. Multiple-Master Mode Connection Diagram

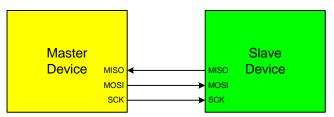

Figure 22.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

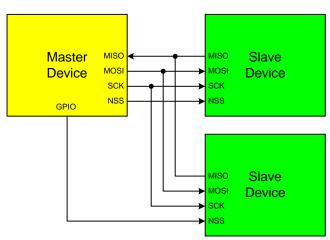

Figure 22.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram