# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671-04-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# FIGURE 4-2: PIC12C67X REGISTER FILE MAP

|                 | WAF                  |                     |                 |

|-----------------|----------------------|---------------------|-----------------|

| File<br>Address | 6                    |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                 | OPTION              | 81h             |

| 02h             | PCL                  | PCL                 | 82h             |

| 02h             | STATUS               | STATUS              | 83h             |

| 03h             | FSR                  | FSR                 | 84h             |

| 0411<br>05h     | GPIO                 | TRIS                | 85h             |

|                 | GFIO                 | INIS                | _               |

| 06h<br>07h      |                      |                     | 86h<br>87h      |

| 07h<br>08h      |                      |                     | 88h             |

|                 |                      |                     |                 |

| 09h             |                      |                     | 89h             |

| 0Ah             | PCLATH               | PCLATH              | 8Ah             |

| 0Bh             | INTCON               | INTCON              | 8Bh             |

| 0Ch             | PIR1                 | PIE1                | 8Ch             |

| 0Dh             |                      |                     | 8Dh             |

| 0Eh             |                      | PCON                | 8Eh             |

| 0Fh             |                      | OSCCAL              | 8Fh             |

| 10h             |                      |                     | 90h             |

| 11h             |                      |                     | 91h             |

| 12h             |                      |                     | 92h             |

| 13h             |                      |                     | 93h             |

| 14h             |                      |                     | 94h             |

| 15h             |                      |                     | 95h             |

| 16h             |                      |                     | 96h             |

| 17h             |                      |                     | 97h             |

| 18h             |                      |                     | 98h             |

| 19h             |                      |                     | 99h             |

| 1Ah             |                      |                     | 9Ah             |

| 1Bh             |                      |                     | 9Bh             |

| 1Ch             |                      |                     | 9Ch             |

| 1Dh             |                      |                     | 9Dh             |

| 1Eh             | ADRES                |                     | 9Eh             |

| 1Fh             | ADCON0               | ADCON1              | 9Fh             |

| 20h             |                      |                     | A0h             |

| 2011            |                      | General             | AUII            |

|                 |                      | Purpose             |                 |

|                 | General              | Register            | BFh             |

|                 | Purpose              |                     | C0h             |

|                 | Register             |                     |                 |

|                 |                      |                     | EFh             |

| 70h             |                      | Mapped              | F0h             |

|                 |                      | in Bank 0           |                 |

| 7Fh             | Bank 0               | Bank 1              | _ FFh           |

|                 | Banko                | Dunki               |                 |

|                 | Unimplemented dat    | ta memory locatio   | ns, read        |

|                 | as '0'.              |                     |                 |

| Note 1:         | Not a physical regis | ster.               |                 |

|                 |                      |                     |                 |

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM.

The Special Function Registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### 4.2.2.2 OPTION REGISTER

The OPTION Register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0 and the weak pull-ups on GPIO. Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

## REGISTER 4-2: OPTION REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1                                                | R/W-1                                                                     | R/W-1                 | R/W-1      | R/W-1                  | R/W-1 | R/W-1 |                                                                                       |

|----------|------------------------------------------------------|---------------------------------------------------------------------------|-----------------------|------------|------------------------|-------|-------|---------------------------------------------------------------------------------------|

| GPPU     | INTEDG                                               | T0CS                                                                      | T0SE                  | PSA        | PS2                    | PS1   | PS0   | R = Readable bit                                                                      |

| bit7     |                                                      |                                                                           |                       |            |                        |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:   | <b>GPPU:</b> We 1 = Weak 0 = Weak                    | pull-ups o                                                                | disabled              | 3P0, GP1,  | GP3)                   |       |       |                                                                                       |

| bit 6:   |                                                      | pt on risi                                                                | ng edge of            |            | KI/AN2/IN<br>KI/AN2/IN |       |       |                                                                                       |

| bit 5:   | <b>TOCS:</b> TM<br>1 = Transit<br>0 = Interna        | ion on Gl                                                                 | P2/T0CKI/             | AN2/INT    |                        |       |       |                                                                                       |

| bit 4:   |                                                      | nent on hi                                                                | gh-to-low             | transition | on GP2/T0<br>on GP2/T0 |       |       |                                                                                       |

| bit 3:   | PSA: Pres<br>1 = Presca<br>0 = Presca                | aler is ass                                                               | signed to t           | he WDT     | module                 |       |       |                                                                                       |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> :                               | Prescaler                                                                 | Rate Sel              | ect bits   |                        |       |       |                                                                                       |

|          | Bit Value                                            | TMR0 R                                                                    | ate WD                | Γ Rate     |                        |       |       |                                                                                       |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 12<br>1 : 25 | 2 1:<br>4 1:<br>28 1: | 2<br>4     |                        |       |       |                                                                                       |

# **PIC12C67X**

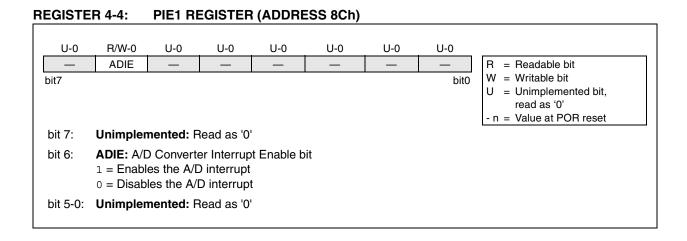

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the Peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

NOTES:

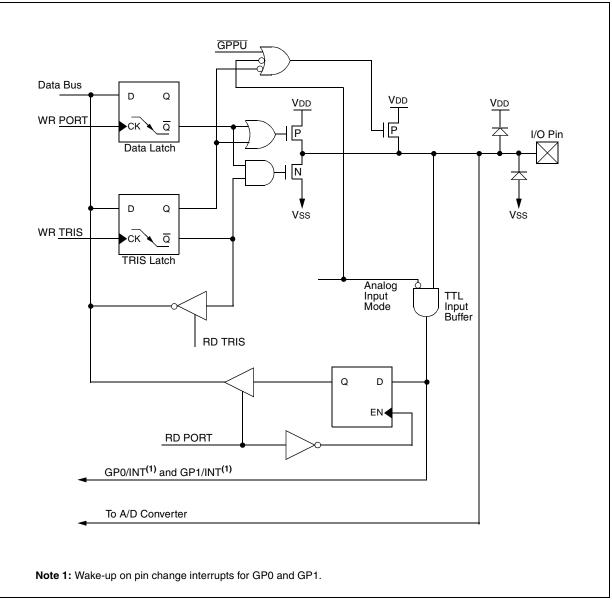

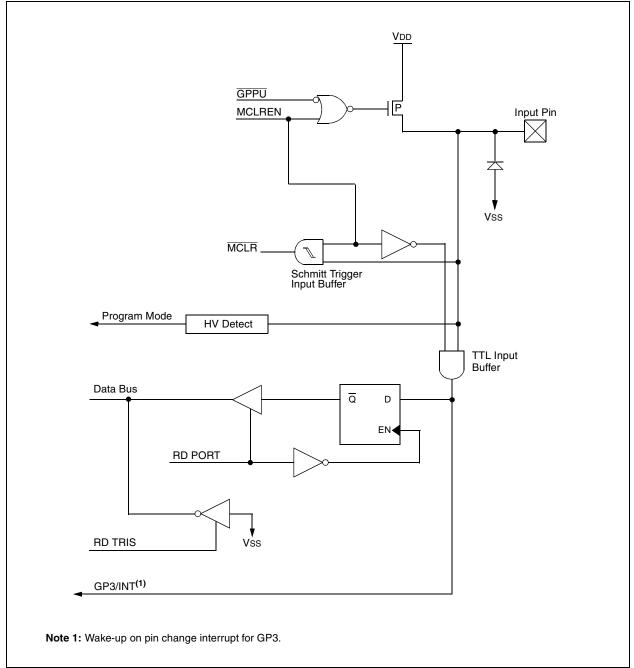

#### FIGURE 5-1: BLOCK DIAGRAM OF GP0/AN0 AND GP1/AN1/VREF PIN

#### 6.3 Write Operations

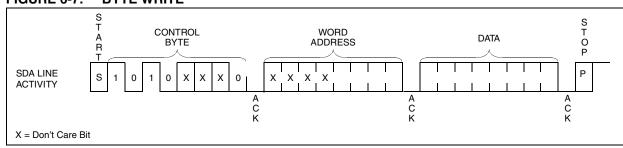

#### 6.3.1 BYTE WRITE

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the  $R/\overline{W}$  bit (which is a logic low) are placed onto the bus by the processor. This indicates to the addressed EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer. Only the lower four address bits are used by the device, and the upper four bits are don't cares. If the address byte is acknowledged, the processor will then transmit the data word to be written into the addressed memory location. The memory acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time will not generate acknowledge signals. After a byte write command, the internal address counter will not be incremented and will point to the same address location that was just written. If a stop bit sequence is transmitted to the device at any point in the write command sequence before the entire sequence is complete, then the command will abort and no data will be written. If more than 8 data bits are transmitted before the stop bit sequence is sent, then the device will clear the previously loaded byte and begin loading the data buffer again. If more than one data byte is transmitted to the device and a stop bit is sent before a full eight data bits have been transmitted, then the write command will abort and no data will be written. The EEPROM memory employs a VCC threshold detector circuit, which disables the internal erase/write logic if the Vcc is below minimum VDD. Byte write operations must be preceded and immediately followed by a bus not busy bus cycle where both SDA and SCL are held high. (See Figure 6-7 for Byte Write operation.)

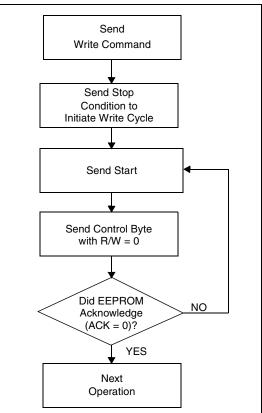

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. (See Figure 6-6 for flow diagram.)

#### FIGURE 6-6: ACKNOWLEDGE POLLING FLOW

#### FIGURE 6-7: BYTE WRITE

#### 6.5 <u>Read Operations</u>

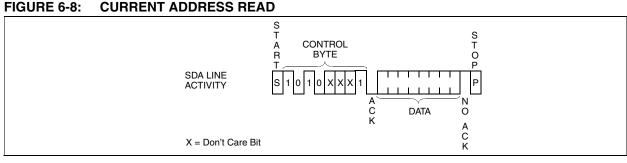

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the EEPROM address is set to one. There are three basic types of read operations; current address read, random read and sequential read.

#### 6.5.1 CURRENT ADDRESS READ

The EEPROM contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous read access was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the EEPROM address with the R/W bit set to one, the EEPROM issues an acknowledge and transmits the 8-bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-8).

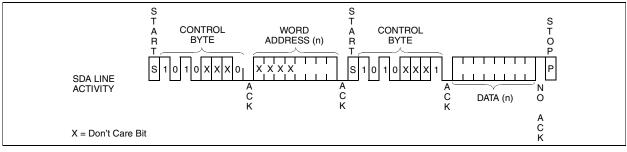

#### 6.5.2 RANDOM READ

Random read operations allow the processor to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the EEPROM as part of a write operation. After the word address is sent, the processor generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the processor issues the control byte again, but with the  $R/\overline{W}$  bit set to a one. The EEPROM will then issue an acknowledge and transmits the 8-bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-9). After this command, the internal address counter will point to the address location following the one that was just read.

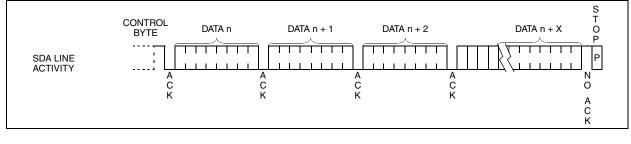

#### 6.5.3 SEQUENTIAL READ

Sequential reads are initiated in the same way as a random read, except that after the device transmits the first data byte, the processor issues an acknowledge as opposed to a stop condition in a random read. This directs the EEPROM to transmit the next sequentially addressed 8-bit word (Figure 6-10).

To provide sequential reads, the EEPROM contains an internal address pointer, which is incremented by one at the completion of each read operation. This address pointer allows the entire memory contents to be serially read during one operation.

#### FIGURE 6-9: RANDOM READ

### FIGURE 6-10: SEQUENTIAL READ

© 1997-2013 Microchip Technology Inc.

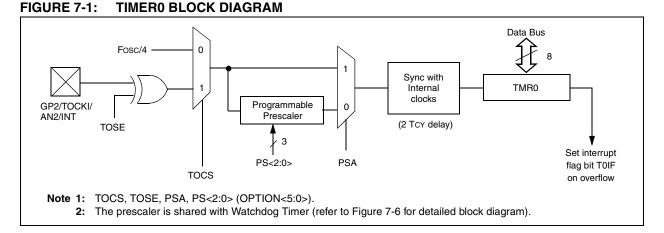

## 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

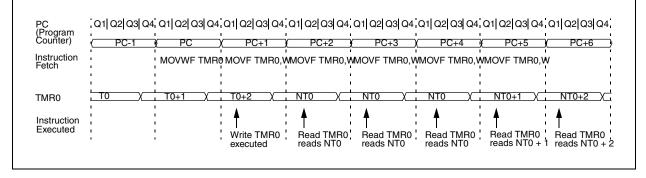

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

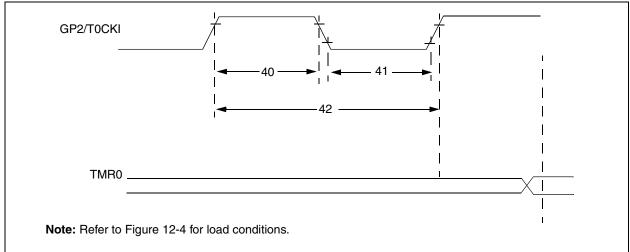

Counter mode is selected by setting bit TOCS (OPTION<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/TOCKI. The incrementing edge is determined by the bit TOSE

(OPTION<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

#### 9.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create a Poweron Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See Table 11-4.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 9.4.4 TIME-OUT SEQUENCE

On power-up, the Time-out Sequence is as follows: first, PWRT time-out is invoked after the POR time delay has expired; then, OST is activated. The total time-out will vary, based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-7, Figure 9-8, and Figure 9-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC12C67X device operating in parallel.

# 9.4.5 POWER CONTROL (PCON)/STATUS REGISTER

The Power Control/Status Register, PCON (address 8Eh), has one bit. See Register 4-6 for register.

Bit1 is POR (Power-on Reset). It is cleared on a Poweron Reset and is unaffected otherwise. The user sets this bit following a Power-on Reset. On subsequent resets, if POR is '0', it will indicate that a Power-on Reset must have occurred.

| <b>Oscillator Configuration</b> | Power            | Wake-up from SLEEP |          |

|---------------------------------|------------------|--------------------|----------|

|                                 | <b>PWRTE</b> = 0 | PWRTE = 1          |          |

| XT, HS, LP                      | 72 ms + 1024Tosc | 1024Tosc           | 1024Tosc |

| INTRC, EXTRC                    | 72 ms            | _                  | —        |

#### TABLE 9-4: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 9-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | то | PD |                                                         |

|-----|----|----|---------------------------------------------------------|

| 0   | 1  | 1  | Power-on Reset                                          |

| 0   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0  | u  | WDT Reset                                               |

| 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

Legend: u = unchanged, x = unknown.

## 10.2 Instruction Descriptions

| ADDLW            | Add Literal and                                         | w                  |         |

|------------------|---------------------------------------------------------|--------------------|---------|

| Syntax:          | [label] ADDLW                                           | / k                |         |

| Operands:        | $0 \leq k \leq 255$                                     |                    |         |

| Operation:       | $(W) + k \to (W)$                                       |                    |         |

| Status Affected: | C, DC, Z                                                |                    |         |

| Encoding:        | 11 111x                                                 | kkkk               | kkkk    |

| Description:     | The contents of added to the eig the result is placter. | ht bit literal     | 'k' and |

| Words:           | 1                                                       |                    |         |

| Cycles:          | 1                                                       |                    |         |

| Example          | ADDLW 0x15                                              |                    |         |

|                  | Before Instruction<br>W =<br>After Instruction<br>W =   | on<br>0x10<br>0x25 |         |

| ANDLW            | And Literal with W                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                 |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                          |

| Status Affected: | Z                                                                                                                        |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                        |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |

| Words:           | 1                                                                                                                        |

| Cycles:          | 1                                                                                                                        |

| Example          | ANDLW 0x5F                                                                                                               |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                          |

| ADDWF            | Add W and f                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                         |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                                |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. |

| Words:           | 1                                                                                                                                                                                |

| Cycles:          | 1                                                                                                                                                                                |

| Example          | addwf fsr, <b>O</b>                                                                                                                                                              |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                      |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |

| Status Affected: | Z                                                                                                                                                           |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                           |

| Cycles:          | 1                                                                                                                                                           |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |

# **PIC12C67X**

| GOTO                              | Unconditional Branch                                                                                                                                                                             | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [ <i>label</i> ] GOTO k                                                                                                                                                                          | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                       |

| Operands:                         | $0 \leq k \leq 2047$                                                                                                                                                                             | Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                                                                                                                                 |

| Operation:                        | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                         |

| Status Affected:                  | None                                                                                                                                                                                             | Status Affected: | None                                                                                                                                                                                                                                                                                                                     |

| Encoding:                         | 10 1kkk kkkk kkkk                                                                                                                                                                                | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                        |

| Description:<br>Words:<br>Cycles: | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two<br>cycle instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle |

| Example                           | GOTO THERE                                                                                                                                                                                       | Words:           | instruction.                                                                                                                                                                                                                                                                                                             |

|                                   | After Instruction                                                                                                                                                                                | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                     |

|                                   | PC = Address THERE                                                                                                                                                                               | Example          | HERE INCFSZ CNT, 1                                                                                                                                                                                                                                                                                                       |

|                                   |                                                                                                                                                                                                  |                  | GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                             |

|                                   |                                                                                                                                                                                                  |                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                                                                                  |

|                                   |                                                                                                                                                                                                  |                  | After Instruction<br>CNT = CNT + 1                                                                                                                                                                                                                                                                                       |

| INCF              | Increme                                                        | nt f      |                  |             |               |

|-------------------|----------------------------------------------------------------|-----------|------------------|-------------|---------------|

| Syntax:           | [ label ]                                                      | INCF      | f,d              |             |               |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 27        |                  |             |               |

| Operation:        | (f) + 1 $\rightarrow$                                          | (dest)    |                  |             |               |

| Status Affected:  | Z                                                              |           |                  |             |               |

| Encoding:         | 0 0                                                            | 1010      | df               | ff          | ffff          |

| Description:      | The content increment                                          | ents of r | egisi<br>I' is N | erra<br>the | are<br>result |

|                   | is placed<br>1, the res<br>ister 'f'.                          | in the V  | V reg            | ister.      | lf 'd' is     |

| Words:            | is placed 1, the res                                           | in the V  | V reg            | ister.      | lf 'd' is     |

| Words:<br>Cycles: | is placed<br>1, the res<br>ister 'f'.                          | in the V  | V reg            | ister.      | lf 'd' is     |

|                   | is placed<br>1, the res<br>ister 'f'.<br>1                     | in the V  | V reg<br>aced    | ister.      | lf 'd' is     |

| IORLW            | Inclusive OR Literal with W                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                         |

| Operands:        | $0 \le k \le 255$                                                                                                |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                |

| Description:     | The contents of the W register are OR'ed with the eight bit literal 'k'. The result is placed in the W register. |

| Words:           | 1                                                                                                                |

| Cycles:          | 1                                                                                                                |

| Example          | IORLW 0x35                                                                                                       |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                         |

if CNT=

PC =

if CNT≠

=

PC

0,

0,

address CONTINUE

address HERE +1

# **PIC12C67X**

| NOP              | No Oper   | ation |      |      |

|------------------|-----------|-------|------|------|

| Syntax:          | [ label ] | NOP   |      |      |

| Operands:        | None      |       |      |      |

| Operation:       | No opera  | ation |      |      |

| Status Affected: | None      |       |      |      |

| Encoding:        | 0 0       | 0000  | 0xx0 | 0000 |

| Description:     | No opera  | tion. |      |      |

| Words:           | 1         |       |      |      |

| Cycles:          | 1         |       |      |      |

| Example          | NOP       |       |      |      |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{TOS} \rightarrow \text{PC}, \\ 1 \rightarrow \text{GIE} \end{array}$                                                                                                                           |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global Inter-<br>rupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| OPTION           | Load Option Register                                                                                |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] OPTION                                                                                      |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                            |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Encoding:        | 0 0                                                                                                 | 00 0000 0110 0010                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Description:     | loaded in<br>This instr<br>code con<br>products.<br>able/writa                                      | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a read-<br>able/writable register, the user can<br>directly address it. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                   |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                   |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Example          |                                                                                                     |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC12C67X products,<br>do not use this instruction. |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two cycle instruction. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                   |

| Example          | CALL TABLE;W contains<br>table<br>;offset value                                                                                                                                     |

| TABLE            | • ;W now has table value                                                                                                                                                            |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |

|                  | •<br>RETLW kn ;End of table                                                                                                                                                         |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                      |

|                  | After Instruction<br>W = value of k8                                                                                                                                                |

### 12.3 DC CHARACTERISTICS:

#### PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

|       |                                    |                                                                      |                |      | -          |       |                                                              |  |  |  |

|-------|------------------------------------|----------------------------------------------------------------------|----------------|------|------------|-------|--------------------------------------------------------------|--|--|--|

|       |                                    |                                                                      |                |      |            |       | herwise specified)                                           |  |  |  |

|       |                                    | Operati                                                              | ng temperature |      |            |       | C (commercial)                                               |  |  |  |

| DC CH | ARACTERISTICS                      | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)                  |                |      |            |       |                                                              |  |  |  |

|       |                                    | -40°C $\leq$ TA $\leq$ +125°C (extended)                             |                |      |            |       |                                                              |  |  |  |

|       |                                    | Operating voltage VDD range as described in DC spec Section 12.1 and |                |      |            |       |                                                              |  |  |  |

|       |                                    | Section                                                              |                |      |            |       | • •••                                                        |  |  |  |

| Param | Characteristic                     | Sym                                                                  | Min            | Тур† | Max        | Units | Conditions                                                   |  |  |  |

| No.   |                                    |                                                                      |                |      |            |       |                                                              |  |  |  |

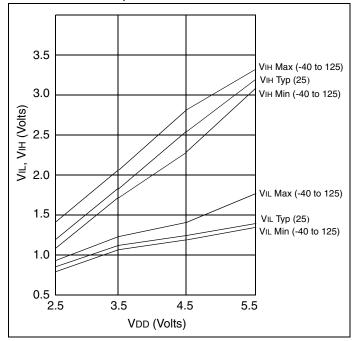

|       | Input Low Voltage                  |                                                                      |                |      |            |       |                                                              |  |  |  |

|       | I/O ports                          | Vi∟                                                                  |                |      |            |       |                                                              |  |  |  |

| D030  | with TTL buffer                    |                                                                      | Vss            | —    | 0.8V       | V     | For $4.5V \le VDD \le 5.5V$                                  |  |  |  |

|       |                                    |                                                                      | Vss            | —    | 0.15Vdd    | V     | otherwise                                                    |  |  |  |

| D031  | with Schmitt Trigger buffer        |                                                                      | Vss            | —    | 0.2Vdd     | V     |                                                              |  |  |  |

| D032  | MCLR, GP2/T0CKI/AN2/INT            |                                                                      | Vss            | —    | 0.2Vdd     | V     |                                                              |  |  |  |

|       | (in EXTRC mode)                    |                                                                      |                |      |            |       |                                                              |  |  |  |

| D033  | OSC1 (in EXTRC mode)               |                                                                      | Vss            | —    | 0.2Vdd     |       | Note 1                                                       |  |  |  |

| D033  | OSC1 (in XT, HS, and LP)           |                                                                      | Vss            | —    | 0.3Vdd     | V     | Note 1                                                       |  |  |  |

|       | Input High Voltage                 |                                                                      |                |      |            |       |                                                              |  |  |  |

|       | I/O ports                          | Vін                                                                  |                | _    |            |       |                                                              |  |  |  |

| D040  | with TTL buffer                    |                                                                      | 2.0V           | _    | Vdd        | v     | $4.5V \le VDD \le 5.5V$                                      |  |  |  |

| D040A |                                    |                                                                      | 0.25VDD + 0.8V | _    | Vdd        | v     | otherwise                                                    |  |  |  |

| D041  | with Schmitt Trigger buffer        |                                                                      | 0.8VDD         | _    | VDD        | v     | For entire VDD range                                         |  |  |  |

| D042  | MCLR. GP2/T0CKI/AN2/INT            |                                                                      | 0.8VDD         | _    | VDD        | v     |                                                              |  |  |  |

| D042A | OSC1 (XT, HS, and LP)              |                                                                      | 0.7VDD         |      | VDD        | V     | Note 1                                                       |  |  |  |

| D043  | OSC1 (in EXTRC mode)               |                                                                      | 0.9VDD         | _    | VDD        | v     |                                                              |  |  |  |

| 2010  | Input Leakage Current (Notes 2, 3) |                                                                      | 0.0755         |      |            | •     |                                                              |  |  |  |

| D060  | I/O ports                          | lı∟                                                                  |                | _    | <u>+</u> 1 | μA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at                           |  |  |  |

| Dooo  |                                    |                                                                      |                |      | <u> </u>   | μι    | hi-impedance                                                 |  |  |  |

| D061  | GP3/MCLR (Note 5)                  |                                                                      |                |      | +30        | μA    | $VSS \leq VPIN \leq VDD$                                     |  |  |  |

| D061A | GP3 (Note 6)                       |                                                                      |                |      | +5         | μA    | $VSS \leq VPIN \leq VDD$                                     |  |  |  |

| D062  | GP2/T0CKI                          |                                                                      |                | _    |            | μA    | $V_{SS} \leq V_{PIN} \leq V_{DD}$                            |  |  |  |

| D063  | OSC1                               |                                                                      |                |      | <u>+</u> 5 | •     |                                                              |  |  |  |

| D063  | 0501                               |                                                                      | _              | _    | <u>+</u> 5 | μA    | VSS $\leq$ VPIN $\leq$ VDD, XT, HS, and LP osc configuration |  |  |  |

| D070  | GPIO weak pull-up current (Note 4) | IPUR                                                                 | 50             | 250  | 400        | μA    | VDD = 5V, VPIN = VSS                                         |  |  |  |

|       | MCLR pull-up current               | —                                                                    | —              | —    | 30         | μA    | VDD = 5V, VPIN = VSS                                         |  |  |  |

|       | Output Low Voltage                 |                                                                      |                |      |            |       |                                                              |  |  |  |

| D080  | I/O ports                          | Vol                                                                  | —              | —    | 0.6        | V     | IOL = 8.5 mA, VDD = 4.5V,<br>−40°C to +85°C                  |  |  |  |

| D080A |                                    |                                                                      | —              | —    | 0.6        | V     | IOL = 7.0 mA, VDD = 4.5V,<br>−40°C to +125°C                 |  |  |  |

| D083  | OSC2/CLKOUT                        |                                                                      | —              | —    | 0.6        | V     | IOL = 1.6 mA, VDD = 4.5V,<br>−40°C to +85°C                  |  |  |  |

| D083A |                                    |                                                                      | _              |      | 0.6        | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                 |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as coming out of the pin.

- 4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

## 12.4 DC CHARACTERISTICS:

#### PIC12LC671/672 (Commercial, Industrial) PIC12LCE673/674 (Commercial, Industrial)

| DC CHA       | RACTERISTICS                       | Operatir      | rd Operating Cor<br>ng temperature<br>ng voltage VDD rai | 0°<br>–40° | $C \leq TA \leq C \leq TA \leq C \leq $ | +70°C<br>+85°C ( | wise specified)<br>(commercial)<br>(industrial)<br>Spec Section 12.1 and |  |  |

|--------------|------------------------------------|---------------|----------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------|--|--|

|              | <u> </u>                           | Section 12.2. |                                                          |            |                                                                                                 |                  |                                                                          |  |  |

| Param<br>No. | Characteristic                     | Sym           | Min                                                      | Тур†       | Max                                                                                             | Units            | Conditions                                                               |  |  |

|              | Input Low Voltage                  |               |                                                          |            |                                                                                                 |                  |                                                                          |  |  |

|              | I/O ports                          | VIL           |                                                          |            |                                                                                                 |                  |                                                                          |  |  |

| D030         | with TTL buffer                    |               | Vss                                                      | —          | 0.8V                                                                                            | V                | For $4.5V \le VDD \le 5.5V$                                              |  |  |

|              |                                    |               | Vss                                                      | —          | 0.15VDD                                                                                         | V                | otherwise                                                                |  |  |

| D031         | with Schmitt Trigger buffer        |               | Vss                                                      | —          | 0.2Vdd                                                                                          | V                |                                                                          |  |  |

| D032         | MCLR, GP2/T0CKI/AN2/INT            |               | Vss                                                      |            | 0.2Vdd                                                                                          | V                |                                                                          |  |  |

|              | (in EXTRC mode)                    |               |                                                          |            |                                                                                                 |                  |                                                                          |  |  |

| D033         | OSC1 (in EXTRC mode)               |               | Vss                                                      | —          | 0.2VDD                                                                                          | V                | Note 1                                                                   |  |  |

| D033         | OSC1 (in XT, HS, and LP)           |               | Vss                                                      | —          | 0.3Vdd                                                                                          | V                | Note 1                                                                   |  |  |

|              | Input High Voltage                 |               |                                                          |            |                                                                                                 |                  |                                                                          |  |  |

|              | I/O ports                          | Vін           |                                                          | —          |                                                                                                 |                  |                                                                          |  |  |

| D040         | with TTL buffer                    |               | 2.0V                                                     | —          | Vdd                                                                                             | V                | $4.5V \le VDD \le 5.5V$                                                  |  |  |

| D040A        |                                    |               | 0.25VDD + 0.8V                                           |            | Vdd                                                                                             | V                | otherwise                                                                |  |  |

| D041         | with Schmitt Trigger buffer        |               | 0.8VDD                                                   | —          | Vdd                                                                                             | V                | For entire VDD range                                                     |  |  |

| D042         | MCLR, GP2/T0CKI/AN2/INT            |               | 0.8VDD                                                   | —          | Vdd                                                                                             | V                | _                                                                        |  |  |

| D042A        | OSC1 (XT, HS, and LP)              |               | 0.7VDD                                                   | _          | Vdd                                                                                             | v                | Note 1                                                                   |  |  |

| D043         | OSC1 (in EXTRC mode)               |               | 0.9VDD                                                   | _          | Vdd                                                                                             | v                |                                                                          |  |  |

|              | Input Leakage Current (Notes 2, 3) |               |                                                          |            |                                                                                                 |                  |                                                                          |  |  |

| D060         | I/O ports                          | lı∟           | _                                                        | _          | <u>+</u> 1                                                                                      | μA               | $Vss \le VPIN \le VDD$ , Pin at hi-impedance                             |  |  |

| D061         | GP3/MCLR (Note 5)                  |               |                                                          |            | <u>+</u> 30                                                                                     | μA               | $Vss \leq VPIN \leq VDD$                                                 |  |  |

| D061A        | GP3 (Note 6)                       |               |                                                          |            | <u>+</u> 5                                                                                      | μA               | $Vss \leq VPIN \leq VDD$                                                 |  |  |

| D062         | GP2/T0CKI                          |               | _                                                        |            | <u>+</u> 5                                                                                      | μA               | $Vss \leq VPIN \leq VDD$                                                 |  |  |

| D063         | OSC1                               |               | —                                                        | _          | <u>+</u> 5                                                                                      | μA               | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration              |  |  |

| D070         | GPIO weak pull-up current (Note 4) | IPUR          | 50                                                       | 250        | 400                                                                                             | μA               | VDD = 5V, VPIN = VSS                                                     |  |  |

|              | MCLR pull-up current               | —             | —                                                        | —          | 30                                                                                              | μA               | VDD = 5V, VPIN = VSS                                                     |  |  |

|              | Output Low Voltage                 | 1             |                                                          |            |                                                                                                 |                  |                                                                          |  |  |

| D080         | I/O ports                          | Vol           | —                                                        | -          | 0.6                                                                                             | V                | IOL = 8.5 mA, VDD = 4.5V,<br>−40°C to +85°C                              |  |  |

| D080A        |                                    |               | —                                                        | _          | 0.6                                                                                             | V                | IOL = 7.0 mA, VDD = 4.5V,<br>−40°C to +125°C                             |  |  |

| D083         | OSC2/CLKOUT                        |               | —                                                        | _          | 0.6                                                                                             | V                | IOL = TBD, VDD = 4.5V,<br>−40°C to +85°C                                 |  |  |

| D083A        |                                    |               | _                                                        | -          | 0.6                                                                                             | V                | IOL = TBD, VDD = 4.5V,<br>−40°C to +125°C                                |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.