Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 8-SOIJ                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671-04-sm |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

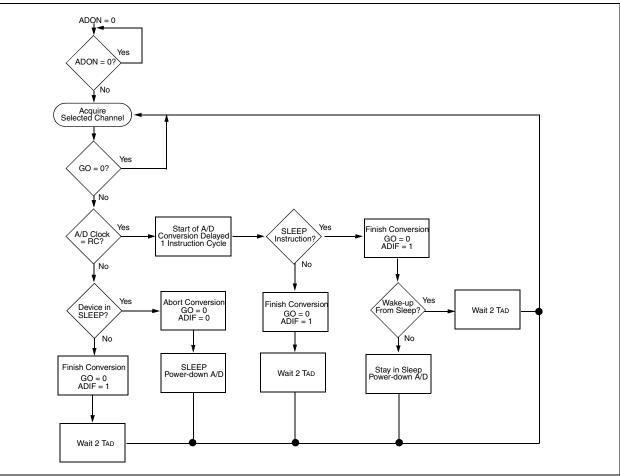

The PIC12C67X devices are low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converter and EEPROM data memory (EEPROM on PIC12CE67X versions only).

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC12C67X microcontrollers have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches, which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC12C67X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC12C67X devices have 128 bytes of RAM, 16 bytes of EEPROM data memory (PIC12CE67X only), 5 I/O pins and 1 input pin. In addition a timer/counter is available. Also a 4-channel, high-speed, 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, (i.e., thermostat control, pressure sensing, etc.)

The PIC12C67X devices have special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. The Power-On Reset (POR), Power-up Timer (PWRT), and Oscillator Start-up Timer (OST) eliminate the need for external reset circuitry. There are five oscillator configurations to choose from, including INTRC precision internal oscillator mode and the power-saving LP (Low Power) oscillator mode. Power-saving SLEEP mode, Watchdog Timer and code protection features improve system cost, power and reliability. The SLEEP (power-down) feature provides a power-saving mode. The user can wake-up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

A UV erasable windowed package version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

# 1.1 <u>Applications</u>

The PIC12C67X series fits perfectly in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The EPROM technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient, while the EEPROM data memory (PIC12CE67X only) technology allows for the changing of calibration factors and security codes. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC12C67X series very versatile even in areas where no microcontroller use has been considered before (i.e., timer functions, replacement of "glue" logic and PLD's in larger systems, coprocessor applications).

## 1.2 Family and Upward Compatibility

The PIC12C67X products are compatible with other members of the 14-bit PIC16CXXX families.

# 1.3 Development Support

The PIC12C67X devices are supported by a fullfeatured macro assembler, a software simulator, an incircuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

# 4.0 MEMORY ORGANIZATION

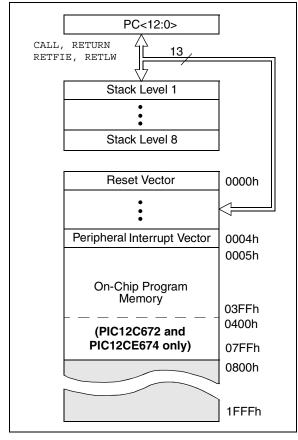

# 4.1 Program Memory Organization

The PIC12C67X has a 13-bit program counter capable of addressing an 8K x 14 program memory space.

For the PIC12C671 and the PIC12CE673, the first 1K x 14 (0000h-03FFh) is implemented.

For the PIC12C672 and the PIC12CE674, the first 2K x 14 (0000h-07FFh) is implemented. Accessing a location above the physically implemented address will cause a wraparound. The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PIC12C67X PROGRAM MEMORY MAP AND STACK

# 4.2 Data Memory Organization

The data memory is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow \text{Bank } 1$

RP0 (STATUS<5>) =  $0 \rightarrow Bank 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain Special Function Registers. Some "high use" Special Function Registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

Also note that F0h through FFh on the PIC12C67X is mapped into Bank 0 registers 70h-7Fh as common RAM.

4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register FSR (Section 4.5).

#### 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 Register overflow, GPIO port change and external GP2/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

# REGISTER 4-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0                                                                                                                                     | R/W-0        | R/W-0       | R/W-0       | R/W-0                             | R/W-0       | R/W-x        |                                                                                                           |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|-----------------------------------|-------------|--------------|-----------------------------------------------------------------------------------------------------------|--|

| GIE<br>bit7 | PEIE                                                                                                                                      | TOIE         | INTE        | GPIE        | TOIF                              | INTF        | GPIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7:      | <b>GIE:</b> Glob<br>1 = Enabl<br>0 = Disab                                                                                                | es all un-r  | nasked in   |             |                                   |             |              |                                                                                                           |  |

| bit 6:      | PEIE: Per<br>1 = Enabl<br>0 = Disab                                                                                                       | es all un-r  | nasked pe   | ripheral ir | iterrupts                         |             |              |                                                                                                           |  |

| bit 5:      | <b>TOIE:</b> TMI<br>1 = Enabl<br>0 = Disab                                                                                                | es the TM    | R0 interru  | ıpt         | bit                               |             |              |                                                                                                           |  |

| bit 4:      |                                                                                                                                           | es the ext   | ernal inter | rupt on GI  | P2/INT/T00<br>P2/INT/T00          |             |              |                                                                                                           |  |

| bit 3:      | <b>GPIE:</b> GPIO Interrupt on Change Enable bit<br>1 = Enables the GPIO Interrupt on Change<br>0 = Disables the GPIO Interrupt on Change |              |             |             |                                   |             |              |                                                                                                           |  |

| bit 2:      | <b>TOIF:</b> TMR<br>1 = TMRC<br>0 = TMRC                                                                                                  | ) register h | as overflo  | wed (mus    | t be cleare                       | d in softwa | re)          |                                                                                                           |  |

| bit 1:      |                                                                                                                                           | xternal int  | errupt on   | GP2/INT/1   | TOCKI/AN2<br>TOCKI/AN2            |             |              | e cleared in software)                                                                                    |  |

| bit 0:      |                                                                                                                                           | GP1 or Gl    | P3 pins ch  | anged sta   | bit<br>ite (must be<br>ve changed |             | n software)  |                                                                                                           |  |

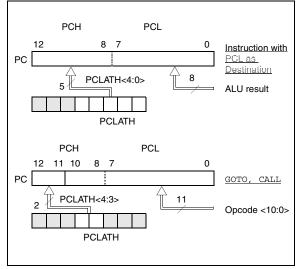

# 4.3 PCL and PCLATH

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL Register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any reset, the PC is cleared. Figure 4-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### 4.3.1 COMPUTED GOTO

A Computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC12C67X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

## 4.4 <u>Program Memory Paging</u>

The PIC12C67X ignores both paging bits PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC12C67X is not recommended since this may affect upward compatibility with future products.

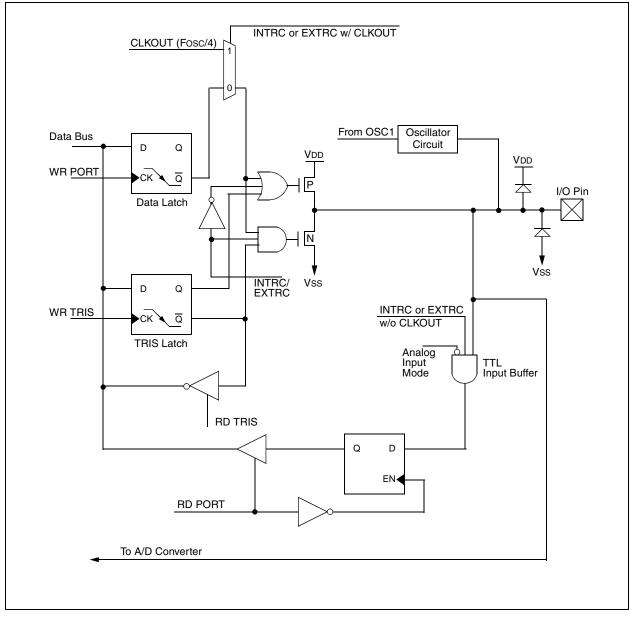

FIGURE 5-4: BLOCK DIAGRAM OF GP4/OSC2/AN3/CLKOUT PIN

#### TABLE 8-2: SUMMARY OF A/D REGISTERS

| Address | Name                  | Bit 7              | Bit 6              | Bit 5                                    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|-----------------------|--------------------|--------------------|------------------------------------------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 0Bh/8Bh | INTCON <sup>(1)</sup> | GIE                | PEIE               | TOIE                                     | INTE  | GPIE  | T0IF  | INTF  | GPIF  | x000 000x                     | 0000 000u                       |

| 0Ch     | PIR1                  | —                  | ADIF               | _                                        | —     | —     | -     | —     | —     | -0                            | -0                              |

| 8Ch     | PIE1                  | —                  | ADIE               | —                                        | _     | _     | _     | —     | —     | -0                            | -0                              |

| 1Eh     | ADRES                 | A/D Res            | sult Regist        | er                                       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| 1Fh     | ADCON0                | ADCS1              | ADCS0              | reserved CHS1 CHS0 GO/DONE reserved ADON |       |       |       |       |       | 0000 0000                     | 0000 0000                       |

| 9Fh     | ADCON1                | _                  | _                  | _                                        |       | -     | PCFG2 | PCFG1 | PCFG0 | 000                           | 000                             |

| 05h     | GPIO                  | SCL <sup>(2)</sup> | SDA <sup>(2)</sup> | GP5                                      | GP4   | GP3   | GP2   | GP1   | GP0   | 11xx xxxx                     | 11uu uuuu                       |

| 85h     | TRIS                  | _                  | _                  | TRIS5                                    | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0 | 11 1111                       | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers can be addressed from either bank.

2: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

#### TABLE 9-6: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | u-               |

| WDT Reset during normal operation  | 000h                  | 0000 uuuu          | u-               |

| WDT Wake-up from SLEEP             | PC + 1                | uuu0 0uuu          | u-               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### TABLE 9-7: INITIALIZATION CON\DITIONS FOR ALL REGISTERS

| Power-on Reset | MCLR Resets<br>WDT Reset                                                                                                                                                                                                                                                                        | Wake-up via<br>WDT or Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xxxx xxxx      | <u>uuuu</u> uuuu                                                                                                                                                                                                                                                                                | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                       | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| xxxx xxxx      | นนนน นนนน                                                                                                                                                                                                                                                                                       | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                       | PC + 1 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                                                                                                                                                                                                                        | uuuq quuu <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| xxxx xxxx      | นนนน นนนน                                                                                                                                                                                                                                                                                       | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11xx xxxx      | 11uu uuuu                                                                                                                                                                                                                                                                                       | 11uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| xx xxxx        | uu uuuu                                                                                                                                                                                                                                                                                         | uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0 0000         | 0 0000                                                                                                                                                                                                                                                                                          | u uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0000 000x      | 0000 000u                                                                                                                                                                                                                                                                                       | uuuu uqqq <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -0             | -0                                                                                                                                                                                                                                                                                              | - <u>q</u> (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                       | uuuu uquu <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1111 1111      | 1111 1111                                                                                                                                                                                                                                                                                       | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11 1111        | 11 1111                                                                                                                                                                                                                                                                                         | uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -0             | -0                                                                                                                                                                                                                                                                                              | -u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0-             | u-                                                                                                                                                                                                                                                                                              | u-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0111 00        | uuuu uu                                                                                                                                                                                                                                                                                         | uuuu uu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 000            | 000                                                                                                                                                                                                                                                                                             | uuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | XXXX XXXX         0000 0000         XXXX XXXX         0000 0000         0001 1xxx         XXXX XXXX         11xx XXXX         11xx XXXX        xx XXXX        xx XXXX        0 0000         0000 000x         -0         0000 0000         1111 1111        11 1111         -0         0.011 00 | WDT Reset           xxxx xxxx         uuuu uuuu           0000 0000         0000 0000           xxxx xxxx         uuuu uuuu           0000 0000         0000 0000           xxxx xxxx         uuuu uuuu           0001 1xxx         000q quuu <sup>(3)</sup> xxxx xxxx         uuuu uuuu           11xx xxxx         11uu uuuu           11xx xxxx         11uu uuuu          xx xxxx        uu uuuu          xx xxxx        uu uuuu          0 0000        0 0000           0000 000x         0000 000u           0000 000x         0000 000u           -0         -0           0000 0000         0000 0000           1111 111         1111 111          11 111        11 1111           -0            -0            -0            -0            -0            -0            -0            -0 </td |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: One or more bits in INTCON and PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 9-5 for reset value for specific condition.

4: If wake-up was due to A/D completing then bit 6 = 1, all other interrupts generating a wake-up will cause bit 6 = u.

5: If wake-up was due to A/D completing then bit 3 = 0, all other interrupts generating a wake-up will cause bit 3 = u.

# PIC12C67X

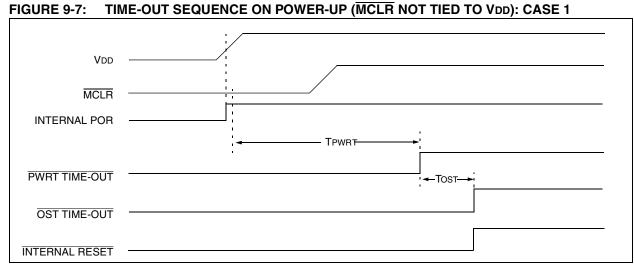

#### FIGURE 9-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

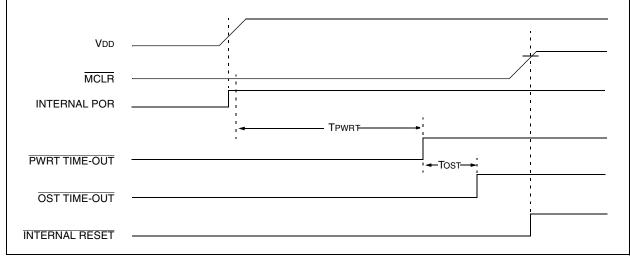

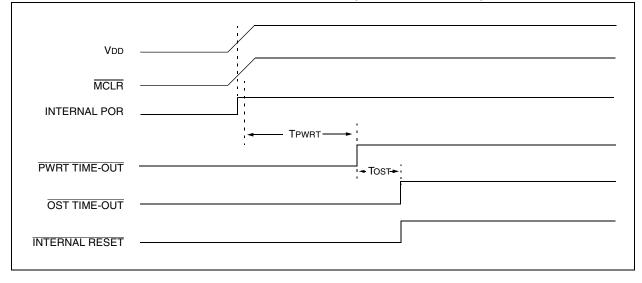

## FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

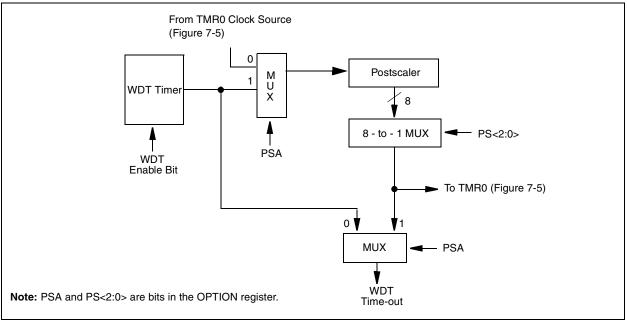

### 9.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 9.1).

#### 9.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized. The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out early and generating a premature device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

9.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

Note: When the prescaler is assigned to the WDT, always execute a CLRWDT instruction before changing the prescale value, otherwise a WDT reset may occur.

See Example 7-1 and Example 7-2 for changing prescaler between WDT and Timer0.

#### FIGURE 9-15: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 9-8: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name                        | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------------------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits <sup>(1)</sup> | MCLRE | CP1    | CP0   | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| 81h     | OPTION                      | GPPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 9-1 for operation of these bits. Not all CP0 and CP1 bits are shown.

| FIGURE 9-16: WAKE-UP FROM SLEEP THROUGH INTERRUPT |

|---------------------------------------------------|

|---------------------------------------------------|

| ; a1   a2   a3   a<br>osc1 ///////      | 4; Q1  Q2  Q3  Q4<br>_/~~~~ |                       | Q1  Q2  Q3  Q4 | 01 02 03 04<br>////////       | 01 02 03 04 | Q1 Q2 Q3 Q4; |

|-----------------------------------------|-----------------------------|-----------------------|----------------|-------------------------------|-------------|--------------|

| CLKOUT(4)                               | -∖/                         | Tost(2)               | /              | \/                            | \/¦         |              |

| GPIO pin                                | <br>                        | x                     |                | I<br>I<br>I                   |             |              |

| GPIF flag<br>(INTCON<0>)                |                             |                       |                | Interrupt Latency<br>(Note 3) |             | i            |

| GIE bit<br>(INTCON<7>)                  | <br><br>                    | Processor in<br>SLEEP |                |                               |             |              |

| INSTRUCTION FLOW                        | 1                           |                       |                | i i                           |             | 1            |

| РС Х РС                                 | X PC+1                      | X PC+2                | PC+2           | X PC + 2                      | X 0004h     | 0005h        |

| Instruction<br>fetched Inst(PC) = SLEEF | Inst(PC + 1)                | I I I                 | Inst(PC + 2)   | I I I                         | Inst(0004h) | Inst(0005h)  |

| Instruction<br>executed Inst(PC - 1)    | SLEEP                       | I i                   | Inst(PC + 1)   | Dummy cycle                   | Dummy cycle | Inst(0004h)  |

Note 1: XT, HS or LP oscillator mode assumed.

- 2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for INTRC and EXTRC osc mode.

- **3:** GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in XT, HS or LP osc modes, but shown here for timing reference.

#### 9.9 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 9.10 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

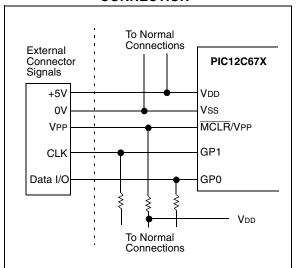

#### 9.11 In-Circuit Serial Programming

PIC12C67X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the GP1 and GP0 pins low, while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). GP1 (clock) becomes the programming clock and GP0 (data) becomes the programming data. Both GP0 and GP1 are Schmitt Trigger inputs in this mode.

After reset, and if the device is placed into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC12C67X Programming Specifications.

#### FIGURE 9-17: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

NOTES:

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- · Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- · Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

#### 11.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

#### 11.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

#### 11.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 11.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

# **PIC12C67X**

NOTES:

# 12.3 DC CHARACTERISTICS:

#### PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

|       |                                    |                                                     |                |       | -          |        |                                                              |  |  |

|-------|------------------------------------|-----------------------------------------------------|----------------|-------|------------|--------|--------------------------------------------------------------|--|--|

|       |                                    |                                                     |                |       |            |        | nerwise specified)                                           |  |  |

|       |                                    | Operati                                             | ng temperature |       |            |        | C (commercial)                                               |  |  |

| DC CH | ARACTERISTICS                      | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) |                |       |            |        |                                                              |  |  |

|       |                                    | -                                                   |                |       |            |        | C (extended)                                                 |  |  |

|       |                                    |                                                     |                | range | as descri  | bed in | DC spec Section 12.1 and                                     |  |  |

|       |                                    | Section                                             |                |       |            |        |                                                              |  |  |

| Param | Characteristic                     | Sym                                                 | Min            | Тур†  | Max        | Units  | Conditions                                                   |  |  |

| No.   |                                    |                                                     |                |       |            |        |                                                              |  |  |

|       | Input Low Voltage                  |                                                     |                |       |            |        |                                                              |  |  |

|       | I/O ports                          | Vi∟                                                 |                |       |            |        |                                                              |  |  |

| D030  | with TTL buffer                    |                                                     | Vss            | —     | 0.8V       | V      | For $4.5V \le VDD \le 5.5V$                                  |  |  |

|       |                                    |                                                     | Vss            | —     | 0.15Vdd    | V      | otherwise                                                    |  |  |

| D031  | with Schmitt Trigger buffer        |                                                     | Vss            | —     | 0.2Vdd     | V      |                                                              |  |  |

| D032  | MCLR, GP2/T0CKI/AN2/INT            |                                                     | Vss            | —     | 0.2Vdd     | V      |                                                              |  |  |

|       | (in EXTRC mode)                    |                                                     |                |       |            |        |                                                              |  |  |

| D033  | OSC1 (in EXTRC mode)               |                                                     | Vss            | —     | 0.2Vdd     |        | Note 1                                                       |  |  |

| D033  | OSC1 (in XT, HS, and LP)           |                                                     | Vss            | —     | 0.3Vdd     | V      | Note 1                                                       |  |  |

|       | Input High Voltage                 |                                                     |                |       |            |        |                                                              |  |  |

|       | I/O ports                          | Vін                                                 |                | _     |            |        |                                                              |  |  |

| D040  | with TTL buffer                    |                                                     | 2.0V           | _     | Vdd        | v      | $4.5V \le VDD \le 5.5V$                                      |  |  |

| D040A |                                    |                                                     | 0.25VDD + 0.8V | _     | Vdd        | v      | otherwise                                                    |  |  |

| D041  | with Schmitt Trigger buffer        |                                                     | 0.8VDD         | _     | VDD        | v      | For entire VDD range                                         |  |  |

| D042  | MCLR. GP2/T0CKI/AN2/INT            |                                                     | 0.8VDD         | _     | VDD        | v      |                                                              |  |  |

| D042A | OSC1 (XT, HS, and LP)              |                                                     | 0.7VDD         |       | VDD        | V      | Note 1                                                       |  |  |

| D043  | OSC1 (in EXTRC mode)               |                                                     | 0.9VDD         | _     | VDD        | v      |                                                              |  |  |

| 2010  | Input Leakage Current (Notes 2, 3) |                                                     | 0.0755         |       |            | •      |                                                              |  |  |

| D060  | I/O ports                          | lı∟                                                 |                | _     | <u>+</u> 1 | μA     | VSS $\leq$ VPIN $\leq$ VDD, Pin at                           |  |  |

| 2000  |                                    |                                                     |                |       | <u> </u>   | μι     | hi-impedance                                                 |  |  |

| D061  | GP3/MCLR (Note 5)                  |                                                     |                |       | +30        | μA     | $VSS \leq VPIN \leq VDD$                                     |  |  |

| D061A | GP3 (Note 6)                       |                                                     |                |       | +5         | μA     | $VSS \leq VPIN \leq VDD$                                     |  |  |

| D062  | GP2/T0CKI                          |                                                     |                | _     |            | μA     | $V_{SS} \leq V_{PIN} \leq V_{DD}$                            |  |  |

| D063  | OSC1                               |                                                     |                |       | <u>+</u> 5 | •      |                                                              |  |  |

| D063  | 0501                               |                                                     | _              | _     | <u>+</u> 5 | μA     | VSS $\leq$ VPIN $\leq$ VDD, XT, HS, and LP osc configuration |  |  |

| D070  | GPIO weak pull-up current (Note 4) | IPUR                                                | 50             | 250   | 400        | μA     | VDD = 5V, VPIN = VSS                                         |  |  |

|       | MCLR pull-up current               | —                                                   | —              | —     | 30         | μA     | VDD = 5V, VPIN = VSS                                         |  |  |

|       | Output Low Voltage                 |                                                     |                |       |            |        |                                                              |  |  |

| D080  | I/O ports                          | Vol                                                 | —              | —     | 0.6        | V      | IOL = 8.5 mA, VDD = 4.5V,<br>−40°C to +85°C                  |  |  |

| D080A |                                    |                                                     | —              | —     | 0.6        | V      | IOL = 7.0 mA, VDD = 4.5V,<br>−40°C to +125°C                 |  |  |

| D083  | OSC2/CLKOUT                        |                                                     | —              | —     | 0.6        | V      | IOL = 1.6 mA, VDD = 4.5V,<br>−40°C to +85°C                  |  |  |

| D083A |                                    |                                                     | _              |       | 0.6        | V      | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                 |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as coming out of the pin.

- 4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

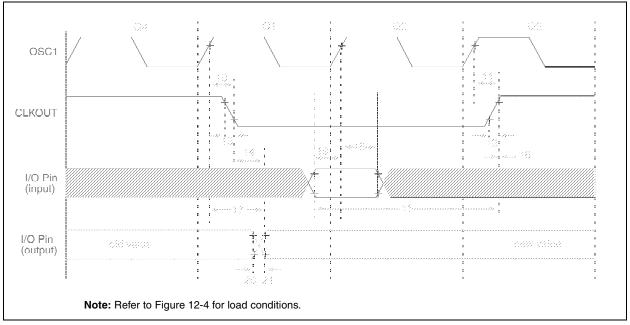

#### FIGURE 12-6: CLKOUT AND I/O TIMING

| TABLE 12-3: | CLKOUT AND I/O TIMING REQUIREMENTS |

|-------------|------------------------------------|

|-------------|------------------------------------|

| Param<br>No. | Sym      | Characteristic                                 |                     | Min        | Тур† | Мах         | Units | Conditions |

|--------------|----------|------------------------------------------------|---------------------|------------|------|-------------|-------|------------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                               |                     | _          | 75   | 200         | ns    | Note 1     |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                               |                     | _          | 75   | 200         | ns    | Note 1     |

| 12*          | TckR     | CLKOUT rise time                               |                     | _          | 35   | 100         | ns    | Note 1     |

| 13*          | TckF     | CLKOUT fall time                               |                     | —          | 35   | 100         | ns    | Note 1     |

| 14*          | TckL2ioV | CLKOUT $\downarrow$ to Port out valid          |                     | —          |      | 0.5TCY + 20 | ns    | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOU                     | Т↑                  | Tosc + 200 | —    | —           | ns    | Note 1     |

| 16*          | TckH2iol | Port in hold after CLKOUT $\uparrow$           |                     | 0          |      | —           | ns    | Note 1     |

| 17*          | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid |                     | —          | 50   | 150         | ns    |            |

| 18*          | TosH2iol | OSC1↑ (Q2 cycle) to Port                       | PIC12 <b>C</b> 67X  | 100        | —    | —           | ns    |            |

| 18A*         |          | input invalid (I/O in hold<br>time)            | PIC12 <b>LC</b> 67X | 200        | —    | —           | ns    |            |

| 19*          | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I time) | /O in setup         | 0          | —    | —           | ns    |            |

| 20*          | TioR     | Port output rise time                          | PIC12 <b>C</b> 67X  | _          | 10   | 40          | ns    |            |

| 20A*         |          |                                                | PIC12 <b>LC</b> 67X | _          |      | 80          | ns    |            |

| 21*          | TioF     | Port output fall time                          | PIC12 <b>C</b> 67X  | —          | 10   | 40          | ns    |            |

| 21A*         |          | PIC12 <b>LC</b> 67X                            |                     | —          | _    | 80          | ns    |            |

| 22††*        | Tinp     | GP2/INT pin high or low time                   |                     | Тсү        |      | —           | ns    |            |

| 23††*        | Trbp     | GP0/GP1/GP3 change INT time                    | high or low         | Тсү        | —    | —           | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in EXTRC and INTRC modes where CLKOUT output is 4 x Tosc.

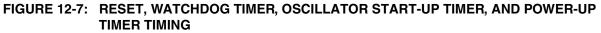

TABLE 12-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER

| Parameter<br>No. | Sym   | Characteristic                                            | Min | Тур†     | Мах | Units | Conditions                                         |

|------------------|-------|-----------------------------------------------------------|-----|----------|-----|-------|----------------------------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                    | 2   | —        |     | μS    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)          | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32               | Tost  | Oscillation Start-up Timer Period                         | _   | 1024Tosc | _   | —     | Tosc = OSC1 period                                 |

| 33*              | Tpwrt | Power up Timer Period                                     | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34               | TIOZ  | I/O Hi-impedance from MCLR<br>Low or Watchdog Timer Reset |     | _        | 2.1 | μS    |                                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

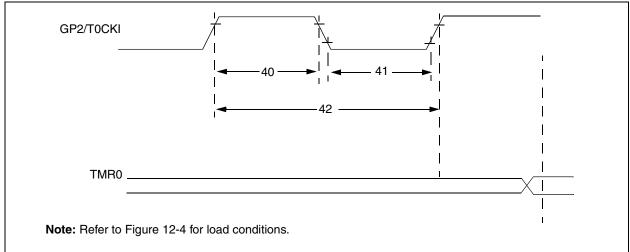

## FIGURE 12-8: TIMER0 CLOCK TIMINGS

## TABLE 12-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No.  | Sym       | Characteristic                                       |                | Min                                       | Тур† | Max       | Units | Conditions                            |

|---------------|-----------|------------------------------------------------------|----------------|-------------------------------------------|------|-----------|-------|---------------------------------------|

| 40*           | Tt0H      | T0CKI High Pulse Width                               | No Prescaler   | 0.5TCY + 20                               | —    | —         | ns    | Must also meet                        |

|               |           |                                                      | With Prescaler | 10                                        | —    | —         | ns    | parameter 42                          |

| 41* TtOL      |           | T0CKI Low Pulse Width                                | No Prescaler   | 0.5TCY + 20                               | -    | _         | ns    | Must also meet                        |

|               |           |                                                      | With Prescaler | 10                                        | -    | _         | ns    | parameter 42                          |

| 42* TtOP TOCH |           | T0CKI Period                                         | No Prescaler   | TCY + 40                                  | —    | _         | ns    |                                       |

|               |           |                                                      | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | —         | ns    | N = prescale<br>value (2, 4,,<br>256) |

| 48            | TCKE2tmr1 | Delay from external clock edge to timer<br>increment |                | 2Tosc                                     | _    | 7Tos<br>c |       |                                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 12-6: GPIO PULL-UP RESISTOR RANGES

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Мах  | Units |

|-------------|------------------|------|------|------|-------|

|             |                  | GP0/ | /GP1 |      |       |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |

|             | 25               | 42K  | 48K  | 63K  | Ω     |

|             | 85               | 42K  | 49K  | 63K  | Ω     |

|             | 125              | 50K  | 55K  | 63K  | Ω     |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |

|             | 25               | 18K  | 20K  | 23K  | Ω     |

|             | 85               | 19K  | 22K  | 25K  | Ω     |

|             | 125              | 22K  | 24K  | 28K  | Ω     |

|             |                  | GI   | P3   |      |       |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |

|             | 25               | 343K | 414K | 532K | Ω     |

|             | 85               | 368K | 457K | 532K | Ω     |

|             | 125              | 431K | 504K | 593K | Ω     |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |

|             | 25               | 288K | 341K | 437K | Ω     |

|             | 85               | 306K | 371K | 448K | Ω     |

|             | 125              | 351K | 407K | 500K | Ω     |

\* These parameters are characterized but not tested.

# **PIC12C67X**

NOTES:

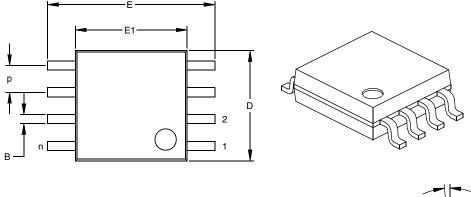

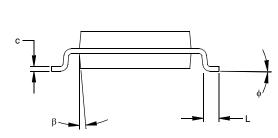

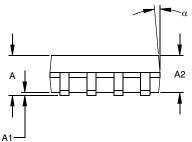

# 8-Lead Plastic Small Outline (SM) – Medium, 208 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |      |      |      | MILLIMETERS |      |      |  |

|--------------------------|-------|------|------|------|-------------|------|------|--|

| Dimension Limits         |       | MIN  | NOM  | MAX  | MIN         | NOM  | MAX  |  |

| Number of Pins           | n     |      | 8    |      |             | 8    |      |  |

| Pitch                    | р     |      | .050 |      |             | 1.27 |      |  |

| Overall Height           | А     | .070 | .075 | .080 | 1.78        | 1.97 | 2.03 |  |

| Molded Package Thickness | A2    | .069 | .074 | .078 | 1.75        | 1.88 | 1.98 |  |

| Standoff                 | A1    | .002 | .005 | .010 | 0.05        | 0.13 | 0.25 |  |

| Overall Width            | Е     | .300 | .313 | .325 | 7.62        | 7.95 | 8.26 |  |

| Molded Package Width     | E1    | .201 | .208 | .212 | 5.11        | 5.28 | 5.38 |  |

| Overall Length           | D     | .202 | .205 | .210 | 5.13        | 5.21 | 5.33 |  |

| Foot Length              | L     | .020 | .025 | .030 | 0.51        | 0.64 | 0.76 |  |

| Foot Angle               | ¢     | 0    | 4    | 8    | 0           | 4    | 8    |  |

| Lead Thickness           | С     | .008 | .009 | .010 | 0.20        | 0.23 | 0.25 |  |

| Lead Width               | В     | .014 | .017 | .020 | 0.36        | 0.43 | 0.51 |  |

| Mold Draft Angle Top     | α     | 0    | 12   | 15   | 0           | 12   | 15   |  |

| Mold Draft Angle Bottom  | β     | 0    | 12   | 15   | 0           | 12   | 15   |  |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

Drawing No. C04-056