Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

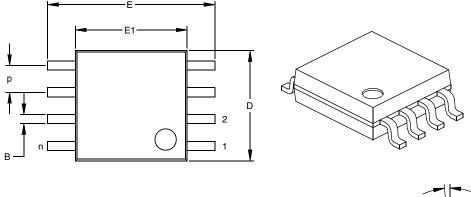

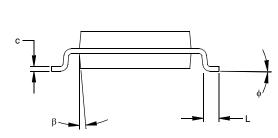

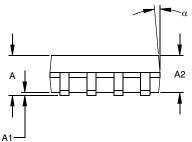

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671-04e-sm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

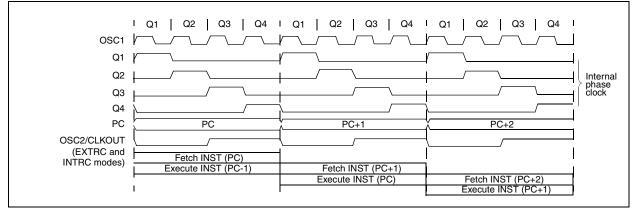

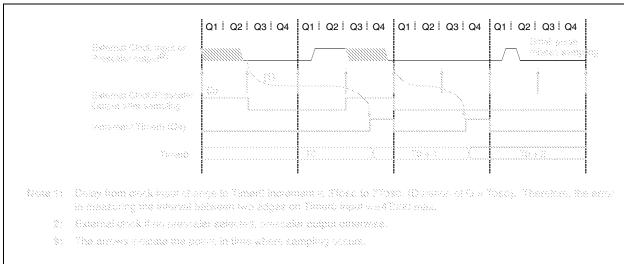

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

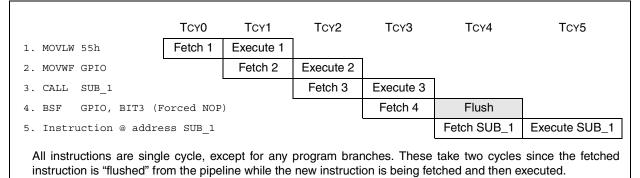

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

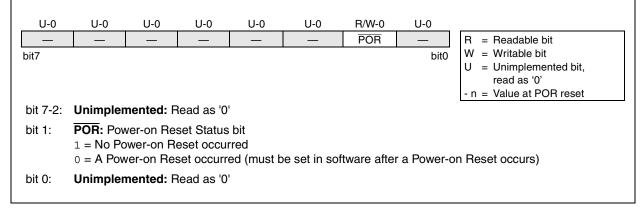

#### 4.2.2.6 PCON REGISTER

The Power Control (PCON) Register contains a flag bit to allow differentiation between a Power-on Reset (POR), an external MCLR Reset and a WDT Reset.

#### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

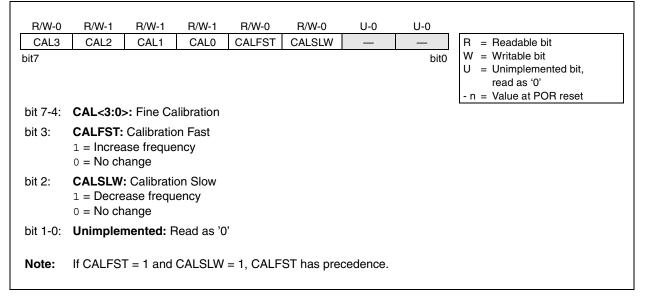

#### 4.2.2.7 OSCCAL REGISTER

The Oscillator Calibration (OSCCAL) Register is used to calibrate the internal 4 MHz oscillator. It contains four bits for fine calibration and two other bits to either increase or decrease frequency.

#### REGISTER 4-7: OSCCAL REGISTER (ADDRESS 8Fh)

### 6.0 EEPROM PERIPHERAL OPERATION

The PIC12CE673 and PIC12CE674 each have 16 bytes of EEPROM data memory. The EEPROM memory has an endurance of 1,000,000 erase/write cycles and a data retention of greater than 40 years. The EEPROM data memory supports a bi-directional 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), that are mapped to bit6 and bit7, respectively, of the GPIO register (SFR 06h). Unlike the GP0-GP5 that are connected to the I/O pins, SDA and SCL are only connected to the internal EEPROM peripheral. For most applications, all that is required is calls to the following functions:

| ;<br>; | Byte_Write: Byte write routine<br>Inputs: EEPROM Address EEADDR |

|--------|-----------------------------------------------------------------|

| ;      | EEPROM Data EEDATA                                              |

| ;      | Outputs: Return 01 in W if OK, else                             |

|        | return 00 in W                                                  |

| ;      |                                                                 |

| ;      | Read_Current: Read EEPROM at address                            |

| Cι     | urrently held by EE device.                                     |

| ;      | Inputs: NONE                                                    |

| ;      | Outputs: EEPROM Data EEDATA                                     |

| ;      | Return 01 in W if OK, else                                      |

|        | return 00 in W                                                  |

| ;      |                                                                 |

| ;      | Read Random: Read EEPROM byte at supplied                       |

| ad     | ddress                                                          |

| ;      | Inputs: EEPROM Address EEADDR                                   |

| ;      | Outputs: EEPROM Data EEDATA                                     |

| ;      | Return 01 in W if OK,                                           |

|        | else return 00 in W                                             |

|        |                                                                 |

The code for these functions is available on our web site (www.microchip.com). The code will be accessed by either including the source code FL67XINC.ASM or by linking FLASH67X.ASM. FLASH67X.INC provides external definition to the calling program.

#### 6.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the device.

For normal data transfer, SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

#### 6.0.2 SERIAL CLOCK

This SCL signal is used to synchronize the data transfer from and to the EEPROM.

#### 6.1 Bus Characteristics

The following **bus protocol** is to be used with the EEPROM data memory. In this section, the term "processor" is used to denote the portion of the PIC12C67X that interfaces to the EEPROM via software.

• Data transfer may be initiated only when the bus is not busy.

During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 6-3).

6.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

6.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

6.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### 6.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the available data EEPROM space.

#### 7.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is used as the clock source. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

# EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

#### TABLE 7-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6       | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|--------|-------------|---------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 | module's re | egister |       |       |       |       |       | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE        | TOIE    | INTE  | GPIE  | TOIF  | INTF  | GPIF  | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | GPPU   | INTEDG      | TOCS    | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111       | 1111 1111                       |

| 85h     | TRIS   | _      |             | TRIS5   | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0 | 11 1111         | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### 8.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5 TAD per 8-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal ADC RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu$ s. If the minimum TAD time of 1.6  $\mu$ s can not be obtained, TAD should be  $\leq 8 \ \mu$ s for preferred operation.

Table 8-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### 8.3 Configuring Analog Port Pins

The ADCON1 and TRIS Registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<2:0> bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channel will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN<3:0> pins) may cause the input buffer to consume current that is out of the devices specification.

#### TABLE 8-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock Source                           | (TAD)     | Device Frequency          |                           |                         |  |

|-------------------------------------------|-----------|---------------------------|---------------------------|-------------------------|--|

| Operation                                 | ADCS<1:0> | 4 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |

| 2Tosc                                     | 0 0       | 500 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |

| 8Tosc                                     | 01        | 2.0 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |

| 32Tosc                                    | 10        | 8.0 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <b>(3)</b>        |  |

| Internal ADC RC Oscillator <sup>(5)</sup> | 11        | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |

**Note 1:** The RC source has a typical TAD time of 4  $\mu$ s.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: While in RC mode, with device frequency above 1 MHz, conversion accuracy is out of specification.

**5:** For extended voltage devices (LC), please refer to Electrical Specifications section.

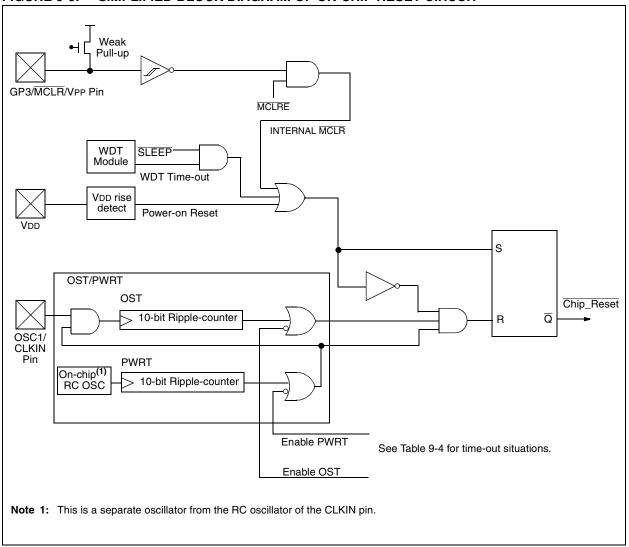

# 9.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC12C67X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC12C67X has a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The INTRC/EXTRC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 9.1 <u>Configuration Bits</u>

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h-3FFFh), which can be accessed only during programming.

# REGISTER 9-1: CONFIGURATION WORD

| CD -1-0-                                                                                                                                                                                                                                                                            |                                                                |                                                                |                                       |             |    |  |  |  |  |      | Address  | 2007h  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------|-------------|----|--|--|--|--|------|----------|--------|

| 1.861.05                                                                                                                                                                                                                                                                            | • Code                                                         |                                                                | ection k                              | hit nairs(1 | 1) |  |  |  |  | bit0 | 71001000 | 200711 |

| <br><b>CP&lt;1:0&gt;:</b> Code Protection bit pairs <sup>(1)</sup><br>11 = Code protection off<br>10 = Locations 400h through 7FEh code protected (do not use for PIC12C671 and PIC12CE673)<br>01 = Locations 200h through 7FEh code protected<br>00 = All memory is code protected |                                                                |                                                                |                                       |             |    |  |  |  |  |      |          |        |

| <br>MCLRE: Master Clear Reset Enable bit<br>1 = Master Clear Enabled<br>0 = Master Clear Disabled                                                                                                                                                                                   |                                                                |                                                                |                                       |             |    |  |  |  |  |      |          |        |

| <b>PWRTE:</b> Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                    |                                                                |                                                                |                                       |             |    |  |  |  |  |      |          |        |

| <b>WDTE:</b> W<br>1 = WDT<br>0 = WDT                                                                                                                                                                                                                                                | enabl                                                          | ed                                                             | ner En                                | able bit    |    |  |  |  |  |      |          |        |

| FOSC<2<br>111 = EX<br>110 = EX<br>101 = IN<br>100 = IN<br>011 = In<br>010 = HS<br>001 = XT<br>000 = LF                                                                                                                                                                              | KTRC,<br>KTRC,<br>TRC,<br>TRC,<br>Valid S<br>S Osci<br>F Oscil | Clocko<br>OSC2<br>Clocko<br>OSC2<br>electio<br>Ilator<br>lator | out on<br>is I/O<br>ut on 0<br>is I/O | OSC2        | S  |  |  |  |  |      |          |        |

FIGURE 9-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 10.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                     |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                            |

| Status Affected: | C, DC, Z                                                                                                                     |

| Encoding:        | 11 111x kkkk kkkk                                                                                                            |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and<br>the result is placed in the W regis-<br>ter. |

| Words:           | 1                                                                                                                            |

| Cycles:          | 1                                                                                                                            |

| Example          | ADDLW 0x15                                                                                                                   |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                              |

| ANDLW            | And Literal with W                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                 |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                          |

| Status Affected: | Z                                                                                                                        |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                        |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |

| Words:           | 1                                                                                                                        |

| Cycles:          | 1                                                                                                                        |

| Example          | ANDLW 0x5F                                                                                                               |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                          |

| ADDWF            | Add W and f                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                       |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                         |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                                |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. |

| Words:           | 1                                                                                                                                                                                |

| Cycles:          | 1                                                                                                                                                                                |

| Example          | ADDWF FSR, <b>0</b>                                                                                                                                                              |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                      |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |

| Status Affected: | Z                                                                                                                                                           |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                           |

| Cycles:          | 1                                                                                                                                                           |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                             |

| Operands:        | None                                                                                                                                                       |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow \underline{WD}T \text{ prescaler,} \\ 1 \rightarrow \underline{TO} \\ 1 \rightarrow PD \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                     |

| Encoding:        | 00 0000 0110 0100                                                                                                                                          |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br><u>prescaler of</u> the WDT. Status bits<br>TO and PD are set.                      |

| Words:           | 1                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                          |

| Example          | CLRWDT                                                                                                                                                     |

|                  | Before Instruction<br>WDT counter = ?                                                                                                                      |

|                  | After Instruction<br>WDT counter = 0x00<br>WDT prescaler= 0<br>TO = 1<br>PD = 1                                                                            |

| COMF             | Complement f                                                                                                                                               |

| Syntax:          | [label] COMF f,d                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                            |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                        |

| Status Affected: | Z                                                                                                                                                          |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'.    |

| Words:           | 1                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                          |

|                  |                                                                                                                                                            |

| Example          | COMF REG1,0                                                                                                                                                |

| DECF                                                                             | Decrement f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:                                                                          | [label] DECF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| Operands:                                                                        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Operation:                                                                       | (f) - 1 $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Status Affected:                                                                 | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Encoding:                                                                        | 00 0011 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Description:                                                                     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W regis-<br>ter. If 'd' is 1, the result is stored<br>back in register 'f'.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Words:                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Cycles:                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Example                                                                          | decf cnt, <b>1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|                                                                                  | Before Instruction<br>CNT = 0x01                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|                                                                                  | Z = 0<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|                                                                                  | CNT = 0x00<br>Z = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|                                                                                  | <b>_</b> - ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| DECFSZ                                                                           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Syntax:                                                                          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Operande                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Operands:                                                                        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Operation:                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|                                                                                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:                                      | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None<br>00 1011 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:                                                   | $d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:                                      | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle                                                                 |  |  |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction.                                                 |  |  |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction.<br>1<br>1(2)<br>HERE DECFSZ CNT, 1              |  |  |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction.<br>1<br>1(2)                                    |  |  |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction.<br>1<br>1(2)<br>HERE DECFSZ CNT, 1<br>GOTO LOOP |  |  |  |  |  |  |  |  |  |

| SWAPF            | Swap Ni                                                                                                                                                        | bbles in  | f    |            |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                     |           |      |            |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                                 | 27        |      |            |  |  |  |  |  |  |

| Operation:       | (f<3:0>) -<br>(f<7:4>) -                                                                                                                                       |           |      |            |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                           |           |      |            |  |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                             | 1110      | dfff | ffff       |  |  |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in W register. If 'd' is 1, the result is placed in register 'f'. |           |      |            |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                              |           |      |            |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                              |           |      |            |  |  |  |  |  |  |

| Example          | SWAPF                                                                                                                                                          | REG,      | 0    |            |  |  |  |  |  |  |

|                  | Before In                                                                                                                                                      | struction |      |            |  |  |  |  |  |  |

|                  | REG1 = 0xA5                                                                                                                                                    |           |      |            |  |  |  |  |  |  |

|                  | After Inst                                                                                                                                                     | ruction   |      |            |  |  |  |  |  |  |

|                  |                                                                                                                                                                | REG1<br>W | -    | xA5<br>x5A |  |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Encoding:        | 11 1010 kkkk kkkk                                                                                                            |  |  |  |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight bit lit-<br>eral 'k'. The result is placed in the<br>W register. |  |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Example:         | XORLW 0xAF                                                                                                                   |  |  |  |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                           |  |  |  |  |  |  |  |  |  |

|                  | W = 0xB5                                                                                                                     |  |  |  |  |  |  |  |  |  |

|                  | After Instruction                                                                                                            |  |  |  |  |  |  |  |  |  |

|                  | W = 0x1A                                                                                                                     |  |  |  |  |  |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                   |           |                                     |        |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------|--------|--|--|--|--|--|--|

| Syntax:          | [label]                                                                                                                                                                              | TRIS      | f                                   |        |  |  |  |  |  |  |

| Operands:        | $5 \leq f \leq 7$                                                                                                                                                                    |           |                                     |        |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow TF$                                                                                                                                                                 | RIS regis | ster f;                             |        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                 |           |                                     |        |  |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                   | 0000      | 0110                                | Offf   |  |  |  |  |  |  |

| Description:     | The instruction is supported for<br>code compatibility with the<br>PIC16C5X products. Since TRIS<br>registers are readable and writ-<br>able, the user can directly address<br>them. |           |                                     |        |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                    |           |                                     |        |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                    |           |                                     |        |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                      |           |                                     |        |  |  |  |  |  |  |

|                  | with futur                                                                                                                                                                           | re PIC12  | rd compa<br>C67X proo<br>struction. | ducts, |  |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |               |        |            |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|------------|--|--|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                   | XORWF         | f,d    |            |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |               |        |            |  |  |  |  |  |  |

| Operation:       | (W) .XOF                                                                                                                                                                    | $R.\;(f)\to($ | dest)  |            |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |               |        |            |  |  |  |  |  |  |

| Encoding:        | 00 0110 dfff ffff                                                                                                                                                           |               |        |            |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |               |        |            |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                           |               |        |            |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                           |               |        |            |  |  |  |  |  |  |

| Example          | XORWF                                                                                                                                                                       | REG           | 1      |            |  |  |  |  |  |  |

|                  | Before In                                                                                                                                                                   | struction     | 1      |            |  |  |  |  |  |  |

|                  |                                                                                                                                                                             | REG<br>W      | =<br>= | 0x/<br>0xl |  |  |  |  |  |  |

|                  | After Inst                                                                                                                                                                  | ruction       |        |            |  |  |  |  |  |  |

|                  |                                                                                                                                                                             | REG<br>W      | =<br>= | 0x<br>0xl  |  |  |  |  |  |  |

NOTES:

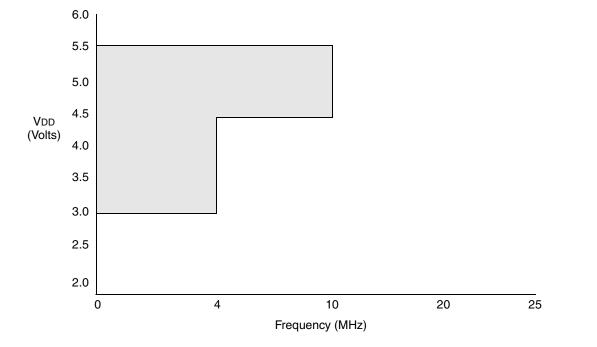

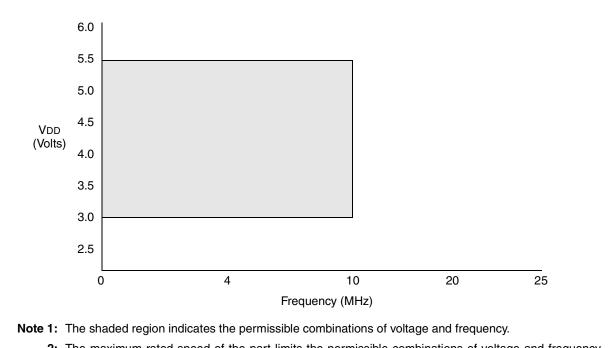

- Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

- **2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

FIGURE 12-2: PIC12C67X VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \le TA \le +70^{\circ}C$

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

#### 12.1 DC Characteristics: PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

| DC CH       | ARACTERISTICS                                                              |       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C &\leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ -40^{\circ}C &\leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ -40^{\circ}C &\leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |                    |          |                  |                                                                                                                                                      |  |  |  |

|-------------|----------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parm<br>No. | Characteristic                                                             | Sym   | Min                                                                                                                                                                                                                                                                                                                           | Typ <sup>(1)</sup> | Max      | Units            | Conditions                                                                                                                                           |  |  |  |

| D001        | Supply Voltage                                                             | Vdd   | 3.0                                                                                                                                                                                                                                                                                                                           |                    | 5.5      | V                |                                                                                                                                                      |  |  |  |

| D002        | RAM Data Retention<br>Voltage <sup>(2)</sup>                               | Vdr   |                                                                                                                                                                                                                                                                                                                               | 1.5*               |          | V                | Device in SLEEP mode                                                                                                                                 |  |  |  |

| D003        | VDD Start Voltage to ensure<br>Power-on Reset                              | VPOR  |                                                                                                                                                                                                                                                                                                                               | Vss                |          | V                | See section on Power-on Reset for details                                                                                                            |  |  |  |

| D004        | VDD Rise Rate to ensure<br>Power-on Reset                                  | SVDD  | 0.05*                                                                                                                                                                                                                                                                                                                         |                    |          | V/ms             | See section on Power-on Reset for details                                                                                                            |  |  |  |

| D010        | Supply Current <sup>(3)</sup>                                              | Idd   | —                                                                                                                                                                                                                                                                                                                             | 1.2                | 2.5      | mA               | Fosc = 4MHz, VDD = 3.0V<br>XT and EXTRC mode (Note 4)                                                                                                |  |  |  |

| D010C       |                                                                            |       | —                                                                                                                                                                                                                                                                                                                             | 1.2                | 2.5      | mA               | Fosc = 4MHz, VDD = 3.0V<br>INTRC mode (Note 6)                                                                                                       |  |  |  |

|             |                                                                            |       | —                                                                                                                                                                                                                                                                                                                             | 2.2                | 8        | mA               | Fosc = 10MHz, VDD = 5.5V<br>HS mode                                                                                                                  |  |  |  |

| D010A       |                                                                            |       | _                                                                                                                                                                                                                                                                                                                             | 19                 | 29       | μA               | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Commercial Temperature                                                                            |  |  |  |

|             |                                                                            |       | _                                                                                                                                                                                                                                                                                                                             | 19<br>32           | 37<br>60 | μΑ<br>μΑ         | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Industrial Temperature<br>Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Extended Temperature |  |  |  |

| D020        | Power-down Current <sup>(5)</sup>                                          | IPD   |                                                                                                                                                                                                                                                                                                                               | 0.25               | 6        | μA               | VDD = 3.0V, Commercial, WDT disabled                                                                                                                 |  |  |  |

| D021        |                                                                            |       | _                                                                                                                                                                                                                                                                                                                             | 0.25               | 7        | μA               | $V_{DD} = 3.0V$ , Industrial, WDT disabled                                                                                                           |  |  |  |

| D021B       |                                                                            |       | —                                                                                                                                                                                                                                                                                                                             | 2                  | 14       | μA               | VDD = 3.0V, Extended, WDT disabled                                                                                                                   |  |  |  |

|             |                                                                            |       | —                                                                                                                                                                                                                                                                                                                             | 0.5                | 8        | μA               | VDD = 5.5V, Commercial, WDT disabled                                                                                                                 |  |  |  |

|             |                                                                            |       | _                                                                                                                                                                                                                                                                                                                             | 0.8<br>3           | 9<br>16  | μA<br>μA         | VDD = 5.5V, Industrial, WDT disabled<br>VDD = 5.5V, Extended, WDT disabled                                                                           |  |  |  |