Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671-04i-p |

#### 1.0 GENERAL DESCRIPTION

The PIC12C67X devices are low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converter and EEPROM data memory (EEPROM on PIC12CE67X versions only).

All PIC® microcontrollers employ an advanced RISC architecture. The PIC12C67X microcontrollers have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches, which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC12C67X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC12C67X devices have 128 bytes of RAM, 16 bytes of EEPROM data memory (PIC12CE67X only), 5 I/O pins and 1 input pin. In addition a timer/counter is available. Also a 4-channel, high-speed, 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, (i.e., thermostat control, pressure sensing, etc.)

The PIC12C67X devices have special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. The Power-On Reset (POR), Power-up Timer (PWRT), and Oscillator Start-up Timer (OST) eliminate the need for external reset circuitry. There are five oscillator configurations to choose from, including INTRC precision internal oscillator mode and the power-saving LP (Low Power) oscillator mode. Power-saving SLEEP mode, Watchdog Timer and code protection features improve system cost, power and reliability. The SLEEP (power-down) feature provides a power-saving mode. The user can wake-up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

A UV erasable windowed package version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

#### 1.1 Applications

The PIC12C67X series fits perfectly in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The EPROM technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient, while the EEPROM data memory (PIC12CE67X only) technology allows for the changing of calibration factors and security codes. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC12C67X series very versatile even in areas where no microcontroller use has been considered before (i.e., timer functions, replacement of "glue" logic and PLD's in larger systems, coprocessor applications).

### 1.2 Family and Upward Compatibility

The PIC12C67X products are compatible with other members of the 14-bit PIC16CXXX families.

#### 1.3 <u>Development Support</u>

The PIC12C67X devices are supported by a full-featured macro assembler, a software simulator, an incircuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

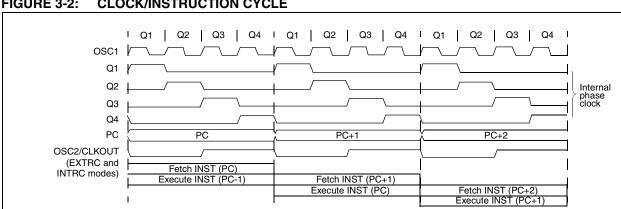

#### 3.1 **Clocking Scheme/Instruction Cycle**

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

#### 3.2 **Instruction Flow/Pipelining**

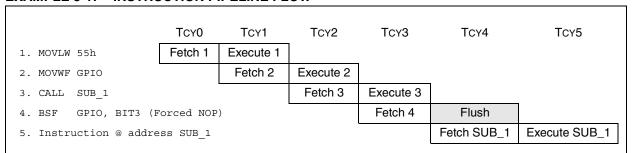

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

FIGURE 3-2: **CLOCK/INSTRUCTION CYCLE**

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetched instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

FIGURE 4-2: PIC12C67X REGISTER FILE MAP

|                             | IVIZAI                          |                                |                 |  |  |  |

|-----------------------------|---------------------------------|--------------------------------|-----------------|--|--|--|

| File<br>Address             | <b>;</b>                        |                                | File<br>Address |  |  |  |

| 00h                         | INDF <sup>(1)</sup>             | INDF <sup>(1)</sup>            | 80h             |  |  |  |

| 01h                         | TMR0                            | OPTION                         | 81h             |  |  |  |

| 02h                         | PCL                             | PCL                            | 82h             |  |  |  |

| 03h                         | STATUS                          | STATUS                         | 83h             |  |  |  |

| 04h                         | FSR                             | FSR                            | 84h             |  |  |  |

| 05h                         | GPIO                            | TRIS                           | 85h             |  |  |  |

| 06h                         | GI 10                           | 11110                          | 86h             |  |  |  |

| 07h                         |                                 |                                | 87h             |  |  |  |

| 08h                         |                                 |                                | 88h             |  |  |  |

| 09h                         |                                 |                                | 89h             |  |  |  |

| 0911<br>0Ah                 | PCLATH                          | PCLATH                         | 8Ah             |  |  |  |

| 0An<br>0Bh                  | INTCON                          | INTCON                         | 8Bh             |  |  |  |

| 0Ch                         | PIR1                            | PIE1                           | 8Ch             |  |  |  |

| 0Dh                         | FINI                            | FIET                           | 8Dh             |  |  |  |

| I                           |                                 | DCON                           |                 |  |  |  |

| 0Eh<br>0Fh                  |                                 | PCON                           | 8Eh             |  |  |  |

| · -                         |                                 | OSCCAL                         | 8Fh             |  |  |  |

| 10h                         |                                 |                                | 90h             |  |  |  |

| 11h                         |                                 |                                | 91h             |  |  |  |

| 12h                         |                                 |                                | 92h             |  |  |  |

| 13h                         |                                 |                                | 93h             |  |  |  |

| 14h                         |                                 |                                | 94h             |  |  |  |

| 15h                         |                                 |                                | 95h             |  |  |  |

| 16h                         |                                 |                                | 96h             |  |  |  |

| 17h                         |                                 |                                | 97h             |  |  |  |

| 18h                         |                                 |                                | 98h             |  |  |  |

| 19h                         |                                 |                                | 99h             |  |  |  |

| 1Ah                         |                                 |                                | 9Ah             |  |  |  |

| 1Bh                         |                                 |                                | 9Bh             |  |  |  |

| 1Ch                         |                                 |                                | 9Ch             |  |  |  |

| 1Dh                         |                                 |                                | 9Dh             |  |  |  |

| 1Eh                         | ADRES                           |                                | 9Eh             |  |  |  |

| 1Fh                         | ADCON0                          | ADCON1                         | 9Fh             |  |  |  |

| 20h                         |                                 | General<br>Purpose<br>Register | A0h             |  |  |  |

|                             | General                         | ricgister                      | BFh             |  |  |  |

|                             | Purpose                         |                                | C0h             |  |  |  |

|                             | Register                        |                                |                 |  |  |  |

|                             |                                 |                                | EFh             |  |  |  |

| 70h                         |                                 | Mapped                         | F0h             |  |  |  |

|                             |                                 | in Bank 0                      |                 |  |  |  |

| 7Fh <sup>[</sup>            | Bank 0                          | Bank 1                         | J FFh │         |  |  |  |

|                             | Danie                           | Dank i                         |                 |  |  |  |

|                             | Jnimplemented da                | ta memory locatio              | ns, read        |  |  |  |

| _                           | as '0'.<br>Not a physical regis | ster.                          |                 |  |  |  |

| 1. Not a physical register. |                                 |                                |                 |  |  |  |

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM.

The Special Function Registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

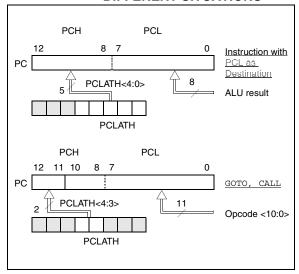

#### 4.3 PCL and PCLATH

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL Register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any reset, the PC is cleared. Figure 4-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A Computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC12C67X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

#### 4.4 Program Memory Paging

The PIC12C67X ignores both paging bits PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC12C67X is not recommended since this may affect upward compatibility with future products.

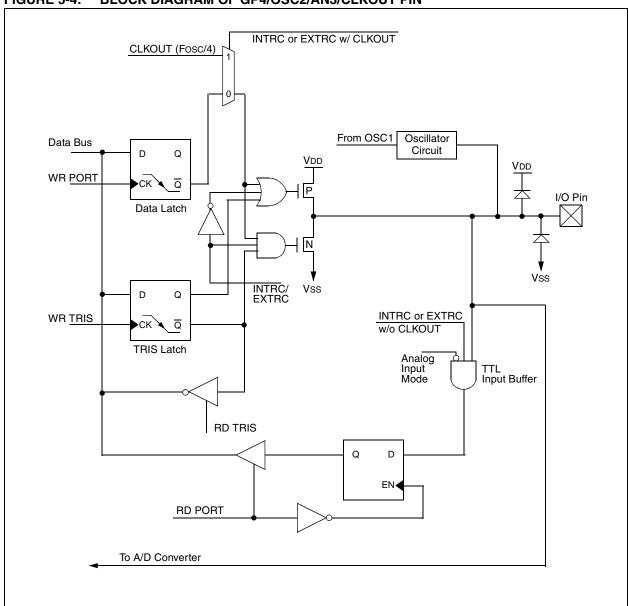

FIGURE 5-4: BLOCK DIAGRAM OF GP4/OSC2/AN3/CLKOUT PIN

#### 6.1.5 ACKNOWLEDGE

The EEPROM, when addressed, will generate an acknowledge after the reception of each byte. The processor must generate an extra clock pulse which is associated with this acknowledge bit.

**Note:** Acknowledge bits are not generated if an internal programming cycle is in progress.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. The processor must signal an end of data to the EEPROM by not generating an acknowledge bit on the last byte that has been clocked out of the EEPROM. In this case, the EEPROM must leave the data line HIGH to enable the processor to generate the STOP condition (Figure 6-4).

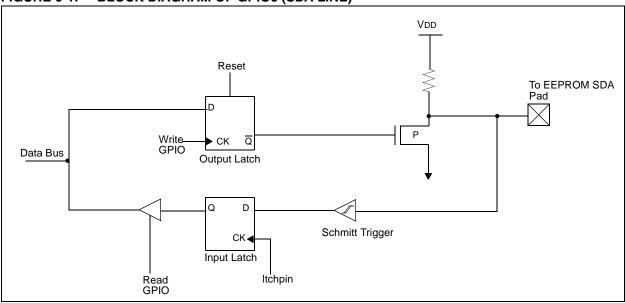

FIGURE 6-1: BLOCK DIAGRAM OF GPIO6 (SDA LINE)

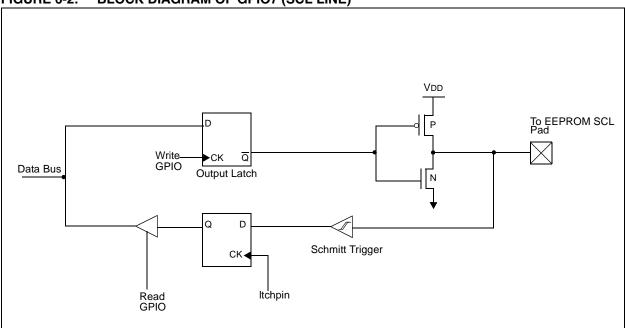

FIGURE 6-2: BLOCK DIAGRAM OF GPIO7 (SCL LINE)

### REGISTER 8-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-----|-----|-----|-----|-----|-------|-------|-------|

| _   |     | 1   | _   | -   | PCFG2 | PCFG1 | PCFG0 |

bit7 bit0

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

- n =Value at POR reset

bit 7-2: Unimplemented: Read as '0'

bit 1-0: PCFG<2:0>: A/D Port Configuration Control bits

| PCFG<2:0> | GP4 | GP2 | GP1  | GP0 | VREF |

|-----------|-----|-----|------|-----|------|

| 000(1)    | А   | А   | Α    | А   | VDD  |

| 001       | Α   | Α   | VREF | Α   | GP1  |

| 010       | D   | Α   | Α    | Α   | VDD  |

| 011       | D   | Α   | VREF | Α   | GP1  |

| 100       | D   | D   | Α    | Α   | VDD  |

| 101       | D   | D   | VREF | Α   | GP1  |

| 110       | D   | D   | D    | Α   | VDD  |

| 111       | D   | D   | D    | D   | VDD  |

A = Analog input

D = Digital I/O

Note 1: Value on reset.

2: Any instruction that reads a pin configured as an analog input will read a '0'.

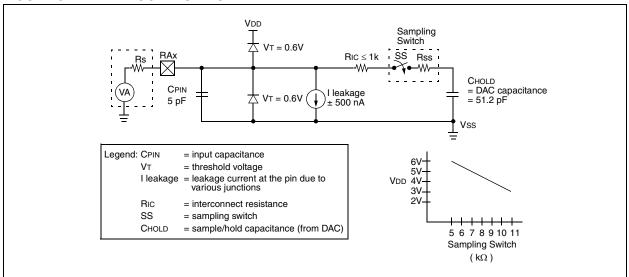

#### 8.1 A/D Sampling Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 8-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 8-2. The maximum recommended impedance for analog sources is 10  $k\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 8-1 may be used. This equation assumes that 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

### EQUATION 8-1: A/D MINIMUM CHARGING TIME

VHOLD = (VREF - (VREF/512)) • (1 -  $e^{(-Tc/CHOLD(Ric + Rss + Rs))}$ )

$Tc = -(51.2 pF)(1 k\Omega + Rss + Rs) ln(1/511)$

Example 8-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

$Rs = 10 \text{ k}\Omega$

1/2 LSb error

$VDD = 5V \rightarrow Rss = 7 \text{ k}\Omega$

Temp (system max.) = 50°C

VHOLD = 0 @ t = 0

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0 TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

# EXAMPLE 8-1: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

TACQ = Internal Amplifier Settling Time +

Holding Capacitor Charging Time +

Temperature Coefficient

TACQ =  $5 \mu s + Tc + [(Temp - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

Tc = -CHOLD (Ric + Rss + Rs) In(1/512)

$-51.2 \text{ pF} (1 \text{ k}\Omega + 7 \text{ k}\Omega + 10 \text{ k}\Omega) \ln(0.0020)$

-51.2 pF (18 kΩ) ln(0.0020)

-0.921 μs (-6.2146)

5.724 μs

TACQ =  $5 \mu s + 5.724 \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

$10.724~\mu s + 1.25~\mu s$

11.974 μs

#### FIGURE 8-2: ANALOG INPUT MODEL

#### 10.0 INSTRUCTION SET SUMMARY

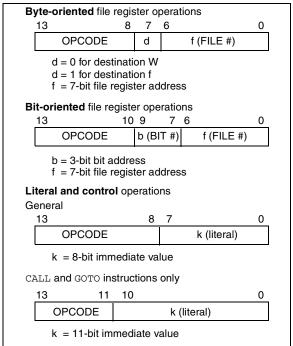

Each PIC12C67X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC12C67X instruction set summary in Table 10-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                              |

| х             | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                       |

| label         | Label name                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                    |

| PCLATH        | Program Counter High Latch                                                                                                                                         |

| GIE           | Global Interrupt Enable bit                                                                                                                                        |

| WDT           | Watchdog Timer/Counter                                                                                                                                             |

| TO            | Time-out bit                                                                                                                                                       |

| PD            | Power-down bit                                                                                                                                                     |

| dest          | Destination either the W register or the specified register file location                                                                                          |

| []            | Options                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                        |

| <>            | Register bit field                                                                                                                                                 |

| €             | In the set of                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 10-2 lists the instructions recognized by the MPASM assembler.

Figure 10-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC12C67X products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

### 10.1 <u>Special Function Registers as Source/Destination</u>

The PIC12C67X's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 10.1.1 STATUS AS DESTINATION

If an instruction writes to STATUS, the Z, C and DC bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF STATUS will clear register STATUS, and then set the Z bit leaving 0000 0100b in the register.

#### 10.1.2 TRIS AS DESTINATION

Bit 3 of the TRIS register always reads as a '1' since GP3 is an input only pin. This fact can affect some read-modify-write operations on the TRIS register.

#### 10.1.3 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

Read PC:  $PCL \rightarrow dest$

Write PCL: PCLATH  $\rightarrow$  PCH;

8-bit destination value → PCL

Read-Modify-Write: PCL→ ALU operand

PCLATH → PCH; 8-bit result → PCL

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 10.1.4 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write). The user should keep this in mind when operating on special function registers, such as ports.

TABLE 10-2: INSTRUCTION SET SUMMARY

| Mnemonic,  |        |                                                           |          | Status | Notes |      |      |            |       |

|------------|--------|-----------------------------------------------------------|----------|--------|-------|------|------|------------|-------|

| Operands   |        |                                                           |          | MSb    |       |      | LSb  | Affected   |       |

| BYTE-ORIE  | NTED I | FILE REGISTER OPERATIONS                                  | I        | I      |       |      |      |            |       |

| ADDWF      | f, d   | Add W and f                                               | 1        | 00     | 0111  | dfff | ffff | C,DC,Z     | 1,2   |

| ANDWF      | f, d   | AND W with f                                              | 1        | 0.0    | 0101  | dfff | ffff | Z          | 1,2   |

| CLRF       | f      | Clear f                                                   | 1        | 0.0    | 0001  | lfff | ffff | Z          | 2     |

| CLRW       | -      | Clear W                                                   | 1        | 00     | 0001  | 0000 | 0011 | Z          |       |

| COMF       | f, d   | Complement f                                              | 1        | 0.0    | 1001  | dfff | ffff | Z          | 1,2   |

| DECF       | f, d   | Decrement f                                               | 1        | 0.0    | 0011  | dfff | ffff | Z          | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0                                    | 1(2)     | 0.0    | 1011  | dfff | ffff |            | 1,2,3 |

| INCF       | f, d   | Increment f                                               | 1        | 0.0    | 1010  | dfff | ffff | Z          | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0                                    | 1(2)     | 0.0    | 1111  | dfff | ffff |            | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f                                     | 1        | 0.0    | 0100  | dfff | ffff | Z          | 1,2   |

| MOVF       | f, d   | Move f                                                    | 1        | 00     | 1000  | dfff | ffff | Z          | 1,2   |

| MOVWF      | f      | Move W to f                                               | 1        | 0.0    | 0000  | lfff | ffff |            |       |

| NOP        | -      | No Operation                                              | 1        | 0.0    | 0000  | 0xx0 | 0000 |            |       |

| RLF        | f, d   | Rotate Left f through Carry                               | 1        | 00     | 1101  | dfff | ffff | С          | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry                              | 1        | 0.0    | 1100  | dfff | ffff | С          | 1,2   |

| SUBWF      | f, d   | Subtract W from f                                         | 1        | 0.0    | 0010  | dfff | ffff | C,DC,Z     | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f                                         | 1        | 0.0    | 1110  | dfff | ffff |            | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f                                     | 1        | 00     | 0110  | dfff | ffff | Z          | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS                                     | I        | I      |       |      |      |            |       |

| BCF        | f, b   | Bit Clear f                                               | 1        | 01     | 00bb  | bfff | ffff |            | 1,2   |

| BSF        | f, b   | Bit Set f                                                 | 1        | 01     | 01bb  | bfff | ffff |            | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear                                 | 1 (2)    | 01     | 10bb  | bfff | ffff |            | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set                                   | 1 (2)    | 01     | 11bb  | bfff | ffff |            | 3     |

| LITERAL A  | ND CO  | NTROL OPERATIONS                                          | ı        | I      |       |      |      |            |       |

| ADDLW      | k      | Add literal and W                                         | 1        | 11     | 111x  | kkkk | kkkk | C,DC,Z     |       |

| ANDLW      | k      | AND literal with W                                        | 1        | 11     |       | kkkk |      | Z          |       |

| CALL       | k      | Call subroutine                                           | 2        | 10     | 0kkk  | kkkk | kkkk |            |       |

| CLRWDT     | -      | Clear Watchdog Timer                                      | 1        | 0.0    | 0000  | 0110 | 0100 | TO,PD      |       |

| GOTO       | k      | Go to address                                             | 2        | 10     | 1kkk  | kkkk | kkkk |            |       |

| IORLW      | k      | Inclusive OR literal with W                               | 1        | 11     | 1000  | kkkk | kkkk | Z          |       |

| MOVLW      | k      | Move literal to W                                         | 1        | 11     | 00xx  | kkkk | kkkk |            |       |

| RETFIE     | -      | Return from interrupt                                     | 2        | 00     | 0000  | 0000 | 1001 |            |       |

| RETLW      | k      | Return with literal in W                                  | 2        | 11     | 01xx  | kkkk | kkkk |            |       |

| RETURN     | -      | Return from Subroutine                                    | 2        | 00     | 0000  | 0000 | 1000 |            |       |

| SLEEP      | -      | Go into standby mode                                      | 1        | 00     | 0000  | 0110 | 0011 | TO,PD      |       |

| SUBLW      | k      | Subtract W from literal                                   | 1        | 11     | 110x  | kkkk | kkkk | C,DC,Z     |       |

| XORLW      | k      | Exclusive OR literal with W                               | 1        | 11     | 1010  | kkkk | kkkk | Z          |       |

|            |        | I/O register is modified as a function of itself ( i.e. M | <u> </u> | L      |       |      |      | that value |       |

Note 1: When an I/O register is modified as a function of itself (i.e., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| CLRWDT           | Clear Watchdog Timer                                               |                      |                          |                     |  |  |  |

|------------------|--------------------------------------------------------------------|----------------------|--------------------------|---------------------|--|--|--|

| Syntax:          | [label] CLRWDT                                                     |                      |                          |                     |  |  |  |

| Operands:        | None                                                               |                      |                          |                     |  |  |  |

| Operation:       | 00h → WDT<br>0 → <u>WD</u> T prescaler,<br>1 → <u>TO</u><br>1 → PD |                      |                          |                     |  |  |  |

| Status Affected: | TO, PD                                                             |                      |                          |                     |  |  |  |

| Encoding:        | 00                                                                 | 0000                 | 0110                     | 0100                |  |  |  |

| Description:     | CLRWDT i<br>Watchdoo<br>prescaler<br>TO and F                      | g Timer.<br>of the V | It also res<br>VDT. Stat | ets the             |  |  |  |

| Words:           | 1                                                                  |                      |                          |                     |  |  |  |

| Cycles:          | 1                                                                  |                      |                          |                     |  |  |  |

| Example          | CLRWDT                                                             |                      |                          |                     |  |  |  |

|                  | After Inst                                                         | WDT cou              | nter =                   | ?<br>0x00<br>0<br>1 |  |  |  |

| DECF             | Decreme                                                                                                                              | ent f    |                          |                        |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------|------------------------|--|--|--|--|

| Syntax:          | [ label ] DECF f,d                                                                                                                   |          |                          |                        |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                       | 27       |                          |                        |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$                                                                                                                | (dest)   |                          |                        |  |  |  |  |

| Status Affected: | Z                                                                                                                                    |          |                          |                        |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                    |          |                          |                        |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |          |                          |                        |  |  |  |  |

| Words:           | 1                                                                                                                                    |          |                          |                        |  |  |  |  |

| Cycles:          | 1                                                                                                                                    |          |                          |                        |  |  |  |  |

| Example          | DECF                                                                                                                                 | CNT,     | 1                        |                        |  |  |  |  |

|                  | After Inst                                                                                                                           | CNT<br>Z | <br> =<br> =<br> =<br> = | 0x01<br>0<br>0x00<br>1 |  |  |  |  |

| COMF             | Complement f                                                                                                                                   |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] COMF f,d                                                                                                                             |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                             |  |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                            |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                              |  |  |  |  |  |  |  |

| Encoding:        | 00 1001 dfff ffff                                                                                                                              |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                              |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                              |  |  |  |  |  |  |  |

| Example          | COMF REG1,0                                                                                                                                    |  |  |  |  |  |  |  |

|                  | Before Instruction  REG1 = 0x13  After Instruction  REG1 = 0x13  W = 0xEC                                                                      |  |  |  |  |  |  |  |

|                  |                                                                                                                                                |  |  |  |  |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] DECFSZ f,d                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 0, the next instruction, which is already fetched, is discarded. A NOP is executed instead making it a two cycle instruction. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1 GOTO LOOP CONTINUE • •                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                  | Before Instruction PC = address HERE  After Instruction CNT = CNT - 1 if CNT = 0, PC = address CONTINUE if CNT \neq 0,                                                                                                                                                                                     |  |  |  |  |  |  |  |

PC =

address HERE+1

## **PIC12C67X**

**NOTES:**

#### 11.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER®/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- · In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- · Device Programmers

- PRO MATE® II Universal Programmer

- PICSTART® Plus Entry-Level Prototype Programmer

- · Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ®

#### 11.1 <u>MPLAB Integrated Development</u> Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows®-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- · A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

#### 11.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

# 11.3 MPLAB-C17 and MPLAB-C18 C Compilers

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 11.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

#### 12.0 ELECTRICAL SPECIFICATIONS FOR PIC12C67X

#### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                                       | 40° to +125°C                  |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Storage temperature                                                                                                  | 65°C to +150°C                 |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                         | -0.3V to (VDD + 0.3V)          |

| Voltage on VDD with respect to Vss                                                                                   | 0 to +7.0V                     |

| Voltage on MCLR with respect to Vss (Note 2)                                                                         | 0 to +14V                      |

| Total power dissipation (Note 1)                                                                                     | 700 mW                         |

| Maximum current out of Vss pin                                                                                       | 200 mA                         |

| Maximum current into VDD pin                                                                                         | 150 mA                         |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                                                        | ± 20 mA                        |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                                                                       | ± 20 mA                        |

| Maximum output current sunk by any I/O pin                                                                           | 25 mA                          |

| Maximum output current sourced by any I/O pin                                                                        | 25 mA                          |

| Maximum current sunk by GPIO pins combined                                                                           | 100 mA                         |

| Maximum current sourced by GPIO pins combined                                                                        | 100 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VdD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD - VOH) | $x IOH$ + $\sum (VOI x IOL)$ . |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

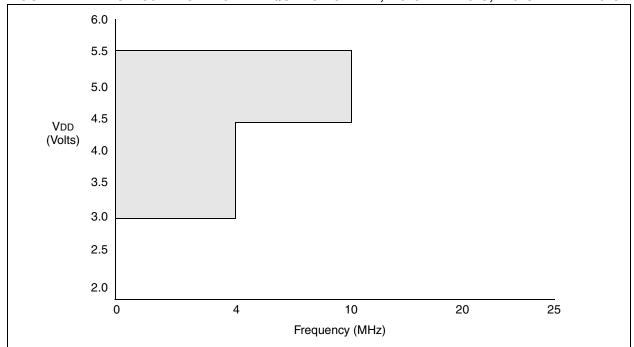

FIGURE 12-1: PIC12C67X VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}C \le TA < 0^{\circ}C$ ,  $+70^{\circ}C < TA \le +125^{\circ}C$

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

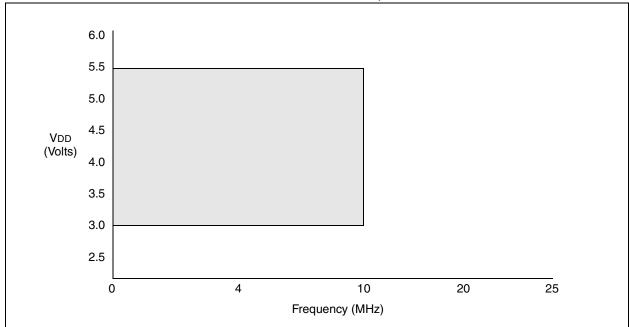

FIGURE 12-2: PIC12C67X VOLTAGE-FREQUENCY GRAPH, 0°C ≤ TA ≤ +70°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

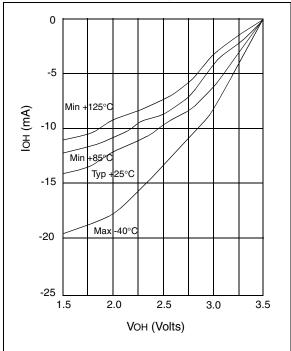

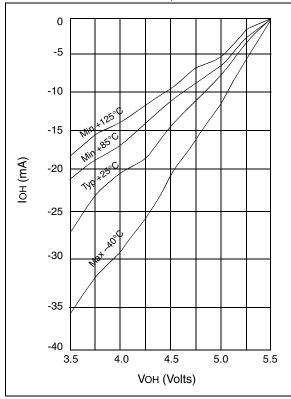

FIGURE 13-5: IOH vs. VOH, VDD = 3.5 V

FIGURE 13-6: IOH vs. VOH, VDD = 5.5 V

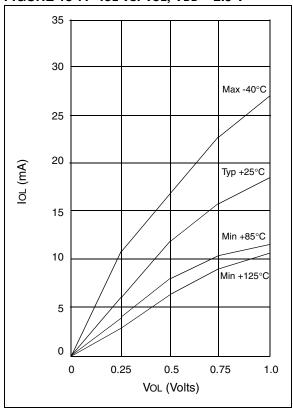

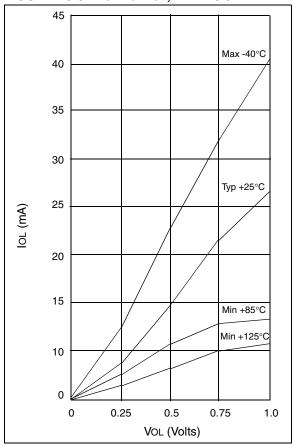

FIGURE 13-7: IOL vs. VOL, VDD = 2.5 V

FIGURE 13-8: IOL vs. VOL, VDD = 3.5 V

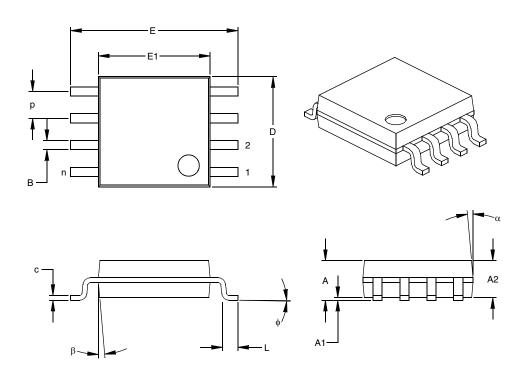

### 8-Lead Plastic Small Outline (SM) - Medium, 208 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | INCHES* |      |      | MILLIMETERS |      |      |      |

|--------------------------|---------|------|------|-------------|------|------|------|

| Dimension Limits         |         | MIN  | NOM  | MAX         | MIN  | NOM  | MAX  |

| Number of Pins           | n       |      | 8    |             |      | 8    |      |

| Pitch                    | р       |      | .050 |             |      | 1.27 |      |

| Overall Height           | Α       | .070 | .075 | .080        | 1.78 | 1.97 | 2.03 |

| Molded Package Thickness | A2      | .069 | .074 | .078        | 1.75 | 1.88 | 1.98 |

| Standoff                 | A1      | .002 | .005 | .010        | 0.05 | 0.13 | 0.25 |

| Overall Width            | Е       | .300 | .313 | .325        | 7.62 | 7.95 | 8.26 |

| Molded Package Width     | E1      | .201 | .208 | .212        | 5.11 | 5.28 | 5.38 |

| Overall Length           | D       | .202 | .205 | .210        | 5.13 | 5.21 | 5.33 |

| Foot Length              | L       | .020 | .025 | .030        | 0.51 | 0.64 | 0.76 |

| Foot Angle               | ф       | 0    | 4    | 8           | 0    | 4    | 8    |

| Lead Thickness           | С       | .008 | .009 | .010        | 0.20 | 0.23 | 0.25 |

| Lead Width               | В       | .014 | .017 | .020        | 0.36 | 0.43 | 0.51 |

| Mold Draft Angle Top     | α       | 0    | 12   | 15          | 0    | 12   | 15   |

| Mold Draft Angle Bottom  | β       | 0    | 12   | 15          | 0    | 12   | 15   |

<sup>\*</sup>Controlling Parameter

Notes

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

Drawing No. C04-056

#### **INDEX**

| A                                        |           |

|------------------------------------------|-----------|

| A/D                                      |           |

| Accuracy/Error                           | 51        |

| ADCON0 Register                          | 45        |

| ADIF bit                                 |           |

| Analog Input Model Block Diagram         |           |

| Analog-to-Digital Converter              |           |

| Configuring Analog Port Pins             |           |

| Configuring the Interrupt                |           |

| Configuring the Module                   |           |

| Connection Considerations                |           |

| Conversion Clock                         |           |

| Conversions                              |           |

| Converter Characteristics                |           |

| Delays                                   |           |

| Effects of a Reset                       |           |

| Equations Flowchart of A/D Operation     |           |

| GO/DONE bit                              |           |

| Internal Sampling Switch (Rss) Impedence | 47<br>40  |

| Operation During Sleep                   |           |

| Sampling Requirements                    |           |

| Sampling Time                            |           |

| Source Impedence                         |           |

| Time Delays                              |           |

| Transfer Function                        |           |

| Absolute Maximum Ratings                 |           |

| ADDLW Instruction                        |           |

| ADDWF Instruction                        | 72        |

| ADIE bit                                 | 18        |

| ADIF bit                                 | 19        |

| ADRES Register13                         | 3, 45, 47 |

| ALU                                      | 7         |

| ANDLW Instruction                        | 72        |

| ANDWF Instruction                        | 72        |

| Application Notes                        |           |

| AN546                                    |           |

| AN556                                    | 22        |

| Architecture                             |           |

| Harvard                                  |           |

| Overview                                 |           |

| von Neumann                              | 7         |

| Assembler                                | 00        |

| MPASM Assembler                          | 83        |

| В                                        |           |

| BOE Leaders Page                         | 70        |

Bit Manipulation ......70

Analog Input Model

48

On-Chip Reset Circuit

57

Timer0

39

Timer0/WDT Prescaler

42

Watchdog Timer

65

BSF Instruction

73

BTFSC Instruction

73

BTFSS Instruction

74

Block Diagrams

| C Dit                                  |          |

|----------------------------------------|----------|

| CAL0 bit                               |          |

| CAL1 bit                               | 21       |

| CAL2 bit                               |          |

| CAL3 bit                               | 21       |

| CALFST bit                             | 21       |

| CALL Instruction                       | 74       |

| CALSLW bit                             |          |

| Carry bit                              |          |

| Clocking Scheme                        | 10       |

| CLRF Instruction                       |          |

| CLRW Instruction                       |          |

| CLRWDT Instruction                     | 75       |

| Code Examples                          |          |

| Changing Prescaler (Timer0 to WDT)     | 43       |

| Changing Prescaler (WDT to Timer0)     |          |

| Indirect Addressing                    |          |

| Code Protection                        | . 53, 67 |

| COMF Instruction                       |          |

| Computed GOTO                          |          |

| Configuration Bits                     |          |

| D                                      |          |

| _                                      |          |

| DC and AC Characteristics              |          |

| DC bit                                 | 15       |

| DC Characteristics                     |          |

| PIC12C671/672, PIC12CE673/674          |          |

| PIC12LC671/672, PIC12LCE673/674        |          |

| DECF Instruction                       |          |

| DECFSZ Instruction                     |          |

| Development Support                    |          |

| Digit Carry bit                        |          |

| Direct Addressing                      | 23       |

| E                                      |          |

| EEPROM Peripheral Operation            | 33       |

| Electrical Characteristics - PIC12C67X | 89       |

| Errata                                 |          |

| External Brown-out Protection Circuit  |          |

| External Power-on Reset Circuit        |          |

| F                                      |          |

| •                                      |          |

| Family of Devices                      |          |

| Features                               | 1        |

| FSR Register 13                        | , 14, 23 |

| G                                      |          |

| General Description                    | 3        |

| GIE bit                                |          |

| GOTO Instruction                       |          |

| GPIF bit                               |          |

| GPIO                                   |          |

| GPIO Register                          |          |

| GPPU bit                               |          |

|                                        |          |

### **PIC16XXXXXX FAMILY**

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support