Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671-04i-sm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 PIC12C67X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC12C67X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For example, the PIC12C67X device "type" is indicated in the device number:

- 1. **C**, as in PIC12**C**671. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC12LC671. These devices have EPROM type memory and operate over an extended voltage range.

- 3. **CE**, as in PIC12**CE**674. These devices have EPROM type memory, EEPROM data memory and operate over the standard voltage range.

- 4. **LCE**, as in PIC12**LCE**674. These devices have EPROM type memory, EEPROM data memory and operate over an extended voltage range.

## 2.1 UV Erasable Devices

The UV erasable version, offered in windowed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> programmers both support the PIC12C67X. Third party programmers also are available; refer to the Microchip Third Party Guide for a list of sources.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 <u>Quick-Turn-Programming (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.4 <u>Serialized Quick-Turn Programming</u> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

#### 4.2.2.1 STATUS REGISTER

The STATUS Register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS Register, because these instructions do not affect the Z, C or DC bits from the STATUS Register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: Bits IRP and RP1 (STATUS<7:6>) are not used by the PIC12C67X and should be maintained clear. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

|             | Reserved                                                                                                                                                                                                                                                          | R/W-0 | R-1        | R-1 | R/W-x | R/W-x | R/W-x     |                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-----|-------|-------|-----------|-----------------------------------------------------------------------------------------------------------|

| IRP<br>bit7 | RP1                                                                                                                                                                                                                                                               | RP0   | TO         | PD  | Z     | DC    | C<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:      |                                                                                                                                                                                                                                                                   |       |            |     |       |       |           |                                                                                                           |

| bit 6-5:    | <b>RP&lt;1:0&gt;:</b> Register Bank Select bits (used for direct addressing) 11 = Bank 3 (180h - 1FFh) 10 = Bank 2 (100h - 17Fh) 01 = Bank 1 (80h - FFh) 00 = Bank 0 (00h - 7Fh) Each bank is 128 bytes. The RP1 bit is reserved; always maintain this bit clear. |       |            |     |       |       |           |                                                                                                           |

| bit 4:      | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                   |       |            |     |       |       |           |                                                                                                           |

| bit 3:      | <b>PD:</b> Power-down bit 1 = After power-up or by the CLRWDT instruction 0 = By execution of the SLEEP instruction                                                                                                                                               |       |            |     |       |       |           |                                                                                                           |

| bit 2:      | <b>Z:</b> Zero bit<br>1 = The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not zero                                                                                                                |       |            |     |       |       |           |                                                                                                           |

| bit 1:      | <b>DC:</b> Digit Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result               |       |            |     |       |       |           |                                                                                                           |

| bit 0:      | <b>C:</b> Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)<br>1 = A carry-out from the most significant bit of the result occurred<br>0 = No carry-out from the most significant bit of the result occurred                                             |       |            |     |       |       |           |                                                                                                           |

| Note:       | ond ope                                                                                                                                                                                                                                                           |       | rotate (RR |     |       |       |           | the two's complement of the sec-<br>either the high or low order bit of                                   |

#### **REGISTER 4-1:** STATUS REGISTER (ADDRESS 03h, 83h)

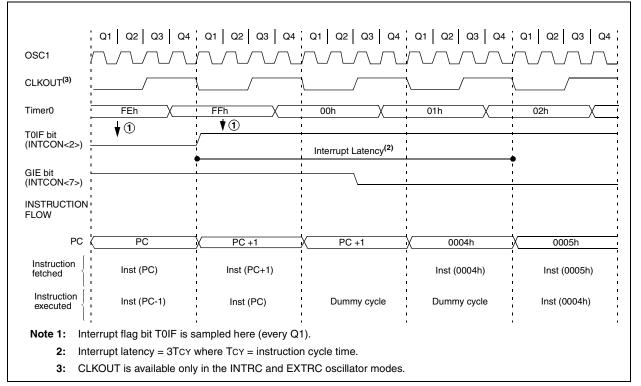

## 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 Register overflow, GPIO port change and external GP2/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

## REGISTER 4-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0                                                                                                                                                                                                    | R/W-0       | R/W-0      | R/W-0       | R/W-0     | R/W-0 | R/W-x        |                                                                                                           |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-----------|-------|--------------|-----------------------------------------------------------------------------------------------------------|

| GIE<br>bit7 | PEIE                                                                                                                                                                                                     | TOIE        | INTE       | GPIE        | TOIF      | INTF  | GPIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:      | <b>GIE:</b> Glob<br>1 = Enabl<br>0 = Disab                                                                                                                                                               | es all un-r | nasked in  |             |           |       |              |                                                                                                           |

| bit 6:      | PEIE: Per<br>1 = Enabl<br>0 = Disab                                                                                                                                                                      | es all un-r | nasked pe  | ripheral ir | iterrupts |       |              |                                                                                                           |

| bit 5:      | <b>TOIE:</b> TMI<br>1 = Enabl<br>0 = Disab                                                                                                                                                               | es the TM   | R0 interru | ıpt         | bit       |       |              |                                                                                                           |

| bit 4:      | INTE: INT External Interrupt Enable bit<br>1 = Enables the external interrupt on GP2/INT/T0CKI/AN2 pin<br>0 = Disables the external interrupt on GP2/INT/T0CKI/AN2 pin                                   |             |            |             |           |       |              |                                                                                                           |

| bit 3:      | <b>GPIE:</b> GPIO Interrupt on Change Enable bit<br>1 = Enables the GPIO Interrupt on Change<br>0 = Disables the GPIO Interrupt on Change                                                                |             |            |             |           |       |              |                                                                                                           |

| bit 2:      | <b>TOIF:</b> TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                    |             |            |             |           |       |              |                                                                                                           |

| bit 1:      | INTF: INT External Interrupt Flag bit<br>1 = The external interrupt on GP2/INT/T0CKI/AN2 pin occurred (must be cleared in software)<br>0 = The external interrupt on GP2/INT/T0CKI/AN2 pin did not occur |             |            |             |           |       |              |                                                                                                           |

| bit 0:      | <ul> <li>GPIF: GPIO Interrupt on Change Flag bit</li> <li>1 = GP0, GP1 or GP3 pins changed state (must be cleared in software)</li> <li>0 = Neither GP0, GP1 nor GP3 pins have changed state</li> </ul>  |             |            |             |           |       |              |                                                                                                           |

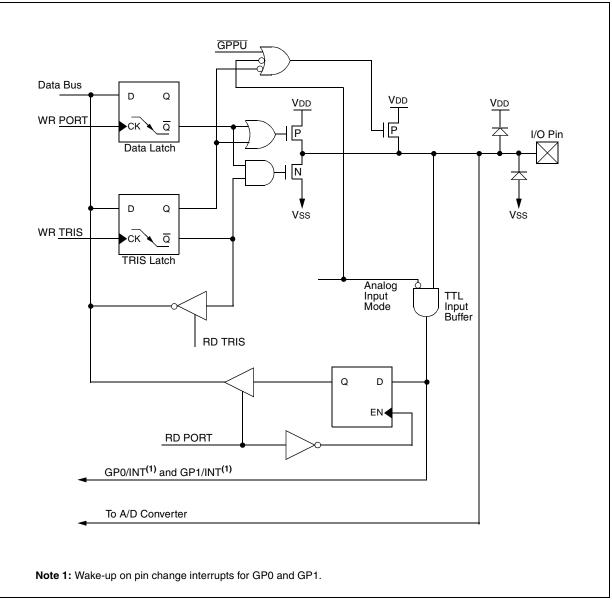

## 5.0 I/O PORT

As with any other register, the I/O register can be written and read under program control. However, read instructions (i.e., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance), since the I/O control registers are all set.

## 5.1 <u>GPIO</u>

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP<5:0>). Bits 6 and 7 (SDA and SCL. respectively) are used by the EEPROM peripheral on the PIC12CE673/674. Refer to Section 6.0 and Appendix B for use of SDA and SCL. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during port read. Pins GP0, GP1 and GP3 can be configured with weak pull-ups and also with interrupt-on-change. The interrupt on change and weak pull-up functions are not pin selectable. If pin 4, (GP3), is configured as MCLR, a weak pull-up is always on. Interrupt-on-change for this pin is not set and GP3 will read as '0'. Interrupt-onchange is enabled by setting bit GPIE, INTCON<3>. Note that external oscillator use overrides the GPIO functions on GP4 and GP5.

## 5.2 TRIS Register

This register controls the data direction for GPIO. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3, which is input only and its TRIS bit will always read as '1', while GP6 and GP7 TRIS bits will read as '0'.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

Upon reset, the TRIS Register is all '1's, making all pins inputs.

TRIS for pins GP4 and GP5 is forced to a '1' where appropriate. Writes to TRIS <5:4> will have an effect in EXTRC and INTRC oscillator modes only. When GP4 is configured as CLKOUT, changes to TRIS<4> will have no effect.

## 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1 through Figure 5-5. All port pins, except GP3, which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (i.e., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

Port pins GP6 (SDA) and GP7 (SCL) are used for the serial EEPROM interface on the PIC12CE673/674. These port pins are not available externally on the package. Users should avoid writing to pins GP6 (SDA) and GP7 (SCL) when not communicating with the serial EEPROM memory. Please see Section 6.0, EEPROM Peripheral Operation, for information on serial EEPROM communication.

Note: On a Power-on Reset, GP0, GP1, GP2 and GP4 are configured as analog inputs and read as '0'.

## FIGURE 5-1: BLOCK DIAGRAM OF GP0/AN0 AND GP1/AN1/VREF PIN

# **PIC12C67X**

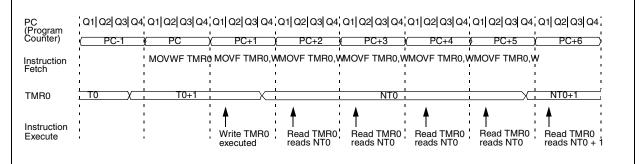

## FIGURE 7-4: TIMER0 INTERRUPT TIMING

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

# EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

#### TABLE 7-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6       | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|--------|-------------|---------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 | module's re | egister |       |       |       |       |       | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE        | TOIE    | INTE  | GPIE  | TOIF  | INTF  | GPIF  | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | GPPU   | INTEDG      | TOCS    | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111       | 1111 1111                       |

| 85h     | TRIS   | _      |             | TRIS5   | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0 | 11 1111         | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

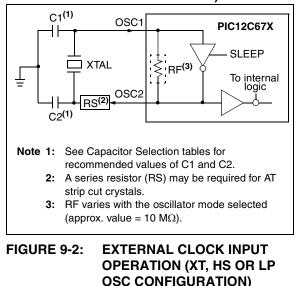

## 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC12C67X can be operated in seven different oscillator modes. The user can program three configuration bits (Fosc<2:0>) to select one of these seven modes:

- LP: Low Power Crystal

- HS: High Speed Crystal/Resonator

- XT: Crystal/Resonator

- INTRC\*: Internal 4 MHz Oscillator

- EXTRC\*: External Resistor/Capacitor

\*Can be configured to support CLKOUT

# 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

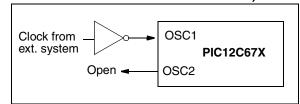

In XT, HS or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 9-1). The PIC12C67X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, HS or LP modes, the device can have an external clock source drive the GP5/OSC1/CLKIN pin (Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT, HS OR LP OSC CONFIGURATION)

#### TABLE 9-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C67X

| Osc<br>Type        | Resonator<br>Freq | Cap. Range<br>C1          | Cap. Range |

|--------------------|-------------------|---------------------------|------------|

| XT                 | 455 kHz           | 22-100,pF                 | 22-100 pF  |

|                    | 2.0 MHz           | 15-68 pf                  | レ15-68 pF  |

|                    | 4.0 MHz           | ~ { <b>1</b> ,5+68 pf ~ ~ | 15-68 pF   |

| HS                 | 4.0-MHX           | \ <b>15-68</b> pF         | 15-68 pF   |

|                    | 8,0 MHz           | 10-68 pF                  | 10-68 pF   |

| $\widehat{\Omega}$ | tp:0 MHz          | 10-22 pF                  | 10-22 pF   |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR - PIC12C67X

| - 1012007A      |                       |                     |                        |  |  |

|-----------------|-----------------------|---------------------|------------------------|--|--|

| Osc<br>Type     | Resonator<br>Freq     | Cap. Range<br>C1    | Cap. Range<br>C2       |  |  |

| LP              | 32 kHz <sup>(1)</sup> | 15 pF               | 15 pF 🚽                |  |  |

|                 | 100 kHz               | 15-30 pF            | 30-47 p⊄               |  |  |

|                 | 200 kHz               | 15-30 pF            | 15-83 pF               |  |  |

| XT              | 100 kHz               | 15-30 pF            | 200-300 pF             |  |  |

|                 | 200 kHz               | 15-30 pE            | 100-200 pF             |  |  |

|                 | 455 kHz               | 15-30 pF            | <sup>™</sup> 15-100 pF |  |  |

|                 | 1 MHz 🔨               | 1,15-30.pF          | 15-30 pF               |  |  |

|                 | 2, MAHz ∖∖            | \ <b>∖</b> 19-30 pF | 15-30 pF               |  |  |

|                 | (AMHz)                | 15-47 pF            | 15-47 pF               |  |  |

| HS              | 4 DAHz                | 15-30 pF            | 15-30 pF               |  |  |

| $(\mathcal{O})$ | 😕 🖲 MHz               | 15-30 pF            | 15-30 pF               |  |  |

| VZ V            | 10 MHz                | 15-30 pF            | 15-30 pF               |  |  |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a pre-packaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Pre-packaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with parallel resonance or one with series resonance.

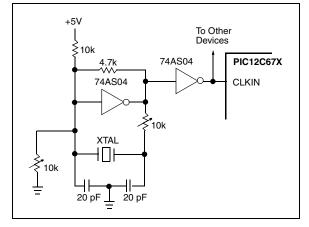

Figure 9-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

#### FIGURE 9-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

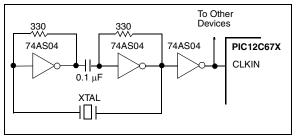

Figure 9-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 9-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

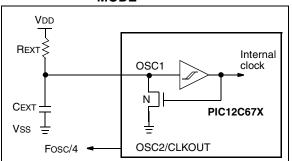

## 9.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 9-5 shows how the R/C combination is connected to the PIC12C67X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable or stop completely. For very high REXT values (i.e., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

#### FIGURE 9-5: EXTERNAL RC OSCILLATOR MODE

## 9.8 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input, if enabled, should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on GPIO should be considered.

The  $\overline{\text{MCLR}}$  pin, if enabled, must be at a logic high level (VIHMC).

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. GP2/INT interrupt, interrupt GPIO port change or some Peripheral Interrupts.

External MCLR Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device reset. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupt can wake the device from SLEEP:

1. A/D conversion (when A/D clock source is RC).

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 9.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

NOTES:

#### 10.1 <u>Special Function Registers as</u> <u>Source/Destination</u>

The PIC12C67X's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 10.1.1 STATUS AS DESTINATION

If an instruction writes to STATUS, the Z, C and DC bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF STATUS will clear register STATUS, and then set the Z bit leaving 0000 0100b in the register.

#### 10.1.2 TRIS AS DESTINATION

Bit 3 of the TRIS register always reads as a '1' since GP3 is an input only pin. This fact can affect some read-modify-write operations on the TRIS register.

### 10.1.3 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCL \to dest$                                                                               |

|--------------------|----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                       |

| Read-Modify-Write: | PCL $\rightarrow$ ALU operand<br>PCLATH $\rightarrow$ PCH;<br>8-bit result $\rightarrow$ PCL |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 10.1.4 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write). The user should keep this in mind when operating on special function registers, such as ports.

| RETURN             | Return from Subroutine                                                                                                | RRF              | Rotate Right f through Carry                                                                                                                                                                          |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:            | [label] RETURN                                                                                                        | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                              |

| Operands:          | None                                                                                                                  | Operands:        | $0 \le f \le 127$                                                                                                                                                                                     |

| Operation:         | $TOS \rightarrow PC$                                                                                                  | •                | d ∈ [0,1]                                                                                                                                                                                             |

| Status Affected:   | None                                                                                                                  | Operation:       | See description below                                                                                                                                                                                 |

| Encoding:          | 00 0000 0000 1000                                                                                                     | Status Affected: | C                                                                                                                                                                                                     |

| Description:       | Return from subroutine. The stack                                                                                     | Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                     |

|                    | is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two cycle<br>instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg- |

| Words:             | 1                                                                                                                     |                  | ister 'f'.                                                                                                                                                                                            |

| Cycles:<br>Example | 2<br>RETURN                                                                                                           |                  | C Register f                                                                                                                                                                                          |

|                    | After Interrupt                                                                                                       | Words:           | 1                                                                                                                                                                                                     |

|                    | PC = TOS                                                                                                              | Cycles:          | 1                                                                                                                                                                                                     |

|                    |                                                                                                                       | Example          | rrf <b>REG1</b> ,<br>0                                                                                                                                                                                |

|                    |                                                                                                                       |                  | Before Instruction                                                                                                                                                                                    |

|                    |                                                                                                                       |                  | REG1 = 1110 0110<br>C = 0                                                                                                                                                                             |

|                    |                                                                                                                       |                  | After Instruction<br>REG1 = 1110 0110                                                                                                                                                                 |

|                    |                                                                                                                       |                  | W = 0111 0011                                                                                                                                                                                         |

|                    |                                                                                                                       |                  | <b>C</b> = 0                                                                                                                                                                                          |

| RLF              | Rotate Left f through Carry                                                                  | SLEEP            |                                                                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                     | Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                           | Operands:        | None                                                                                                                                                                                                                               |

| Operation:       | See description below                                                                        | Operation:       | $00h \rightarrow WDT,$                                                                                                                                                                                                             |

| Status Affected: | С                                                                                            |                  | $0 \rightarrow \underline{WDT}$ prescaler,<br>1 $\rightarrow \underline{TO}$ ,                                                                                                                                                     |

| Encoding:        | 00 1101 dfff ffff                                                                            |                  | $0 \rightarrow PD$                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are                                                             | Status Affected: |                                                                                                                                                                                                                                    |

| -                | rotated one bit to the left through the Carry Flag. If 'd' is 0, the result                  | Encoding:        | 00 0000 0110 0011                                                                                                                                                                                                                  |

| is<br>1,         | is placed in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. | Description:     | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |

| Words:           | 1                                                                                            | Words:           | 1                                                                                                                                                                                                                                  |

| Cycles:          | 1                                                                                            | Cycles:          | 1                                                                                                                                                                                                                                  |

| Example          | RLF REG1,0                                                                                   | Example:         | SLEEP                                                                                                                                                                                                                              |

|                  | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                         |                  |                                                                                                                                                                                                                                    |

## 12.0 ELECTRICAL SPECIFICATIONS FOR PIC12C67X

## Absolute Maximum Ratings †

| <b>3</b>                                                                                                       |                                    |

|----------------------------------------------------------------------------------------------------------------|------------------------------------|

| Ambient temperature under bias                                                                                 | 40° to +125°C                      |

| Storage temperature                                                                                            | –65°C to +150°C                    |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | –0.3V to (VDD + 0.3V)              |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.0V                         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                               | 700 mW                             |

| Maximum current out of Vss pin                                                                                 | 200 mA                             |

| Maximum current into VDD pin                                                                                   |                                    |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                   | ±20 mA                             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                 |                                    |

| Maximum output current sunk by any I/O pin                                                                     | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                  | 25 mA                              |

| Maximum current sunk by GPIO pins combined                                                                     | 100 mA                             |

| Maximum current sourced by GPIO pins combined                                                                  | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VO | OH) x IOH} + $\Sigma$ (VOI x IOL). |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

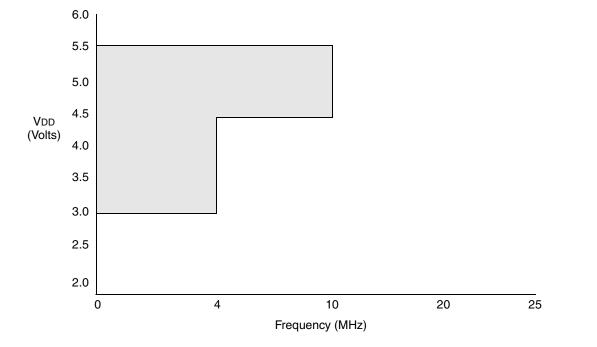

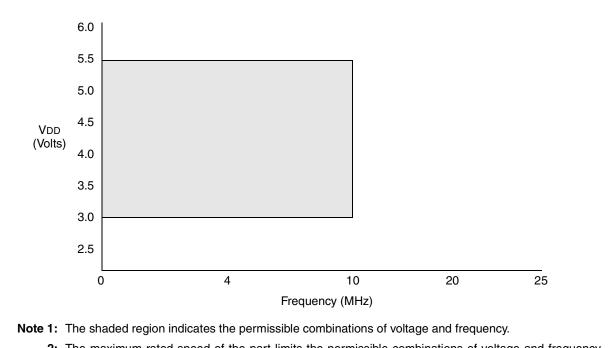

- Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

- **2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

FIGURE 12-2: PIC12C67X VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \le TA \le +70^{\circ}C$

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

## 12.1 DC Characteristics: PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

| DC CH                 | ARACTERISTICS                                                              |               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |              |          |                                                                                                                     |  |  |  |

|-----------------------|----------------------------------------------------------------------------|---------------|------------------------------------------------------|--------------------|--------------|----------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parm<br>No.           | Characteristic                                                             | Sym           | Min                                                  | Typ <sup>(1)</sup> | Max          | Units    | Conditions                                                                                                          |  |  |  |

| D001                  | Supply Voltage                                                             | Vdd           | 3.0                                                  |                    | 5.5          | V        |                                                                                                                     |  |  |  |

| D002                  | RAM Data Retention<br>Voltage <sup>(2)</sup>                               | Vdr           |                                                      | 1.5*               |              | V        | Device in SLEEP mode                                                                                                |  |  |  |

| D003                  | VDD Start Voltage to ensure<br>Power-on Reset                              | VPOR          |                                                      | Vss                |              | V        | See section on Power-on Reset for details                                                                           |  |  |  |

| D004                  | VDD Rise Rate to ensure<br>Power-on Reset                                  | SVDD          | 0.05*                                                |                    |              | V/ms     | See section on Power-on Reset for details                                                                           |  |  |  |

| D010                  | Supply Current <sup>(3)</sup>                                              | Idd           | —                                                    | 1.2                | 2.5          | mA       | Fosc = 4MHz, VDD = 3.0V<br>XT and EXTRC mode (Note 4)                                                               |  |  |  |

| D010C                 |                                                                            |               | —                                                    | 1.2                | 2.5          | mA       | Fosc = 4MHz, VDD = 3.0V<br>INTRC mode (Note 6)                                                                      |  |  |  |

|                       |                                                                            |               | —                                                    | 2.2                | 8            | mA       | Fosc = 10MHz, VDD = 5.5V<br>HS mode                                                                                 |  |  |  |

| D010A                 |                                                                            |               | —                                                    | 19                 | 29           | μA       | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Commercial Temperature                                           |  |  |  |

|                       |                                                                            |               | _                                                    | 19<br>32           | 37<br>60     | μΑ<br>μΑ | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Industrial Temperature<br>Fosc = 32kHz, VDD = 3.0V, WDT disabled |  |  |  |

|                       |                                                                            |               |                                                      |                    |              | •        | LP mode, Extended Temperature                                                                                       |  |  |  |

| D020<br>D021<br>D021B | Power-down Current <sup>(5)</sup>                                          | IPD           |                                                      | 0.25<br>0.25<br>2  | 6<br>7<br>14 | μΑ<br>μΑ | VDD = 3.0V, Commercial, WDT disabled<br>VDD = 3.0V, Industrial, WDT disabled<br>VDD = 3.0V, Extended, WDT disabled  |  |  |  |

| DUZID                 |                                                                            |               | _                                                    | 0.5                | 8            | μΑ<br>μΑ | VDD = 5.5V, Extended, WDT disabled $VDD = 5.5V$ , Commercial, WDT disabled                                          |  |  |  |

|                       |                                                                            |               | —                                                    | 0.8                | 9            | μA       | $V_{DD} = 5.5V$ , Industrial, WDT disabled                                                                          |  |  |  |

|                       |                                                                            |               | —                                                    | 3                  | 16           | μA       | VDD = 5.5V, Extended, WDT disabled                                                                                  |  |  |  |

| D022                  | Watchdog Timer Current                                                     | $\Delta$ IWDT | _                                                    | 2.2                | 5            | μA       | VDD = 3.0V, Commercial                                                                                              |  |  |  |

|                       |                                                                            |               | _                                                    | 2.2<br>4           | 6<br>11      | μΑ<br>μΑ | VDD = 3.0V, Industrial<br>VDD = 3.0V, Extended                                                                      |  |  |  |

| D028                  | Supply Current <sup>(3)</sup><br>During read/write to<br>EEPROM peripheral | ΔIEE          | —                                                    | 0.1                | 0.2          | mA       | Fosc = 4MHz, VDD = 5.5V, SCL = 400kHz<br>For PIC12CE673/674 only                                                    |  |  |  |

These parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

**6:** INTRC calibration value is for 4MHz nominal at 5V,  $25^{\circ}$ C.

| DC CH4      | ARACTERISTICS                                                                         |      | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C &\leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ -40^{\circ}C &\leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ -40^{\circ}C &\leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |                    |                         |            |                                      |  |  |  |

|-------------|---------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|------------|--------------------------------------|--|--|--|

| Parm<br>No. | Characteristic                                                                        | Sym  | Min                                                                                                                                                                                                                                                                                                                           | Typ <sup>(1)</sup> | Max                     | Units      | Units Conditions                     |  |  |  |

|             | LP Oscillator Operating<br>Frequency<br>INTRC/EXTRC Oscillator<br>Operating Frequency | Fosc | 0                                                                                                                                                                                                                                                                                                                             |                    | 200<br>4 <sup>(6)</sup> | kHz<br>MHz | All temperatures<br>All temperatures |  |  |  |

|             | XT Oscillator Operating<br>Frequency                                                  |      | 0                                                                                                                                                                                                                                                                                                                             |                    | 4                       | MHz        | All temperatures                     |  |  |  |

|             | HS Oscillator Operating<br>Frequency                                                  |      | 0                                                                                                                                                                                                                                                                                                                             |                    | 10                      | MHz        | All temperatures                     |  |  |  |

I hese parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD,

$\overline{MCLR} = VDD; WDT$  disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

### Standard Operating Conditions (unless otherwise specified)

#### Operating temperature

#### DC CHARACTERISTICS

$0^{\circ}C \leq TA \leq +70^{\circ}C$  (commercial)  $-40^{\circ}C \le TA \le +85^{\circ}C$  (industrial)  $-40^{\circ}C \le TA \le +125^{\circ}C$  (extended)

Operating voltage VDD range as described in DC spec Section 12.1 and Section 12.2.

|       |                                            | 0000001 |           |      |     |       |                                                               |

|-------|--------------------------------------------|---------|-----------|------|-----|-------|---------------------------------------------------------------|

| Param | Characteristic                             | Sym     | Min       | Typ† | Max | Units | Conditions                                                    |

| No.   |                                            |         |           |      |     |       |                                                               |

|       | Output High Voltage                        |         |           |      |     |       |                                                               |

| D090  | I/O ports (Note 3)                         | Voн     | Vdd - 0.7 | —    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>–40°С to +85°С                  |

| D090A |                                            |         | Vdd - 0.7 | —    | —   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>−40°C to +125°C                 |

| D092  | OSC2/CLKOUT                                |         | Vdd - 0.7 | —    | —   | V     | ІОн = 1.3 mA, VDD = 4.5V,<br>−40°C to +85°C                   |

| D092A |                                            |         | Vdd - 0.7 | —    | —   | V     | ІОн = 1.0 mA, VDD = 4.5V,<br>−40°C to +125°C                  |

|       | Capacitive Loading Specs on<br>Output Pins |         |           |      |     |       |                                                               |

| D100  | OSC2 pin                                   | Cosc2   | _         | _    | 15  | pF    | In XT and LP modes when external clock is used to drive OSC1. |

| D101  | All I/O pins                               | Сю      | —         | —    | 50  | pF    |                                                               |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

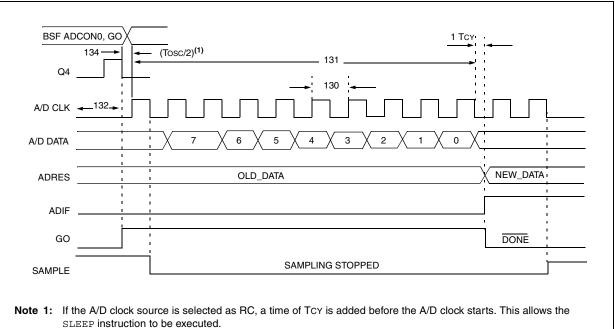

## FIGURE 12-9: A/D CONVERSION TIMING

| Param<br>No. | Sym  | Characteristic                         |                     | Min    | Тур†     | Max | Units | Conditions                                                                                                                                                                                                                      |

|--------------|------|----------------------------------------|---------------------|--------|----------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | Tad  | A/D clock period                       | PIC12 <b>C</b> 67X  | 1.6    | _        |     | μS    | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                                    |

|              |      |                                        | PIC12 <b>LC</b> 67X | 2.0    | _        | _   | μS    | TOSC based, VREF full range                                                                                                                                                                                                     |

|              |      |                                        | PIC12 <b>C</b> 67X  | 2.0    | 4.0      | 6.0 | μS    | A/D RC Mode                                                                                                                                                                                                                     |

|              |      |                                        | PIC12 <b>LC</b> 67X | 3.0    | 6.0      | 9.0 | μS    | A/D RC Mode                                                                                                                                                                                                                     |

| 131          | TCNV | Conversion time (not in time) (Note 1) | 11                  | —      | 11       | Tad |       |                                                                                                                                                                                                                                 |

| 132          | TACQ | Acquisition time                       |                     | Note 2 | 20       |     | μS    |                                                                                                                                                                                                                                 |

|              |      |                                        |                     | 5*     | _        | _   | μS    | The minimum time is the<br>amplifier setting time. This<br>may be used if the "new"<br>input voltage has not<br>changed by more than 1 LSt<br>(i.e., 20.0 mV @ 5.12V) from<br>the last sampled voltage (as<br>stated on CHOLD). |

| 134          | TGO  | O Q4 to A/D clock start                |                     |        | Tosc/2 § |     |       | If the A/D clock source is<br>selected as RC, a time of<br>TCY is added before the A/D<br>clock starts. This allows the<br>SLEEP instruction to be exe-<br>cuted.                                                               |

| 135          | Tswc | Switching from convert                 | 1.5 §               |        | _        | TAD |       |                                                                                                                                                                                                                                 |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

This specification ensured by design. §

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 8.1 for min. conditions.

# **PIC12C67X**

NOTES: