# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | <u>.</u>                                                                 |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671-10-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2.1 STATUS REGISTER

The STATUS Register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS Register, because these instructions do not affect the Z, C or DC bits from the STATUS Register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: Bits IRP and RP1 (STATUS<7:6>) are not used by the PIC12C67X and should be maintained clear. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

|             | Reserved                                                                                                                                                                                                                                                            | R/W-0      | R-1         | R-1 | R/W-x                          | R/W-x | R/W-x     |                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-----|--------------------------------|-------|-----------|-----------------------------------------------------------------------------------------------------------|

| IRP<br>bit7 | RP1                                                                                                                                                                                                                                                                 | RP0        | TO          | PD  | Z                              | DC    | C<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:      |                                                                                                                                                                                                                                                                     |            |             |     |                                |       |           |                                                                                                           |

| bit 6-5:    | RP<1:0>: Register Bank Select bits (used for direct addressing)<br>11 = Bank 3 (180h - 1FFh)<br>10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes. The RP1 bit is reserved; always maintain this bit clear. |            |             |     |                                |       |           |                                                                                                           |

| bit 4:      | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                     |            |             |     |                                |       |           |                                                                                                           |

| bit 3:      | <b>PD:</b> Power<br>1 = After p<br>0 = By exe                                                                                                                                                                                                                       | ower-up c  | or by the C |     |                                |       |           |                                                                                                           |

| bit 2:      |                                                                                                                                                                                                                                                                     | sult of an |             |     | peration is z<br>peration is r |       |           |                                                                                                           |

| bit 1:      | <b>DC:</b> Digit Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result                 |            |             |     |                                |       |           |                                                                                                           |

| bit 0:      | <b>C:</b> Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)<br>1 = A carry-out from the most significant bit of the result occurred<br>0 = No carry-out from the most significant bit of the result occurred                                               |            |             |     |                                |       |           |                                                                                                           |

| Note:       | ond ope                                                                                                                                                                                                                                                             |            | rotate (RR  |     |                                |       |           | the two's complement of the sec-<br>either the high or low order bit of                                   |

#### **REGISTER 4-1:** STATUS REGISTER (ADDRESS 03h, 83h)

#### 4.2.2.2 OPTION REGISTER

The OPTION Register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0 and the weak pull-ups on GPIO. Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

### REGISTER 4-2: OPTION REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1                                                | R/W-1                                                                     | R/W-1                 | R/W-1      | R/W-1                  | R/W-1 | R/W-1 |                                                                                       |  |

|----------|------------------------------------------------------|---------------------------------------------------------------------------|-----------------------|------------|------------------------|-------|-------|---------------------------------------------------------------------------------------|--|

| GPPU     | INTEDG                                               | T0CS                                                                      | T0SE                  | PSA        | PS2                    | PS1   | PS0   | R = Readable bit                                                                      |  |

| bit7     |                                                      |                                                                           |                       |            |                        |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7:   |                                                      |                                                                           |                       |            |                        |       |       |                                                                                       |  |

| bit 6:   |                                                      | pt on risi                                                                | ng edge of            |            | KI/AN2/IN<br>KI/AN2/IN |       |       |                                                                                       |  |

| bit 5:   | <b>TOCS:</b> TM<br>1 = Transit<br>0 = Interna        | ion on Gl                                                                 | P2/T0CKI/             | AN2/INT    |                        |       |       |                                                                                       |  |

| bit 4:   |                                                      | nent on hi                                                                | gh-to-low             | transition | on GP2/T0<br>on GP2/T0 |       |       |                                                                                       |  |

| bit 3:   | PSA: Pres<br>1 = Presca<br>0 = Presca                | aler is ass                                                               | signed to t           | he WDT     | module                 |       |       |                                                                                       |  |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> :                               | Prescaler                                                                 | Rate Sel              | ect bits   |                        |       |       |                                                                                       |  |

|          | Bit Value                                            | TMR0 R                                                                    | ate WD                | Γ Rate     |                        |       |       |                                                                                       |  |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 12<br>1 : 25 | 2 1:<br>4 1:<br>28 1: | 2<br>4     |                        |       |       |                                                                                       |  |

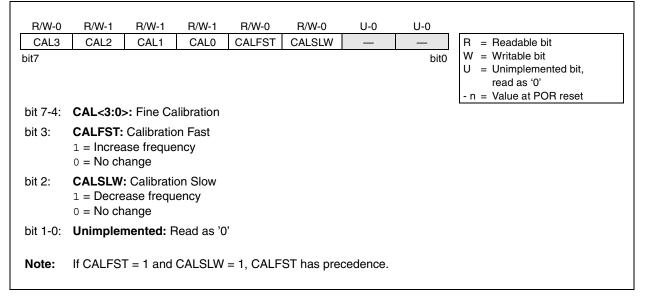

#### 4.2.2.7 OSCCAL REGISTER

The Oscillator Calibration (OSCCAL) Register is used to calibrate the internal 4 MHz oscillator. It contains four bits for fine calibration and two other bits to either increase or decrease frequency.

#### REGISTER 4-7: OSCCAL REGISTER (ADDRESS 8Fh)

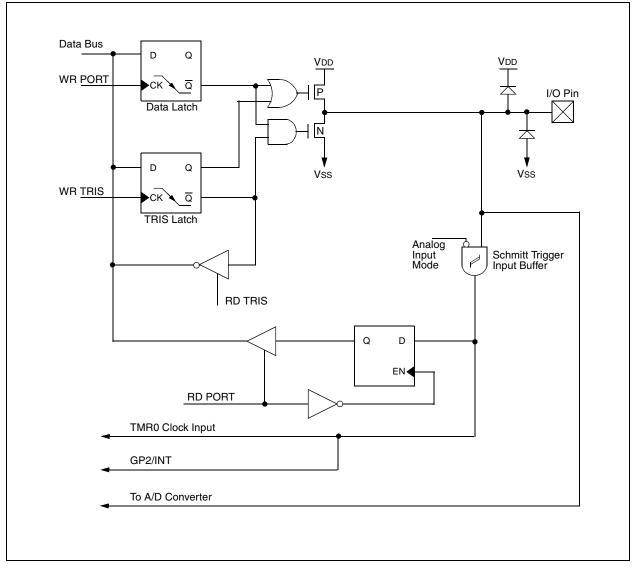

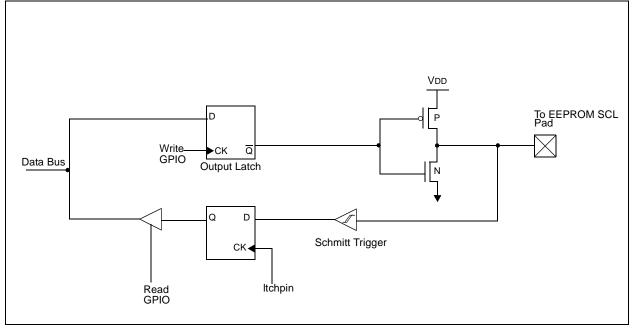

FIGURE 5-2: BLOCK DIAGRAM OF GP2/T0CKI/AN2/INT PIN

NOTES:

#### 6.1.5 ACKNOWLEDGE

The EEPROM, when addressed, will generate an acknowledge after the reception of each byte. The processor must generate an extra clock pulse which is associated with this acknowledge bit.

**Note:** Acknowledge bits are not generated if an internal programming cycle is in progress.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. The processor must signal an end of data to the EEPROM by not generating an acknowledge bit on the last byte that has been clocked out of the EEPROM. In this case, the EEPROM must leave the data line HIGH to enable the processor to generate the STOP condition (Figure 6-4).

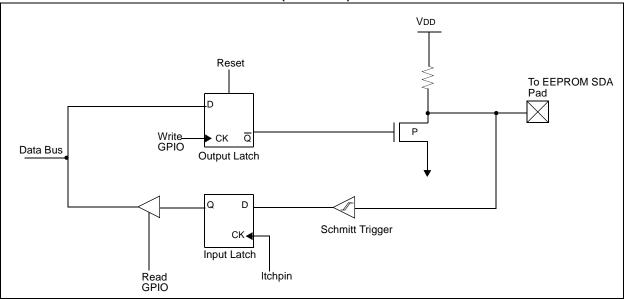

FIGURE 6-1: BLOCK DIAGRAM OF GPIO6 (SDA LINE)

FIGURE 6-2: BLOCK DIAGRAM OF GPIO7 (SCL LINE)

# **PIC12C67X**

NOTES:

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

## EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

## EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

#### TABLE 7-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6       | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|--------|-------------|---------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 | module's re | egister |       |       |       |       |       | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE        | TOIE    | INTE  | GPIE  | TOIF  | INTF  | GPIF  | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | GPPU   | INTEDG      | TOCS    | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111       | 1111 1111                       |

| 85h     | TRIS   | _      |             | TRIS5   | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0 | 11 1111         | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

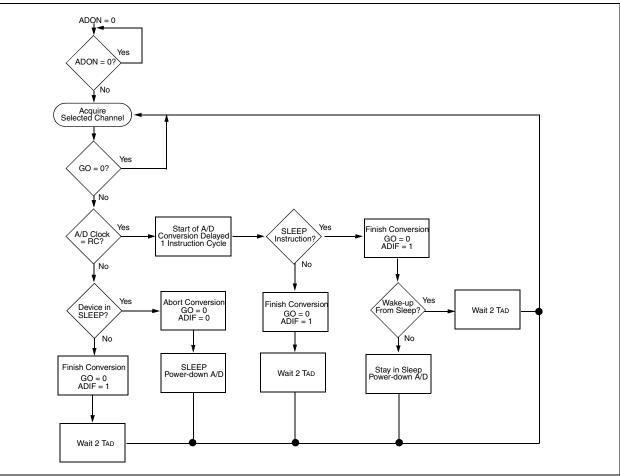

#### 8.5 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS<1:0> = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared, and the result loaded into the ADRES Register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS<1:0> = 11). To perform an A/D conversion in SLEEP, the GO/DONE bit must be set, followed by the SLEEP instruction.

#### 8.6 <u>A/D Accuracy/Error</u>

The overall accuracy of the A/D is less than  $\pm$  1 LSb for VDD = 5V  $\pm$  10% and the analog VREF = VDD. This overall accuracy includes offset error, full scale error, and integral error. The A/D converter is monotonic over the full VDD range. The resolution and accuracy may be less when either the analog reference (VDD) is less than 5.0V or when the analog reference (VREF) is less than VDD.

The maximum pin leakage current is specified in the Device Data Sheet electrical specification, parameter #D060.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from Tosc, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

#### 8.7 Effects of a Reset

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted. The value that is in the ADRES register is not modified for a Reset. The ADRES register will contain unknown data after a Power-on Reset.

#### 8.8 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

| Note: | For the PIC12C67X, care must be taken       |

|-------|---------------------------------------------|

|       | when using the GP4 pin in A/D conver-       |

|       | sions due to its proximity to the OSC1 pin. |

An external RC filter is sometimes added for antialiasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

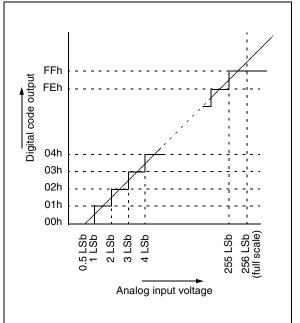

#### 8.9 <u>Transfer Function</u>

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is 1 LSb (or Analog VREF / 256) (Figure 8-3).

#### FIGURE 8-3: A/D TRANSFER FUNCTION

#### TABLE 8-2: SUMMARY OF A/D REGISTERS

| Address | Name                  | Bit 7              | Bit 6              | Bit 5    | Bit 4 | Bit 3 | Bit 2   | Bit 1    | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|-----------------------|--------------------|--------------------|----------|-------|-------|---------|----------|-------|-------------------------------|---------------------------------|

| 0Bh/8Bh | INTCON <sup>(1)</sup> | GIE                | PEIE               | TOIE     | INTE  | GPIE  | T0IF    | INTF     | GPIF  | x000 000x                     | 0000 000u                       |

| 0Ch     | PIR1                  | —                  | ADIF               | _        | —     | —     | -       | —        | —     | -0                            | -0                              |

| 8Ch     | PIE1                  | —                  | ADIE               | —        | _     | _     | _       | —        | —     | -0                            | -0                              |

| 1Eh     | ADRES                 | A/D Res            | sult Regist        | er       |       |       |         |          |       | xxxx xxxx                     | uuuu uuuu                       |

| 1Fh     | ADCON0                | ADCS1              | ADCS0              | reserved | CHS1  | CHS0  | GO/DONE | reserved | ADON  | 0000 0000                     | 0000 0000                       |

| 9Fh     | ADCON1                | _                  | _                  | _        |       | -     | PCFG2   | PCFG1    | PCFG0 | 000                           | 000                             |

| 05h     | GPIO                  | SCL <sup>(2)</sup> | SDA <sup>(2)</sup> | GP5      | GP4   | GP3   | GP2     | GP1      | GP0   | 11xx xxxx                     | 11uu uuuu                       |

| 85h     | TRIS                  | _                  | _                  | TRIS5    | TRIS4 | TRIS3 | TRIS2   | TRIS1    | TRIS0 | 11 1111                       | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers can be addressed from either bank.

2: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC12C67X can be operated in seven different oscillator modes. The user can program three configuration bits (Fosc<2:0>) to select one of these seven modes:

- LP: Low Power Crystal

- HS: High Speed Crystal/Resonator

- XT: Crystal/Resonator

- INTRC\*: Internal 4 MHz Oscillator

- EXTRC\*: External Resistor/Capacitor

\*Can be configured to support CLKOUT

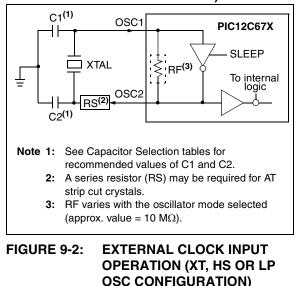

### 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

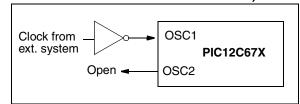

In XT, HS or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 9-1). The PIC12C67X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, HS or LP modes, the device can have an external clock source drive the GP5/OSC1/CLKIN pin (Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT, HS OR LP OSC CONFIGURATION)

#### TABLE 9-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C67X

| Osc<br>Type        | Resonator<br>Freq | Cap. Range<br>C1          | Cap. Range |

|--------------------|-------------------|---------------------------|------------|

| XT                 | 455 kHz           | 22-100,pF                 | 22-100 pF  |

|                    | 2.0 MHz           | 15-68 pf                  | レ15-68 pF  |

|                    | 4.0 MHz           | ~ { <b>1</b> ,5+68 pf ~ ~ | 15-68 pF   |

| HS                 | 4.0-MHX           | \ <b>15-68</b> pF         | 15-68 pF   |

|                    | 8,0 MHz           | 10-68 pF                  | 10-68 pF   |

| $\widehat{\Omega}$ | tp:0 MHz          | 10-22 pF                  | 10-22 pF   |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR - PIC12C67X

| - 11012007X     |                       |                     |                        |  |  |  |  |

|-----------------|-----------------------|---------------------|------------------------|--|--|--|--|

| Osc<br>Type     | Resonator<br>Freq     | Cap. Range<br>C1    | Cap. Range<br>C2       |  |  |  |  |

| LP              | 32 kHz <sup>(1)</sup> | 15 pF               | 15 pF 🚽                |  |  |  |  |

|                 | 100 kHz               | 15-30 pF            | 30-47 p⊄               |  |  |  |  |

|                 | 200 kHz               | 15-30 pF            | 15-83 pF               |  |  |  |  |

| XT              | 100 kHz               | 15-30 pF            | 200-300 pF             |  |  |  |  |

|                 | 200 kHz               | 15-30 pE            | 100-200 pF             |  |  |  |  |

|                 | 455 kHz               | 15-30 pF            | <sup>™</sup> 15-100 pF |  |  |  |  |

|                 | 1 MHz 🔨               | 1,15-30.pF          | 15-30 pF               |  |  |  |  |

|                 | 2, MAHz ∖∖            | \ <b>∖</b> 19-30 pF | 15-30 pF               |  |  |  |  |

|                 | (AMHz)                | 15-47 pF            | 15-47 pF               |  |  |  |  |

| HS              | 4 10AHz               | 15-30 pF            | 15-30 pF               |  |  |  |  |

| $(\mathcal{O})$ | 😕 🖲 MHz               | 15-30 pF            | 15-30 pF               |  |  |  |  |

| VZ Z            | 10 MHz                | 15-30 pF            | 15-30 pF               |  |  |  |  |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 9.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at  $V_{DD} = 5V$  and  $25^{\circ}$ C. See Section 13.0 for information on variation over voltage and temperature.

In addition, a calibration instruction is programmed into the last address of the program memory which contains the calibration value for the internal RC oscillator. This value is programmed as a RETLW XX instruction where XX is the calibration value. In order to retrieve the calibration value, issue a CALL YY instruction where YY is the last location in program memory (03FFh for the PIC12C671 and the PIC12CE673, 07FFh for the PIC12C672 and the PIC12CE674). Control will be returned to the user's program with the calibration value loaded into the W register. The program should then perform a MOVWF OSCCAL instruction to load the value into the internal RC oscillator trim register.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency. Bits <7:4>, CAL<3:0> are used for fine calibration, while bit 3, CALFST, and bit 2, CALSLW, are used for more coarse adjustment. Adjusting CAL<3:0> from 0000 to 1111 yields a higher clock speed. Set CALFST = 1 for greater increase in frequency or set CALSLW = 1 for greater decrease in frequency. Note that bits 1 and 0 of OSCCAL are unimplemented and should be written as 0 when modifying OSCCAL for compatibility with future devices.

| Note: | Please note that erasing the device will       |

|-------|------------------------------------------------|

|       | also erase the pre-programmed internal         |

|       | calibration value for the internal oscillator. |

|       | The calibration value must be saved prior      |

|       | to erasing the part.                           |

#### 9.2.6 CLKOUT

The PIC12C67X can be configured to provide a clock out signal (CLKOUT) on pin 3 when the configuration word address (2007h) is programmed with Fosc2, Fosc1, and Fosc0, equal to 101 for INTRC or 111 for EXTRC. The oscillator frequency, divided by 4, can be used for test purposes or to synchronize other logic.

#### 9.3 <u>Reset</u>

The PIC12C67X differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), MCLR Reset, WDT Reset, and MCLR Reset during SLEEP. They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations, as indicated in Table 9-5. These bits are used in software to determine the nature of the reset. See Table 9-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 9-6.

The PIC12C67X has a MCLR noise filter in the MCLR reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

When MCLR is asserted, the state of the OSC1/CLKIN and CLKOUT/OSC2 pins are as follows:

### TABLE 9-3:CLKIN/CLKOUT PIN STATESWHEN MCLR ASSERTED

| Oscillator Mode          | OSC1/CLKIN Pin                                                | OSC2/CLKout Pin               |

|--------------------------|---------------------------------------------------------------|-------------------------------|

| EXTRC, CLKOUT<br>on OSC2 | OSC1 pin is<br>tristated and<br>driven by external<br>circuit | OSC2 pin is driven<br>low     |

| EXTRC, OSC2 is<br>I/O    | OSC1 pin is<br>tristated and<br>driven by external<br>circuit | OSC2 pin is tristate input    |

| INTRC, CLKOUT<br>on OSC2 | OSC1 pin is<br>tristate input                                 | OSC2 pin is driven<br>low     |

| INTRC, OSC2 is<br>I/O    | OSC1 pin is<br>tristate input                                 | OSC2 pin is<br>tristate input |

#### 9.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create a Poweron Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See Table 11-4.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

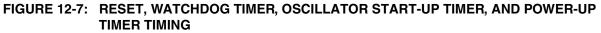

#### 9.4.4 TIME-OUT SEQUENCE

On power-up, the Time-out Sequence is as follows: first, PWRT time-out is invoked after the POR time delay has expired; then, OST is activated. The total time-out will vary, based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-7, Figure 9-8, and Figure 9-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC12C67X device operating in parallel.

### 9.4.5 POWER CONTROL (PCON)/STATUS REGISTER

The Power Control/Status Register, PCON (address 8Eh), has one bit. See Register 4-6 for register.

Bit1 is POR (Power-on Reset). It is cleared on a Poweron Reset and is unaffected otherwise. The user sets this bit following a Power-on Reset. On subsequent resets, if POR is '0', it will indicate that a Power-on Reset must have occurred.

| <b>Oscillator Configuration</b> | Power            | Wake-up from SLEEP |          |

|---------------------------------|------------------|--------------------|----------|

|                                 | <b>PWRTE</b> = 0 | PWRTE = 1          |          |

| XT, HS, LP                      | 72 ms + 1024Tosc | 1024Tosc           | 1024Tosc |

| INTRC, EXTRC                    | 72 ms            | _                  | _        |

TABLE 9-4: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 9-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | TO | PD |                                                         |  |

|-----|----|----|---------------------------------------------------------|--|

| 0   | 1  | 1  | Power-on Reset                                          |  |

| 0   | 0  | x  | Illegal, TO is set on POR                               |  |

| 0   | х  | 0  | Illegal, PD is set on POR                               |  |

| 1   | 0  | u  | WDT Reset                                               |  |

| 1   | 0  | 0  | WDT Wake-up                                             |  |

| 1   | u  | u  | MCLR Reset during normal operation                      |  |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |

Legend: u = unchanged, x = unknown.

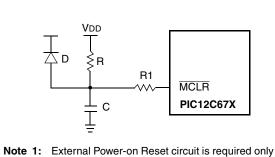

#### FIGURE 9-10: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Iote 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- **3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C, in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

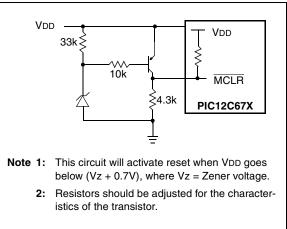

#### FIGURE 9-11: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

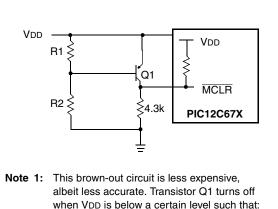

#### FIGURE 9-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

2: Resistors should be adjusted for the characteristics of the transistor.

TABLE 12-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER

| Parameter<br>No. | Sym   | Characteristic                                            | Min | Тур†     | Мах | Units | Conditions                                         |

|------------------|-------|-----------------------------------------------------------|-----|----------|-----|-------|----------------------------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                    | 2   | —        |     | μS    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)          | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32               | Tost  | Oscillation Start-up Timer Period                         | _   | 1024Tosc | _   | —     | Tosc = OSC1 period                                 |

| 33*              | Tpwrt | Power up Timer Period                                     | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34               | TIOZ  | I/O Hi-impedance from MCLR<br>Low or Watchdog Timer Reset |     | _        | 2.1 | μS    |                                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 14.0 PACKAGING INFORMATION

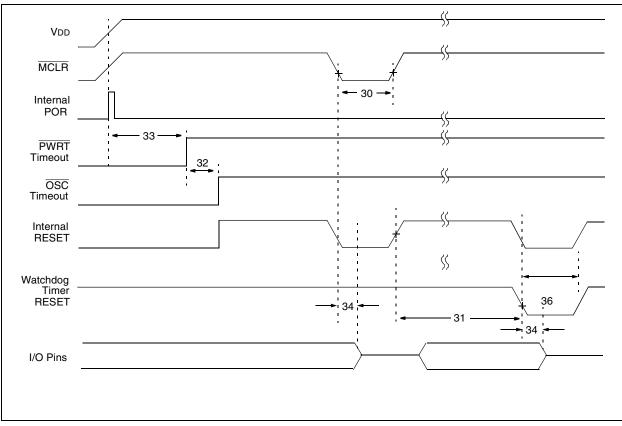

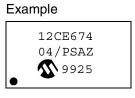

#### 14.1 Package Marking Information

#### 8-Lead PDIP (300 mil)

#### 8-Lead SOIC (208 mil)

#### 8-Lead Windowed Ceramic Side Brazed (300 mil)

| Legen | d: MMM<br>XXX<br>AA<br>BB<br>C                                                                                                                                                                               | Microchip part number information<br>Customer specific information*<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Facility code of the plant at which wafer is manufactured<br>O = Outside Vendor<br>C = 5" Line<br>S = 6" Line<br>H = 8" Line<br>Mask revision number<br>Assembly code of the plant or country of origin in which<br>part was assembled |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Note: | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line thus limiting the number of available characters<br>for customer specific information. |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

#### **APPENDIX A: COMPATIBILITY**

To convert code written for PIC16C5X to PIC12C67X, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

#### APPENDIX B: CODE FOR ACCESSING EEPROM DATA MEMORY

Please refer to our web site at www.microchip.com for code availability.

#### **APPENDIX C: REVISION HISTORY**

Revision C (January 2013)

Added a note to each package outline drawing.

# PIC16XXXXX FAMILY

#### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: |                                                                                               | Total Pages Sent              |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|

| Fror       | m: Name                                                                                       |                               |  |  |  |  |  |  |

|            | Company                                                                                       |                               |  |  |  |  |  |  |

|            | Address                                                                                       |                               |  |  |  |  |  |  |

|            | City / State / ZIP / Country                                                                  |                               |  |  |  |  |  |  |

|            | Telephone: ()                                                                                 | FAX: ()                       |  |  |  |  |  |  |

| Арр        | lication (optional):                                                                          |                               |  |  |  |  |  |  |

| Wou        | uld you like a reply? Y N                                                                     |                               |  |  |  |  |  |  |

| Dev        | vice: PIC16xxxxxx family                                                                      | Literature Number: DS30561C   |  |  |  |  |  |  |

| Que        | estions:                                                                                      |                               |  |  |  |  |  |  |

| 1.         | What are the best features of this document?                                                  |                               |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

| 2.         | <ol> <li>How does this document meet your hardware and software development needs?</li> </ol> |                               |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

| 3.         | B. Do you find the organization of this document easy to follow? If not, why?                 |                               |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

| 4.         | What additions to the document do you think would enhar                                       | ce the structure and subject? |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

| _          |                                                                                               | <i></i>                       |  |  |  |  |  |  |

| 5.         | 5. What deletions from the document could be made without affecting the overall usefulness?   |                               |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

| 6.         | . Is there any incorrect or misleading information (what and where)?                          |                               |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

| 7.         | How would you improve this document?                                                          |                               |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

|            |                                                                                               |                               |  |  |  |  |  |  |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1997-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769287

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12