Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                |                                                                           |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 8-SOIJ                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671-10-sm |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>TABLE 3-1:</b> | PIC12C67X PINOUT DESCRIPTION |

|-------------------|------------------------------|

|-------------------|------------------------------|

| Name                     | DIP Pin # | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|-----------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/AN0                  | 7         | I/O           | TTL/ST         | Bi-directional I/O port/serial programming data/analog input 0.<br>Can be software programmed for internal weak pull-up and<br>interrupt-on-pin change. This buffer is a Schmitt Trigger input<br>when used in serial programming mode.                                                                                                                                                                                |

| GP1/AN1/V <sub>REF</sub> | 6         | I/O           | TTL/ST         | Bi-directional I/O port/serial programming clock/analog input 1/<br>voltage reference. Can be software programmed for internal<br>weak pull-up and interrupt-on-pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming mode.                                                                                                                                                            |

| GP2/T0CKI/AN2/INT        | 5         | I/O           | ST             | Bi-directional I/O port/analog input 2. Can be configured as T0CKI or external interrupt.                                                                                                                                                                                                                                                                                                                              |

| GP3/MCLR/Vpp             | 4         | Ι             | TTL/ST         | Input port/master clear (reset) input/programming voltage<br>input. When configured as MCLR, this pin is an active low<br>reset to the device. Voltage on MCLR/VPP must not exceed<br>VDD during normal device operation. Can be software pro-<br>grammed for internal weak pull-up and interrupt-on-pin<br>change. Weak pull-up always on if configured as MCLR. This<br>buffer is Schmitt Trigger when in MCLR mode. |

| GP4/OSC2/AN3/CLKOUT      | 3         | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output/analog input 3.<br>Connections to crystal or resonator in crystal oscillator mode<br>(HS, XT and LP modes only, GPIO in other modes). In EXTRC<br>and INTRC modes, the pin output can be configured to CLK-<br>OUT, which has 1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.                                                                   |

| GP5/OSC1/CLKIN           | 2         | I/O           | TTL/ST         | Bi-directional IO port/oscillator crystal input/external clock<br>source input (GPIO in INTRC mode only, OSC1 in all other<br>oscillator modes). Schmitt trigger input for EXTRC oscillator<br>mode.                                                                                                                                                                                                                   |

| Vdd                      | 1         | Р             | _              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                |

| Vss                      | 8         | Р             | _              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                               |

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input.

NOTES:

# 8.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-To-Digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the GP1/AN1/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 Register, shown in Figure 8-1, controls the operation of the A/D module. The ADCON1 Register, shown in Figure 8-2, configures the functions of the port pins. The port pins can be configured as analog inputs (GP1 can also be a voltage reference) or as digital I/O.

- Note 1: If the port pins are configured as analog inputs (reset condition), reading the port (MOVF GPIO,W) results in reading '0's.

- 2: Changing ADCON1 Register can cause the GPIF and INTF flags to be set in the INTCON Register. These interrupts should be disabled prior to modifying ADCON1.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ADCS1 ADCS0 CHS1 CHS0 GO/DONE ADON R = Readable bit reserved reserved W = Writable bit bit0 bit7 U = Unimplemented bit, read as '0' n = Value at POR reset bit 7-6: ADCS<1:0>: A/D Conversion Clock Select bits 00 = Fosc/201 = Fosc/810 = Fosc/3211 = FRC (clock derived from an RC oscillation) Reserved bit 5: bit 4-3: CHS<1:0>: Analog Channel Select bits 00 = channel 0, (GP0/AN0) 01 = channel 1, (GP1/AN1) 10 = channel 2, (GP2/AN2) 11 = channel 3, (GP4/AN3) GO/DONE: A/D Conversion Status bit bit 2: If ADON = 11 = A/D conversion in progress (setting this bit starts the A/D conversion) 0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete) bit 1: Reserved bit 0: ADON: A/D on bit 1 = A/D converter module is operating 0 = A/D converter module is shut off and consumes no operating current

#### REGISTER 8-1: ADCON0 REGISTER (ADDRESS 1Fh)

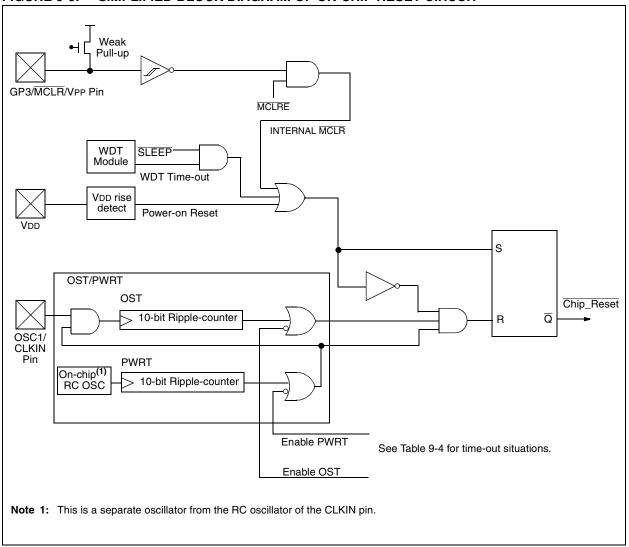

FIGURE 9-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 9.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create a Poweron Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See Table 11-4.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 9.4.4 TIME-OUT SEQUENCE

On power-up, the Time-out Sequence is as follows: first, PWRT time-out is invoked after the POR time delay has expired; then, OST is activated. The total time-out will vary, based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-7, Figure 9-8, and Figure 9-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC12C67X device operating in parallel.

# 9.4.5 POWER CONTROL (PCON)/STATUS REGISTER

The Power Control/Status Register, PCON (address 8Eh), has one bit. See Register 4-6 for register.

Bit1 is POR (Power-on Reset). It is cleared on a Poweron Reset and is unaffected otherwise. The user sets this bit following a Power-on Reset. On subsequent resets, if POR is '0', it will indicate that a Power-on Reset must have occurred.

| <b>Oscillator Configuration</b> | Power            | Wake-up from SLEEP |          |

|---------------------------------|------------------|--------------------|----------|

|                                 | <b>PWRTE</b> = 0 | PWRTE = 1          |          |

| XT, HS, LP                      | 72 ms + 1024Tosc | 1024Tosc           | 1024Tosc |

| INTRC, EXTRC                    | 72 ms            | _                  | —        |

### TABLE 9-4: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 9-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | то | PD |                                                         |

|-----|----|----|---------------------------------------------------------|

| 0   | 1  | 1  | Power-on Reset                                          |

| 0   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0  | u  | WDT Reset                                               |

| 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

Legend: u = unchanged, x = unknown.

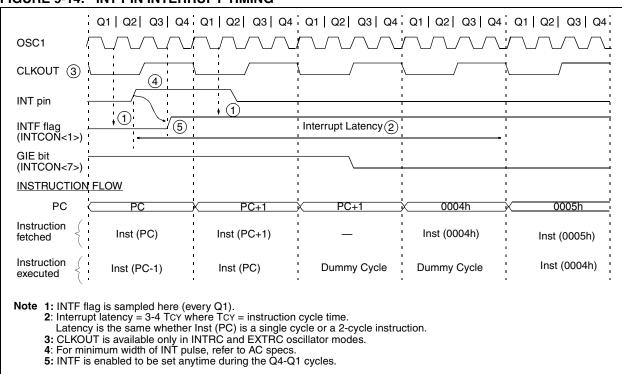

#### FIGURE 9-14: INT PIN INTERRUPT TIMING

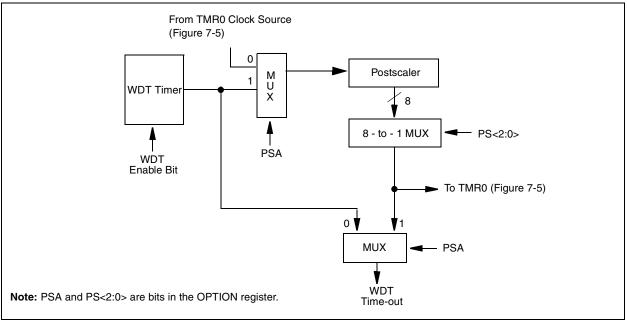

#### 9.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 9.1).

#### 9.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized. The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out early and generating a premature device RESET condition.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

9.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

Note: When the prescaler is assigned to the WDT, always execute a CLRWDT instruction before changing the prescale value, otherwise a WDT reset may occur.

See Example 7-1 and Example 7-2 for changing prescaler between WDT and Timer0.

#### FIGURE 9-15: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 9-8: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name                        | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------------------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits <sup>(1)</sup> | MCLRE | CP1    | CP0   | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| 81h     | OPTION                      | GPPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 9-1 for operation of these bits. Not all CP0 and CP1 bits are shown.

# **10.0 INSTRUCTION SET SUMMARY**

Each PIC12C67X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC12C67X instruction set summary in Table 10-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 10-2 lists the instructions recognized by the MPASM assembler.

Figure 10-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC12C67X products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

#### FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

|                                                                                       |       |         |        | 10          |   |

|---------------------------------------------------------------------------------------|-------|---------|--------|-------------|---|

| Byte-oriented file                                                                    | regis | ster op | oerati | ons         |   |

| 13                                                                                    | 8     | 7       | 6      |             | 0 |

| OPCODE                                                                                |       | d       |        | f (FILE #)  |   |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |       |         |        |             |   |

| Bit-oriented file re                                                                  | giste | er ope  | ratior | าร          |   |

| 13                                                                                    | 10    | 9       | 7      | 6           | 0 |

| OPCODE                                                                                |       | b (Bl   | T #)   | f (FILE #)  |   |

| Literal and contro<br>General                                                         | l op  | eratio  | ns     |             |   |

| 13                                                                                    |       | 8       | 7      |             | 0 |

| OPCODE                                                                                |       |         |        | k (literal) |   |

| k = 8-bit imm                                                                         | nedia | ate va  | ue     |             |   |

| CALL and GOTO ins                                                                     | struc | tions   | only   |             |   |

| 13 11                                                                                 | 10    |         |        |             | 0 |

| OPCODE                                                                                |       |         | k (l   | literal)    |   |

| k = 11-bit im                                                                         | med   | iate v  | alue   |             |   |

#### 10.1 <u>Special Function Registers as</u> <u>Source/Destination</u>

The PIC12C67X's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 10.1.1 STATUS AS DESTINATION

If an instruction writes to STATUS, the Z, C and DC bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF STATUS will clear register STATUS, and then set the Z bit leaving 0000 0100b in the register.

#### 10.1.2 TRIS AS DESTINATION

Bit 3 of the TRIS register always reads as a '1' since GP3 is an input only pin. This fact can affect some read-modify-write operations on the TRIS register.

#### 10.1.3 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCL \to dest$                                                                               |

|--------------------|----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                       |

| Read-Modify-Write: | PCL $\rightarrow$ ALU operand<br>PCLATH $\rightarrow$ PCH;<br>8-bit result $\rightarrow$ PCL |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 10.1.4 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write). The user should keep this in mind when operating on special function registers, such as ports.

# **PIC12C67X**

| GOTO                              | Unconditional Branch                                                                                                                                                                                  | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [ <i>label</i> ] GOTO k                                                                                                                                                                               | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                       |

| Operands:                         | $0 \le k \le 2047$                                                                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                        |

| Operation:                        | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                       | Operation:       | $d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                        |

| Status Affected:                  | None                                                                                                                                                                                                  | Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |

| Encoding:                         | 10 1kkk kkkk kkkk                                                                                                                                                                                     | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                                        |

| Description:<br>Words:<br>Cycles: | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two<br>cycle instruction.<br>1 | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction. |

| Example                           | GOTO THERE                                                                                                                                                                                            | Words:           | 1                                                                                                                                                                                                                                                                                                                                        |

|                                   | After Instruction<br>PC = Address THERE                                                                                                                                                               | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                                     |

|                                   |                                                                                                                                                                                                       | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE<br>•                                                                                                                                                                                                                                                                                         |

|                                   |                                                                                                                                                                                                       |                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1                                                                                                                                                                                                                                                            |

| INCF             | Increment f                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                          |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                        |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                        |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'. |

| Words:           | 1                                                                                                                                                                        |

| Cycles:          | 1                                                                                                                                                                        |

| Example          | INCF CNT, 1                                                                                                                                                              |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction                                                                                                           |

|                  | $\begin{array}{rcl} CNT &=& 0x00 \\ Z &=& 1 \end{array}$                                                                                                                 |

| IORLW            | Inclusive OR Literal with W                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                                              |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                |

| Description:     | The contents of the W register are OR'ed with the eight bit literal 'k'. The result is placed in the W register. |

| Words:           | 1                                                                                                                |

| Cycles:          | 1                                                                                                                |

| Example          | IORLW 0x35                                                                                                       |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                         |

if CNT=

PC =

if CNT≠

=

PC

0,

0,

address CONTINUE

address HERE +1

NOTES:

# **PIC12C67X**

NOTES:

# 12.0 ELECTRICAL SPECIFICATIONS FOR PIC12C67X

### Absolute Maximum Ratings †

| <b>3</b>                                                                                                       |                                    |

|----------------------------------------------------------------------------------------------------------------|------------------------------------|

| Ambient temperature under bias                                                                                 | 40° to +125°C                      |

| Storage temperature                                                                                            | –65°C to +150°C                    |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | –0.3V to (VDD + 0.3V)              |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.0V                         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                               | 700 mW                             |

| Maximum current out of Vss pin                                                                                 | 200 mA                             |

| Maximum current into VDD pin                                                                                   |                                    |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                   | ±20 mA                             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                 |                                    |

| Maximum output current sunk by any I/O pin                                                                     | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                  | 25 mA                              |

| Maximum current sunk by GPIO pins combined                                                                     | 100 mA                             |

| Maximum current sourced by GPIO pins combined                                                                  | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VO | OH) x IOH} + $\Sigma$ (VOI x IOL). |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

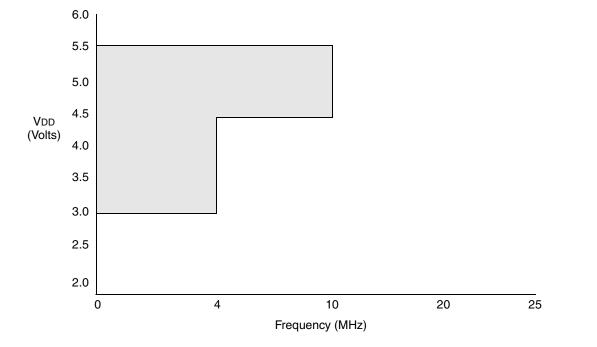

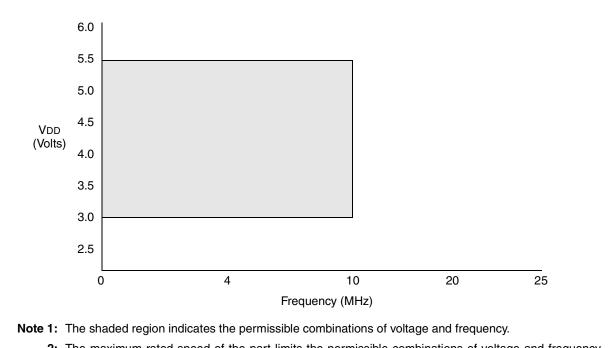

- Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

- **2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

FIGURE 12-2: PIC12C67X VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \le TA \le +70^{\circ}C$

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

#### 12.2 DC Characteristics: PIC12LC671/672 (Commercial, Industrial) PIC12LCE673/674 (Commercial, Industrial)

| DC CHAF               |                                               | Standard Operating Conditions (unless otherwise specified)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial) |       |            |                  |          |                                                                                                                             |

|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                | Sym                                                                                                                                                                                       | Min   | Тур†       | Max              | Units    | Conditions                                                                                                                  |

| D001                  | Supply Voltage                                | Vdd                                                                                                                                                                                       | 2.5   |            | 5.5              | V        |                                                                                                                             |

| D002                  | RAM Data Retention<br>Voltage <sup>(2)</sup>  | Vdr                                                                                                                                                                                       |       | 1.5*       |                  | V        | Device in SLEEP mode                                                                                                        |

| D003                  | VDD Start Voltage to<br>ensure Power-on Reset | VPOR                                                                                                                                                                                      |       | Vss        |                  | V        | See section on Power-on Reset for details                                                                                   |

| D004                  | VDD Rise Rate to ensure<br>Power-on Reset     | SVDD                                                                                                                                                                                      | 0.05* |            |                  | V/ms     | See section on Power-on Reset for details                                                                                   |

| D010                  | Supply Current <sup>(3)</sup>                 | IDD                                                                                                                                                                                       | —     | 0.4        | 2.1              | mA       | Fosc = 4MHz, VDD = 2.5V<br>XT and EXTRC mode (Note 4)                                                                       |

| D010C<br>D010A        |                                               |                                                                                                                                                                                           | _     | 0.4<br>15  | 2.1<br>33        | mA<br>μA | Fosc = 4MHz, VDD = 2.5V<br>INTRC mode (Note 6)<br>Fosc = 32kHz, VDD = 2.5V, WDT disabled<br>LP mode, Industrial Temperature |

| D020<br>D021<br>D021B | Power-down Current <sup>(5)</sup>             | IPD                                                                                                                                                                                       | _     | 0.2<br>0.2 | 5<br>6           | μΑ<br>μΑ | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                                                                            |

|                       | Watchdog Timer Current                        | ΔIWDT                                                                                                                                                                                     | —     | 2.0<br>2.0 | 4<br>6           | μΑ<br>μΑ | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                                                                            |

|                       | LP Oscillator Operating<br>Frequency          | Fosc                                                                                                                                                                                      | 0     |            | 200              | kHz      | All temperatures                                                                                                            |

|                       | INTRC/EXTRC Oscillator<br>Operating Frequency |                                                                                                                                                                                           | -     |            | 4 <sup>(6)</sup> | MHz      | All temperatures                                                                                                            |

|                       | XT Oscillator Operating<br>Frequency          |                                                                                                                                                                                           | 0     |            | 4                | MHz      | All temperatures                                                                                                            |

|                       | HS Oscillator Operating<br>Frequency          |                                                                                                                                                                                           | 0     |            | 10               | MHz      | All temperatures                                                                                                            |

\* These parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

#### Standard Operating Conditions (unless otherwise specified)

#### Operating temperature

#### DC CHARACTERISTICS

$0^{\circ}C \leq TA \leq +70^{\circ}C$  (commercial)  $-40^{\circ}C \le TA \le +85^{\circ}C$  (industrial)  $-40^{\circ}C \le TA \le +125^{\circ}C$  (extended)

Operating voltage VDD range as described in DC spec Section 12.1 and Section 12.2.

| Param | Characteristic                             | Sym   | Min       | Typ† | Max | Units | Conditions                                                    |

|-------|--------------------------------------------|-------|-----------|------|-----|-------|---------------------------------------------------------------|

| No.   |                                            |       |           |      |     |       |                                                               |

|       | Output High Voltage                        |       |           |      |     |       |                                                               |

| D090  | I/O ports (Note 3)                         | Voн   | Vdd - 0.7 | —    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>–40°С to +85°С                  |

| D090A |                                            |       | Vdd - 0.7 | —    | —   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>−40°C to +125°C                 |

| D092  | OSC2/CLKOUT                                |       | Vdd - 0.7 | —    | —   | V     | ІОн = 1.3 mA, VDD = 4.5V,<br>−40°C to +85°C                   |

| D092A |                                            |       | Vdd - 0.7 | —    | —   | V     | ІОн = 1.0 mA, VDD = 4.5V,<br>−40°C to +125°C                  |

|       | Capacitive Loading Specs on<br>Output Pins |       |           |      |     |       |                                                               |

| D100  | OSC2 pin                                   | Cosc2 | _         | _    | 15  | pF    | In XT and LP modes when external clock is used to drive OSC1. |

| D101  | All I/O pins                               | Сю    | —         | —    | 50  | pF    |                                                               |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

# 14.0 PACKAGING INFORMATION

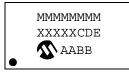

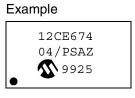

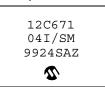

### 14.1 Package Marking Information

### 8-Lead PDIP (300 mil)

#### 8-Lead SOIC (208 mil)

### 8-Lead Windowed Ceramic Side Brazed (300 mil)

| Legen | d: MMM<br>XXX<br>AA<br>BB<br>C                                                                                                                                                                               | Microchip part number information<br>Customer specific information*<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Facility code of the plant at which wafer is manufactured<br>O = Outside Vendor<br>C = 5" Line<br>S = 6" Line<br>H = 8" Line<br>Mask revision number<br>Assembly code of the plant or country of origin in which<br>part was assembled |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Note: | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line thus limiting the number of available characters<br>for customer specific information. |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

NOTES:

# PIC16XXXXX FAMILY

## READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: |                                                                               | Total Pages Sent                  |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|

| Fror       | m: Name                                                                       |                                   |  |  |  |  |  |

|            | Company                                                                       |                                   |  |  |  |  |  |

|            | Address                                                                       |                                   |  |  |  |  |  |

|            | City / State / ZIP / Country                                                  |                                   |  |  |  |  |  |

|            | Telephone: ()                                                                 | FAX: ()                           |  |  |  |  |  |

| Арр        | lication (optional):                                                          |                                   |  |  |  |  |  |

| Wou        | uld you like a reply? Y N                                                     |                                   |  |  |  |  |  |

| Dev        | vice: PIC16xxxxxx family                                                      | Literature Number: DS30561C       |  |  |  |  |  |

| Que        | estions:                                                                      |                                   |  |  |  |  |  |

| 1.         | What are the best features of this document?                                  |                                   |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

| 2.         | How does this document meet your hardware and softwar                         | e development needs?              |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

| 3.         | B. Do you find the organization of this document easy to follow? If not, why? |                                   |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

| 4.         | What additions to the document do you think would enhar                       | ce the structure and subject?     |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

| _          |                                                                               | <i></i>                           |  |  |  |  |  |

| 5.         | What deletions from the document could be made without                        | affecting the overall usefulness? |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

| 6.         | Is there any incorrect or misleading information (what and                    | where)?                           |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

| 7.         | How would you improve this document?                                          |                                   |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

|            |                                                                               |                                   |  |  |  |  |  |

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12