Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671t-04-sm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12C67X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C67X uses a Harvard architecture, in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses also allow instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single instruction cycle. A two-stage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), and non-volatile memory (EEPROM) for each PIC12C67X device.

| Device     | Program<br>Memory | RAM Data<br>Memory | EEPROM<br>Data<br>Memory |

|------------|-------------------|--------------------|--------------------------|

| PIC12C671  | 1K x 14           | 128 x 8            | —                        |

| PIC12C672  | 2K x 14           | 128 x 8            | —                        |

| PIC12CE673 | 1K x 14           | 128 x 8            | 16x8                     |

| PIC12CE674 | 2K x 14           | 128 x 8            | 16x8                     |

The PIC12C67X can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC12C67X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C67X simple yet efficient. In addition, the learning curve is reduced significantly.

PIC12C67X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| Address              | Name   | Bit 7              | Bit 6                                         | Bit 5        | Bit 4         | Bit 3          | Bit 2           | Bit 1        | Bit 0       | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets <sup>(3)</sup> |

|----------------------|--------|--------------------|-----------------------------------------------|--------------|---------------|----------------|-----------------|--------------|-------------|-------------------------------|------------------------------------------------|

| Bank 1               |        |                    |                                               |              |               |                | •               | •            |             |                               |                                                |

| 80h <sup>(1)</sup>   | INDF   | Addressing         | this location                                 | uses conter  | nts of FSR to | address dat    | a memory (n     | ot a physica | l register) | 0000 0000                     | 0000 0000                                      |

| 81h                  | OPTION | GPPU               | INTEDG                                        | TOCS         | TOSE          | PSA            | PS2             | PS1          | PS0         | 1111 1111                     | 1111 1111                                      |

| 82h <sup>(1)</sup>   | PCL    | Program Co         | Program Counter's (PC) Least Significant Byte |              |               |                |                 |              |             |                               | 0000 0000                                      |

| 83h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                            | RP0          | TO            | PD             | Z               | DC           | С           | 0001 1xxx                     | 000q quuu                                      |

| 84h <sup>(1)</sup>   | FSR    | Indirect data      | a memory ac                                   | dress pointe | ər            |                |                 |              |             | xxxx xxxx                     | uuuu uuuu                                      |

| 85h                  | TRIS   | _                  | _                                             | GPIO Data    | Direction Re  | gister         |                 |              |             | 11 1111                       | 11 1111                                        |

| 86h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | —                                              |

| 87h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | —                                              |

| 88h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | _                                              |

| 89h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | —                                              |

| 8Ah <sup>(1,2)</sup> | PCLATH | _                  | —                                             | _            | Write Buffe   | r for the uppe | er 5 bits of th | e PC         |             | 0 0000                        | 0 0000                                         |

| 8Bh <sup>(1)</sup>   | INTCON | GIE                | PEIE                                          | TOIE         | INTE          | GPIE           | TOIF            | INTF         | GPIF        | 0000 000x                     | 0000 000u                                      |

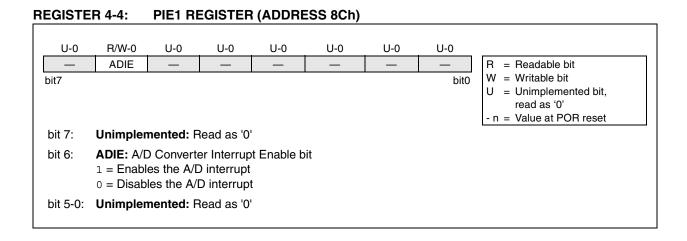

| 8Ch                  | PIE1   | _                  | ADIE                                          | _            | _             | —              | —               | —            | _           | -0                            | -0                                             |

| 8Dh                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | —                                              |

| 8Eh                  | PCON   | _                  | _                                             | _            | _             | _              | _               | POR          | _           | 0 -                           | u-                                             |

| 8Fh                  | OSCCAL | CAL3               | CAL2                                          | CAL1         | CAL0          | CALFST         | CALSLW          | _            | _           | 0111 00                       | uuuu uu                                        |

| 90h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | -                             | _                                              |

| 91h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | —                                              |

| 92h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | —                                              |

| 93h                  | _      | Unimpleme          | Inimplemented                                 |              |               |                |                 |              |             |                               | _                                              |

| 94h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | —                                              |

| 95h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | _                                              |

| 96h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | -                             | _                                              |

| 97h                  | —      | Unimpleme          | nted                                          |              |               |                |                 |              |             | -                             | —                                              |

| 98h                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | -                             | _                                              |

| 99h                  | —      | Unimpleme          | Inimplemented                                 |              |               |                |                 |              |             |                               | —                                              |

| 9Ah                  | —      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | _                                              |

| 9Bh                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | -                             | _                                              |

| 9Ch                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | _                                              |

| 9Dh                  | —      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | _                                              |

| 9Eh                  | _      | Unimpleme          | nted                                          |              |               |                |                 |              |             | _                             | _                                              |

| 9Fh                  | ADCON1 | _                  | _                                             | _            | _             | —              | PCFG2           | PCFG1        | PCFG0       | 000                           | 000                                            |

### TABLE 4-1: PIC12C67X SPECIAL FUNCTION REGISTER SUMMARY (CONT.)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC12C67X; always maintain these bits clear.

5: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the Peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

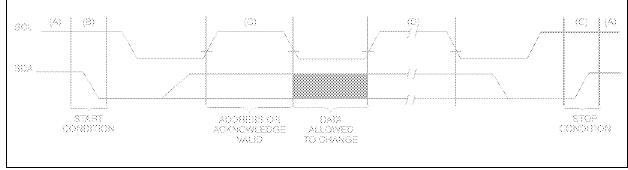

#### 6.1.5 ACKNOWLEDGE

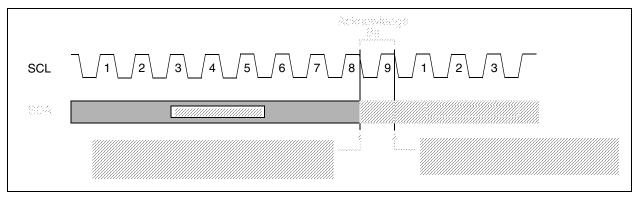

The EEPROM, when addressed, will generate an acknowledge after the reception of each byte. The processor must generate an extra clock pulse which is associated with this acknowledge bit.

**Note:** Acknowledge bits are not generated if an internal programming cycle is in progress.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. The processor must signal an end of data to the EEPROM by not generating an acknowledge bit on the last byte that has been clocked out of the EEPROM. In this case, the EEPROM must leave the data line HIGH to enable the processor to generate the STOP condition (Figure 6-4).

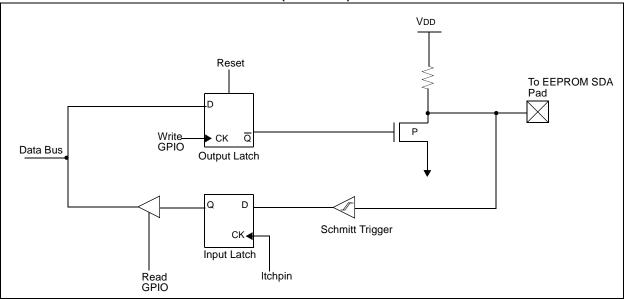

FIGURE 6-1: BLOCK DIAGRAM OF GPIO6 (SDA LINE)

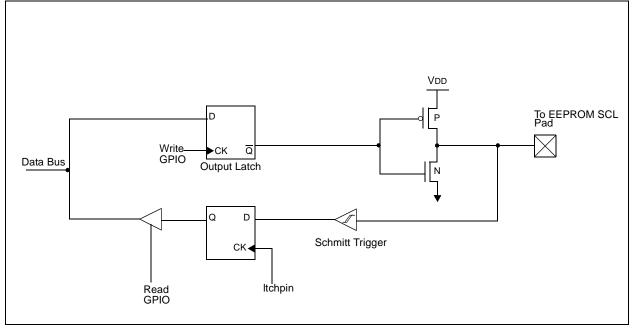

FIGURE 6-2: BLOCK DIAGRAM OF GPIO7 (SCL LINE)

FIGURE 6-4: ACKNOWLEDGE TIMING

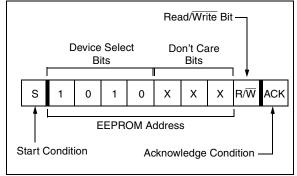

# 6.2 Device Addressing

After generating a START condition, the processor transmits a control byte consisting of a EEPROM address and a Read/Write bit that indicates what type of operation is to be performed. The EEPROM address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one, a read operation is selected, and when set to a zero, a write operation is selected (Figure 6-5). The bus is monitored for its corresponding EEPROM address all the time. It generates an acknowledge bit if the EEPROM address was true and it is not in a programming mode.

NOTES:

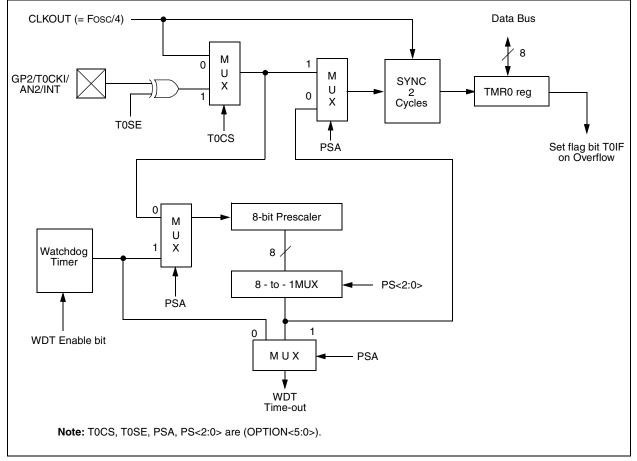

#### 7.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x..., etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

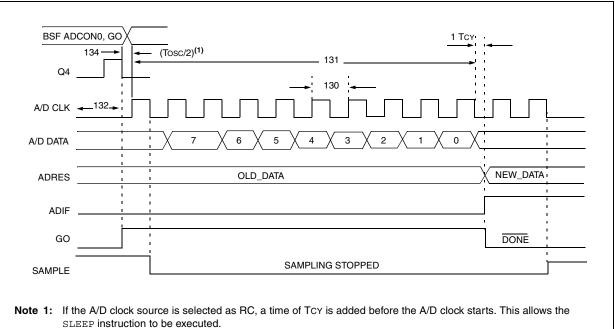

# 8.4 <u>A/D Conversions</u>

;

;

;

Example 8-2 shows how to perform an A/D conversion. The GPIO pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled and the A/D conversion clock is FRC. The conversion is performed on the GP0 channel.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

# EXAMPLE 8-2: DOING AN A/D CONVERSION

| BSF         | STATUS,   | RP0          | ;  | Select Page 1                                       |

|-------------|-----------|--------------|----|-----------------------------------------------------|

| CLRF        | ADCON1    |              | ;  | Configure A/D inputs                                |

| BSF         | PIE1,     | ADIE         | ;  | Enable A/D interrupts                               |

| BCF         | STATUS,   | RP0          | ;  | Select Page 0                                       |

| MOVLW       | 0xC1      |              | ;  | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF       | ADCON0    |              | ;  |                                                     |

| BCF         | PIR1,     | ADIF         | ;  | Clear A/D interrupt flag bit                        |

| BSF         | INTCON,   | PEIE         | ;  | Enable peripheral interrupts                        |

| BSF         | INTCON,   | GIE          | ;  | Enable all interrupts                               |

|             |           |              |    |                                                     |

| Ensure that | at the re | equired samp | li | ng time for the selected input channel has elapsed. |

Then the conversion may be started.

| BSF | ADCON0, GO | ; Start A/D Conversion                             |

|-----|------------|----------------------------------------------------|

| :   |            | ; The ADIF bit will be set and the GO/DONE bit     |

| :   |            | ; is cleared upon completion of the A/D Conversion |

# 9.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC12C67X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

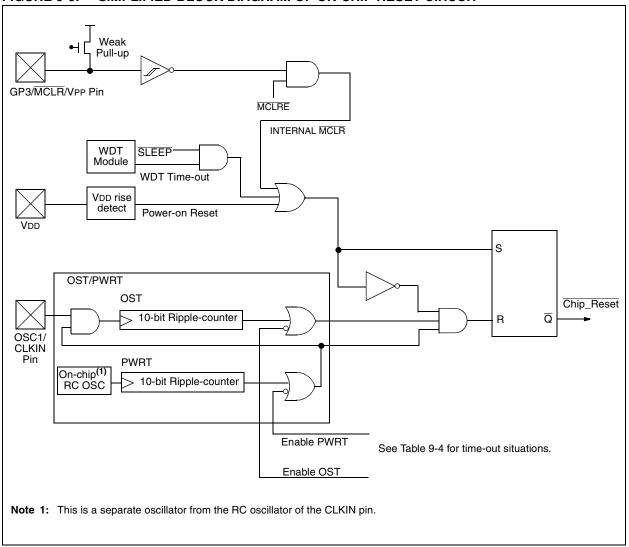

The PIC12C67X has a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The INTRC/EXTRC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

# 9.1 <u>Configuration Bits</u>

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h-3FFFh), which can be accessed only during programming.

# REGISTER 9-1: CONFIGURATION WORD

|                                                                                                                                                                                                                                                                                                                                    | CD -1-0-                                                                                               |                                                                |                                                                |                                       |             |    |  |  |      | Address  | 2007h  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------|-------------|----|--|--|------|----------|--------|

|                                                                                                                                                                                                                                                                                                                                    | 1.861.05                                                                                               | • Code                                                         |                                                                | ection k                              | hit nairs(1 | 1) |  |  | bit0 | 71001000 | 200711 |

| <ul> <li>bit 13-8, CP&lt;1:0&gt;: Code Protection bit pairs<sup>(1)</sup></li> <li>6-5: 11 = Code protection off</li> <li>10 = Locations 400h through 7FEh code protected (do not use for PIC12C671 and PIC12CE673)</li> <li>01 = Locations 200h through 7FEh code protected</li> <li>00 = All memory is code protected</li> </ul> |                                                                                                        |                                                                |                                                                |                                       |             |    |  |  |      |          |        |

|                                                                                                                                                                                                                                                                                                                                    |                                                                                                        |                                                                |                                                                |                                       |             |    |  |  |      |          |        |

|                                                                                                                                                                                                                                                                                                                                    | <b>PWRTE:</b> Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                       |                                                                |                                                                |                                       |             |    |  |  |      |          |        |

|                                                                                                                                                                                                                                                                                                                                    | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                 |                                                                |                                                                |                                       |             |    |  |  |      |          |        |

|                                                                                                                                                                                                                                                                                                                                    | FOSC<2<br>111 = EX<br>110 = EX<br>101 = IN<br>100 = IN<br>011 = In<br>010 = HS<br>001 = XT<br>000 = LF | KTRC,<br>KTRC,<br>TRC,<br>TRC,<br>Valid S<br>S Osci<br>F Oscil | Clocko<br>OSC2<br>Clocko<br>OSC2<br>electio<br>Ilator<br>lator | out on<br>is I/O<br>ut on 0<br>is I/O | OSC2        | S  |  |  |      |          |        |

# 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC12C67X can be operated in seven different oscillator modes. The user can program three configuration bits (Fosc<2:0>) to select one of these seven modes:

- LP: Low Power Crystal

- HS: High Speed Crystal/Resonator

- XT: Crystal/Resonator

- INTRC\*: Internal 4 MHz Oscillator

- EXTRC\*: External Resistor/Capacitor

\*Can be configured to support CLKOUT

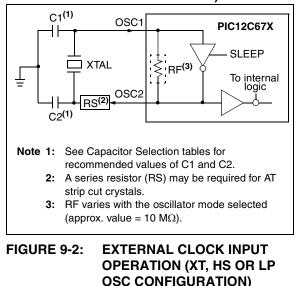

# 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

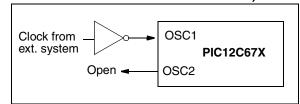

In XT, HS or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 9-1). The PIC12C67X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, HS or LP modes, the device can have an external clock source drive the GP5/OSC1/CLKIN pin (Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT, HS OR LP OSC CONFIGURATION)

#### TABLE 9-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C67X

| Osc<br>Type        | Resonator<br>Freq | Cap. Range<br>C1          | Cap. Range |

|--------------------|-------------------|---------------------------|------------|

| XT                 | 455 kHz           | 22-100,pF                 | 22-100 pF  |

|                    | 2.0 MHz           | 15-68 pf                  | レ15-68 pF  |

|                    | 4.0 MHz           | ~ { <b>1</b> ,5+68 pf ~ ~ | 15-68 pF   |

| HS                 | 4.0-MHX           | \ <b>15-68</b> pF         | 15-68 pF   |

|                    | 8,0 MHz           | 10-68 pF                  | 10-68 pF   |

| $\widehat{\Omega}$ | tp:0 MHz          | 10-22 pF                  | 10-22 pF   |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR - PIC12C67X

| - FICI2007X     |                       |                     |                        |  |  |  |  |

|-----------------|-----------------------|---------------------|------------------------|--|--|--|--|

| Osc<br>Type     | Resonator<br>Freq     | Cap. Range<br>C1    | Cap. Range<br>C2       |  |  |  |  |

| LP              | 32 kHz <sup>(1)</sup> | 15 pF               | 15 pF 🚽                |  |  |  |  |

|                 | 100 kHz               | 15-30 pF            | 30-47 p⊄               |  |  |  |  |

|                 | 200 kHz               | 15-30 pF            | 15-83 pF               |  |  |  |  |

| XT              | 100 kHz               | 15-30 pF            | 200-300 pF             |  |  |  |  |

|                 | 200 kHz               | 15-30 pE            | 100-200 pF             |  |  |  |  |

|                 | 455 kHz               | 15-30 pF            | <sup>™</sup> 15-100 pF |  |  |  |  |

|                 | 1 MHz 🔨               | 1,15-30.pF          | 15-30 pF               |  |  |  |  |

|                 | 2, MM,Hz ∖∖           | \ <b>∖</b> 15-30 pF | 15-30 pF               |  |  |  |  |

|                 | (AMHz)                | 15-47 pF            | 15-47 pF               |  |  |  |  |

| HS              | 4 10AHz               | 15-30 pF            | 15-30 pF               |  |  |  |  |

| $(\mathcal{O})$ | 🖓 🖇 MHz               | 15-30 pF            | 15-30 pF               |  |  |  |  |

| VZ Z            | 10 MHz                | 15-30 pF            | 15-30 pF               |  |  |  |  |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

FIGURE 9-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

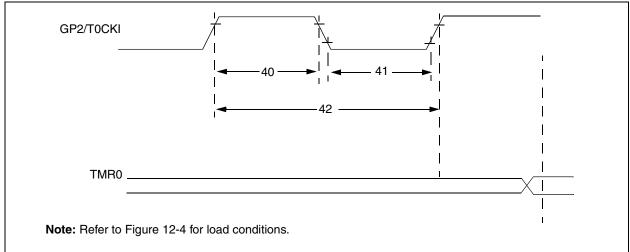

#### 9.5.1 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 7.0). The flag bit T0IF (INTCON<2>) will be set, regardless of the state of the enable bits. If used, this flag must be cleared in software.

#### 9.5.2 INT INTERRUPT

External interrupt on GP2/INT pin is edge triggered; either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the GP2/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP mode.

#### 9.5.3 GPIO INTCON CHANGE

An input change on GP3, GP1 or GP0 sets flag bit GPIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit GPIE (INTCON<3>) (Section 5.1). This flag bit GPIF (INTCON<0>) will be set, regardless of the state of the enable bits. If used, this flag must be cleared in software.

#### 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W register and STATUS register). This will have to be implemented in software.

Example 9-1 shows the storing and restoring of the STATUS and W registers. The register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

Example 9-2 shows the saving and restoring of STA-TUS and W using RAM locations 0x70 - 0x7F. W\_TEMP is defined at 0x70 and STATUS\_TEMP is defined at 0x71.

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

- f) Returns from interrupt.

# EXAMPLE 9-1: SAVING STATUS AND W REGISTERS USING GENERAL PURPOSE RAM (0x20 - 0x6F)

|                | W_TEMP<br>STATUS,W<br>STATUS,RP0<br>STATUS_TEMP |                                                                                                                                                                      |

|----------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>SWAPF | _<br>STATUS<br>W_TEMP,F                         | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)<br>;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W<br>;Return from interrupt |

|                |                                                 |                                                                                                                                                                      |

| EXAMPLE 9-2:   | SAVING STATUS                                   | AND W REGISTERS USING SHARED RAM (0x70 - 0x7F)                                                                                                                       |

| MOVWF<br>MOVF  | W_TEMP<br>STATUS,W                              | AND W REGISTERS USING SHARED RAM (0x70 - 0x7F)<br>;Copy W to TEMP register (bank independent)<br>;Move STATUS register into W<br>;Save contents of STATUS register   |

| BTFSS                                                                                                    | Bit Test f, Skip if Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Operands:                                                                                                | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Operation:                                                                                               | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Status Affected:                                                                                         | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Encoding:                                                                                                | 01 11bb bfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Description:                                                                                             | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a 2 cycle instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Cycles:                                                                                                  | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Example                                                                                                  | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CO<br>TRUE • DE<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                          | PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                          | if FLAG<1> = 1,<br>PC = address TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CALL                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CALL<br>Syntax:                                                                                          | PC = address TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                          | PC = address TRUE Call Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Syntax:                                                                                                  | PC = address TRUE  Call Subroutine [label] CALL k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Syntax:<br>Operands:                                                                                     | PC = address TRUE<br>Call Subroutine<br>[ label ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Syntax:<br>Operands:<br>Operation:                                                                       | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11><br>None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | PC =address TRUECall Subroutine[ label ] CALL k $0 \le k \le 2047$ (PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>None100kkkkkkkLog Rest (PC+1) is pushed onto<br>the stack. The eleven bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is                                                                                                                                                                                                                                                                                                                                                                                 |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k \\ 0 \le k \le 2047 \\ (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0 >, \\ (PCLATH < 4:3 >) \rightarrow PC < 12:11 > \\ \hline None \\ \hline 10 0 kkk kkk kkk \\ \hline Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits < 10:0 >. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. \\ \hline \end{tabular}$                                                                                                                                                                                                                                                |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $PC = address TRUE$ $[label] CALL k$ $0 \le k \le 2047$ $(PC)+1 \rightarrow TOS, k \rightarrow PC < 12:11 >$ $PC = Call Subroutine, brist, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits < 10:0 >. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction.$                                                                                                                                                                                                                                                                                                                                                                                                   |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k \\ 0 \le k \le 2047 \\ (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<4:3>) \rightarrow PC<12:11> \\ \hline None \\ \hline 10  0kkk  kkkk  kkkk \\ \hline Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. \\ 1 \\ 2 \\ HERE  CALL \\ \underline{THER} \\ \hline HERE \\ \hline \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ |

| CLRF             | Clear f                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                                                                                          |

| Operands:        | $0 \leq f \leq 127$                                                                                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                   |

| Status Affected: | Z                                                                                                                                       |

| Encoding:        | 00 0001 1fff ffff                                                                                                                       |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                                                                          |

| Words:           | 1                                                                                                                                       |

| Cycles:          | 1                                                                                                                                       |

| Example          | CLRF FLAG_REG                                                                                                                           |

|                  | $\begin{array}{rcl} Before \ Instruction \\ FLAG_REG & = & 0x5A \\ After \ Instruction \\ FLAG_REG & = & 0x00 \\ Z & = & 1 \end{array}$ |

| CLRW             | Clear W                                                              |                       |            |           |

|------------------|----------------------------------------------------------------------|-----------------------|------------|-----------|

| Syntax:          | [ label ]                                                            | CLRW                  |            |           |

| Operands:        | None                                                                 |                       |            |           |

| Operation:       | $\begin{array}{c} 00h \rightarrow (V \\ 1 \rightarrow Z \end{array}$ | V)                    |            |           |

| Status Affected: | Z                                                                    |                       |            |           |

| Encoding:        | 00                                                                   | 0001                  | 0000       | 0011      |

| Description:     | W registe<br>is set.                                                 | er is cle             | ared. Zero | o bit (Z) |

| Words:           | 1                                                                    |                       |            |           |

| Cycles:          | 1                                                                    |                       |            |           |

| Example          | CLRW                                                                 |                       |            |           |

|                  | Before In                                                            | structio<br>W =       | on<br>0x5A |           |

|                  |                                                                      | ruction<br>W =<br>Z = | 0x00<br>1  |           |

TABLE 11-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                   |                                                                                                                                                                                                                                                                       | PIC12CXXX                | PIC14000                 | PIC16C5X    | PIC16C6X  | PIC16CXXX  | PIC16F62X | PIC16C7X       | XX7Oðfolg | PIC16C8X  | PIC16F8XX  | PIC16C9XX | PIC17C4X | XXTOTIOI9  | PIC18CXX2 | 63CXX<br>52CXX/<br>54CXX/ | хххэн      | МСВЕХХХ    | MCP2510 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|-------------|-----------|------------|-----------|----------------|-----------|-----------|------------|-----------|----------|------------|-----------|---------------------------|------------|------------|---------|

| ≥ ∩<br>s oo_      | MPLAB <sup>®</sup> Integrated<br>Development Environment                                                                                                                                                                                                              | >                        | >                        | >           | >         | >          | >         | >              | >         | >         | >          | >         | >        | >          | >         |                           |            |            |         |

|                   | MPLAB <sup>®</sup> C17 Compiler                                                                                                                                                                                                                                       |                          |                          |             |           |            |           |                |           |           |            |           | >        | >          |           |                           |            |            |         |

|                   | MPLAB <sup>®</sup> C18 Compiler                                                                                                                                                                                                                                       |                          |                          |             |           |            |           |                |           |           |            |           |          |            | >         |                           |            |            |         |

|                   | MPASM/MPLINK                                                                                                                                                                                                                                                          | >                        | ~                        | >           | >         | >          | >         | >              | >         | >         | >          | >         | >        | >          | >         | >                         | >          |            |         |

|                   | MPLAB <sup>®</sup> -ICE                                                                                                                                                                                                                                               | >                        | ~                        | >           | >         | >          | ** `      | >              | >         | >         | >          | >         | >        | >          | >         |                           |            |            |         |

|                   | PICMASTER/PICMASTER-CE                                                                                                                                                                                                                                                | `                        | ~                        | >           | >         | >          |           | >              | >         | >         |            | >         | ~        | >          |           |                           |            |            |         |

| nm⊒               | ICEPIC™ Low-Cost<br>In-Circuit Emulator                                                                                                                                                                                                                               | ~                        |                          | >           | >         | >          |           | >              | >         | >         |            | >         |          |            |           |                           |            |            |         |

| ם ≤<br>Depnââeı   | MPLAB <sup>®</sup> -ICD In-Circuit<br>Debugger                                                                                                                                                                                                                        |                          |                          |             | *>        |            |           | *>             |           |           | >          |           |          |            |           |                           |            |            |         |

|                   | PICSTART <sup>®</sup> Plus<br>Low-Cost Universal Dev. Kit                                                                                                                                                                                                             | >                        | >                        | >           | >         | >          | **^       | >              | `         | >         | >          | >         | `        | >          | `         |                           |            |            |         |

| с ⊐<br>Ргодгат    | PRO MATE <sup>®</sup> II<br>Universal Programmer                                                                                                                                                                                                                      | >                        | >                        | >           | >         | >          | **^       | >              | >         | >         | >          | >         | >        | >          | >         | >                         | >          |            |         |

| S                 | SIMICE                                                                                                                                                                                                                                                                | >                        |                          | >           |           |            |           |                |           | <u> </u>  |            |           |          |            |           |                           |            |            |         |

| 4                 | PICDEM-1                                                                                                                                                                                                                                                              |                          |                          | >           |           | >          |           | ۲ <sup>+</sup> |           | >         |            |           | >        |            |           |                           |            |            |         |

| ₽.                | PICDEM-2                                                                                                                                                                                                                                                              |                          |                          |             | à         |            |           | à              |           |           |            |           |          |            | >         |                           |            |            |         |

|                   | PICDEM-3                                                                                                                                                                                                                                                              |                          |                          |             |           |            |           |                |           |           |            | ~         |          |            |           |                           |            |            |         |

| ם<br>Pl K         | PICDEM-14A                                                                                                                                                                                                                                                            |                          | ~                        |             |           |            |           |                |           |           |            |           |          |            |           |                           |            |            |         |

|                   | PICDEM-17                                                                                                                                                                                                                                                             |                          |                          |             |           |            |           |                |           |           |            |           |          | >          |           |                           |            |            |         |

|                   | KEELoo <sup>®</sup> Evaluation Kit                                                                                                                                                                                                                                    |                          |                          |             |           |            |           |                |           |           |            |           |          |            |           |                           | >          |            |         |

|                   | KEELoo Transponder Kit                                                                                                                                                                                                                                                |                          |                          |             |           |            |           |                |           |           |            |           |          |            |           |                           | >          |            |         |

|                   | microlD™ Programmer's Kit                                                                                                                                                                                                                                             |                          |                          |             |           |            |           |                |           |           |            |           |          |            |           |                           |            | ~          |         |

|                   | 125 kHz microID Developer's Kit                                                                                                                                                                                                                                       |                          |                          |             |           |            |           |                |           |           |            |           |          |            |           |                           |            | ~          |         |

|                   | 125 kHz Anticollision microlD<br>Developer's Kit                                                                                                                                                                                                                      |                          |                          |             |           |            |           |                |           |           |            |           |          |            |           |                           |            | >          |         |

| - 0               | 13.56 MHz Anticollision microlD<br>Developer's Kit                                                                                                                                                                                                                    |                          |                          |             |           |            |           |                |           |           |            |           |          |            |           |                           |            | >          |         |

| ž                 | MCP2510 CAN Developer's Kit                                                                                                                                                                                                                                           |                          |                          |             |           |            |           |                |           |           |            |           |          |            |           |                           |            |            | >       |

| * *<br>C C<br>O O | * Contact the Microchip Technology Inc. web site at www.microchip.com for information on how to use the MPLAB <sup>®</sup> -ICD In-Circuit Debugger (DV164001) with PIC16C62, 63, 64, 65, 72, 73, 74, 76, ** Contact Microchip Technology Inc. for availability date. | nc. web si<br>or availab | te at www<br>ility date. | ı. microchi | p.com for | informatic | woh no n  | to use the     | e MPLAB   | B-ICD In- | -Circuit D | ebugger ( | DV16400  | 1) with PI | C16C62,   | 63, 64, 6                 | 5, 72, 73, | 74, 76, 77 | ~       |

\*\* Contact Microchip Technology Inc. for availability <sup>†</sup> Development tool is available on select devices.

NOTES:

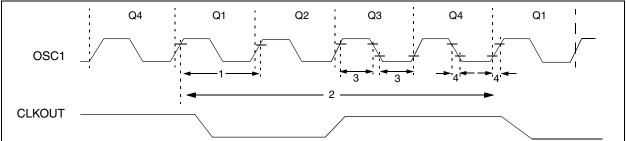

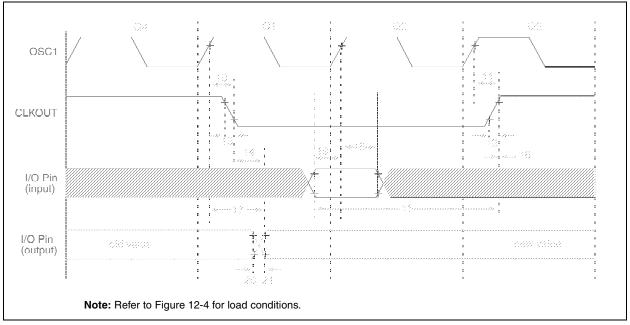

# 12.6 <u>Timing Diagrams and Specifications</u>

# TABLE 12-1: CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                  | Min  | Тур† | Max    | Units | Conditions                  |

|------------------|-------|---------------------------------|------|------|--------|-------|-----------------------------|

|                  | Fosc  | External CLKIN Frequency        | DC   | _    | 4      | MHz   | XT and EXTRC osc mode       |

|                  |       | (Note 1)                        | DC   | —    | 4      | MHz   | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | DC   | —    | 10     | MHz   | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | DC   | _    | 200    | kHz   | LP osc mode                 |

|                  |       | Oscillator Frequency            | DC   | _    | 4      | MHz   | EXTRC osc mode              |

|                  |       | (Note 1)                        | .455 | —    | 4      | MHz   | XT osc mode                 |

|                  |       |                                 | 4    | —    | 4      | MHz   | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 4    | —    | 10     | MHz   | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | —    | 200    | kHz   | LP osc mode                 |

| 1                | Tosc  | External CLKIN Period           | 250  | _    | _      | ns    | XT and EXTRC osc mode       |

|                  |       | (Note 1)                        | 250  | _    | _      | ns    | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 100  | —    |        | ns    | HS osc mode (PIC12CE67X-10) |