Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                |                                                                             |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 8-SOIJ                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c671t-04e-sm |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12C67X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C67X uses a Harvard architecture, in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses also allow instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single instruction cycle. A two-stage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), and non-volatile memory (EEPROM) for each PIC12C67X device.

| Device     | Program<br>Memory | RAM Data<br>Memory | EEPROM<br>Data<br>Memory |

|------------|-------------------|--------------------|--------------------------|

| PIC12C671  | 1K x 14           | 128 x 8            | —                        |

| PIC12C672  | 2K x 14           | 128 x 8            | —                        |

| PIC12CE673 | 1K x 14           | 128 x 8            | 16x8                     |

| PIC12CE674 | 2K x 14           | 128 x 8            | 16x8                     |

The PIC12C67X can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC12C67X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C67X simple yet efficient. In addition, the learning curve is reduced significantly.

PIC12C67X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 Register overflow, GPIO port change and external GP2/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

### REGISTER 4-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0                                      | R/W-0        | R/W-0       | R/W-0       | R/W-0                             | R/W-0       | R/W-x        |                                                                                                           |

|-------------|--------------------------------------------|--------------|-------------|-------------|-----------------------------------|-------------|--------------|-----------------------------------------------------------------------------------------------------------|

| GIE<br>bit7 | PEIE                                       | TOIE         | INTE        | GPIE        | TOIF                              | INTF        | GPIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:      | <b>GIE:</b> Glob<br>1 = Enabl<br>0 = Disab | es all un-r  | nasked in   |             |                                   |             |              |                                                                                                           |

| bit 6:      | PEIE: Per<br>1 = Enabl<br>0 = Disab        | es all un-r  | nasked pe   | ripheral ir | iterrupts                         |             |              |                                                                                                           |

| bit 5:      | <b>TOIE:</b> TMI<br>1 = Enabl<br>0 = Disab | es the TM    | R0 interru  | ıpt         | bit                               |             |              |                                                                                                           |

| bit 4:      |                                            | es the ext   | ernal inter | rupt on GI  | P2/INT/T00<br>P2/INT/T00          |             |              |                                                                                                           |

| bit 3:      | <b>GPIE:</b> GP<br>1 = Enabl<br>0 = Disab  | es the GP    | IO Interru  | pt on Cha   | nge                               |             |              |                                                                                                           |

| bit 2:      | <b>TOIF:</b> TMR<br>1 = TMRC<br>0 = TMRC   | ) register h | as overflo  | wed (mus    | t be cleare                       | d in softwa | re)          |                                                                                                           |

| bit 1:      |                                            | xternal int  | errupt on   | GP2/INT/1   | TOCKI/AN2<br>TOCKI/AN2            |             |              | e cleared in software)                                                                                    |

| bit 0:      |                                            | GP1 or Gl    | P3 pins ch  | anged sta   | bit<br>ite (must be<br>ve changed |             | n software)  |                                                                                                           |

## **PIC12C67X**

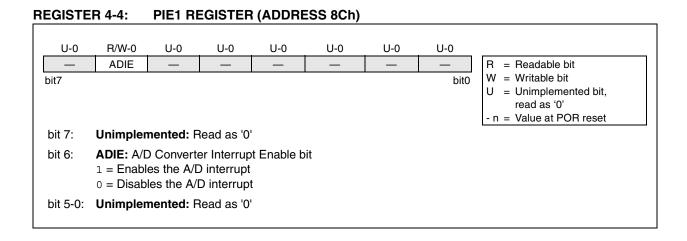

### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the Peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

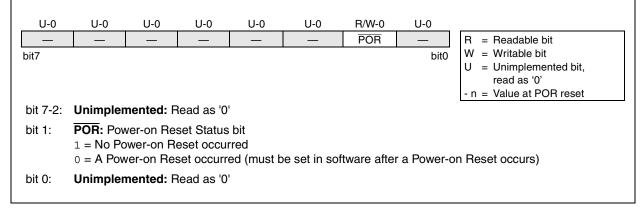

### 4.2.2.6 PCON REGISTER

The Power Control (PCON) Register contains a flag bit to allow differentiation between a Power-on Reset (POR), an external MCLR Reset and a WDT Reset.

### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

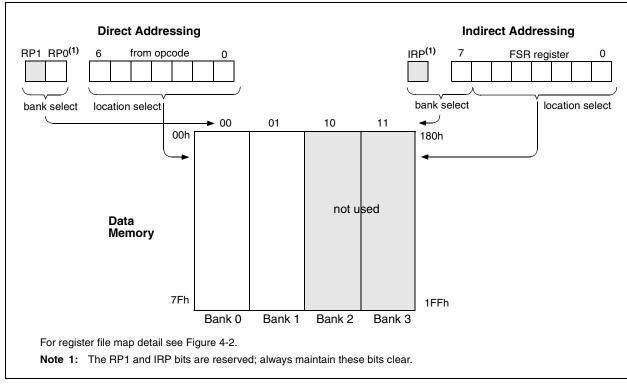

### 4.5 Indirect Addressing, INDF and FSR Registers

The INDF Register is not a physical register. Addressing the INDF Register will cause indirect addressing.

Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF Register itself indirectly (FSR = '0') will read 00h. Writing to the INDF Register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR Register and the IRP bit (STATUS<7>), as shown in Figure 4-4. However, IRP is not used in the PIC12C67X.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-1.

### EXAMPLE 4-1: INDIRECT ADDRESSING

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ;to RAM              |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR,F | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

### FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

### 5.0 I/O PORT

As with any other register, the I/O register can be written and read under program control. However, read instructions (i.e., MOVF GPIO, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance), since the I/O control registers are all set.

### 5.1 <u>GPIO</u>

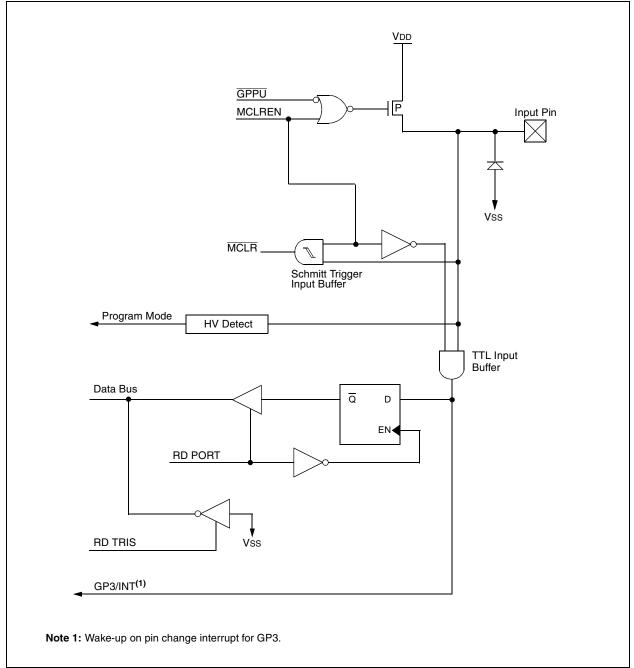

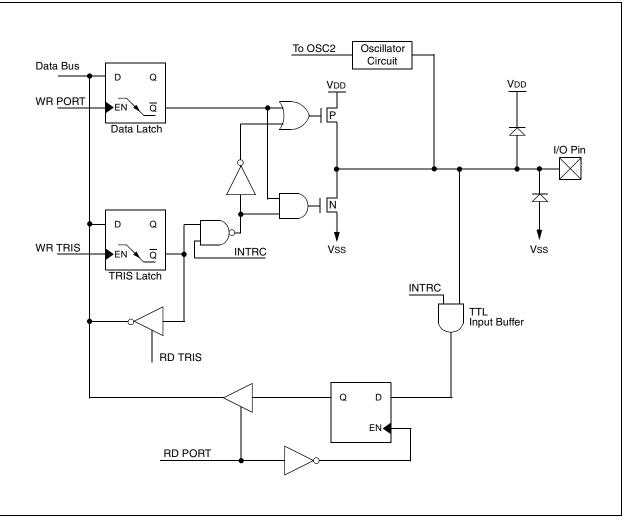

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP<5:0>). Bits 6 and 7 (SDA and SCL. respectively) are used by the EEPROM peripheral on the PIC12CE673/674. Refer to Section 6.0 and Appendix B for use of SDA and SCL. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during port read. Pins GP0, GP1 and GP3 can be configured with weak pull-ups and also with interrupt-on-change. The interrupt on change and weak pull-up functions are not pin selectable. If pin 4, (GP3), is configured as MCLR, a weak pull-up is always on. Interrupt-on-change for this pin is not set and GP3 will read as '0'. Interrupt-onchange is enabled by setting bit GPIE, INTCON<3>. Note that external oscillator use overrides the GPIO functions on GP4 and GP5.

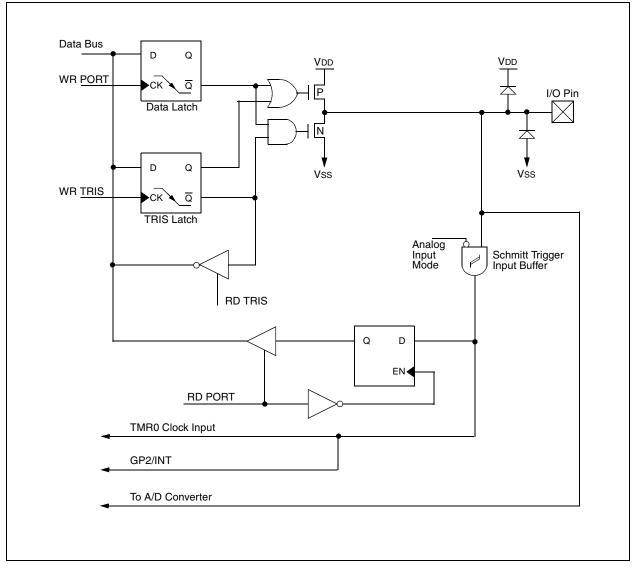

### 5.2 TRIS Register

This register controls the data direction for GPIO. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3, which is input only and its TRIS bit will always read as '1', while GP6 and GP7 TRIS bits will read as '0'.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

Upon reset, the TRIS Register is all '1's, making all pins inputs.

TRIS for pins GP4 and GP5 is forced to a '1' where appropriate. Writes to TRIS <5:4> will have an effect in EXTRC and INTRC oscillator modes only. When GP4 is configured as CLKOUT, changes to TRIS<4> will have no effect.

### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1 through Figure 5-5. All port pins, except GP3, which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (i.e., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

Port pins GP6 (SDA) and GP7 (SCL) are used for the serial EEPROM interface on the PIC12CE673/674. These port pins are not available externally on the package. Users should avoid writing to pins GP6 (SDA) and GP7 (SCL) when not communicating with the serial EEPROM memory. Please see Section 6.0, EEPROM Peripheral Operation, for information on serial EEPROM communication.

Note: On a Power-on Reset, GP0, GP1, GP2 and GP4 are configured as analog inputs and read as '0'.

FIGURE 5-2: BLOCK DIAGRAM OF GP2/T0CKI/AN2/INT PIN

### FIGURE 5-5: BLOCK DIAGRAM OF GP5/OSC1/CLKIN PIN

### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

### EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

### EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

### TABLE 7-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7                    | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|--------------------------|--------|-------|-------|-------|-------|-------|-----------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 module's register |        |       |       |       |       |       | xxxx xxxx | uuuu uuuu       |                                 |

| 0Bh/8Bh | INTCON | GIE                      | PEIE   | TOIE  | INTE  | GPIE  | TOIF  | INTF  | GPIF      | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | GPPU                     | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0       | 1111 1111       | 1111 1111                       |

| 85h     | TRIS   | _                        |        | TRIS5 | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0     | 11 1111         | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

NOTES:

# **PIC12C67X**

| IORWF            | Inclusive OR W with f                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                         |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                         |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in regis-<br>ter 'f'. |

| Words:           | 1                                                                                                                                                                         |

| Cycles:          | 1                                                                                                                                                                         |

| Example          | IORWF RESULT, 0                                                                                                                                                           |

|                  | Before Instruction<br>RESULT = $0x13$<br>W = $0x91$<br>After Instruction<br>RESULT = $0x13$<br>W = $0x93$<br>Z = $1$                                                      |

| MOVLW            | Move Literal to W                                                                                |                |      |      |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------|----------------|------|------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |                |      |      |  |  |  |  |

| Operands:        | $0 \le k \le 25$                                                                                 | 55             |      |      |  |  |  |  |

| Operation:       | $k \to (W)$                                                                                      |                |      |      |  |  |  |  |

| Status Affected: | None                                                                                             |                |      |      |  |  |  |  |

| Encoding:        | 11                                                                                               | 00xx           | kkkk | kkkk |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |                |      |      |  |  |  |  |

| Words:           | 1                                                                                                |                |      |      |  |  |  |  |

| Cycles:          | 1                                                                                                |                |      |      |  |  |  |  |

| Example          | MOVLW                                                                                            | 0x5A           |      |      |  |  |  |  |

|                  | After Inst                                                                                       | ruction<br>W = | 0x5A |      |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ , des-<br>tination is W register. If $d = 1$ , the<br>destination is file register f itself.<br>d = 1 is useful to test a file register<br>since status flag Z is affected. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                                                                            |  |  |  |  |  |  |

| MOVWF            | Move W                                          | to f        |             |                                      |      |  |

|------------------|-------------------------------------------------|-------------|-------------|--------------------------------------|------|--|

| Syntax:          | [ label ]                                       | MOVW        | = f         |                                      |      |  |

| Operands:        | $0 \le f \le 12$                                | 7           |             |                                      |      |  |

| Operation:       | $(W) \to (f)$                                   |             |             |                                      |      |  |

| Status Affected: | None                                            |             |             |                                      |      |  |

| Encoding:        | 0 0                                             | 0000        | 1ff         | f                                    | ffff |  |

| Description:     | Move data from W register to reg-<br>ister 'f'. |             |             |                                      |      |  |

| Words:           | 1                                               |             |             |                                      |      |  |

| Cycles:          | 1                                               |             |             |                                      |      |  |

| Example          | MOVWF                                           | OPT         | TION        |                                      |      |  |

|                  | After Inst                                      | OPTION<br>W | =<br>=<br>= | 0xFF<br>0x4F<br>0x4F<br>0x4F<br>0x4F | :    |  |

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

### 11.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 11.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

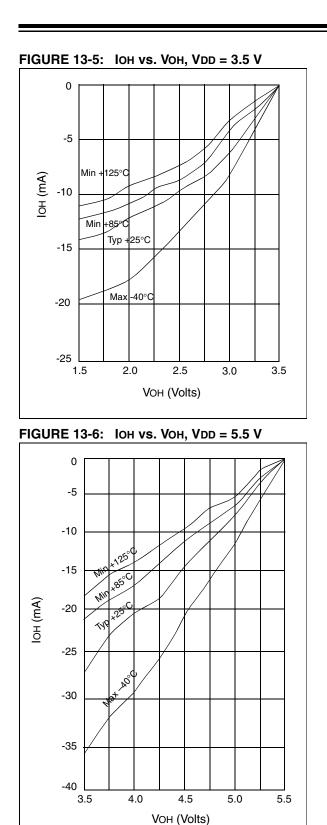

### 12.3 DC CHARACTERISTICS:

### PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

|       |                                    |                                                                                                                                   |                |      | -          |       |                                                              |  |  |

|-------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|------|------------|-------|--------------------------------------------------------------|--|--|

|       |                                    | Standard Operating Conditions (unless otherwise specified)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) |                |      |            |       |                                                              |  |  |

|       |                                    | Operati                                                                                                                           | ng temperature |      |            |       |                                                              |  |  |

| DC CH | ARACTERISTICS                      | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)                                                                               |                |      |            |       |                                                              |  |  |

|       |                                    | $-40^{\circ}C \le TA \le +125^{\circ}C \text{ (extended)}$                                                                        |                |      |            |       |                                                              |  |  |

|       |                                    | Operating voltage VDD range as described in DC spec Section 12.1 and                                                              |                |      |            |       |                                                              |  |  |

|       |                                    | Section 12.2.                                                                                                                     |                |      |            |       |                                                              |  |  |

| Param | Characteristic                     | Sym                                                                                                                               | Min            | Тур† | Max        | Units | Conditions                                                   |  |  |

| No.   |                                    |                                                                                                                                   |                |      |            |       |                                                              |  |  |

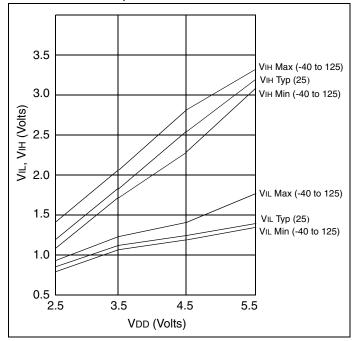

|       | Input Low Voltage                  |                                                                                                                                   |                |      |            |       |                                                              |  |  |

|       | I/O ports                          | Vi∟                                                                                                                               |                |      |            |       |                                                              |  |  |

| D030  | with TTL buffer                    |                                                                                                                                   | Vss            | —    | 0.8V       | V     | For $4.5V \le VDD \le 5.5V$                                  |  |  |

|       |                                    |                                                                                                                                   | Vss            | —    | 0.15Vdd    | V     | otherwise                                                    |  |  |

| D031  | with Schmitt Trigger buffer        |                                                                                                                                   | Vss            | —    | 0.2Vdd     | V     |                                                              |  |  |

| D032  | MCLR, GP2/T0CKI/AN2/INT            |                                                                                                                                   | Vss            | —    | 0.2Vdd     | V     |                                                              |  |  |

|       | (in EXTRC mode)                    |                                                                                                                                   |                |      |            |       |                                                              |  |  |

| D033  | OSC1 (in EXTRC mode)               |                                                                                                                                   | Vss            | —    | 0.2Vdd     |       | Note 1                                                       |  |  |

| D033  | OSC1 (in XT, HS, and LP)           |                                                                                                                                   | Vss            | —    | 0.3Vdd     | V     | Note 1                                                       |  |  |

|       | Input High Voltage                 |                                                                                                                                   |                |      |            |       |                                                              |  |  |

|       | I/O ports                          | Vін                                                                                                                               |                | _    |            |       |                                                              |  |  |

| D040  | with TTL buffer                    |                                                                                                                                   | 2.0V           | _    | Vdd        | v     | $4.5V \le VDD \le 5.5V$                                      |  |  |

| D040A |                                    |                                                                                                                                   | 0.25VDD + 0.8V | _    | Vdd        | v     | otherwise                                                    |  |  |

| D041  | with Schmitt Trigger buffer        |                                                                                                                                   | 0.8VDD         | _    | VDD        | v     | For entire VDD range                                         |  |  |

| D042  | MCLR. GP2/T0CKI/AN2/INT            |                                                                                                                                   | 0.8VDD         | _    | VDD        | v     |                                                              |  |  |

| D042A | OSC1 (XT, HS, and LP)              |                                                                                                                                   | 0.7VDD         |      | VDD        | V     | Note 1                                                       |  |  |

| D043  | OSC1 (in EXTRC mode)               |                                                                                                                                   | 0.9VDD         | _    | VDD        | v     |                                                              |  |  |

| 2010  | Input Leakage Current (Notes 2, 3) |                                                                                                                                   | 0.0755         |      |            | •     |                                                              |  |  |

| D060  | I/O ports                          | lı∟                                                                                                                               |                | _    | <u>+</u> 1 | μA    | Vss $\leq$ VPIN $\leq$ VDD, Pin at                           |  |  |

| 2000  |                                    |                                                                                                                                   |                |      | <u> </u>   | μι    | hi-impedance                                                 |  |  |

| D061  | GP3/MCLR (Note 5)                  |                                                                                                                                   |                |      | +30        | μA    | $VSS \leq VPIN \leq VDD$                                     |  |  |

| D061A | GP3 (Note 6)                       |                                                                                                                                   |                |      | +5         | μA    | $VSS \leq VPIN \leq VDD$                                     |  |  |

| D062  | GP2/T0CKI                          |                                                                                                                                   |                | _    |            | μA    | $VSS \leq VPIN \leq VDD$                                     |  |  |

| D063  | OSC1                               |                                                                                                                                   |                |      | <u>+</u> 5 | •     |                                                              |  |  |

| D063  | 0501                               |                                                                                                                                   | _              | _    | <u>+</u> 5 | μA    | VSS $\leq$ VPIN $\leq$ VDD, XT, HS, and LP osc configuration |  |  |

| D070  | GPIO weak pull-up current (Note 4) | IPUR                                                                                                                              | 50             | 250  | 400        | μA    | VDD = 5V, VPIN = VSS                                         |  |  |

|       | MCLR pull-up current               | —                                                                                                                                 | —              | —    | 30         | μA    | VDD = 5V, VPIN = VSS                                         |  |  |

|       | Output Low Voltage                 |                                                                                                                                   |                |      |            |       |                                                              |  |  |

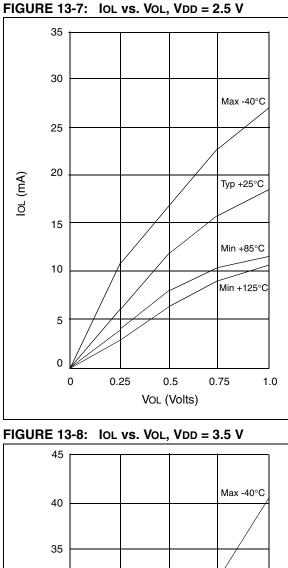

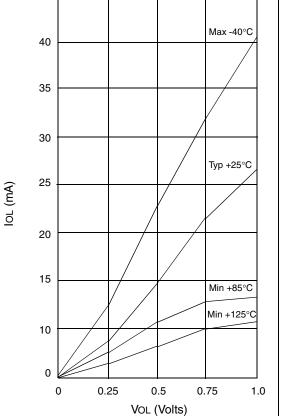

| D080  | I/O ports                          | Vol                                                                                                                               | —              | —    | 0.6        | V     | IOL = 8.5 mA, VDD = 4.5V,<br>−40°C to +85°C                  |  |  |

| D080A |                                    |                                                                                                                                   | —              | —    | 0.6        | V     | IOL = 7.0 mA, VDD = 4.5V,<br>−40°C to +125°C                 |  |  |

| D083  | OSC2/CLKOUT                        |                                                                                                                                   | —              | —    | 0.6        | V     | IOL = 1.6 mA, VDD = 4.5V,<br>−40°C to +85°C                  |  |  |

| D083A |                                    |                                                                                                                                   | _              |      | 0.6        | V     | IOL = 1.2 mA, VDD = 4.5V,<br>−40°C to +125°C                 |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as coming out of the pin.

- 4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

### 12.6 <u>Timing Diagrams and Specifications</u>

### TABLE 12-1: CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                  | Min  | Тур† | Max    | Units | Conditions                  |

|------------------|-------|---------------------------------|------|------|--------|-------|-----------------------------|

|                  | Fosc  | External CLKIN Frequency        | DC   | _    | 4      | MHz   | XT and EXTRC osc mode       |

|                  |       | (Note 1)                        | DC   | —    | 4      | MHz   | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | DC   | —    | 10     | MHz   | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | DC   | _    | 200    | kHz   | LP osc mode                 |

|                  |       | Oscillator Frequency            | DC   | _    | 4      | MHz   | EXTRC osc mode              |

|                  |       | (Note 1)                        | .455 | —    | 4      | MHz   | XT osc mode                 |

|                  |       |                                 | 4    | —    | 4      | MHz   | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 4    | —    | 10     | MHz   | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | —    | 200    | kHz   | LP osc mode                 |

| 1                | Tosc  | External CLKIN Period           | 250  | _    | _      | ns    | XT and EXTRC osc mode       |

|                  |       | (Note 1)                        | 250  | _    | _      | ns    | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 100  | —    |        | ns    | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | _    | _      | μs    | LP osc mode                 |

|                  |       | Oscillator Period               | 250  | —    | —      | ns    | EXTRC osc mode              |

|                  |       | (Note 1)                        | 250  | —    | 10,000 | ns    | XT osc mode                 |

|                  |       |                                 | 250  | —    | 250    | ns    | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 100  | —    | 250    | ns    | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | —    | —      | μs    | LP osc mode                 |

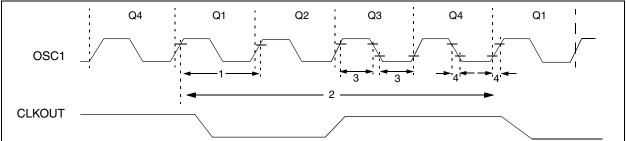

| 2                | Тсү   | Instruction Cycle Time (Note 1) | 400  | —    | DC     | ns    | TCY = 4/FOSC                |

| 3                | TosL, | External Clock in (OSC1) High   | 50   | —    | —      | ns    | XT oscillator               |

|                  | TosH  | or Low Time                     | 2.5  | —    | —      | μS    | LP oscillator               |

|                  |       |                                 | 10   | —    | —      | ns    | HS oscillator               |

| 4                | TosR, | External Clock in (OSC1) Rise   | —    | —    | 25     | ns    | XT oscillator               |

|                  | TosF  | or Fall Time                    | —    | —    | 50     | ns    | LP oscillator               |

|                  |       |                                 | —    | —    | 15     | ns    | HS oscillator               |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC12C67X.

FIGURE 13-11: VIL, VIH OF NMCLR AND TOCKI vs. VDD

## **PIC12C67X**

NOTES:

## PIC16XXXXX FAMILY

### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: |                                                                              | Total Pages Sent                  |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|--|

| Fror       | m: Name                                                                      |                                   |  |  |  |  |  |  |

|            | Company                                                                      |                                   |  |  |  |  |  |  |

|            | Address                                                                      |                                   |  |  |  |  |  |  |

|            | City / State / ZIP / Country                                                 |                                   |  |  |  |  |  |  |

|            | Telephone: ()                                                                | FAX: ()                           |  |  |  |  |  |  |

| Арр        | lication (optional):                                                         |                                   |  |  |  |  |  |  |

| Wou        | uld you like a reply? Y N                                                    |                                   |  |  |  |  |  |  |

| Dev        | vice: PIC16xxxxxx family                                                     | Literature Number: DS30561C       |  |  |  |  |  |  |

| Que        | estions:                                                                     |                                   |  |  |  |  |  |  |

| 1.         | 1. What are the best features of this document?                              |                                   |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

| 2.         | 2. How does this document meet your hardware and software development needs? |                                   |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

| 3.         | Do you find the organization of this document easy to follow? If not, why?   |                                   |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

| 4.         | What additions to the document do you think would enhar                      | ce the structure and subject?     |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

| _          |                                                                              | <i></i>                           |  |  |  |  |  |  |

| 5.         | What deletions from the document could be made without                       | affecting the overall usefulness? |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

| 6.         | Is there any incorrect or misleading information (what and                   | where)?                           |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

| 7.         | How would you improve this document?                                         |                                   |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12