Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c672-10e-sm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC12C67X devices are low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converter and EEPROM data memory (EEPROM on PIC12CE67X versions only).

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC12C67X microcontrollers have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches, which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC12C67X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC12C67X devices have 128 bytes of RAM, 16 bytes of EEPROM data memory (PIC12CE67X only), 5 I/O pins and 1 input pin. In addition a timer/counter is available. Also a 4-channel, high-speed, 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, (i.e., thermostat control, pressure sensing, etc.)

The PIC12C67X devices have special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. The Power-On Reset (POR), Power-up Timer (PWRT), and Oscillator Start-up Timer (OST) eliminate the need for external reset circuitry. There are five oscillator configurations to choose from, including INTRC precision internal oscillator mode and the power-saving LP (Low Power) oscillator mode. Power-saving SLEEP mode, Watchdog Timer and code protection features improve system cost, power and reliability. The SLEEP (power-down) feature provides a power-saving mode. The user can wake-up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

A UV erasable windowed package version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

#### 1.1 <u>Applications</u>

The PIC12C67X series fits perfectly in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The EPROM technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient, while the EEPROM data memory (PIC12CE67X only) technology allows for the changing of calibration factors and security codes. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC12C67X series very versatile even in areas where no microcontroller use has been considered before (i.e., timer functions, replacement of "glue" logic and PLD's in larger systems, coprocessor applications).

#### 1.2 Family and Upward Compatibility

The PIC12C67X products are compatible with other members of the 14-bit PIC16CXXX families.

### 1.3 Development Support

The PIC12C67X devices are supported by a fullfeatured macro assembler, a software simulator, an incircuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12C67X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12C67X uses a Harvard architecture, in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses also allow instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single instruction cycle. A two-stage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM), and non-volatile memory (EEPROM) for each PIC12C67X device.

| Device     | Program<br>Memory | RAM Data<br>Memory | EEPROM<br>Data<br>Memory |  |

|------------|-------------------|--------------------|--------------------------|--|

| PIC12C671  | 1K x 14           | 128 x 8            | —                        |  |

| PIC12C672  | 2K x 14           | 128 x 8            | —                        |  |

| PIC12CE673 | 1K x 14           | 128 x 8            | 16x8                     |  |

| PIC12CE674 | 2K x 14           | 128 x 8            | 16x8                     |  |

The PIC12C67X can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC12C67X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC12C67X simple yet efficient. In addition, the learning curve is reduced significantly.

PIC12C67X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| <b>TABLE 3-1:</b> | PIC12C67X PINOUT DESCRIPTION |

|-------------------|------------------------------|

|-------------------|------------------------------|

| Name                     | DIP Pin # | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|-----------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/AN0                  | 7         | I/O           | TTL/ST         | Bi-directional I/O port/serial programming data/analog input 0.<br>Can be software programmed for internal weak pull-up and<br>interrupt-on-pin change. This buffer is a Schmitt Trigger input<br>when used in serial programming mode.                                                                                                                                                                                |

| GP1/AN1/V <sub>REF</sub> | 6         | I/O           | TTL/ST         | Bi-directional I/O port/serial programming clock/analog input 1/<br>voltage reference. Can be software programmed for internal<br>weak pull-up and interrupt-on-pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming mode.                                                                                                                                                            |

| GP2/T0CKI/AN2/INT        | 5         | I/O           | ST             | Bi-directional I/O port/analog input 2. Can be configured as T0CKI or external interrupt.                                                                                                                                                                                                                                                                                                                              |

| GP3/MCLR/Vpp             | 4         | Ι             | TTL/ST         | Input port/master clear (reset) input/programming voltage<br>input. When configured as MCLR, this pin is an active low<br>reset to the device. Voltage on MCLR/VPP must not exceed<br>VDD during normal device operation. Can be software pro-<br>grammed for internal weak pull-up and interrupt-on-pin<br>change. Weak pull-up always on if configured as MCLR. This<br>buffer is Schmitt Trigger when in MCLR mode. |

| GP4/OSC2/AN3/CLKOUT      | 3         | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output/analog input 3.<br>Connections to crystal or resonator in crystal oscillator mode<br>(HS, XT and LP modes only, GPIO in other modes). In EXTRC<br>and INTRC modes, the pin output can be configured to CLK-<br>OUT, which has 1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.                                                                   |

| GP5/OSC1/CLKIN           | 2         | I/O           | TTL/ST         | Bi-directional IO port/oscillator crystal input/external clock<br>source input (GPIO in INTRC mode only, OSC1 in all other<br>oscillator modes). Schmitt trigger input for EXTRC oscillator<br>mode.                                                                                                                                                                                                                   |

| Vdd                      | 1         | Р             | _              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                |

| Vss                      | 8         | Р             | _              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                               |

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input.

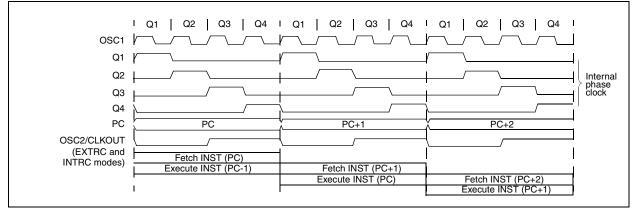

#### 3.1 Clocking Scheme/Instruction Cycle

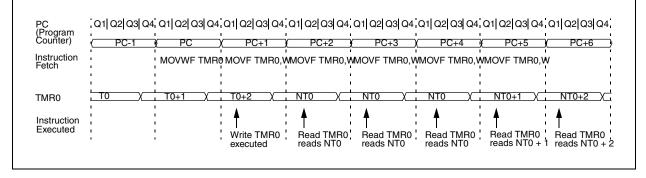

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

#### 3.2 Instruction Flow/Pipelining

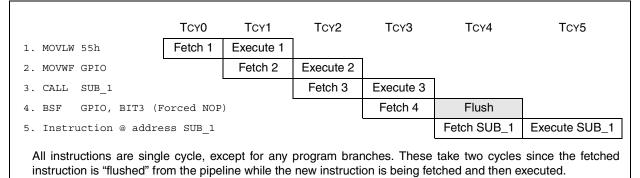

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

#### 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 Register overflow, GPIO port change and external GP2/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

## REGISTER 4-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0                                                                                                                                                                   | R/W-0        | R/W-0      | R/W-0     | R/W-0                             | R/W-0       | R/W-x        |                                                                                                           |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|-----------|-----------------------------------|-------------|--------------|-----------------------------------------------------------------------------------------------------------|--|

| GIE<br>bit7 | PEIE                                                                                                                                                                    | TOIE         | INTE       | GPIE      | TOIF                              | INTF        | GPIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7:      |                                                                                                                                                                         |              |            |           |                                   |             |              |                                                                                                           |  |

| bit 6:      |                                                                                                                                                                         |              |            |           |                                   |             |              |                                                                                                           |  |

| bit 5:      | bit 5: <b>T0IE:</b> TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                             |              |            |           |                                   |             |              |                                                                                                           |  |

| bit 4:      | bit 4: INT External Interrupt Enable bit<br>1 = Enables the external interrupt on GP2/INT/T0CKI/AN2 pin<br>0 = Disables the external interrupt on GP2/INT/T0CKI/AN2 pin |              |            |           |                                   |             |              |                                                                                                           |  |

| bit 3:      | bit 3: <b>GPIE:</b> GPIO Interrupt on Change Enable bit<br>1 = Enables the GPIO Interrupt on Change<br>0 = Disables the GPIO Interrupt on Change                        |              |            |           |                                   |             |              |                                                                                                           |  |

| bit 2:      | <b>TOIF:</b> TMR<br>1 = TMRC<br>0 = TMRC                                                                                                                                | ) register h | as overflo | wed (mus  | t be cleare                       | d in softwa | re)          |                                                                                                           |  |

| bit 1:      |                                                                                                                                                                         | xternal int  | errupt on  | GP2/INT/1 | TOCKI/AN2<br>TOCKI/AN2            |             |              | e cleared in software)                                                                                    |  |

| bit 0:      |                                                                                                                                                                         | GP1 or Gl    | P3 pins ch | anged sta | bit<br>ite (must be<br>ve changed |             | n software)  |                                                                                                           |  |

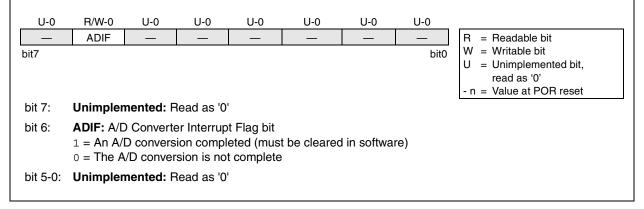

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the Peripheral interrupts.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 4-5: PIR1 REGISTER (ADDRESS 0Ch)

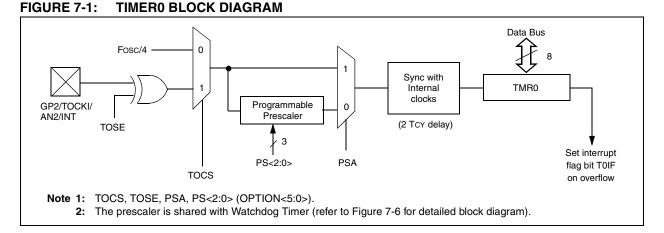

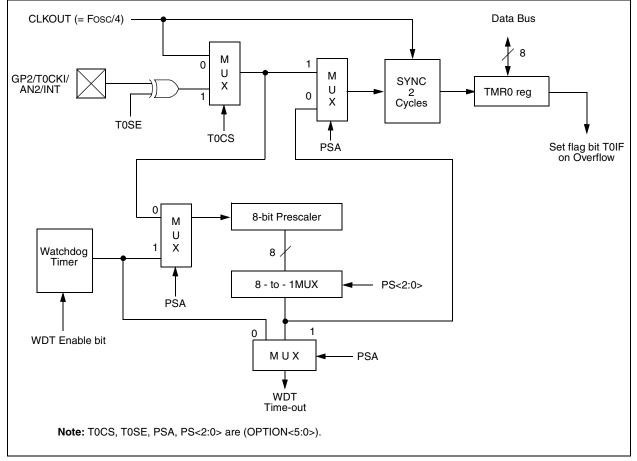

## 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/TOCKI. The incrementing edge is determined by the bit TOSE

(OPTION<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

#### 7.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x..., etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

## **PIC12C67X**

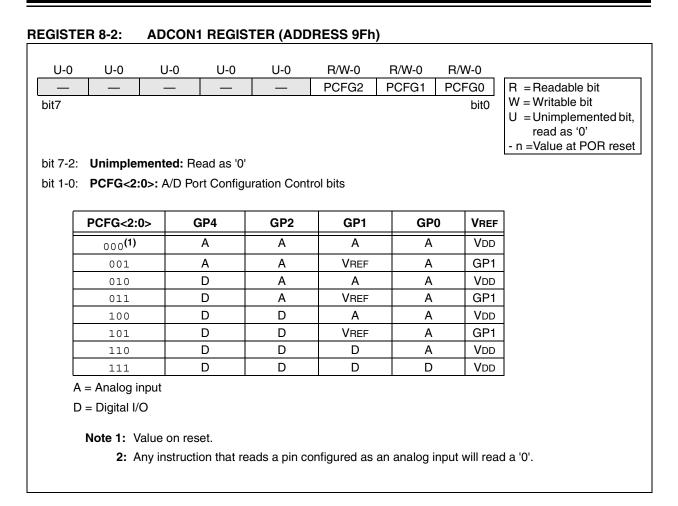

#### 8.4 <u>A/D Conversions</u>

;

;

;

Example 8-2 shows how to perform an A/D conversion. The GPIO pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled and the A/D conversion clock is FRC. The conversion is performed on the GP0 channel.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

#### EXAMPLE 8-2: DOING AN A/D CONVERSION

| BSF         | STATUS,   | RP0          | ;  | Select Page 1                                       |

|-------------|-----------|--------------|----|-----------------------------------------------------|

| CLRF        | ADCON1    |              | ;  | Configure A/D inputs                                |

| BSF         | PIE1,     | ADIE         | ;  | Enable A/D interrupts                               |

| BCF         | STATUS,   | RP0          | ;  | Select Page 0                                       |

| MOVLW       | 0xC1      |              | ;  | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF       | ADCON0    |              | ;  |                                                     |

| BCF         | PIR1,     | ADIF         | ;  | Clear A/D interrupt flag bit                        |

| BSF         | INTCON,   | PEIE         | ;  | Enable peripheral interrupts                        |

| BSF         | INTCON,   | GIE          | ;  | Enable all interrupts                               |

|             |           |              |    |                                                     |

| Ensure that | at the re | equired samp | li | ng time for the selected input channel has elapsed. |

Then the conversion may be started.

| BSF | ADCON0, GO | ; Start A/D Conversion                             |

|-----|------------|----------------------------------------------------|

| :   |            | ; The ADIF bit will be set and the GO/DONE bit     |

| :   |            | ; is cleared upon completion of the A/D Conversion |

# **PIC12C67X**

| IORWF            | Inclusive OR W with f                                                                                                                                                     |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                         |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |  |  |  |  |  |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                         |  |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in regis-<br>ter 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |  |  |  |  |

| Example          | IORWF RESULT, 0                                                                                                                                                           |  |  |  |  |  |  |  |

|                  | Before Instruction<br>RESULT = $0x13$<br>W = $0x91$<br>After Instruction<br>RESULT = $0x13$<br>W = $0x93$<br>Z = $1$                                                      |  |  |  |  |  |  |  |

| MOVLW            | Move Literal to W                    |                |            |      |  |  |  |  |

|------------------|--------------------------------------|----------------|------------|------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k             |                |            |      |  |  |  |  |

| Operands:        | $0 \le k \le 25$                     | 55             |            |      |  |  |  |  |

| Operation:       | $k \to (W)$                          |                |            |      |  |  |  |  |

| Status Affected: | None                                 |                |            |      |  |  |  |  |

| Encoding:        | 11                                   | 00xx           | kkkk       | kkkk |  |  |  |  |

| Description:     | The eight<br>into W re<br>will asser | gister. Th     | ne don't c |      |  |  |  |  |

| Words:           | 1                                    |                |            |      |  |  |  |  |

| Cycles:          | 1                                    |                |            |      |  |  |  |  |

| Example          | MOVLW                                | 0x5A           |            |      |  |  |  |  |

|                  | After Inst                           | ruction<br>W = | 0x5A       |      |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ , des-<br>tination is W register. If $d = 1$ , the<br>destination is file register f itself.<br>d = 1 is useful to test a file register<br>since status flag Z is affected. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                                                                            |  |  |  |  |  |  |

| MOVWF            | Move W                                          | to f        |             |                                      |      |  |  |  |

|------------------|-------------------------------------------------|-------------|-------------|--------------------------------------|------|--|--|--|

| Syntax:          | [ label ]                                       | MOVW        | = f         |                                      |      |  |  |  |

| Operands:        | $0 \le f \le 127$                               |             |             |                                      |      |  |  |  |

| Operation:       | $(W) \to (f)$                                   |             |             |                                      |      |  |  |  |

| Status Affected: | None                                            |             |             |                                      |      |  |  |  |

| Encoding:        | 0 0                                             | 0000        | 1ff         | f                                    | ffff |  |  |  |

| Description:     | Move data from W register to reg-<br>ister 'f'. |             |             |                                      |      |  |  |  |

| Words:           | 1                                               |             |             |                                      |      |  |  |  |

| Cycles:          | 1                                               |             |             |                                      |      |  |  |  |

| Example          | MOVWF                                           | OPT         | TION        |                                      |      |  |  |  |

|                  | After Inst                                      | OPTION<br>W | =<br>=<br>= | 0xFF<br>0x4F<br>0x4F<br>0x4F<br>0x4F | :    |  |  |  |

NOTES:

#### 12.2 DC Characteristics: PIC12LC671/672 (Commercial, Industrial) PIC12LCE673/674 (Commercial, Industrial)

| DC CHAF               |                                               | Standard Operating Conditions (unless otherwise specified)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ (commercial) $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial) |       |            |                  |          |                                                                                                                             |

|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                | Sym                                                                                                                                                                                       | Min   | Тур†       | Max              | Units    | Conditions                                                                                                                  |

| D001                  | Supply Voltage                                | Vdd                                                                                                                                                                                       | 2.5   |            | 5.5              | V        |                                                                                                                             |

| D002                  | RAM Data Retention<br>Voltage <sup>(2)</sup>  | Vdr                                                                                                                                                                                       |       | 1.5*       |                  | V        | Device in SLEEP mode                                                                                                        |

| D003                  | VDD Start Voltage to<br>ensure Power-on Reset | VPOR                                                                                                                                                                                      |       | Vss        |                  | V        | See section on Power-on Reset for details                                                                                   |

| D004                  | VDD Rise Rate to ensure<br>Power-on Reset     | SVDD                                                                                                                                                                                      | 0.05* |            |                  | V/ms     | See section on Power-on Reset for details                                                                                   |

| D010                  | Supply Current <sup>(3)</sup>                 | IDD                                                                                                                                                                                       | —     | 0.4        | 2.1              | mA       | Fosc = 4MHz, VDD = 2.5V<br>XT and EXTRC mode (Note 4)                                                                       |

| D010C<br>D010A        |                                               |                                                                                                                                                                                           | _     | 0.4<br>15  | 2.1<br>33        | mA<br>μA | Fosc = 4MHz, VDD = 2.5V<br>INTRC mode (Note 6)<br>Fosc = 32kHz, VDD = 2.5V, WDT disabled<br>LP mode, Industrial Temperature |

| D020<br>D021<br>D021B | Power-down Current <sup>(5)</sup>             | IPD                                                                                                                                                                                       | _     | 0.2<br>0.2 | 5<br>6           | μΑ<br>μΑ | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                                                                            |

|                       | Watchdog Timer Current                        | ΔIWDT                                                                                                                                                                                     | —     | 2.0<br>2.0 | 4<br>6           | μΑ<br>μΑ | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                                                                            |

|                       | LP Oscillator Operating<br>Frequency          | Fosc                                                                                                                                                                                      | 0     |            | 200              | kHz      | All temperatures                                                                                                            |

|                       | INTRC/EXTRC Oscillator<br>Operating Frequency |                                                                                                                                                                                           | -     |            | 4 <sup>(6)</sup> | MHz      | All temperatures                                                                                                            |

|                       | XT Oscillator Operating<br>Frequency          |                                                                                                                                                                                           | 0     |            | 4                | MHz      | All temperatures                                                                                                            |

|                       | HS Oscillator Operating<br>Frequency          |                                                                                                                                                                                           | 0     |            | 10               | MHz      | All temperatures                                                                                                            |

\* These parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

### 12.5 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS           |                                     | 3. Tcc:st | (I <sup>2</sup> C specifications only) |  |

|-----------------------|-------------------------------------|-----------|----------------------------------------|--|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |  |

| Т                     |                                     |           |                                        |  |

| F                     | Frequency                           | Т         | Time                                   |  |

| Lowercas              | se letters (pp) and their meanings: | ·         |                                        |  |

| рр                    |                                     |           |                                        |  |

| сс                    | CCP1                                | OSC       | OSC1                                   |  |

| ck                    | CLKOUT                              | rd        | RD                                     |  |

| CS                    | CS                                  | rw        | RD or WR                               |  |

| di                    | SDI                                 | sc        | SCK                                    |  |

| do                    | SDO                                 | SS        | SS                                     |  |

| dt                    | Data in                             | tO        | TOCKI                                  |  |

| io                    | I/O port                            | t1        | T1CKI                                  |  |

| mc                    | MCLR                                | wr        | WR                                     |  |

| Upperca               | se letters and their meanings:      |           |                                        |  |

| S                     |                                     |           |                                        |  |

| F                     | Fall                                | Р         | Period                                 |  |

| Н                     | High                                | R         | Rise                                   |  |

| I                     | Invalid (Hi-impedance)              | V         | Valid                                  |  |

| L                     | Low                                 | Z         | Hi-impedance                           |  |

| I <sup>2</sup> C only |                                     |           |                                        |  |

| AA                    | output access                       | High      | High                                   |  |

| BUF                   | Bus free                            | Low       | Low                                    |  |

| Tcc:st (I             | <sup>2</sup> C specifications only) | •         |                                        |  |

| CC                    |                                     |           |                                        |  |

| HD                    | Hold                                | SU        | Setup                                  |  |

| ST                    |                                     |           |                                        |  |

| DAT                   | DATA input hold                     | STO       | STOP condition                         |  |

| STA                   | START condition                     |           |                                        |  |

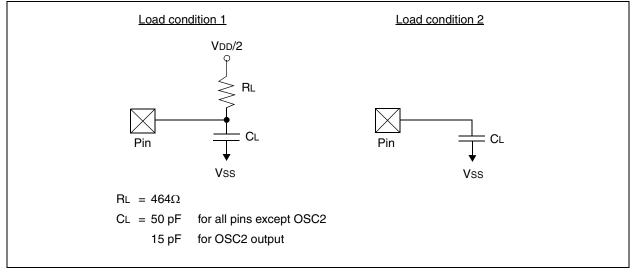

#### FIGURE 12-4: LOAD CONDITIONS

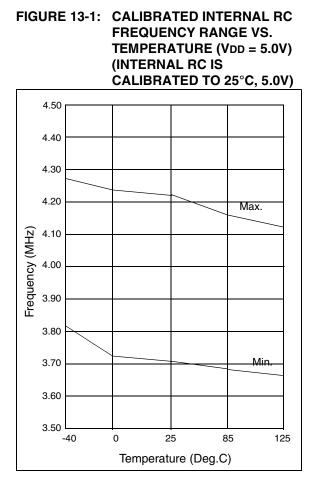

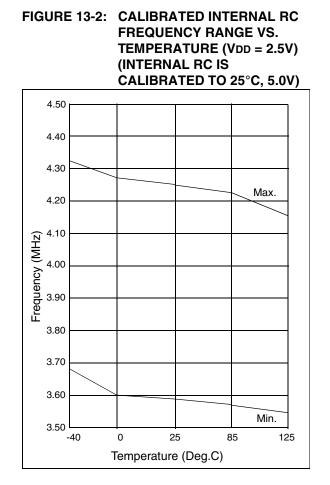

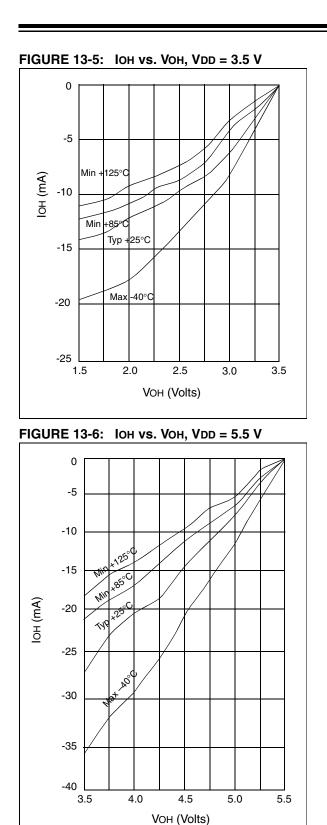

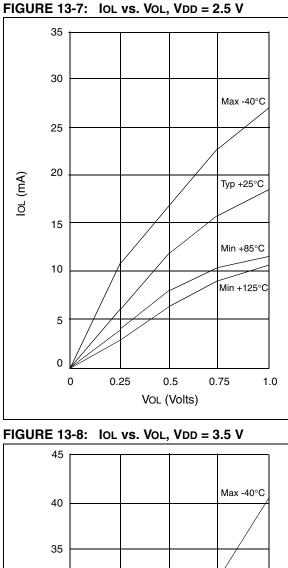

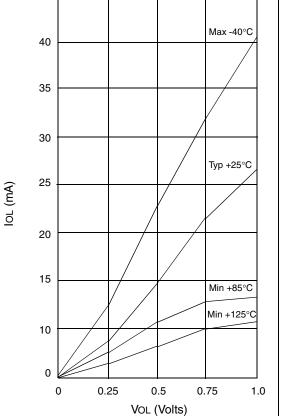

### 13.0 DC AND AC CHARACTERISTICS - PIC12C671/PIC12C672/PIC12LC671/ PIC12LC672/PIC12CE673/PIC12CE674/PIC12LCE673/PIC12LCE674

The graphs and tables provided in this section are for design guidance and are not tested. In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices will operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation.

## **PIC12C67X**

NOTES:

## **APPENDIX A: COMPATIBILITY**

To convert code written for PIC16C5X to PIC12C67X, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

## APPENDIX B: CODE FOR ACCESSING EEPROM DATA MEMORY

Please refer to our web site at www.microchip.com for code availability.

## **APPENDIX C: REVISION HISTORY**

Revision C (January 2013)

Added a note to each package outline drawing.

## PIC16XXXXX FAMILY

### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: |                                                                              | Total Pages Sent                  |  |  |  |  |  |  |  |

|------------|------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|--|--|

| Fror       | m: Name                                                                      |                                   |  |  |  |  |  |  |  |

|            | Company                                                                      |                                   |  |  |  |  |  |  |  |

|            | Address                                                                      |                                   |  |  |  |  |  |  |  |

|            | City / State / ZIP / Country                                                 |                                   |  |  |  |  |  |  |  |

|            | Telephone: ()                                                                | FAX: ()                           |  |  |  |  |  |  |  |

| Арр        | lication (optional):                                                         |                                   |  |  |  |  |  |  |  |

| Wou        | uld you like a reply? Y N                                                    |                                   |  |  |  |  |  |  |  |

| Dev        | vice: PIC16xxxxxx family                                                     | Literature Number: DS30561C       |  |  |  |  |  |  |  |

| Que        | estions:                                                                     |                                   |  |  |  |  |  |  |  |

| 1.         | 1. What are the best features of this document?                              |                                   |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

| 2.         | 2. How does this document meet your hardware and software development needs? |                                   |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

| 3.         | Do you find the organization of this document easy to follow? If not, why?   |                                   |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

| 4.         | What additions to the document do you think would enhar                      | ce the structure and subject?     |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

| _          |                                                                              | <i></i>                           |  |  |  |  |  |  |  |

| 5.         | What deletions from the document could be made without                       | affecting the overall usefulness? |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

| 6.         | Is there any incorrect or misleading information (what and                   | where)?                           |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

| 7.         | How would you improve this document?                                         |                                   |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

|            |                                                                              |                                   |  |  |  |  |  |  |  |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1997-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769287

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.