Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c672-10i-sm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## FIGURE 4-2: PIC12C67X REGISTER FILE MAP

|                                           | WAF                 |                     |                 |  |  |  |

|-------------------------------------------|---------------------|---------------------|-----------------|--|--|--|

| File<br>Address                           | 6                   |                     | File<br>Address |  |  |  |

| 00h                                       | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |  |

| 01h                                       | TMR0                | OPTION              | 81h             |  |  |  |

| 02h                                       | PCL                 | PCL                 | 82h             |  |  |  |

| 02h                                       | STATUS              | STATUS              | 83h             |  |  |  |

| 03h                                       | FSR                 | FSR                 | 84h             |  |  |  |

| 0411<br>05h                               | GPIO                | TRIS                | 85h             |  |  |  |

|                                           | GFIO                | INIS                | _               |  |  |  |

| 06h<br>07h                                |                     |                     | 86h<br>87h      |  |  |  |

| 07h<br>08h                                |                     |                     | 88h             |  |  |  |

|                                           |                     |                     |                 |  |  |  |

| 09h                                       |                     |                     | 89h             |  |  |  |

| 0Ah                                       | PCLATH              | PCLATH              | 8Ah             |  |  |  |

| 0Bh                                       | INTCON              | INTCON              | 8Bh             |  |  |  |

| 0Ch                                       | PIR1                | PIE1                | 8Ch             |  |  |  |

| 0Dh                                       |                     |                     | 8Dh             |  |  |  |

| 0Eh                                       |                     | PCON                | 8Eh             |  |  |  |

| 0Fh                                       |                     | OSCCAL              | 8Fh             |  |  |  |

| 10h                                       |                     |                     | 90h             |  |  |  |

| 11h                                       |                     |                     | 91h             |  |  |  |

| 12h                                       |                     |                     | 92h             |  |  |  |

| 13h                                       |                     |                     | 93h             |  |  |  |

| 14h                                       |                     |                     | 94h             |  |  |  |

| 15h                                       |                     |                     | 95h             |  |  |  |

| 16h                                       |                     |                     | 96h             |  |  |  |

| 17h                                       |                     |                     | 97h             |  |  |  |

| 18h                                       |                     |                     | 98h             |  |  |  |

| 19h                                       |                     |                     | 99h             |  |  |  |

| 1Ah                                       |                     |                     | 9Ah             |  |  |  |

| 1Bh                                       |                     |                     | 9Bh             |  |  |  |

| 1Ch                                       |                     |                     | 9Ch             |  |  |  |

| 1Dh                                       |                     |                     | 9Dh             |  |  |  |

| 1Eh                                       | ADRES               |                     | 9Eh             |  |  |  |

| 1Fh                                       | ADCON0              | ADCON1              | 9Fh             |  |  |  |

| 20h                                       |                     |                     | A0h             |  |  |  |

| 2011                                      |                     | General             | AUII            |  |  |  |

|                                           |                     | Purpose             |                 |  |  |  |

|                                           | General             | Register            | BFh             |  |  |  |

|                                           | Purpose             |                     | C0h             |  |  |  |

|                                           | Register            |                     |                 |  |  |  |

|                                           |                     |                     | EFh             |  |  |  |

| 70h                                       |                     | Mapped              | F0h             |  |  |  |

|                                           |                     | in Bank 0           |                 |  |  |  |

| 7Fh                                       | Bank 0              | Bank 1              | _ FFh           |  |  |  |

|                                           |                     |                     |                 |  |  |  |

| Unimplemented data memory locations, read |                     |                     |                 |  |  |  |

|                                           | as '0'.             |                     |                 |  |  |  |

| Note 1: Not a physical register.          |                     |                     |                 |  |  |  |

|                                           |                     |                     |                 |  |  |  |

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM.

The Special Function Registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

# **PIC12C67X**

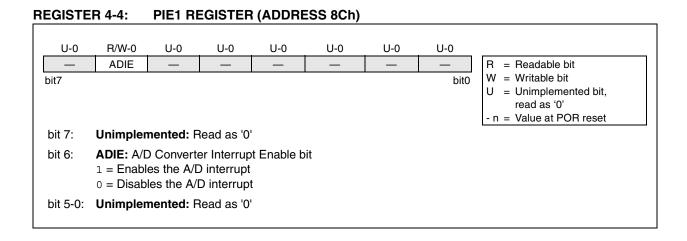

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the Peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

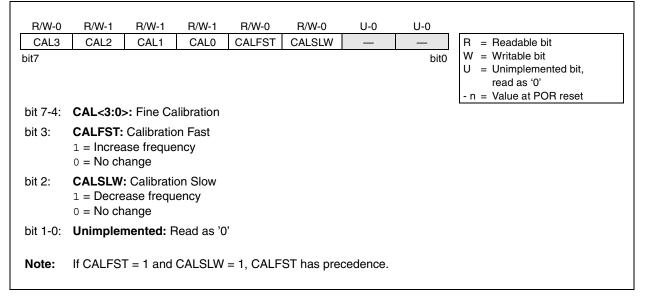

#### 4.2.2.7 OSCCAL REGISTER

The Oscillator Calibration (OSCCAL) Register is used to calibrate the internal 4 MHz oscillator. It contains four bits for fine calibration and two other bits to either increase or decrease frequency.

#### REGISTER 4-7: OSCCAL REGISTER (ADDRESS 8Fh)

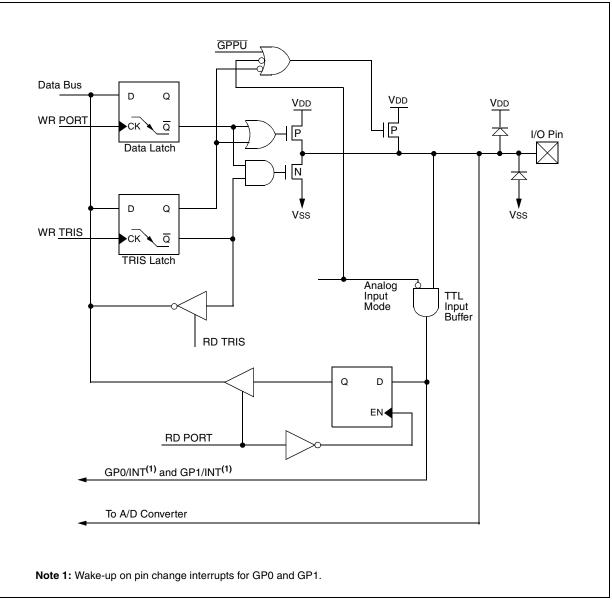

#### FIGURE 5-1: BLOCK DIAGRAM OF GP0/AN0 AND GP1/AN1/VREF PIN

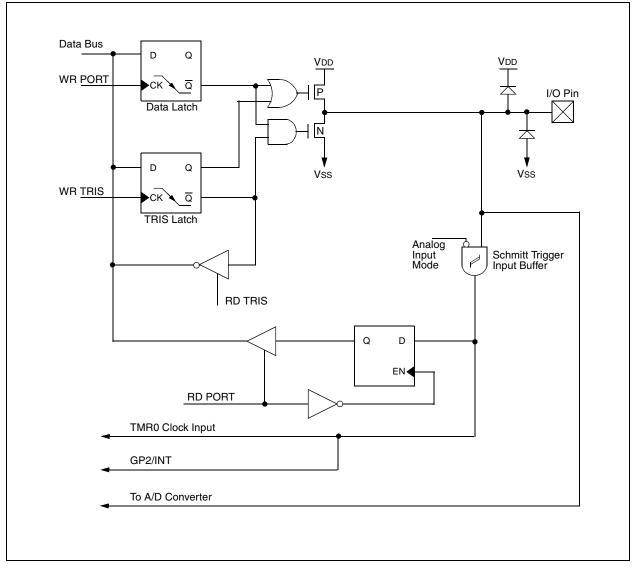

FIGURE 5-2: BLOCK DIAGRAM OF GP2/T0CKI/AN2/INT PIN

#### 6.0 EEPROM PERIPHERAL OPERATION

The PIC12CE673 and PIC12CE674 each have 16 bytes of EEPROM data memory. The EEPROM memory has an endurance of 1,000,000 erase/write cycles and a data retention of greater than 40 years. The EEPROM data memory supports a bi-directional 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), that are mapped to bit6 and bit7, respectively, of the GPIO register (SFR 06h). Unlike the GP0-GP5 that are connected to the I/O pins, SDA and SCL are only connected to the internal EEPROM peripheral. For most applications, all that is required is calls to the following functions:

| ;<br>; | Byte_Write: Byte write routine<br>Inputs: EEPROM Address EEADDR |

|--------|-----------------------------------------------------------------|

| ;      | EEPROM Data EEDATA                                              |

| ;      | Outputs: Return 01 in W if OK, else                             |

|        | return 00 in W                                                  |

| ;      |                                                                 |

| ;      | Read_Current: Read EEPROM at address                            |

| Cι     | urrently held by EE device.                                     |

| ;      | Inputs: NONE                                                    |

| ;      | Outputs: EEPROM Data EEDATA                                     |

| ;      | Return 01 in W if OK, else                                      |

|        | return 00 in W                                                  |

| ;      |                                                                 |

| ;      | Read Random: Read EEPROM byte at supplied                       |

| ad     | ddress                                                          |

| ;      | Inputs: EEPROM Address EEADDR                                   |

| ;      | Outputs: EEPROM Data EEDATA                                     |

| ;      | Return 01 in W if OK,                                           |

|        | else return 00 in W                                             |

|        |                                                                 |

The code for these functions is available on our web site (www.microchip.com). The code will be accessed by either including the source code FL67XINC.ASM or by linking FLASH67X.ASM. FLASH67X.INC provides external definition to the calling program.

#### 6.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the device.

For normal data transfer, SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

#### 6.0.2 SERIAL CLOCK

This SCL signal is used to synchronize the data transfer from and to the EEPROM.

#### 6.1 Bus Characteristics

The following **bus protocol** is to be used with the EEPROM data memory. In this section, the term "processor" is used to denote the portion of the PIC12C67X that interfaces to the EEPROM via software.

• Data transfer may be initiated only when the bus is not busy.

During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 6-3).

6.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

6.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

6.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### 6.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the available data EEPROM space.

# **PIC12C67X**

#### 9.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create a Poweron Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See Table 11-4.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 9.4.4 TIME-OUT SEQUENCE

On power-up, the Time-out Sequence is as follows: first, PWRT time-out is invoked after the POR time delay has expired; then, OST is activated. The total time-out will vary, based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-7, Figure 9-8, and Figure 9-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC12C67X device operating in parallel.

### 9.4.5 POWER CONTROL (PCON)/STATUS REGISTER

The Power Control/Status Register, PCON (address 8Eh), has one bit. See Register 4-6 for register.

Bit1 is POR (Power-on Reset). It is cleared on a Poweron Reset and is unaffected otherwise. The user sets this bit following a Power-on Reset. On subsequent resets, if POR is '0', it will indicate that a Power-on Reset must have occurred.

| <b>Oscillator Configuration</b> | Power            | Wake-up from SLEEP |          |

|---------------------------------|------------------|--------------------|----------|

|                                 | <b>PWRTE</b> = 0 | PWRTE = 1          |          |

| XT, HS, LP                      | 72 ms + 1024Tosc | 1024Tosc           | 1024Tosc |

| INTRC, EXTRC                    | 72 ms            | _                  | —        |

#### TABLE 9-4: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 9-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | то | PD |                                                         |

|-----|----|----|---------------------------------------------------------|

| 0   | 1  | 1  | Power-on Reset                                          |

| 0   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0  | u  | WDT Reset                                               |

| 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

Legend: u = unchanged, x = unknown.

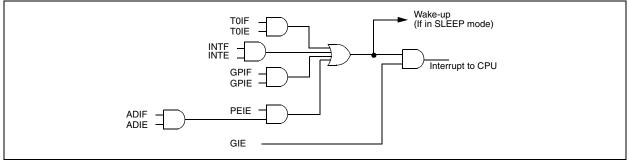

#### 9.5 Interrupts

There are four sources of interrupt:

| Interrupt Sources                                |

|--------------------------------------------------|

| TMR0 Overflow Interrupt                          |

| External Interrupt GP2/INT pin                   |

| GPIO Port Change Interrupts (pins GP0, GP1, GP3) |

| A/D Interrupt                                    |

The Interrupt Control Register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|

|       | less of the status of their corresponding       |  |  |  |  |

|       | mask bit or the GIE bit.                        |  |  |  |  |

A global interrupt enable bit, GIE (INTCON<7>), enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit. The GIE bit is cleared on reset. The "return-from-interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The GP2/INT, GPIO port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag ADIF, is contained in the Special Function Register PIR1. The corresponding interrupt enable bit is contained in Special Function Register PIE1, and the peripheral interrupt enable bit is contained in Special Function Register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid repeated interrupts.

For external interrupt events, such as GPIO change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends on when the interrupt event occurs (Figure 9-14). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

#### FIGURE 9-13: INTERRUPT LOGIC

#### 9.5.1 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 7.0). The flag bit T0IF (INTCON<2>) will be set, regardless of the state of the enable bits. If used, this flag must be cleared in software.

#### 9.5.2 INT INTERRUPT

External interrupt on GP2/INT pin is edge triggered; either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the GP2/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP mode.

#### 9.5.3 GPIO INTCON CHANGE

An input change on GP3, GP1 or GP0 sets flag bit GPIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit GPIE (INTCON<3>) (Section 5.1). This flag bit GPIF (INTCON<0>) will be set, regardless of the state of the enable bits. If used, this flag must be cleared in software.

#### 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W register and STATUS register). This will have to be implemented in software.

Example 9-1 shows the storing and restoring of the STATUS and W registers. The register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

Example 9-2 shows the saving and restoring of STA-TUS and W using RAM locations 0x70 - 0x7F. W\_TEMP is defined at 0x70 and STATUS\_TEMP is defined at 0x71.

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

- f) Returns from interrupt.

## EXAMPLE 9-1: SAVING STATUS AND W REGISTERS USING GENERAL PURPOSE RAM (0x20 - 0x6F)

|                | W_TEMP<br>STATUS,W<br>STATUS,RP0<br>STATUS_TEMP |                                                                                                                                                                      |

|----------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>SWAPF | _<br>STATUS<br>W_TEMP,F                         | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)<br>;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W<br>;Return from interrupt |

|                |                                                 |                                                                                                                                                                      |

| EXAMPLE 9-2:   | SAVING STATUS                                   | AND W REGISTERS USING SHARED RAM (0x70 - 0x7F)                                                                                                                       |

| MOVWF<br>MOVF  | W_TEMP<br>STATUS,W                              | AND W REGISTERS USING SHARED RAM (0x70 - 0x7F)<br>;Copy W to TEMP register (bank independent)<br>;Move STATUS register into W<br>;Save contents of STATUS register   |

| FIGURE 9-16: WAKE-UP FROM SLEEP THROUGH INTERRUPT |

|---------------------------------------------------|

|---------------------------------------------------|

| ; a1   a2   a3   a<br>osc1 ///////      | 4; Q1  Q2  Q3  Q4<br>_/~~~~ |                       | Q1  Q2  Q3  Q4 | 01 02 03 04<br>////////       | 01 02 03 04 | Q1 Q2 Q3 Q4; |

|-----------------------------------------|-----------------------------|-----------------------|----------------|-------------------------------|-------------|--------------|

| CLKOUT(4)                               | -∖/                         | Tost(2)               | /              | \/                            | \/¦         |              |

| GPIO pin                                | <br>                        | x                     |                | I<br>I<br>I                   |             |              |

| GPIF flag<br>(INTCON<0>)                |                             |                       |                | Interrupt Latency<br>(Note 3) |             | i            |

| GIE bit<br>(INTCON<7>)                  | <br><br>                    | Processor in<br>SLEEP |                |                               |             |              |

| INSTRUCTION FLOW                        | 1                           |                       |                | i i                           |             | 1            |

| РС Х РС                                 | X PC+1                      | X PC+2                | PC+2           | X PC + 2                      | X 0004h     | 0005h        |

| Instruction<br>fetched Inst(PC) = SLEEF | Inst(PC + 1)                | I I I                 | Inst(PC + 2)   | I I I                         | Inst(0004h) | Inst(0005h)  |

| Instruction<br>executed Inst(PC - 1)    | SLEEP                       | I i                   | Inst(PC + 1)   | Dummy cycle                   | Dummy cycle | Inst(0004h)  |

Note 1: XT, HS or LP oscillator mode assumed.

- 2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for INTRC and EXTRC osc mode.

- **3:** GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in XT, HS or LP osc modes, but shown here for timing reference.

#### 9.9 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 9.10 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

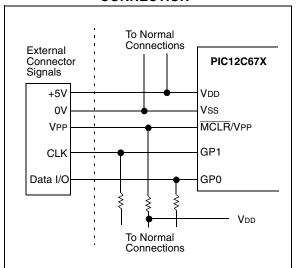

#### 9.11 In-Circuit Serial Programming

PIC12C67X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the GP1 and GP0 pins low, while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). GP1 (clock) becomes the programming clock and GP0 (data) becomes the programming data. Both GP0 and GP1 are Schmitt Trigger inputs in this mode.

After reset, and if the device is placed into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC12C67X Programming Specifications.

#### FIGURE 9-17: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

#### 10.2 Instruction Descriptions

| ADDLW            | Add Literal and                                                                                                   | w                  |      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|--------------------|------|--|

| Syntax:          | [label] ADDLW                                                                                                     | / k                |      |  |

| Operands:        | $0 \leq k \leq 255$                                                                                               |                    |      |  |

| Operation:       | $(W) + k \to (W)$                                                                                                 |                    |      |  |

| Status Affected: | C, DC, Z                                                                                                          |                    |      |  |

| Encoding:        | 11 111x                                                                                                           | kkkk               | kkkk |  |

| Description:     | The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register. |                    |      |  |

| Words:           | 1                                                                                                                 |                    |      |  |

| Cycles:          | 1                                                                                                                 |                    |      |  |

| Example          | ADDLW 0x15                                                                                                        |                    |      |  |

|                  | Before Instruction<br>W =<br>After Instruction<br>W =                                                             | on<br>0x10<br>0x25 |      |  |

| ANDLW            | And Literal with W                                                                                                       |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                 |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |  |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                        |  |  |  |  |  |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                        |  |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                        |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                        |  |  |  |  |  |  |

| Example          | ANDLW 0x5F                                                                                                               |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                          |  |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                      |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                  |  |  |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                           |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                         |  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                                |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                |  |  |  |  |  |  |

| Example          | addwf fsr, <b>O</b>                                                                                                                                                              |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                      |  |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |  |  |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |  |  |  |  |  |  |  |

|                  | ANDWF FSR, T<br>Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                 |  |  |  |  |  |  |  |

| CLRWDT                                                                                                   | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                                                  | [label] CLRWDT                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:                                                                                                | None                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Operation:                                                                                               | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ \text{O} \rightarrow \underline{\text{WDT}} \text{ prescaler,} \\ 1 \rightarrow \underline{\text{TO}} \\ 1 \rightarrow \text{PD} \end{array}$                                                                                                                              |  |  |  |  |  |  |

| Status Affected:                                                                                         | TO, PD                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Encoding:                                                                                                | 00 0000 0110 0100                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Description:                                                                                             | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits<br>TO and PD are set.                                                                                                                                                                                                    |  |  |  |  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Cycles:                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Example                                                                                                  | CLRWDT                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                                                                          | Before Instruction<br>WDT counter = ?                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                                                                                          | After Instruction<br>WDT counter = $0x00$<br>WDT prescaler= $0$<br>TO = $1$                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                                                                                                          | PD = 1                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| COMF                                                                                                     | PD = 1<br>Complement f                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| COMF<br>Syntax:                                                                                          |                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                                                                                          | Complement f                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Syntax:                                                                                                  | Complement f<br>[ <i>label</i> ] COMF f,d<br>$0 \le f \le 127$                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                     | Complement f<br>[ <i>label</i> ] COMF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                                       | Complement f<br>[ <i>label</i> ] COMF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>( $\overline{f}$ ) $\rightarrow$ (dest)                                                                                                                                                                                                        |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | Complement f<br>[ <i>label</i> ] COMF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>( $\tilde{f}$ ) $\rightarrow$ (dest)<br>Z                                                                                                                                                                                                      |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | Complement f[ label ]COMFf,d $0 \le f \le 127$ $d \in [0,1]$ $(\tilde{f}) \rightarrow$ (dest)Z001001dffffffThe contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the                                                                                                                |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | Complement f[ label ] COMF f,d $0 \le f \le 127$ $d \in [0,1]$ $(\overline{f}) \rightarrow$ (dest)Z001001dffffffThe contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'.                                                           |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | Complement f[ label ] COMF f,d $0 \le f \le 127$ $d \in [0,1]$ ( $\tilde{f}$ ) $\rightarrow$ (dest)Z001001dfffffffThe contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'.1                                                        |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | Complement f[ label ] COMF f,d $0 \le f \le 127$ $d \in [0,1]$ ( $\overline{f}$ ) $\rightarrow$ (dest)Z001001dffffffThe contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'.11COMFREG1, 0Before Instruction<br>REG1REG1 $= 0x13$   |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | Complement f[ label ] COMF f,d $0 \le f \le 127$ $d \in [0,1]$ ( $\tilde{f}$ ) $\rightarrow$ (dest)Z001001dffffffThe contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'.11COMFREG1, 0Before Instruction                           |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | Complement f[ label ] COMF f,d $0 \le f \le 127$ $d \in [0,1]$ $(\bar{f}) \rightarrow$ (dest)Z001001dffffffThe contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'.11COMFREG1, 0Before Instruction<br>REG1 = 0x13After Instruction |  |  |  |  |  |  |

| DECF                                                                             | Decrement f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                                          | [ <i>label</i> ] DECF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Operands:                                                                        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Operation:                                                                       | (f) - 1 $\rightarrow$ (dest)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Status Affected:                                                                 | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Encoding:                                                                        | 00 0011 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Description:                                                                     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W regis-<br>ter. If 'd' is 1, the result is stored<br>back in register 'f'.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Words:                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Cycles:                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Example                                                                          | decf cnt, <b>1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                                                                  | Before Instruction<br>CNT = 0x01<br>Z = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                                                                                  | After Instruction<br>CNT = 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                                                                  | Z = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| DECFSZ                                                                           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Syntax:                                                                          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Operands:                                                                        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Operation:                                                                       | $d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:                                                   | $d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:                                      | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0 None 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:                                                   | $d \in [0,1]$<br>(f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:                                      | $d \in [0,1]$ (f) - 1 → (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle                                                                             |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction.                                                 |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction.<br>1<br>1(2)<br>HERE DECFSZ CNT, 1              |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction.<br>1<br>1(2)                                    |  |  |  |  |  |  |  |

| Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $d \in [0,1]$ (f) - 1 $\rightarrow$ (dest); skip if result = 0<br>None $\boxed{00  1011  dfff  ffff}$ The contents of register 'f' are<br>decremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction.<br>1<br>1(2)<br>HERE DECFSZ CNT, 1<br>GOTO LOOP |  |  |  |  |  |  |  |

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

#### 11.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 11.6 <u>MPLAB-ICE High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PIC microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PIC MCU.

#### 11.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PIC microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

#### 11.8 <u>ICEPIC</u>

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

#### 11.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

#### 11.10 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In

|        | Standard Operating Conditions (unless otherwise specified) |           |                                                     |         |          |          |                                                                     |  |  |  |

|--------|------------------------------------------------------------|-----------|-----------------------------------------------------|---------|----------|----------|---------------------------------------------------------------------|--|--|--|

|        |                                                            | Operating | temperature                                         | 0°0     | C ≤ TA ≤ | ≤ +70°C  | (commercial)                                                        |  |  |  |

| DC CHA | RACTERISTICS                                               |           | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) |         |          |          |                                                                     |  |  |  |

|        |                                                            | Operating | y voltage VDD r                                     | ange as | describe | ed in DC | spec Section 12.1 and                                               |  |  |  |

|        |                                                            | Section 1 | 2.2.                                                |         |          |          |                                                                     |  |  |  |

| Param  | Characteristic                                             | Sym       | Min                                                 | Typ†    | Max      | Units    | Conditions                                                          |  |  |  |

| No.    |                                                            |           |                                                     |         |          |          |                                                                     |  |  |  |

|        | Output High Voltage                                        |           |                                                     |         |          |          |                                                                     |  |  |  |

| D090   | I/O ports (Note 3)                                         | Vон       | Vdd - 0.7                                           | —       | _        | V        | IOH = -3.0 mA, VDD = 4.5V,<br>–40°С to +85°С                        |  |  |  |

| D090A  |                                                            |           | Vdd - 0.7                                           | -       | —        | V        | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                       |  |  |  |

| D092   | OSC2/CLKOUT                                                |           | VDD - 0.7                                           | —       | —        | V        | IOH = TBD, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |

| D092A  |                                                            |           | VDD - 0.7                                           | -       | —        | V        | IOH = TBD, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |  |

|        | Capacitive Loading Specs on                                |           |                                                     |         |          |          |                                                                     |  |  |  |

|        | Output Pins                                                |           |                                                     |         |          |          |                                                                     |  |  |  |

| D100   | OSC2 pin                                                   | Cosc2     | _                                                   |         | 15       | pF       | In XT and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101   | All I/O pins                                               | Cio       | _                                                   |         | 50       | pF       |                                                                     |  |  |  |

tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.