Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12c672t-04-sm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 PIC12C67X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC12C67X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For example, the PIC12C67X device "type" is indicated in the device number:

- 1. **C**, as in PIC12**C**671. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC12LC671. These devices have EPROM type memory and operate over an extended voltage range.

- 3. **CE**, as in PIC12**CE**674. These devices have EPROM type memory, EEPROM data memory and operate over the standard voltage range.

- 4. **LCE**, as in PIC12**LCE**674. These devices have EPROM type memory, EEPROM data memory and operate over an extended voltage range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in windowed package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> programmers both support the PIC12C67X. Third party programmers also are available; refer to the Microchip Third Party Guide for a list of sources.

Note: Please note that erasing the device will also erase the pre-programmed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing the part.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turn-Programming (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turn Programming</u> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

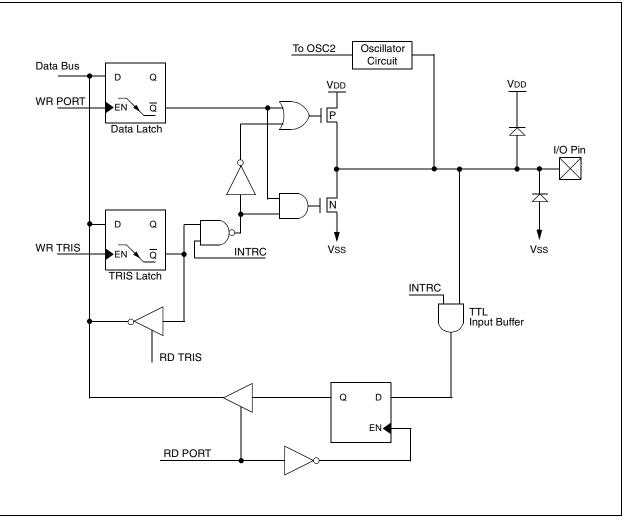

#### FIGURE 5-5: BLOCK DIAGRAM OF GP5/OSC1/CLKIN PIN

| TABLE 5-1: S | SUMMARY | <b>OF PORT</b> | REGISTERS |

|--------------|---------|----------------|-----------|

|--------------|---------|----------------|-----------|

| Address | Name   | Bit 7              | Bit 6              | Bit 5   | Bit 4       | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|--------|--------------------|--------------------|---------|-------------|---------|-------|-------|-------|-------------------------------|---------------------------------|

| 85h     | TRIS   | —                  |                    | GPIO Da | ata Directi | on Regi | ster  |       |       | 11 1111                       | 11 1111                         |

| 81h     | OPTION | GPPU               | INTEDG             | T0CS    | T0SE        | PSA     | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| 03h     | STATUS | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup> | RP0     | TO          | PD      | Z     | DC    | С     | 0001 1xxx                     | 000q quuu                       |

| 05h     | GPIO   | SCL <sup>(2)</sup> | SDA <sup>(2)</sup> | GP5     | GP4         | GP3     | GP2   | GP1   | GP0   | 11xx xxxx                     | 11uu uuuu                       |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, q = see tables in Section 9.4 for possible values.

Note 1: The IRP and RP1 bits are reserved on the PIC12C67X; always maintain these bits clear.

2: The SCL and SDA bits are unimplemented on the PIC12C671 and PIC12C672.

#### 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of GPIO will cause all eight bits of GPIO to be read into the CPU. Then the BSF operation takes place on bit5 and GPIO is written to the output latches. If another bit of GPIO is used as a bi-directional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched to an output, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch. Example 5-1 shows the effect of two sequential readmodify-write instructions on an I/O port.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

| ; | ;Initial GPIO Settings |         |       |      |         |      |        |

|---|------------------------|---------|-------|------|---------|------|--------|

| ; | ; GPIO<5:3> Inputs     |         |       |      |         |      |        |

| ; | GPIO<2                 | 2:0> Oi | ıtput | S    |         |      |        |

| ; |                        |         |       |      |         |      |        |

| ; |                        |         |       | GPIC | ) latch | GPIC | ) pins |

| ; |                        |         |       |      |         |      |        |

|   | BCF                    | GPIO,   | 5     | ;01  | -ppp    | 11   | pppp   |

|   | BCF                    | GPIO,   | 4     | ;10  | -ppp    | 11   | pppp   |

|   | MOVLW                  | 007h    |       | ;    |         |      |        |

|   | TRIS                   | GPIO    |       | ;10  | -ppp    | 10   | pppp   |

| ; |                        |         |       |      |         |      |        |

;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;GP5 to be latched as the pin value (High).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip. NOTES:

#### 6.3 Write Operations

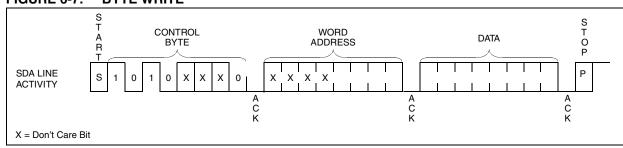

#### 6.3.1 BYTE WRITE

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the  $R/\overline{W}$  bit (which is a logic low) are placed onto the bus by the processor. This indicates to the addressed EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer. Only the lower four address bits are used by the device, and the upper four bits are don't cares. If the address byte is acknowledged, the processor will then transmit the data word to be written into the addressed memory location. The memory acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time will not generate acknowledge signals. After a byte write command, the internal address counter will not be incremented and will point to the same address location that was just written. If a stop bit sequence is transmitted to the device at any point in the write command sequence before the entire sequence is complete, then the command will abort and no data will be written. If more than 8 data bits are transmitted before the stop bit sequence is sent, then the device will clear the previously loaded byte and begin loading the data buffer again. If more than one data byte is transmitted to the device and a stop bit is sent before a full eight data bits have been transmitted, then the write command will abort and no data will be written. The EEPROM memory employs a VCC threshold detector circuit, which disables the internal erase/write logic if the Vcc is below minimum VDD. Byte write operations must be preceded and immediately followed by a bus not busy bus cycle where both SDA and SCL are held high. (See Figure 6-7 for Byte Write operation.)

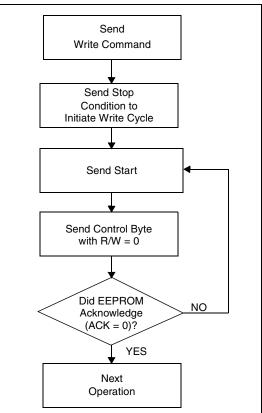

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. (See Figure 6-6 for flow diagram.)

#### FIGURE 6-6: ACKNOWLEDGE POLLING FLOW

#### FIGURE 6-7: BYTE WRITE

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

# EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

#### TABLE 7-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6       | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|--------|-------------|---------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 | module's re | egister |       |       |       |       |       | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE        | TOIE    | INTE  | GPIE  | TOIF  | INTF  | GPIF  | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | GPPU   | INTEDG      | TOCS    | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111       | 1111 1111                       |

| 85h     | TRIS   | _      |             | TRIS5   | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0 | 11 1111         | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

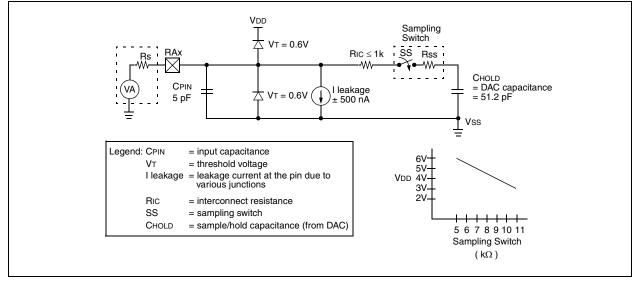

#### 8.1 A/D Sampling Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 8-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 8-2. The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 8-1 may be used. This equation assumes that 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

### EQUATION 8-1: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/512)) \bullet (1 - e^{(-Tc/CHOLD(Ric + Rss + Rs))})$ or

$Tc = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 8-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

Rs = 10 kΩ

1/2 LSb error

$\text{VDD}=\text{5V}\rightarrow\text{Rss}=\text{7 k}\Omega$

Temp (system max.) = 50°C

VHOLD = 0 @ t = 0

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0 TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### EXAMPLE 8-1: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

TACQ = Internal Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

TACQ =  $5 \,\mu s + Tc + [(Temp - 25^{\circ}C)(0.05 \,\mu s/^{\circ}C)]$

Tc = -CHOLD (Ric + Rss + Rs) ln(1/512)-51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020) -51.2 pF (18 kΩ) ln(0.0020) -0.921 µs (-6.2146) 5.724 µs TACQ = 5 µs + 5.724 µs + [(50°C - 25°C)(0.05 µs/°C)]

10.724 μs + 1.25 μs

11.974 μs

#### FIGURE 8-2: ANALOG INPUT MODEL

#### 8.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5 TAD per 8-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal ADC RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu$ s. If the minimum TAD time of 1.6  $\mu$ s can not be obtained, TAD should be  $\leq 8 \mu$ s for preferred operation.

Table 8-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### 8.3 Configuring Analog Port Pins

The ADCON1 and TRIS Registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<2:0> bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channel will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN<3:0> pins) may cause the input buffer to consume current that is out of the devices specification.

#### TABLE 8-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock Source                           | Device Frequency |                           |                           |                         |  |

|-------------------------------------------|------------------|---------------------------|---------------------------|-------------------------|--|

| Operation                                 | ADCS<1:0>        | 4 MHz                     | 1.25 MHz                  | 333.33 kHz              |  |

| 2Tosc                                     | 0 0              | 500 ns <sup>(2)</sup>     | 1.6 μs                    | 6 μs                    |  |

| 8Tosc                                     | 01               | 2.0 μs                    | 6.4 μs                    | 24 μs <sup>(3)</sup>    |  |

| 32Tosc                                    | 10               | 8.0 μs                    | 25.6 μs <sup>(3)</sup>    | 96 μs <b>(3)</b>        |  |

| Internal ADC RC Oscillator <sup>(5)</sup> | 11               | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1,4)</sup> | 2 - 6 μs <sup>(1)</sup> |  |

**Note 1:** The RC source has a typical TAD time of 4  $\mu$ s.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: While in RC mode, with device frequency above 1 MHz, conversion accuracy is out of specification.

**5:** For extended voltage devices (LC), please refer to Electrical Specifications section.

# PIC12C67X

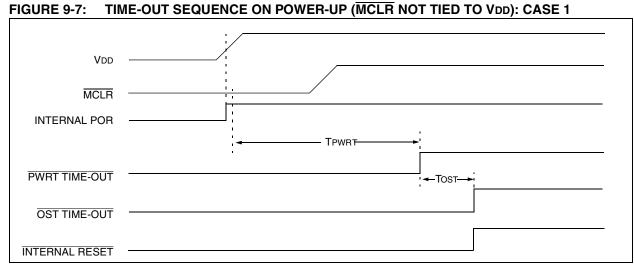

#### FIGURE 9-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

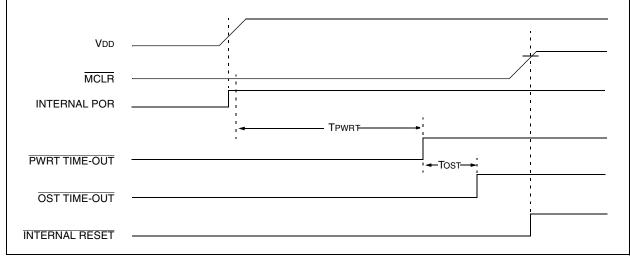

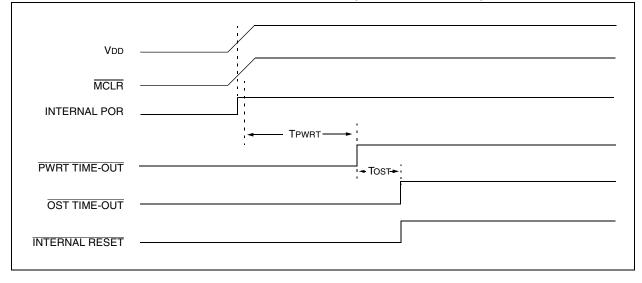

#### FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### 9.8 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input, if enabled, should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on GPIO should be considered.

The  $\overline{\text{MCLR}}$  pin, if enabled, must be at a logic high level (VIHMC).

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. GP2/INT interrupt, interrupt GPIO port change or some Peripheral Interrupts.

External MCLR Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device reset. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupt can wake the device from SLEEP:

1. A/D conversion (when A/D clock source is RC).

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 9.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

NOTES:

#### 10.2 Instruction Descriptions

| ADDLW            | Add Literal and                                         | w                  |         |  |

|------------------|---------------------------------------------------------|--------------------|---------|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                |                    |         |  |

| Operands:        | $0 \leq k \leq 255$                                     |                    |         |  |

| Operation:       | $(W) + k \to (W)$                                       |                    |         |  |

| Status Affected: | C, DC, Z                                                |                    |         |  |

| Encoding:        | 11 111x                                                 | kkkk               | kkkk    |  |

| Description:     | The contents of added to the eig the result is placter. | ht bit literal     | 'k' and |  |

| Words:           | 1                                                       |                    |         |  |

| Cycles:          | 1                                                       |                    |         |  |

| Example          | ADDLW 0x15                                              |                    |         |  |

|                  | Before Instruction<br>W =<br>After Instruction<br>W =   | on<br>0x10<br>0x25 |         |  |

| ANDLW            | And Literal with W                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                 |

| Operands:        | $0 \le k \le 255$                                                                                                        |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                          |

| Status Affected: | Z                                                                                                                        |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                        |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |

| Words:           | 1                                                                                                                        |

| Cycles:          | 1                                                                                                                        |

| Example          | ANDLW 0x5F                                                                                                               |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                          |

| ADDWF            | Add W and f                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                         |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                                |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. |

| Words:           | 1                                                                                                                                                                                |

| Cycles:          | 1                                                                                                                                                                                |

| Example          | addwf fsr, <b>O</b>                                                                                                                                                              |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                      |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |

| Status Affected: | Z                                                                                                                                                           |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                           |

| Cycles:          | 1                                                                                                                                                           |

| Example          | ANDWF FSR, <b>1</b>                                                                                                                                         |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |

#### 12.1 DC Characteristics: PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS |                                                                            |       |       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C &\leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ -40^{\circ}C &\leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ -40^{\circ}C &\leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |          |                  |                                                                                                                                                      |  |  |

|--------------------|----------------------------------------------------------------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parm<br>No.        | Characteristic                                                             | Sym   | Min   | Typ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                            | Max      | Units            | Conditions                                                                                                                                           |  |  |

| D001               | Supply Voltage                                                             | Vdd   | 3.0   |                                                                                                                                                                                                                                                                                                                               | 5.5      | V                |                                                                                                                                                      |  |  |

| D002               | RAM Data Retention<br>Voltage <sup>(2)</sup>                               | Vdr   |       | 1.5*                                                                                                                                                                                                                                                                                                                          |          | V                | Device in SLEEP mode                                                                                                                                 |  |  |

| D003               | VDD Start Voltage to ensure<br>Power-on Reset                              | VPOR  |       | Vss                                                                                                                                                                                                                                                                                                                           |          | V                | See section on Power-on Reset for details                                                                                                            |  |  |

| D004               | VDD Rise Rate to ensure<br>Power-on Reset                                  | SVDD  | 0.05* |                                                                                                                                                                                                                                                                                                                               |          | V/ms             | See section on Power-on Reset for details                                                                                                            |  |  |

| D010               | Supply Current <sup>(3)</sup>                                              | Idd   | —     | 1.2                                                                                                                                                                                                                                                                                                                           | 2.5      | mA               | Fosc = 4MHz, VDD = 3.0V<br>XT and EXTRC mode (Note 4)                                                                                                |  |  |

| D010C              |                                                                            |       | —     | 1.2                                                                                                                                                                                                                                                                                                                           | 2.5      | mA               | Fosc = 4MHz, VDD = 3.0V<br>INTRC mode (Note 6)                                                                                                       |  |  |

|                    |                                                                            |       | —     | 2.2                                                                                                                                                                                                                                                                                                                           | 8        | mA               | Fosc = 10MHz, VDD = 5.5V<br>HS mode                                                                                                                  |  |  |

| D010A              |                                                                            |       | _     | 19                                                                                                                                                                                                                                                                                                                            | 29       | μA               | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Commercial Temperature                                                                            |  |  |

|                    |                                                                            |       | _     | 19<br>32                                                                                                                                                                                                                                                                                                                      | 37<br>60 | μΑ<br>μΑ         | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Industrial Temperature<br>Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Extended Temperature |  |  |

| D020               | Power-down Current <sup>(5)</sup>                                          | IPD   |       | 0.25                                                                                                                                                                                                                                                                                                                          | 6        | μA               | VDD = 3.0V, Commercial, WDT disabled                                                                                                                 |  |  |

| D021               |                                                                            |       | _     | 0.25                                                                                                                                                                                                                                                                                                                          | 7        | μA               | $V_{DD} = 3.0V$ , Industrial, WDT disabled                                                                                                           |  |  |

| D021B              |                                                                            |       | —     | 2                                                                                                                                                                                                                                                                                                                             | 14       | μA               | VDD = 3.0V, Extended, WDT disabled                                                                                                                   |  |  |

|                    |                                                                            |       | —     | 0.5                                                                                                                                                                                                                                                                                                                           | 8        | μA               | VDD = 5.5V, Commercial, WDT disabled                                                                                                                 |  |  |

|                    |                                                                            |       | _     | 0.8<br>3                                                                                                                                                                                                                                                                                                                      | 9<br>16  | μA<br>μA         | VDD = 5.5V, Industrial, WDT disabled<br>VDD = 5.5V, Extended, WDT disabled                                                                           |  |  |

| D022               | Watchdog Timer Current                                                     | ΔIWDT |       | 2.2                                                                                                                                                                                                                                                                                                                           | 5        | μA               | VDD = 3.0V, Commercial                                                                                                                               |  |  |

|                    |                                                                            |       | _     | 2.2<br>4                                                                                                                                                                                                                                                                                                                      | 6<br>11  | μ <b>Α</b><br>μΑ | VDD = 3.0V, Industrial<br>VDD = 3.0V, Extended                                                                                                       |  |  |

| D028               | Supply Current <sup>(3)</sup><br>During read/write to<br>EEPROM peripheral | ΔIEE  |       | 0.1                                                                                                                                                                                                                                                                                                                           | 0.2      | mA               | Fosc = 4MHz, VDD = 5.5V, SCL = 400kHz<br>For PIC12CE673/674 only                                                                                     |  |  |

These parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

**6:** INTRC calibration value is for 4MHz nominal at 5V,  $25^{\circ}$ C.

| DC CHARACTERISTICS |                                                                                       |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                         |            |                                      |  |

|--------------------|---------------------------------------------------------------------------------------|------|------------------------------------------------------|-----|-------------------------|------------|--------------------------------------|--|

| Parm<br>No.        | Sym                                                                                   | Min  | Typ <sup>(1)</sup>                                   | Max | Units                   | Conditions |                                      |  |

|                    | LP Oscillator Operating<br>Frequency<br>INTRC/EXTRC Oscillator<br>Operating Frequency | Fosc | 0                                                    |     | 200<br>4 <sup>(6)</sup> | kHz<br>MHz | All temperatures<br>All temperatures |  |

|                    | XT Oscillator Operating<br>Frequency                                                  |      | 0                                                    |     | 4                       | MHz        | All temperatures                     |  |

|                    | HS Oscillator Operating<br>Frequency                                                  |      | 0                                                    |     | 10                      | MHz        | All temperatures                     |  |

I hese parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD,

$\overline{MCLR} = VDD; WDT$  disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

#### 12.5 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2pp            | oS                                  | 3. TCC:ST | (I <sup>2</sup> C specifications only) |  |

|-----------------------|-------------------------------------|-----------|----------------------------------------|--|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |  |

| Т                     |                                     |           |                                        |  |

| F                     | Frequency                           | Т         | Time                                   |  |

| Lowercas              | se letters (pp) and their meanings: | ·         |                                        |  |

| рр                    |                                     |           |                                        |  |

| сс                    | CCP1                                | OSC       | OSC1                                   |  |

| ck                    | CLKOUT                              | rd        | RD                                     |  |

| CS                    | CS                                  | rw        | RD or WR                               |  |

| di                    | SDI                                 | sc        | SCK                                    |  |

| do                    | SDO                                 | SS        | SS                                     |  |

| dt                    | Data in                             | tO        | TOCKI                                  |  |

| io                    | I/O port                            | t1        | T1CKI                                  |  |

| mc                    | MCLR                                | wr        | WR                                     |  |

| Upperca               | se letters and their meanings:      |           |                                        |  |

| S                     |                                     |           |                                        |  |

| F                     | Fall                                | Р         | Period                                 |  |

| Н                     | High                                | R         | Rise                                   |  |

| I                     | Invalid (Hi-impedance)              | V         | Valid                                  |  |

| L                     | Low                                 | Z         | Hi-impedance                           |  |

| I <sup>2</sup> C only |                                     |           |                                        |  |

| AA                    | output access                       | High      | High                                   |  |

| BUF                   | Bus free                            | Low       | Low                                    |  |

| Tcc:st (I             | <sup>2</sup> C specifications only) |           |                                        |  |

| CC                    |                                     |           |                                        |  |

| HD                    | Hold                                | SU        | Setup                                  |  |

| ST                    |                                     |           |                                        |  |

| DAT                   | DATA input hold                     | STO       | STOP condition                         |  |

| STA                   | START condition                     |           |                                        |  |

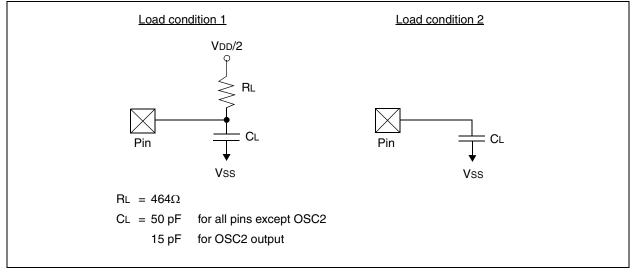

#### FIGURE 12-4: LOAD CONDITIONS

#### 12.6 <u>Timing Diagrams and Specifications</u>

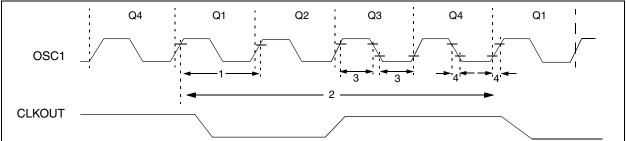

#### TABLE 12-1: CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                  | Min  | Тур† | Max    | Units | Conditions                  |

|------------------|-------|---------------------------------|------|------|--------|-------|-----------------------------|

|                  | Fosc  | External CLKIN Frequency        | DC   | _    | 4      | MHz   | XT and EXTRC osc mode       |

|                  |       | (Note 1)                        | DC   | —    | 4      | MHz   | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | DC   | —    | 10     | MHz   | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | DC   | _    | 200    | kHz   | LP osc mode                 |

|                  |       | Oscillator Frequency            | DC   | _    | 4      | MHz   | EXTRC osc mode              |

|                  |       | (Note 1)                        | .455 | —    | 4      | MHz   | XT osc mode                 |

|                  |       |                                 | 4    | —    | 4      | MHz   | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 4    | —    | 10     | MHz   | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | —    | 200    | kHz   | LP osc mode                 |

| 1                | Tosc  | External CLKIN Period           | 250  | _    | _      | ns    | XT and EXTRC osc mode       |

|                  |       | (Note 1)                        | 250  | _    | _      | ns    | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 100  | —    |        | ns    | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | _    | _      | μs    | LP osc mode                 |

|                  |       | Oscillator Period               | 250  | —    | —      | ns    | EXTRC osc mode              |

|                  |       | (Note 1)                        | 250  | —    | 10,000 | ns    | XT osc mode                 |

|                  |       |                                 | 250  | —    | 250    | ns    | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 100  | —    | 250    | ns    | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | —    | —      | μs    | LP osc mode                 |

| 2                | Тсү   | Instruction Cycle Time (Note 1) | 400  | —    | DC     | ns    | TCY = 4/FOSC                |

| 3                | TosL, | External Clock in (OSC1) High   | 50   | —    | —      | ns    | XT oscillator               |

|                  | TosH  | or Low Time                     | 2.5  | —    | —      | μS    | LP oscillator               |

|                  |       |                                 | 10   | —    | —      | ns    | HS oscillator               |

| 4                | TosR, | External Clock in (OSC1) Rise   | —    | —    | 25     | ns    | XT oscillator               |

|                  | TosF  | or Fall Time                    | —    | —    | 50     | ns    | LP oscillator               |

|                  |       |                                 | —    | —    | 15     | ns    | HS oscillator               |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC12C67X.

# **PIC12C67X**

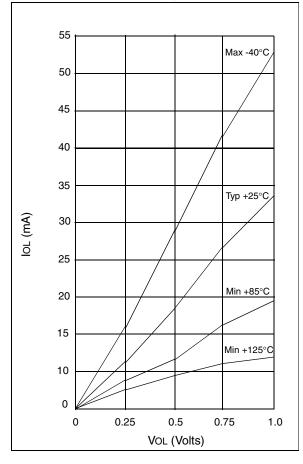

#### FIGURE 13-9: IOL vs. VOL, VDD = 5.5 V

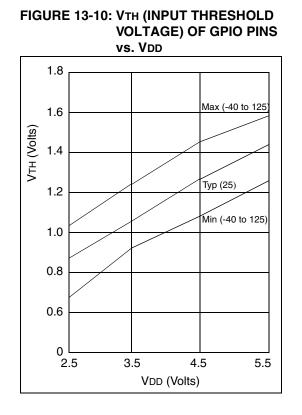

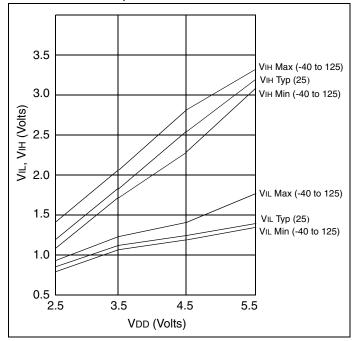

FIGURE 13-11: VIL, VIH OF NMCLR AND TOCKI vs. VDD

| 1                                           |    |

|---------------------------------------------|----|

| I/O Interfacing                             |    |

| I/O Ports                                   | 25 |

| I/O Programming Considerations              |    |

| ID Locations<br>INCF Instruction            |    |

| INCF Instruction                            |    |

| In-Circuit Serial Programming               |    |

| INDF Register                               |    |

| Indirect Addressing                         |    |

| Initialization Conditions for All Registers |    |

| Instruction Cycle                           | 10 |

| Instruction Flow/Pipelining                 |    |

| Instruction Format<br>Instruction Set       |    |

| ADDLW                                       | 72 |

| ADDWF                                       |    |

| ANDLW                                       |    |

| ANDWF                                       |    |

| BCF                                         |    |

| BSF                                         |    |

| BTFSC                                       |    |

| BTFSS<br>CALL                               |    |

| CALL<br>CLRF                                |    |

| CLRW                                        |    |

| CLRWDT                                      |    |

| COMF                                        |    |

| DECF                                        |    |

| DECFSZ                                      |    |

| GOTO                                        |    |

|                                             |    |

| INCFSZIORLW                                 |    |

| IORWF                                       |    |

| MOVF                                        |    |

| MOVLW                                       |    |

| MOVWF                                       |    |

| NOP                                         |    |

| OPTION                                      |    |

| RETFIE                                      |    |

| RETLW<br>RETURN                             |    |

| RLF                                         |    |

| RRF                                         |    |

| SLEEP                                       | 79 |

| SUBLW                                       |    |

| SUBWF                                       |    |

| SWAPF                                       |    |

| TRIS<br>XORLW                               | -  |

| XORWF                                       |    |

| Section                                     |    |

| INTCON Register                             |    |

| INTEDG bit                                  |    |

| Internal Sampling Switch (Rss) Impedence    |    |

| Interrupts                                  |    |

|                                             |    |

| GP2/INT<br>GPIO Port                        |    |

| Section                                     |    |

| TMR0                                        |    |

| TMR0 Overflow                               |    |

| IORLW Instruction                           |    |

| IORWF Instruction                           |    |

| IRP bit                                     | 15 |

#### к

| KeeLoq® Evaluation and Programming Tools          | . 86 |

|---------------------------------------------------|------|

| L                                                 |      |

| Loading of PC                                     | . 22 |

| M                                                 |      |

| MCLR                                              | 59   |

| Memory                                            | , 55 |

| Data Memory                                       | 11   |

| Program Memory                                    |      |

| Register File Map - PIC12CE67X                    |      |

| MOVF Instruction                                  |      |

| MOVLW Instruction                                 |      |

| MOVWF Instruction                                 |      |

| MPLAB Integrated Development Environment Software |      |

| N                                                 |      |

| NOP Instruction                                   | . 78 |

| 0                                                 |      |

| Opcode                                            | . 69 |

| OPTION Instruction                                |      |

| OPTION Register                                   | -    |

| Orthogonal                                        |      |

| OSC selection                                     |      |

| OSCCAL Register                                   |      |

| Oscillator                                        |      |

| EXTRC                                             | . 58 |

| HS                                                | . 58 |

| INTRC                                             | . 58 |

| LP                                                | . 58 |

| XT                                                | . 58 |

| Oscillator Configurations                         | . 54 |

| Oscillator Types                                  |      |

| EXTRC                                             | . 54 |

| HS                                                | . 54 |

| INTRC                                             | . 54 |

| LP                                                | . 54 |

| XT                                                | . 54 |

| Р                                                 |      |

| Package Marking Information                       | 115  |

| Packaging Information                             |      |

| Paging, Program Memory                            |      |

| PCL                                               |      |

| PCL Register 13, 14                               |      |

| PCLATH                                            | . 59 |

| PCLATH Register 13, 14                            | , 22 |

| PCON Register 20                                  | , 58 |

|                                                   |      |

| Package Marking Information                   |            |

|-----------------------------------------------|------------|

| Packaging Information                         | 115        |

| Paging, Program Memory                        | 22         |

| PCL                                           | 70         |

| PCL Register                                  | 13, 14, 22 |

| PCLATH                                        | 59         |

| PCLATH Register                               | 13, 14, 22 |

| PCON Register                                 | 20, 58     |

| PD bit                                        | 15, 56     |

| PICDEM-1 Low-Cost PIC MCU Demo Board          | 85         |

| PICDEM-2 Low-Cost PIC16CXX Demo Board         |            |

| PICDEM-3 Low-Cost PIC16CXXX Demo Board        | 85         |

| PICSTART® Plus Entry Level Development Syster | n 85       |

| PIE1 Register                                 | 18         |

| Pinout Description - PIC12CE67X               | 9          |

| PIR1 Register                                 | 19         |

| POP                                           |            |

| POR                                           | 58         |

| Oscillator Start-up Timer (OST)               | 53, 58     |

| Power Control Register (PCON)                 |            |

| Power-on Reset (POR)                          |            |

| Power-up Timer (PWRT)                         |            |

| Power-Up-Timer (PWRT)                         |            |

| Time-out Sequence                             |            |

| Time-out Sequence on Power-up                 |            |

| <u>то</u>                                     |            |

| Power                                         |            |

|                                               |            |

#### PIC12C67X PRODUCT IDENTIFICATION SYSTEM

| PART NOXX X /XX XXX |                       |                                                                                                                           | Examples                                                                                                     |

|---------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|                     | Pattern:              | Special Requirements                                                                                                      | a) PIC12CE673-04/P<br>Commercial Temp.,                                                                      |

|                     | Package:              | P = 300 mil PDIP<br>JW = 300 mil Windowed Ceramic Side Brazed                                                             | PDIP Package, 4 MHz, normal VDD limits                                                                       |

|                     | Temperature<br>Range: | SM = 208 mil SOIC<br>- = $0^{\circ}C$ to +70°C<br>I = -40°C to +85°C<br>E = -40°C to +125°C                               | <ul> <li>b) PIC12CE673-04I/P<br/>Industrial Temp., PDIP<br/>package, 4 MHz, normai<br/>VDD limits</li> </ul> |

|                     | Frequency<br>Range:   | 04 = 4 MHz/200 kHz<br>10 = 10 MHz                                                                                         | c) PIC12CE673-10I/P<br>Industrial Temp.,<br>PDIP package, 10 MHz<br>normal VDD limits                        |

|                     | Device                | PIC12CE673<br>PIC12CE674<br>PIC12LCE673<br>PIC12LCE674<br>PIC12CC674                                                      | d) PIC12C671-04/P<br>Commercial Temp.,<br>PDIP Package, 4 MHz,<br>normal VDD limits                          |

|                     |                       | PIC12C672<br>PIC12C671T (Tape & reel for SOIC only)<br>PIC12C672T (Tape & reel for SOIC only)<br>PIC12LC671<br>PIC12LC672 | e) PIC12C671-04I/SM<br>Industrial Temp., SOIC<br>package,4 MHz, norma<br>VDD limits                          |

|                     |                       | PIC12LC671T (Tape & reel for SOIC only)<br>PIC12LC672T (Tape & reel for SOIC only)                                        | f) PIC12C671-04I/P<br>Industrial Temp.,<br>PDIP package, 4 MHz,<br>normal VDD limits                         |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

#### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)