Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed4MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeOTPEEPROM Size16 x 8RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOperating Temperature0°C ~ 70°C (TA)Munting TypeThrough HolePackage / Case8-DIP (0.300°, 7.62mm)Supplier Device Package8-PDIPPurchase URLhttps://www.e-xfl.com/product-detail/microchip-technology/pic12ce673-04-p |                            |                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------|

| Core Size8-BitSpeed4MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeOTPEEPROM Size16 x 8RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300°, 7.62mm)Supplier Device Package8-DIP                                                                                                    | Product Status             | Active                                                                    |

| Speed4MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeOTPEEPROM Size16 x 8RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                 | Core Processor             | PIC                                                                       |

| Connectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeOTPEEPROM Size16 x 8RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                          | Core Size                  | 8-Bit                                                                     |

| PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeOTPEEPROM Size16 x 8RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                       | Speed                      | 4MHz                                                                      |

| Number of I/O5Program Memory Size1.75KB (1K × 14)Program Memory TypeOTPEEPROM Size16 × 8RAM Size128 × 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4×8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                          | Connectivity               | -                                                                         |

| Program Memory Size1.75KB (1K x 14)Program Memory TypeOTPEEPROM Size16 x 8RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                        | Peripherals                | POR, WDT                                                                  |

| Program Memory TypeOTPEEPROM Size16 x 8RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                                                           | Number of I/O              | 5                                                                         |

| EEPROM Size16 x 8RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                                                                                 | Program Memory Size        | 1.75KB (1K x 14)                                                          |

| RAM Size128 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                                                                                                  | Program Memory Type        | ОТР                                                                       |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                                                                                                                 | EEPROM Size                | 16 × 8                                                                    |

| Data ConvertersA/D 4x8bOscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                                                                                                                                                    | RAM Size                   | 128 x 8                                                                   |

| Oscillator TypeInternalOperating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                                                                                                                                                                           | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Operating Temperature0°C ~ 70°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                                                                                                                                                                                                  | Data Converters            | A/D 4x8b                                                                  |

| Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package8-PDIP                                                                                                                                                                                                                                                                                                                                                                                      | Oscillator Type            | Internal                                                                  |

| Package / Case     8-DIP (0.300", 7.62mm)       Supplier Device Package     8-PDIP                                                                                                                                                                                                                                                                                                                                                                                              | Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Supplier Device Package 8-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mounting Type              | Through Hole                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic12ce673-04-p                                                                                                                                                                                                                                                                                                                                                                                          | Supplier Device Package    | 8-PDIP                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce673-04-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| <b>TABLE 3-1:</b> | PIC12C67X PINOUT DESCRIPTION |

|-------------------|------------------------------|

|-------------------|------------------------------|

| Name                     | DIP Pin # | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|-----------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/AN0                  | 7         | I/O           | TTL/ST         | Bi-directional I/O port/serial programming data/analog input 0.<br>Can be software programmed for internal weak pull-up and<br>interrupt-on-pin change. This buffer is a Schmitt Trigger input<br>when used in serial programming mode.                                                                                                                                                                                |

| GP1/AN1/V <sub>REF</sub> | 6         | I/O           | TTL/ST         | Bi-directional I/O port/serial programming clock/analog input 1/<br>voltage reference. Can be software programmed for internal<br>weak pull-up and interrupt-on-pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming mode.                                                                                                                                                            |

| GP2/T0CKI/AN2/INT        | 5         | I/O           | ST             | Bi-directional I/O port/analog input 2. Can be configured as T0CKI or external interrupt.                                                                                                                                                                                                                                                                                                                              |

| GP3/MCLR/Vpp             | 4         | Ι             | TTL/ST         | Input port/master clear (reset) input/programming voltage<br>input. When configured as MCLR, this pin is an active low<br>reset to the device. Voltage on MCLR/VPP must not exceed<br>VDD during normal device operation. Can be software pro-<br>grammed for internal weak pull-up and interrupt-on-pin<br>change. Weak pull-up always on if configured as MCLR. This<br>buffer is Schmitt Trigger when in MCLR mode. |

| GP4/OSC2/AN3/CLKOUT      | 3         | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output/analog input 3.<br>Connections to crystal or resonator in crystal oscillator mode<br>(HS, XT and LP modes only, GPIO in other modes). In EXTRC<br>and INTRC modes, the pin output can be configured to CLK-<br>OUT, which has 1/4 the frequency of OSC1 and denotes the<br>instruction cycle rate.                                                                   |

| GP5/OSC1/CLKIN           | 2         | I/O           | TTL/ST         | Bi-directional IO port/oscillator crystal input/external clock<br>source input (GPIO in INTRC mode only, OSC1 in all other<br>oscillator modes). Schmitt trigger input for EXTRC oscillator<br>mode.                                                                                                                                                                                                                   |

| Vdd                      | 1         | Р             | _              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                                |

| Vss                      | 8         | Р             | _              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                                               |

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input.

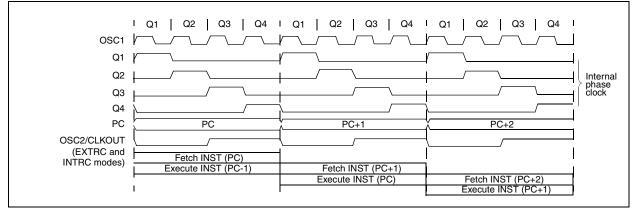

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

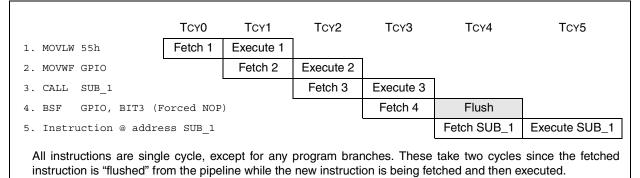

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

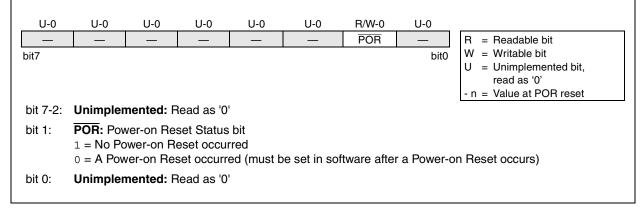

#### 4.2.2.6 PCON REGISTER

The Power Control (PCON) Register contains a flag bit to allow differentiation between a Power-on Reset (POR), an external MCLR Reset and a WDT Reset.

#### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

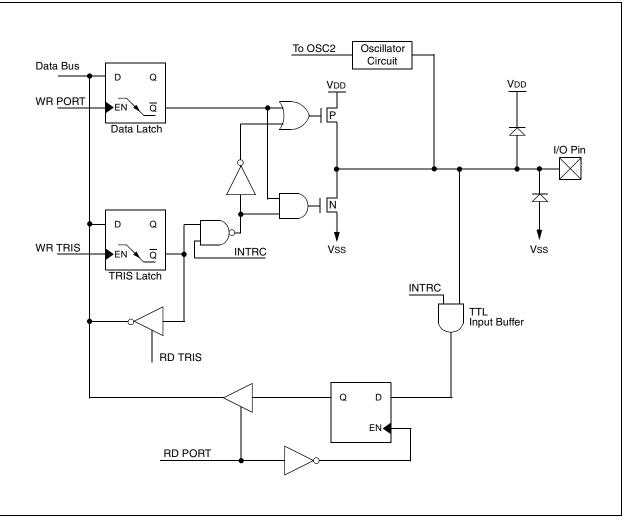

#### FIGURE 5-5: BLOCK DIAGRAM OF GP5/OSC1/CLKIN PIN

## **PIC12C67X**

NOTES:

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

## EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

## EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

#### TABLE 7-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6       | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|--------|-------------|---------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 | module's re | egister |       |       |       |       |       | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE        | TOIE    | INTE  | GPIE  | TOIF  | INTF  | GPIF  | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | GPPU   | INTEDG      | TOCS    | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111       | 1111 1111                       |

| 85h     | TRIS   | _      |             | TRIS5   | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0 | 11 1111         | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

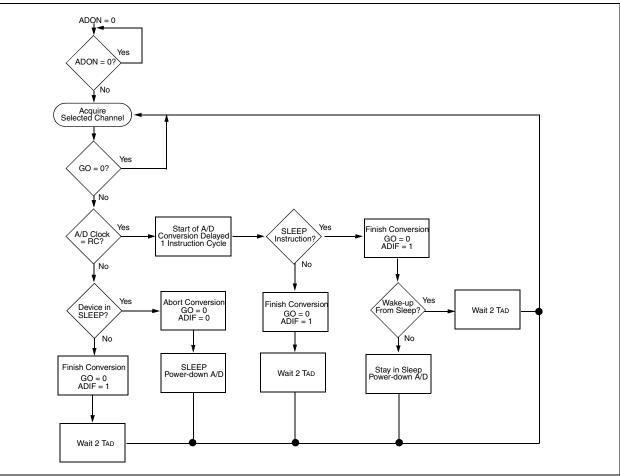

#### 8.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-To-Digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the GP1/AN1/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 Register, shown in Figure 8-1, controls the operation of the A/D module. The ADCON1 Register, shown in Figure 8-2, configures the functions of the port pins. The port pins can be configured as analog inputs (GP1 can also be a voltage reference) or as digital I/O.

- Note 1: If the port pins are configured as analog inputs (reset condition), reading the port (MOVF GPIO,W) results in reading '0's.

- 2: Changing ADCON1 Register can cause the GPIF and INTF flags to be set in the INTCON Register. These interrupts should be disabled prior to modifying ADCON1.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ADCS1 ADCS0 CHS1 CHS0 GO/DONE ADON R = Readable bit reserved reserved W = Writable bit bit0 bit7 U = Unimplemented bit, read as '0' n = Value at POR reset bit 7-6: ADCS<1:0>: A/D Conversion Clock Select bits 00 = Fosc/201 = Fosc/810 = Fosc/3211 = FRC (clock derived from an RC oscillation) Reserved bit 5: bit 4-3: CHS<1:0>: Analog Channel Select bits 00 = channel 0, (GP0/AN0) 01 = channel 1, (GP1/AN1) 10 = channel 2, (GP2/AN2) 11 = channel 3, (GP4/AN3) GO/DONE: A/D Conversion Status bit bit 2: If ADON = 11 = A/D conversion in progress (setting this bit starts the A/D conversion) 0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete) bit 1: Reserved bit 0: ADON: A/D on bit 1 = A/D converter module is operating 0 = A/D converter module is shut off and consumes no operating current

#### REGISTER 8-1: ADCON0 REGISTER (ADDRESS 1Fh)

#### 8.5 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS<1:0> = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared, and the result loaded into the ADRES Register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS<1:0> = 11). To perform an A/D conversion in SLEEP, the GO/DONE bit must be set, followed by the SLEEP instruction.

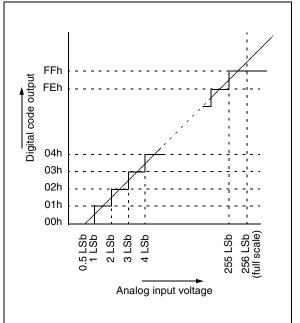

#### 8.6 <u>A/D Accuracy/Error</u>

The overall accuracy of the A/D is less than  $\pm$  1 LSb for VDD = 5V  $\pm$  10% and the analog VREF = VDD. This overall accuracy includes offset error, full scale error, and integral error. The A/D converter is monotonic over the full VDD range. The resolution and accuracy may be less when either the analog reference (VDD) is less than 5.0V or when the analog reference (VREF) is less than VDD.

The maximum pin leakage current is specified in the Device Data Sheet electrical specification, parameter #D060.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from Tosc, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

#### 8.7 Effects of a Reset

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted. The value that is in the ADRES register is not modified for a Reset. The ADRES register will contain unknown data after a Power-on Reset.

#### 8.8 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

| Note: | For the PIC12C67X, care must be taken       |

|-------|---------------------------------------------|

|       | when using the GP4 pin in A/D conver-       |

|       | sions due to its proximity to the OSC1 pin. |

An external RC filter is sometimes added for antialiasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

#### 8.9 <u>Transfer Function</u>

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is 1 LSb (or Analog VREF / 256) (Figure 8-3).

#### FIGURE 8-3: A/D TRANSFER FUNCTION

#### TABLE 8-2: SUMMARY OF A/D REGISTERS

| Address | Name                  | Bit 7              | Bit 6              | Bit 5    | Bit 4 | Bit 3 | Bit 2   | Bit 1    | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|-----------------------|--------------------|--------------------|----------|-------|-------|---------|----------|-------|-------------------------------|---------------------------------|

| 0Bh/8Bh | INTCON <sup>(1)</sup> | GIE                | PEIE               | TOIE     | INTE  | GPIE  | T0IF    | INTF     | GPIF  | x000 000x                     | 0000 000u                       |

| 0Ch     | PIR1                  | —                  | ADIF               | _        | —     | —     | -       | —        | —     | -0                            | -0                              |

| 8Ch     | PIE1                  | —                  | ADIE               | —        | _     | _     | _       | —        | —     | -0                            | -0                              |

| 1Eh     | ADRES                 | A/D Res            | sult Regist        | er       |       |       |         |          |       | xxxx xxxx                     | uuuu uuuu                       |

| 1Fh     | ADCON0                | ADCS1              | ADCS0              | reserved | CHS1  | CHS0  | GO/DONE | reserved | ADON  | 0000 0000                     | 0000 0000                       |

| 9Fh     | ADCON1                | _                  | _                  | _        |       | -     | PCFG2   | PCFG1    | PCFG0 | 000                           | 000                             |

| 05h     | GPIO                  | SCL <sup>(2)</sup> | SDA <sup>(2)</sup> | GP5      | GP4   | GP3   | GP2     | GP1      | GP0   | 11xx xxxx                     | 11uu uuuu                       |

| 85h     | TRIS                  | _                  | _                  | TRIS5    | TRIS4 | TRIS3 | TRIS2   | TRIS1    | TRIS0 | 11 1111                       | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers can be addressed from either bank.

2: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

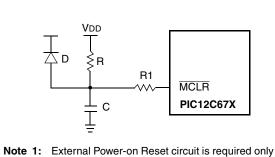

#### FIGURE 9-10: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- **lote 1:** External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- **3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C, in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

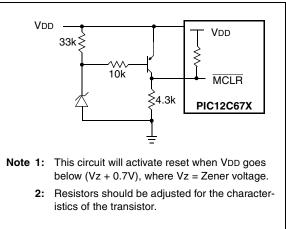

#### FIGURE 9-11: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

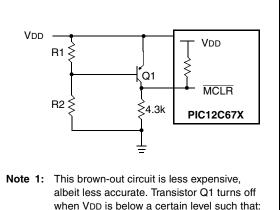

#### FIGURE 9-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

**2:** Resistors should be adjusted for the characteristics of the transistor.

| FIGURE 9-16: WAKE-UP FROM SLEEP THROUGH INTERRUPT |

|---------------------------------------------------|

|---------------------------------------------------|

| ; a1   a2   a3   a<br>osc1 ///////      | 4; Q1  Q2  Q3  Q4<br>_/~~~~ |                       | Q1  Q2  Q3  Q4 | a1 a2 a3 a4<br>/\_/\_/\_/     | 01 02 03 04 | Q1 Q2 Q3 Q4; |

|-----------------------------------------|-----------------------------|-----------------------|----------------|-------------------------------|-------------|--------------|

| CLKOUT(4)                               | -∖/                         | Tost(2)               | /              | \/                            | \/¦         |              |

| GPIO pin                                | <br>                        | x                     |                | I<br>I<br>I                   |             |              |

| GPIF flag<br>(INTCON<0>)                |                             |                       |                | Interrupt Latency<br>(Note 3) |             | i            |

| GIE bit<br>(INTCON<7>)                  | <br><br>                    | Processor in<br>SLEEP |                |                               |             |              |

| INSTRUCTION FLOW                        | 1                           |                       |                | i i                           |             | 1            |

| РС Х РС                                 | X PC+1                      | X PC+2                | PC+2           | X PC + 2                      | X 0004h     | 0005h        |

| Instruction<br>fetched Inst(PC) = SLEEF | Inst(PC + 1)                | I I I                 | Inst(PC + 2)   | I I I                         | Inst(0004h) | Inst(0005h)  |

| Instruction<br>executed Inst(PC - 1)    | SLEEP                       | I i                   | Inst(PC + 1)   | Dummy cycle                   | Dummy cycle | Inst(0004h)  |

Note 1: XT, HS or LP oscillator mode assumed.

- 2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for INTRC and EXTRC osc mode.

- **3:** GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in XT, HS or LP osc modes, but shown here for timing reference.

#### 9.9 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 9.10 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

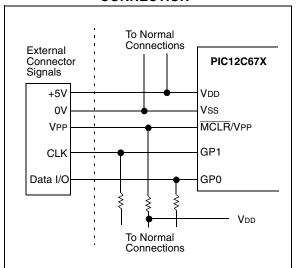

#### 9.11 In-Circuit Serial Programming

PIC12C67X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the GP1 and GP0 pins low, while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). GP1 (clock) becomes the programming clock and GP0 (data) becomes the programming data. Both GP0 and GP1 are Schmitt Trigger inputs in this mode.

After reset, and if the device is placed into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC12C67X Programming Specifications.

#### FIGURE 9-17: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

#### 10.1 <u>Special Function Registers as</u> <u>Source/Destination</u>

The PIC12C67X's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 10.1.1 STATUS AS DESTINATION

If an instruction writes to STATUS, the Z, C and DC bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF STATUS will clear register STATUS, and then set the Z bit leaving 0000 0100b in the register.

#### 10.1.2 TRIS AS DESTINATION

Bit 3 of the TRIS register always reads as a '1' since GP3 is an input only pin. This fact can affect some read-modify-write operations on the TRIS register.

#### 10.1.3 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCL \to dest$                                                                               |

|--------------------|----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                       |

| Read-Modify-Write: | PCL $\rightarrow$ ALU operand<br>PCLATH $\rightarrow$ PCH;<br>8-bit result $\rightarrow$ PCL |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 10.1.4 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write). The user should keep this in mind when operating on special function registers, such as ports.

#### 10.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                       |                    |         |  |  |  |  |

|------------------|---------------------------------------------------------|--------------------|---------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                |                    |         |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                     |                    |         |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                       |                    |         |  |  |  |  |

| Status Affected: | C, DC, Z                                                |                    |         |  |  |  |  |

| Encoding:        | 11 111x                                                 | kkkk               | kkkk    |  |  |  |  |

| Description:     | The contents of added to the eig the result is placter. | ht bit literal     | 'k' and |  |  |  |  |

| Words:           | 1                                                       |                    |         |  |  |  |  |

| Cycles:          | 1                                                       |                    |         |  |  |  |  |

| Example          | ADDLW 0x15                                              |                    |         |  |  |  |  |

|                  | Before Instruction<br>W =<br>After Instruction<br>W =   | on<br>0x10<br>0x25 |         |  |  |  |  |

| ANDLW            | And Literal with W                                                                                                       |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                 |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                        |  |  |  |  |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                        |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |  |  |  |  |  |

| Words:           | 1                                                                                                                        |  |  |  |  |  |

| Cycles:          | 1                                                                                                                        |  |  |  |  |  |

| Example          | ANDLW 0x5F                                                                                                               |  |  |  |  |  |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                          |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                         |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                                |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. |

| Words:           | 1                                                                                                                                                                                |

| Cycles:          | 1                                                                                                                                                                                |

| Example          | addwf fsr, <b>O</b>                                                                                                                                                              |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                      |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |

| Example          | andwf fsr, <b>1</b>                                                                                                                                         |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |

# **PIC12C67X**

| BTFSS                                                                                                    | Bit Test f, Skip if Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                                                  | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Operands:                                                                                                | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Operation:                                                                                               | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Status Affected:                                                                                         | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Encoding:                                                                                                | 01 11bb bfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Description:                                                                                             | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a 2 cycle instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Cycles:                                                                                                  | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Example                                                                                                  | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CO<br>TRUE • DE<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                                                                                                          | PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                                                                                          | if FLAG<1> = 1,<br>PC = address TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| CALL                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| CALL<br>Syntax:                                                                                          | PC = address TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                                                                                                          | PC = address TRUE Call Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Syntax:                                                                                                  | PC = address TRUE  Call Subroutine [label] CALL k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                     | PC = address TRUE<br>Call Subroutine<br>[ label ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                                       | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | PC = address TRUE<br>Call Subroutine<br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11><br>None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | PC =address TRUECall Subroutine[ label ] CALL k $0 \le k \le 2047$ (PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>None100kkkkkkkkkkkkkkkCall Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k \\ 0 \le k \le 2047 \\ (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0 >, \\ (PCLATH < 4:3 >) \rightarrow PC < 12:11 > \\ \hline None \\ \hline 10 0 kkk kkk kkk \\ \hline Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits < 10:0 >. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. \\ \hline \end{tabular}$                                                                                                                                                                                                                                                |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $PC = address TRUE$ $[label] CALL k$ $0 \le k \le 2047$ $(PC)+1 \rightarrow TOS, k \rightarrow PC < 12:11 >$ $PC = C < C < C < C < C < C < C < C < C < $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k \\ 0 \le k \le 2047 \\ (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<4:3>) \rightarrow PC<12:11> \\ \hline None \\ \hline 10  0kkk  kkkk  kkkk \\ \hline Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. \\ 1 \\ 2 \\ HERE  CALL \\ \underline{THER} \\ \hline HERE \\ \hline \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ |  |  |  |  |  |

| CLRF             | Clear f                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                                                                                          |

| Operands:        | $0 \leq f \leq 127$                                                                                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                                                                   |

| Status Affected: | Z                                                                                                                                       |

| Encoding:        | 00 0001 1fff ffff                                                                                                                       |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                                                                          |

| Words:           | 1                                                                                                                                       |

| Cycles:          | 1                                                                                                                                       |

| Example          | CLRF FLAG_REG                                                                                                                           |

|                  | $\begin{array}{rcl} Before \ Instruction \\ FLAG_REG & = & 0x5A \\ After \ Instruction \\ FLAG_REG & = & 0x00 \\ Z & = & 1 \end{array}$ |

| CLRW             | Clear W                                                              |                       |            |           |  |  |

|------------------|----------------------------------------------------------------------|-----------------------|------------|-----------|--|--|

| Syntax:          | [label] CLRW                                                         |                       |            |           |  |  |

| Operands:        | None                                                                 |                       |            |           |  |  |

| Operation:       | $\begin{array}{c} 00h \rightarrow (V \\ 1 \rightarrow Z \end{array}$ | V)                    |            |           |  |  |

| Status Affected: | Z                                                                    |                       |            |           |  |  |

| Encoding:        | 00                                                                   | 0001                  | 0000       | 0011      |  |  |

| Description:     | W registe<br>is set.                                                 | er is cle             | ared. Zero | o bit (Z) |  |  |

| Words:           | 1                                                                    |                       |            |           |  |  |

| Cycles:          | 1                                                                    |                       |            |           |  |  |

| Example          | CLRW                                                                 |                       |            |           |  |  |

|                  | Before In                                                            | structio<br>W =       | on<br>0x5A |           |  |  |

|                  |                                                                      | ruction<br>W =<br>Z = | 0x00<br>1  |           |  |  |

TABLE 11-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                    |                                                                                                                                                                                                                                                                       | PIC12CXXX                | PIC14000                 | PIC16C5X    | PIC16C6X  | PIC16CXXX  | PIC16F62X | PIC16C7X       | XX7Oðfolg | PIC16C8X  | PIC16F8XX  | PIC16C9XX | PIC17C4X | XXTOTIOI9  | PIC18CXX2 | 63CXX<br>52CXX/<br>54CXX/ | хххэн      | МСВЕХХХ    | MCP2510 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|-------------|-----------|------------|-----------|----------------|-----------|-----------|------------|-----------|----------|------------|-----------|---------------------------|------------|------------|---------|

| ≥ ∩<br>s oo_       | MPLAB <sup>®</sup> Integrated<br>Development Environment                                                                                                                                                                                                              | >                        | >                        | >           | >         | >          | >         | >              | >         | >         | >          | >         | >        | >          | >         |                           |            |            |         |

|                    | MPLAB <sup>®</sup> C17 Compiler                                                                                                                                                                                                                                       |                          |                          |             |           |            |           |                |           |           |            |           | >        | >          |           |                           |            |            |         |

|                    | MPLAB <sup>®</sup> C18 Compiler                                                                                                                                                                                                                                       |                          |                          |             |           |            |           |                |           |           |            |           |          |            | >         |                           |            |            |         |

|                    | MPASM/MPLINK                                                                                                                                                                                                                                                          | >                        | ~                        | >           | >         | >          | >         | >              | >         | >         | >          | >         | >        | >          | >         | >                         | >          |            |         |

|                    | MPLAB <sup>®</sup> -ICE                                                                                                                                                                                                                                               | >                        | ~                        | >           | >         | >          | ** `      | >              | >         | >         | >          | >         | >        | >          | >         |                           |            |            |         |

|                    | PICMASTER/PICMASTER-CE                                                                                                                                                                                                                                                | `                        | ~                        | >           | >         | >          |           | >              | >         | >         |            | >         | ~        | >          |           |                           |            |            |         |

| nm⊒                | ICEPIC™ Low-Cost<br>In-Circuit Emulator                                                                                                                                                                                                                               | ~                        |                          | >           | >         | >          |           | >              | >         | >         |            | >         |          |            |           |                           |            |            |         |

| ם ≤<br>Depnââeı    | MPLAB <sup>®</sup> -ICD In-Circuit<br>Debugger                                                                                                                                                                                                                        |                          |                          |             | *>        |            |           | *>             |           |           | >          |           |          |            |           |                           |            |            |         |

|                    | PICSTART <sup>®</sup> Plus<br>Low-Cost Universal Dev. Kit                                                                                                                                                                                                             | >                        | >                        | >           | >         | >          | **^       | >              | `         | >         | >          | >         | `        | >          | `         |                           |            |            |         |

| Program<br>Program | PRO MATE <sup>®</sup> II<br>Universal Programmer                                                                                                                                                                                                                      | >                        | >                        | >           | >         | >          | ** ^      | >              | >         | >         | >          | >         | >        | >          | >         | >                         | >          |            |         |

| S                  | SIMICE                                                                                                                                                                                                                                                                | >                        |                          | >           |           |            |           |                |           |           |            |           |          |            |           |                           |            |            |         |