Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 14110                  |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | 16 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

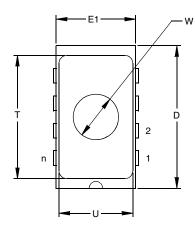

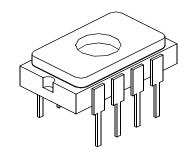

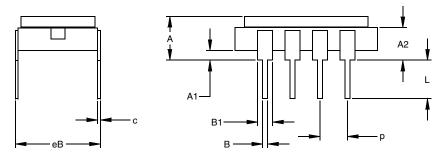

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 8-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce673-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **PIC12C67X**

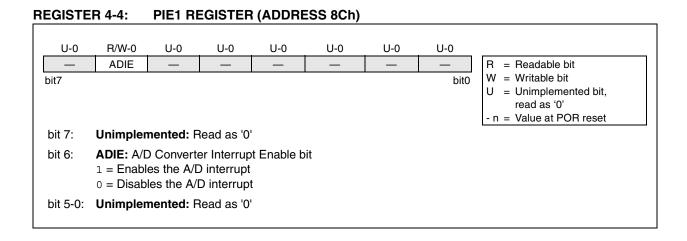

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the Peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

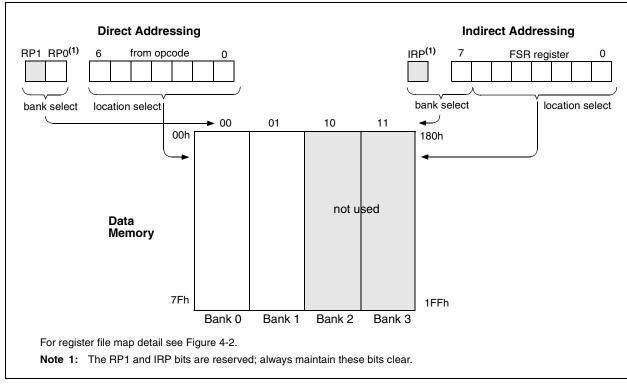

#### 4.5 Indirect Addressing, INDF and FSR Registers

The INDF Register is not a physical register. Addressing the INDF Register will cause indirect addressing.

Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF Register itself indirectly (FSR = '0') will read 00h. Writing to the INDF Register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR Register and the IRP bit (STATUS<7>), as shown in Figure 4-4. However, IRP is not used in the PIC12C67X.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-1.

#### EXAMPLE 4-1: INDIRECT ADDRESSING

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ;to RAM              |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR,F | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

#### FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

NOTES:

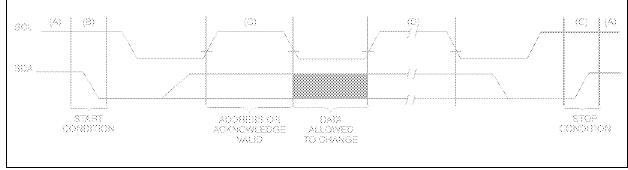

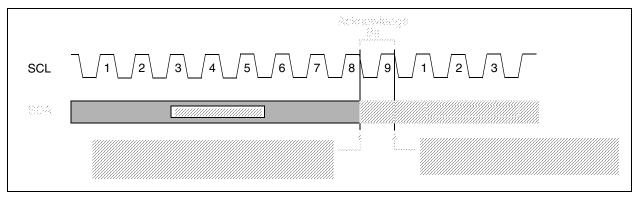

FIGURE 6-4: ACKNOWLEDGE TIMING

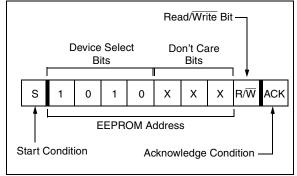

#### 6.2 Device Addressing

After generating a START condition, the processor transmits a control byte consisting of a EEPROM address and a Read/Write bit that indicates what type of operation is to be performed. The EEPROM address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one, a read operation is selected, and when set to a zero, a write operation is selected (Figure 6-5). The bus is monitored for its corresponding EEPROM address all the time. It generates an acknowledge bit if the EEPROM address was true and it is not in a programming mode.

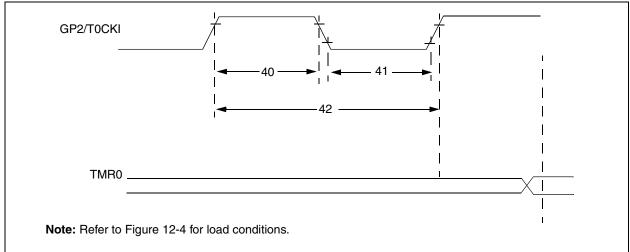

#### 7.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

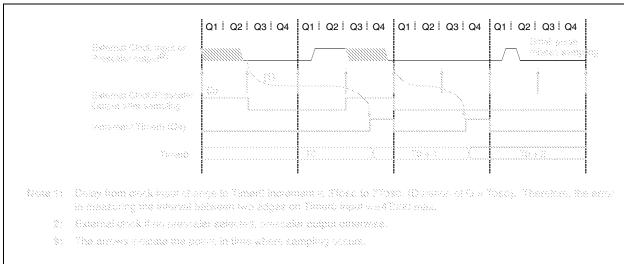

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is used as the clock source. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for TOCKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

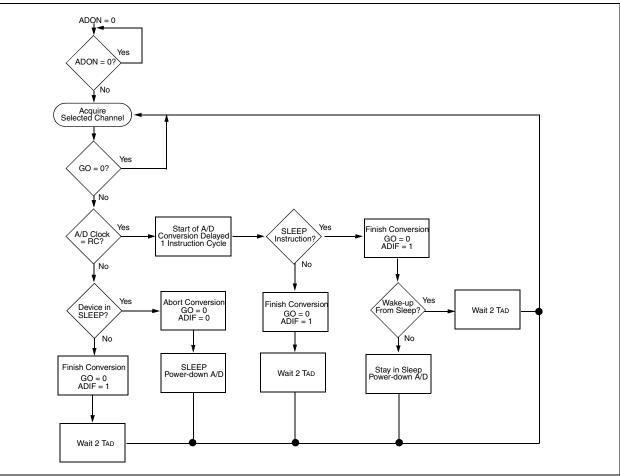

#### TABLE 8-2: SUMMARY OF A/D REGISTERS

| Address | Name                  | Bit 7              | Bit 6               | Bit 5    | Bit 4 | Bit 3 | Bit 2   | Bit 1     | Bit 0     | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|-----------------------|--------------------|---------------------|----------|-------|-------|---------|-----------|-----------|-------------------------------|---------------------------------|

| 0Bh/8Bh | INTCON <sup>(1)</sup> | GIE                | PEIE                | TOIE     | INTE  | GPIE  | T0IF    | INTF      | GPIF      | x000 000x                     | 0000 000u                       |

| 0Ch     | PIR1                  | —                  | ADIF                | _        | —     | —     | -       | —         | —         | -0                            | -0                              |

| 8Ch     | PIE1                  | —                  | ADIE                | —        | _     | _     | _       | —         | —         | -0                            | -0                              |

| 1Eh     | ADRES                 | A/D Res            | A/D Result Register |          |       |       |         | xxxx xxxx | uuuu uuuu |                               |                                 |

| 1Fh     | ADCON0                | ADCS1              | ADCS0               | reserved | CHS1  | CHS0  | GO/DONE | reserved  | ADON      | 0000 0000                     | 0000 0000                       |

| 9Fh     | ADCON1                | _                  | _                   | _        |       | -     | PCFG2   | PCFG1     | PCFG0     | 000                           | 000                             |

| 05h     | GPIO                  | SCL <sup>(2)</sup> | SDA <sup>(2)</sup>  | GP5      | GP4   | GP3   | GP2     | GP1       | GP0       | 11xx xxxx                     | 11uu uuuu                       |

| 85h     | TRIS                  | _                  | _                   | TRIS5    | TRIS4 | TRIS3 | TRIS2   | TRIS1     | TRIS0     | 11 1111                       | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers can be addressed from either bank.

2: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC12C67X can be operated in seven different oscillator modes. The user can program three configuration bits (Fosc<2:0>) to select one of these seven modes:

- LP: Low Power Crystal

- HS: High Speed Crystal/Resonator

- XT: Crystal/Resonator

- INTRC\*: Internal 4 MHz Oscillator

- EXTRC\*: External Resistor/Capacitor

\*Can be configured to support CLKOUT

### 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

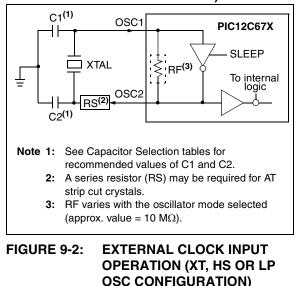

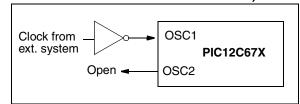

In XT, HS or LP modes, a crystal or ceramic resonator is connected to the GP5/OSC1/CLKIN and GP4/OSC2 pins to establish oscillation (Figure 9-1). The PIC12C67X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, HS or LP modes, the device can have an external clock source drive the GP5/OSC1/CLKIN pin (Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (XT, HS OR LP OSC CONFIGURATION)

#### TABLE 9-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS - PIC12C67X

| Osc<br>Type        | Resonator<br>Freq | Cap. Range<br>C1          | Cap. Range |

|--------------------|-------------------|---------------------------|------------|

| XT                 | 455 kHz           | 22-100,pF                 | 22-100 pF  |

|                    | 2.0 MHz           | 15-68 pf                  | レ15-68 pF  |

|                    | 4.0 MHz           | ~ { <b>1</b> ,5+68 pf ~ ~ | 15-68 pF   |

| HS                 | 4.0-MHX           | \ <b>15-68</b> pF         | 15-68 pF   |

|                    | 8,0 MHz           | 10-68 pF                  | 10-68 pF   |

| $\widehat{\Omega}$ | tp:0 MHz          | 10-22 pF                  | 10-22 pF   |

These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR - PIC12C67X

| - FIC 12007 A   |                       |                     |                        |

|-----------------|-----------------------|---------------------|------------------------|

| Osc<br>Type     | Resonator<br>Freq     | Cap. Range<br>C1    | Cap. Range<br>C2       |

| LP              | 32 kHz <sup>(1)</sup> | 15 pF               | 15 pF 🚽                |

|                 | 100 kHz               | 15-30 pF            | 30-47 p⊄               |

|                 | 200 kHz               | 15-30 pF            | 15-83 pF               |

| XT              | 100 kHz               | 15-30 pF            | 200-300 pF             |

|                 | 200 kHz               | 15-30 pE            | 100-200 pF             |

|                 | 455 kHz               | 15-30 pF            | <sup>™</sup> 15-100 pF |

|                 | 1 MHz 🔨               | 1,15-30.pF          | 15-30 pF               |

|                 | 2, MAHz ∖∖            | \ <b>∖</b> 19-30 pF | 15-30 pF               |

|                 | (AMHz)                | 15-47 pF            | 15-47 pF               |

| HS              | 4 10AHz               | 15-30 pF            | 15-30 pF               |

| $(\mathcal{O})$ | 😕 🖲 MHz               | 15-30 pF            | 15-30 pF               |

| VZ Z            | 10 MHz                | 15-30 pF            | 15-30 pF               |

Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

These values are for design guidance only. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 9.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at  $V_{DD} = 5V$  and  $25^{\circ}$ C. See Section 13.0 for information on variation over voltage and temperature.

In addition, a calibration instruction is programmed into the last address of the program memory which contains the calibration value for the internal RC oscillator. This value is programmed as a RETLW XX instruction where XX is the calibration value. In order to retrieve the calibration value, issue a CALL YY instruction where YY is the last location in program memory (03FFh for the PIC12C671 and the PIC12CE673, 07FFh for the PIC12C672 and the PIC12CE674). Control will be returned to the user's program with the calibration value loaded into the W register. The program should then perform a MOVWF OSCCAL instruction to load the value into the internal RC oscillator trim register.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency. Bits <7:4>, CAL<3:0> are used for fine calibration, while bit 3, CALFST, and bit 2, CALSLW, are used for more coarse adjustment. Adjusting CAL<3:0> from 0000 to 1111 yields a higher clock speed. Set CALFST = 1 for greater increase in frequency or set CALSLW = 1 for greater decrease in frequency. Note that bits 1 and 0 of OSCCAL are unimplemented and should be written as 0 when modifying OSCCAL for compatibility with future devices.

| Note: | Please note that erasing the device will       |

|-------|------------------------------------------------|

|       | also erase the pre-programmed internal         |

|       | calibration value for the internal oscillator. |

|       | The calibration value must be saved prior      |

|       | to erasing the part.                           |

#### 9.2.6 CLKOUT

The PIC12C67X can be configured to provide a clock out signal (CLKOUT) on pin 3 when the configuration word address (2007h) is programmed with Fosc2, Fosc1, and Fosc0, equal to 101 for INTRC or 111 for EXTRC. The oscillator frequency, divided by 4, can be used for test purposes or to synchronize other logic.

#### 9.3 <u>Reset</u>

The PIC12C67X differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), MCLR Reset, WDT Reset, and MCLR Reset during SLEEP. They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations, as indicated in Table 9-5. These bits are used in software to determine the nature of the reset. See Table 9-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 9-6.

The PIC12C67X has a MCLR noise filter in the MCLR reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

When MCLR is asserted, the state of the OSC1/CLKIN and CLKOUT/OSC2 pins are as follows:

## TABLE 9-3:CLKIN/CLKOUT PIN STATESWHEN MCLR ASSERTED

| Oscillator Mode          | OSC1/CLKIN Pin                                                | OSC2/CLKout Pin               |

|--------------------------|---------------------------------------------------------------|-------------------------------|

| EXTRC, CLKOUT<br>on OSC2 | OSC1 pin is<br>tristated and<br>driven by external<br>circuit | OSC2 pin is driven<br>low     |

| EXTRC, OSC2 is<br>I/O    | OSC1 pin is<br>tristated and<br>driven by external<br>circuit | OSC2 pin is<br>tristate input |

| INTRC, CLKOUT<br>on OSC2 | OSC1 pin is<br>tristate input                                 | OSC2 pin is driven<br>low     |

| INTRC, OSC2 is<br>I/O    | OSC1 pin is<br>tristate input                                 | OSC2 pin is tristate input    |

#### TABLE 9-6: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | u-               |

| WDT Reset during normal operation  | 000h                  | 0000 uuuu          | u-               |

| WDT Wake-up from SLEEP             | PC + 1                | uuu0 0uuu          | u-               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

#### TABLE 9-7: INITIALIZATION CON\DITIONS FOR ALL REGISTERS

| Power-on Reset | MCLR Resets<br>WDT Reset                                                                                                                                                                                                                                                                        | Wake-up via<br>WDT or Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xxxx xxxx      | <u>uuuu</u> uuuu                                                                                                                                                                                                                                                                                | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                       | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| xxxx xxxx      | นนนน นนนน                                                                                                                                                                                                                                                                                       | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                       | PC + 1 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                                                                                                                                                                                                                        | uuuq quuu <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| xxxx xxxx      | นนนน นนนน                                                                                                                                                                                                                                                                                       | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11xx xxxx      | 11uu uuuu                                                                                                                                                                                                                                                                                       | 11uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| xx xxxx        | uu uuuu                                                                                                                                                                                                                                                                                         | uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0 0000         | 0 0000                                                                                                                                                                                                                                                                                          | u uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0000 000x      | 0000 000u                                                                                                                                                                                                                                                                                       | uuuu uqqq <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -0             | -0                                                                                                                                                                                                                                                                                              | - <u>q</u> (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                       | uuuu uquu <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1111 1111      | 1111 1111                                                                                                                                                                                                                                                                                       | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11 1111        | 11 1111                                                                                                                                                                                                                                                                                         | uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -0             | -0                                                                                                                                                                                                                                                                                              | -u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0-             | u-                                                                                                                                                                                                                                                                                              | u-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0111 00        | uuuu uu                                                                                                                                                                                                                                                                                         | uuuu uu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 000            | 000                                                                                                                                                                                                                                                                                             | uuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | XXXX XXXX         0000 0000         XXXX XXXX         0000 0000         0001 1xxx         XXXX XXXX         11xx XXXX         11xx XXXX        xx XXXX        xx XXXX        0 0000         0000 000x         -0         0000 0000         1111 1111        11 1111         -0         0.011 00 | WDT Reset           xxxx xxxx         uuuu uuuu           0000 0000         0000 0000           xxxx xxxx         uuuu uuuu           0000 0000         0000 0000           xxxx xxxx         uuuu uuuu           0001 1xxx         000q quuu <sup>(3)</sup> xxxx xxxx         uuuu uuuu           11xx xxxx         11uu uuuu           11xx xxxx         11uu uuuu          xx xxxx        uu uuuu          xx xxxx        uu uuuu          0 0000        0 0000           0000 000x         0000 000u           0000 000x         0000 000u           -0         -0           0000 0000         0000 0000           1111 111         1111 111          11 111        11 1111           -0            -0            -0            -0            -0            -0            -0            -0 </td |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: One or more bits in INTCON and PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 9-5 for reset value for specific condition.

4: If wake-up was due to A/D completing then bit 6 = 1, all other interrupts generating a wake-up will cause bit 6 = u.

5: If wake-up was due to A/D completing then bit 3 = 0, all other interrupts generating a wake-up will cause bit 3 = u.

# **PIC12C67X**

| GOTO                              | Unconditional Branch                                                                                                                                                                                  | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [ <i>label</i> ] GOTO k                                                                                                                                                                               | Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                       |

| Operands:                         | $0 \le k \le 2047$                                                                                                                                                                                    | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                        |

| Operation:                        | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                       | Operation:       | $d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                        |

| Status Affected:                  | None                                                                                                                                                                                                  | Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |

| Encoding:                         | 10 1kkk kkkk kkkk                                                                                                                                                                                     | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                                        |

| Description:<br>Words:<br>Cycles: | GOTO is an unconditional branch.<br>The eleven bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two<br>cycle instruction.<br>1 | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded. A NOP is executed<br>instead making it a two cycle<br>instruction. |

| Example                           | GOTO THERE                                                                                                                                                                                            | Words:           | 1                                                                                                                                                                                                                                                                                                                                        |

|                                   | After Instruction<br>PC = Address THERE                                                                                                                                                               | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                                     |

|                                   |                                                                                                                                                                                                       | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE<br>•                                                                                                                                                                                                                                                                                         |

|                                   |                                                                                                                                                                                                       |                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1                                                                                                                                                                                                                                                            |

| INCF             | Increment f                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                          |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                        |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                        |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'. |

| Words:           | 1                                                                                                                                                                        |

| Cycles:          | 1                                                                                                                                                                        |

| Example          | INCF CNT, 1                                                                                                                                                              |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction                                                                                                           |

|                  | $\begin{array}{rcl} CNT &=& 0x00 \\ Z &=& 1 \end{array}$                                                                                                                 |

| IORLW            | Inclusive OR Literal with W                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                                              |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                |

| Description:     | The contents of the W register are OR'ed with the eight bit literal 'k'. The result is placed in the W register. |

| Words:           | 1                                                                                                                |

| Cycles:          | 1                                                                                                                |

| Example          | IORLW 0x35                                                                                                       |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                         |

if CNT=

PC =

if CNT≠

=

PC

0,

0,

address CONTINUE

address HERE +1

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

#### 11.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 11.6 <u>MPLAB-ICE High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PIC microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PIC MCU.

#### 11.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PIC microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

#### 11.8 <u>ICEPIC</u>

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

#### 11.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

#### 11.10 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In

#### 12.0 ELECTRICAL SPECIFICATIONS FOR PIC12C67X

#### Absolute Maximum Ratings †

| <b>3</b>                                                                                                       |                                    |

|----------------------------------------------------------------------------------------------------------------|------------------------------------|

| Ambient temperature under bias                                                                                 | 40° to +125°C                      |

| Storage temperature                                                                                            | –65°C to +150°C                    |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | –0.3V to (VDD + 0.3V)              |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.0V                         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                               | 700 mW                             |

| Maximum current out of Vss pin                                                                                 | 200 mA                             |

| Maximum current into VDD pin                                                                                   |                                    |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                   | ±20 mA                             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                 |                                    |

| Maximum output current sunk by any I/O pin                                                                     | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                  | 25 mA                              |

| Maximum current sunk by GPIO pins combined                                                                     | 100 mA                             |

| Maximum current sourced by GPIO pins combined                                                                  | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VO | OH) x IOH} + $\Sigma$ (VOI x IOL). |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| DC CH4      | ARACTERISTICS                                                                         |                                                                                 | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C &\leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ -40^{\circ}C &\leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ -40^{\circ}C &\leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |  |                         |            |                                      |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------|------------|--------------------------------------|--|--|--|--|

| Parm<br>No. | Characteristic                                                                        | Sym         Min         Typ <sup>(1)</sup> Max         Units         Conditions |                                                                                                                                                                                                                                                                                                                               |  |                         |            |                                      |  |  |  |  |

|             | LP Oscillator Operating<br>Frequency<br>INTRC/EXTRC Oscillator<br>Operating Frequency | Fosc                                                                            | 0                                                                                                                                                                                                                                                                                                                             |  | 200<br>4 <sup>(6)</sup> | kHz<br>MHz | All temperatures<br>All temperatures |  |  |  |  |

|             | XT Oscillator Operating<br>Frequency                                                  |                                                                                 | 0                                                                                                                                                                                                                                                                                                                             |  | 4                       | MHz        | All temperatures                     |  |  |  |  |

|             | HS Oscillator Operating<br>Frequency                                                  |                                                                                 | 0 10 MHz All temperatures                                                                                                                                                                                                                                                                                                     |  |                         |            |                                      |  |  |  |  |

I hese parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD,

$\overline{MCLR} = VDD; WDT$  disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

#### 12.2 DC Characteristics: PIC12LC671/672 (Commercial, Industrial) PIC12LCE673/674 (Commercial, Industrial)

| DC CHAF               | RACTERISTICS                                  |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |                  |          |                                                                                                                             |  |  |  |

|-----------------------|-----------------------------------------------|-------|------------------------------------------------------|------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.          | Characteristic                                | Sym   | Min                                                  | Тур†       | Max              | Units    | Conditions                                                                                                                  |  |  |  |

| D001                  | Supply Voltage                                | Vdd   | 2.5                                                  |            | 5.5              | V        |                                                                                                                             |  |  |  |

| D002                  | RAM Data Retention<br>Voltage <sup>(2)</sup>  | Vdr   |                                                      | 1.5*       |                  | V        | Device in SLEEP mode                                                                                                        |  |  |  |

| D003                  | VDD Start Voltage to<br>ensure Power-on Reset | VPOR  |                                                      | Vss        |                  | V        | See section on Power-on Reset for details                                                                                   |  |  |  |

| D004                  | VDD Rise Rate to ensure<br>Power-on Reset     | Svdd  | 0.05*                                                |            |                  | V/ms     | See section on Power-on Reset for details                                                                                   |  |  |  |

| D010                  | Supply Current <sup>(3)</sup>                 | IDD   | —                                                    | 0.4        | 2.1              | mA       | Fosc = 4MHz, VDD = 2.5V<br>XT and EXTRC mode (Note 4)                                                                       |  |  |  |

| D010C<br>D010A        |                                               |       | _                                                    | 0.4<br>15  | 2.1<br>33        | mA<br>μA | Fosc = 4MHz, VDD = 2.5V<br>INTRC mode (Note 6)<br>Fosc = 32kHz, VDD = 2.5V, WDT disabled<br>LP mode, Industrial Temperature |  |  |  |

| D020<br>D021<br>D021B | Power-down Current <sup>(5)</sup>             | IPD   | _                                                    | 0.2<br>0.2 | 5<br>6           | μΑ<br>μΑ | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                                                                            |  |  |  |

|                       | Watchdog Timer Current                        | ΔIWDT | —                                                    | 2.0<br>2.0 | 4<br>6           | μΑ<br>μΑ | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                                                                            |  |  |  |

|                       | LP Oscillator Operating<br>Frequency          | Fosc  | 0                                                    |            | 200              | kHz      | All temperatures                                                                                                            |  |  |  |

|                       | INTRC/EXTRC Oscillator<br>Operating Frequency |       | -                                                    |            | 4 <sup>(6)</sup> | MHz      | All temperatures                                                                                                            |  |  |  |

|                       | XT Oscillator Operating<br>Frequency          |       | 0                                                    |            | 4                | MHz      | All temperatures                                                                                                            |  |  |  |

|                       | HS Oscillator Operating<br>Frequency          |       | 0                                                    |            | 10               | MHz      | All temperatures                                                                                                            |  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

#### 12.5 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2pp            | oS                                  | 3. TCC:ST | (I <sup>2</sup> C specifications only) |  |

|-----------------------|-------------------------------------|-----------|----------------------------------------|--|

| 2. TppS               |                                     | 4. Ts     | (I <sup>2</sup> C specifications only) |  |

| Т                     |                                     |           |                                        |  |

| F                     | Frequency                           | Т         | Time                                   |  |

| Lowercas              | se letters (pp) and their meanings: | ·         |                                        |  |

| рр                    |                                     |           |                                        |  |

| сс                    | CCP1                                | OSC       | OSC1                                   |  |

| ck                    | CLKOUT                              | rd        | RD                                     |  |

| CS                    | CS                                  | rw        | RD or WR                               |  |

| di                    | SDI                                 | sc        | SCK                                    |  |

| do                    | SDO                                 | SS        | SS                                     |  |

| dt                    | Data in                             | tO        | TOCKI                                  |  |

| io                    | I/O port                            | t1        | T1CKI                                  |  |

| mc                    | MCLR                                | wr        | WR                                     |  |

| Upperca               | se letters and their meanings:      |           |                                        |  |

| S                     |                                     |           |                                        |  |

| F                     | Fall                                | Р         | Period                                 |  |

| Н                     | High                                | R         | Rise                                   |  |

| I                     | Invalid (Hi-impedance)              | V         | Valid                                  |  |

| L                     | Low                                 | Z         | Hi-impedance                           |  |

| I <sup>2</sup> C only |                                     |           |                                        |  |

| AA                    | output access                       | High      | High                                   |  |

| BUF                   | Bus free                            | Low       | Low                                    |  |

| Tcc:st (I             | <sup>2</sup> C specifications only) |           |                                        |  |

| CC                    |                                     |           |                                        |  |

| HD                    | Hold                                | SU        | Setup                                  |  |

| ST                    |                                     |           |                                        |  |

| DAT                   | DATA input hold                     | STO       | STOP condition                         |  |

| STA                   | START condition                     |           |                                        |  |

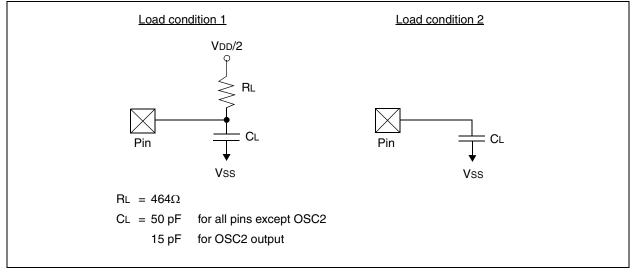

#### FIGURE 12-4: LOAD CONDITIONS

#### FIGURE 12-8: TIMER0 CLOCK TIMINGS

#### TABLE 12-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteris                            | tic            | Min                                       | Тур†      | Max | Units | Conditions                            |  |

|--------------|-----------|----------------------------------------|----------------|-------------------------------------------|-----------|-----|-------|---------------------------------------|--|

| 40*          | Tt0H      | T0CKI High Pulse Width                 | No Prescaler   | 0.5TCY + 20                               | —         | —   | ns    | Must also meet                        |  |

|              |           |                                        | With Prescaler | 10                                        | —         | —   | ns    | parameter 42                          |  |

| 41*          | Tt0L      | Tt0L T0CKI Low Pulse Width             |                | 0.5TCY + 20                               | -         | _   | ns    | Must also meet                        |  |

|              |           |                                        | With Prescaler | 10                                        | -         | _   | ns    | parameter 42                          |  |

| 42*          | Tt0P      | T0CKI Period                           | No Prescaler   | TCY + 40                                  | —         | _   | ns    |                                       |  |

|              |           |                                        | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _         | —   | ns    | N = prescale<br>value (2, 4,,<br>256) |  |

| 48           | TCKE2tmr1 | Delay from external clock of increment | 2Tosc          | _                                         | 7Tos<br>c |     |       |                                       |  |

\* These parameters are characterized but not tested.