Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | 16 × 8                                                                     |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 8-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce673-10e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.0 MEMORY ORGANIZATION

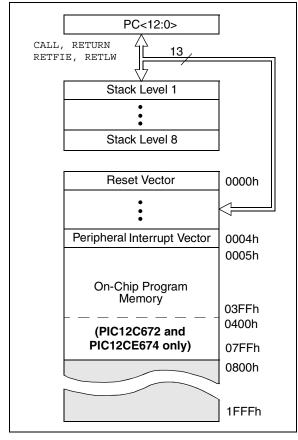

#### 4.1 Program Memory Organization

The PIC12C67X has a 13-bit program counter capable of addressing an 8K x 14 program memory space.

For the PIC12C671 and the PIC12CE673, the first 1K x 14 (0000h-03FFh) is implemented.

For the PIC12C672 and the PIC12CE674, the first 2K x 14 (0000h-07FFh) is implemented. Accessing a location above the physically implemented address will cause a wraparound. The reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 4-1: PIC12C67X PROGRAM MEMORY MAP AND STACK

#### 4.2 Data Memory Organization

The data memory is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow \text{Bank } 1$

RP0 (STATUS<5>) =  $0 \rightarrow Bank 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain Special Function Registers. Some "high use" Special Function Registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

Also note that F0h through FFh on the PIC12C67X is mapped into Bank 0 registers 70h-7Fh as common RAM.

4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register FSR (Section 4.5).

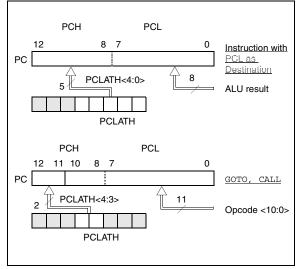

#### 4.3 PCL and PCLATH

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL Register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any reset, the PC is cleared. Figure 4-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### 4.3.1 COMPUTED GOTO

A Computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC12C67X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

#### 4.4 <u>Program Memory Paging</u>

The PIC12C67X ignores both paging bits PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC12C67X is not recommended since this may affect upward compatibility with future products.

#### 6.3 Write Operations

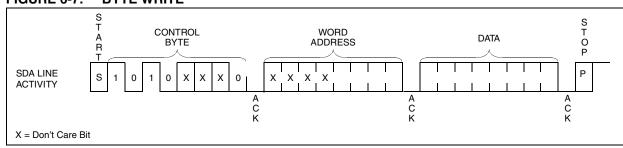

#### 6.3.1 BYTE WRITE

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the  $R/\overline{W}$  bit (which is a logic low) are placed onto the bus by the processor. This indicates to the addressed EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer. Only the lower four address bits are used by the device, and the upper four bits are don't cares. If the address byte is acknowledged, the processor will then transmit the data word to be written into the addressed memory location. The memory acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time will not generate acknowledge signals. After a byte write command, the internal address counter will not be incremented and will point to the same address location that was just written. If a stop bit sequence is transmitted to the device at any point in the write command sequence before the entire sequence is complete, then the command will abort and no data will be written. If more than 8 data bits are transmitted before the stop bit sequence is sent, then the device will clear the previously loaded byte and begin loading the data buffer again. If more than one data byte is transmitted to the device and a stop bit is sent before a full eight data bits have been transmitted, then the write command will abort and no data will be written. The EEPROM memory employs a VCC threshold detector circuit, which disables the internal erase/write logic if the Vcc is below minimum VDD. Byte write operations must be preceded and immediately followed by a bus not busy bus cycle where both SDA and SCL are held high. (See Figure 6-7 for Byte Write operation.)

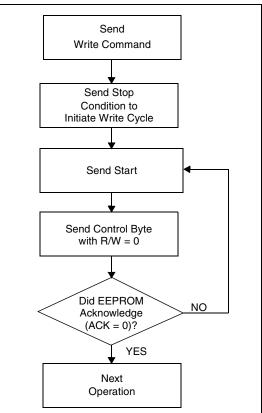

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. (See Figure 6-6 for flow diagram.)

#### FIGURE 6-6: ACKNOWLEDGE POLLING FLOW

#### FIGURE 6-7: BYTE WRITE

## **PIC12C67X**

NOTES:

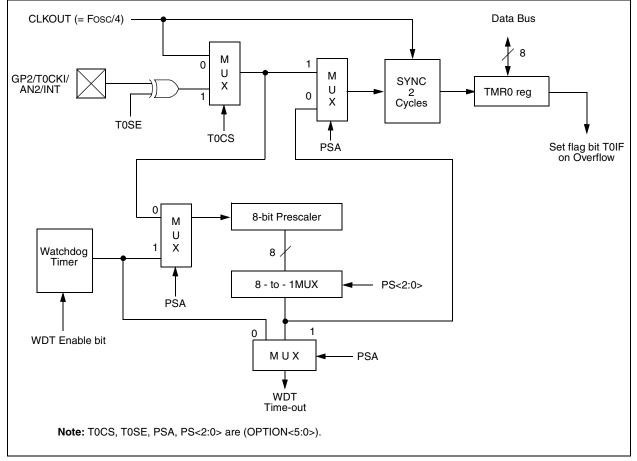

#### 7.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x..., etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

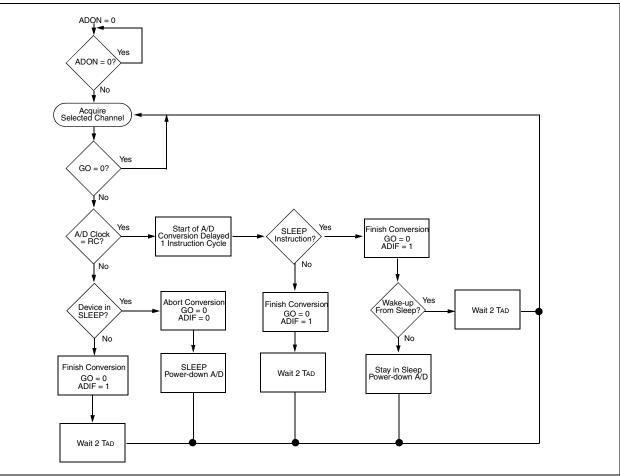

#### 8.4 <u>A/D Conversions</u>

;

;

;

Example 8-2 shows how to perform an A/D conversion. The GPIO pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled and the A/D conversion clock is FRC. The conversion is performed on the GP0 channel.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

#### EXAMPLE 8-2: DOING AN A/D CONVERSION

| BSF         | STATUS,   | RP0          | ;  | Select Page 1                                       |

|-------------|-----------|--------------|----|-----------------------------------------------------|

| CLRF        | ADCON1    |              | ;  | Configure A/D inputs                                |

| BSF         | PIE1,     | ADIE         | ;  | Enable A/D interrupts                               |

| BCF         | STATUS,   | RP0          | ;  | Select Page 0                                       |

| MOVLW       | 0xC1      |              | ;  | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF       | ADCON0    |              | ;  |                                                     |

| BCF         | PIR1,     | ADIF         | ;  | Clear A/D interrupt flag bit                        |

| BSF         | INTCON,   | PEIE         | ;  | Enable peripheral interrupts                        |

| BSF         | INTCON,   | GIE          | ;  | Enable all interrupts                               |

|             |           |              |    |                                                     |

| Ensure that | at the re | equired samp | li | ng time for the selected input channel has elapsed. |

Then the conversion may be started.

| BSF | ADCON0, GO | ; Start A/D Conversion                             |

|-----|------------|----------------------------------------------------|

| :   |            | ; The ADIF bit will be set and the GO/DONE bit     |

| :   |            | ; is cleared upon completion of the A/D Conversion |

#### TABLE 8-2: SUMMARY OF A/D REGISTERS

| Address | Name                  | Bit 7              | Bit 6              | Bit 5    | Bit 4 | Bit 3 | Bit 2   | Bit 1    | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|-----------------------|--------------------|--------------------|----------|-------|-------|---------|----------|-------|-------------------------------|---------------------------------|

| 0Bh/8Bh | INTCON <sup>(1)</sup> | GIE                | PEIE               | TOIE     | INTE  | GPIE  | T0IF    | INTF     | GPIF  | x000 000x                     | 0000 000u                       |

| 0Ch     | PIR1                  | —                  | ADIF               | _        | —     | —     | -       | —        | —     | -0                            | -0                              |

| 8Ch     | PIE1                  | —                  | ADIE               | —        | _     | _     | _       | —        | —     | -0                            | -0                              |

| 1Eh     | ADRES                 | A/D Res            | sult Regist        | er       |       |       |         |          |       | xxxx xxxx                     | uuuu uuuu                       |

| 1Fh     | ADCON0                | ADCS1              | ADCS0              | reserved | CHS1  | CHS0  | GO/DONE | reserved | ADON  | 0000 0000                     | 0000 0000                       |

| 9Fh     | ADCON1                | _                  | _                  | _        |       | -     | PCFG2   | PCFG1    | PCFG0 | 000                           | 000                             |

| 05h     | GPIO                  | SCL <sup>(2)</sup> | SDA <sup>(2)</sup> | GP5      | GP4   | GP3   | GP2     | GP1      | GP0   | 11xx xxxx                     | 11uu uuuu                       |

| 85h     | TRIS                  | _                  | _                  | TRIS5    | TRIS4 | TRIS3 | TRIS2   | TRIS1    | TRIS0 | 11 1111                       | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers can be addressed from either bank.

2: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

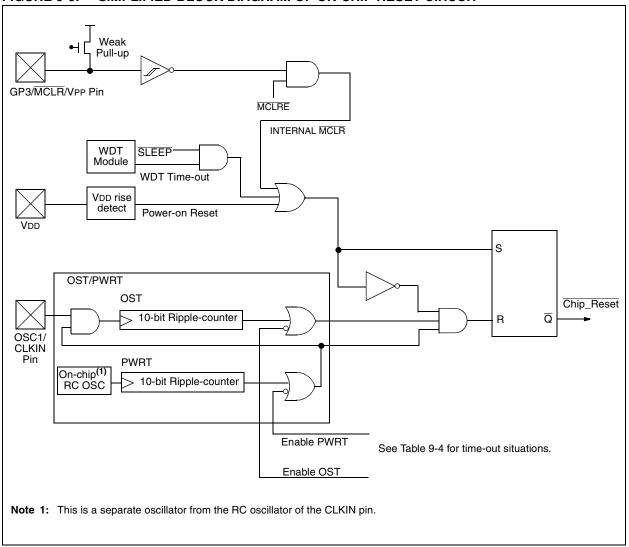

FIGURE 9-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

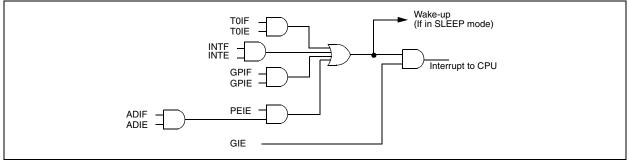

#### 9.5 Interrupts

There are four sources of interrupt:

| Interrupt Sources                                |

|--------------------------------------------------|

| TMR0 Overflow Interrupt                          |

| External Interrupt GP2/INT pin                   |

| GPIO Port Change Interrupts (pins GP0, GP1, GP3) |

| A/D Interrupt                                    |

The Interrupt Control Register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|

|       | less of the status of their corresponding       |  |  |  |  |

|       | mask bit or the GIE bit.                        |  |  |  |  |

A global interrupt enable bit, GIE (INTCON<7>), enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit. The GIE bit is cleared on reset. The "return-from-interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The GP2/INT, GPIO port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag ADIF, is contained in the Special Function Register PIR1. The corresponding interrupt enable bit is contained in Special Function Register PIE1, and the peripheral interrupt enable bit is contained in Special Function Register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid repeated interrupts.

For external interrupt events, such as GPIO change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends on when the interrupt event occurs (Figure 9-14). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

#### FIGURE 9-13: INTERRUPT LOGIC

#### 9.5.1 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 7.0). The flag bit T0IF (INTCON<2>) will be set, regardless of the state of the enable bits. If used, this flag must be cleared in software.

#### 9.5.2 INT INTERRUPT

External interrupt on GP2/INT pin is edge triggered; either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the GP2/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP mode.

#### 9.5.3 GPIO INTCON CHANGE

An input change on GP3, GP1 or GP0 sets flag bit GPIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit GPIE (INTCON<3>) (Section 5.1). This flag bit GPIF (INTCON<0>) will be set, regardless of the state of the enable bits. If used, this flag must be cleared in software.

#### 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W register and STATUS register). This will have to be implemented in software.

Example 9-1 shows the storing and restoring of the STATUS and W registers. The register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

Example 9-2 shows the saving and restoring of STA-TUS and W using RAM locations 0x70 - 0x7F. W\_TEMP is defined at 0x70 and STATUS\_TEMP is defined at 0x71.

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

- f) Returns from interrupt.

## EXAMPLE 9-1: SAVING STATUS AND W REGISTERS USING GENERAL PURPOSE RAM (0x20 - 0x6F)

|                | W_TEMP<br>STATUS,W<br>STATUS,RP0<br>STATUS_TEMP |                                                                                                                                                                      |

|----------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>SWAPF | _<br>STATUS<br>W_TEMP,F                         | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)<br>;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W<br>;Return from interrupt |

|                |                                                 |                                                                                                                                                                      |

| EXAMPLE 9-2:   | SAVING STATUS                                   | AND W REGISTERS USING SHARED RAM (0x70 - 0x7F)                                                                                                                       |

| MOVWF<br>MOVF  | W_TEMP<br>STATUS,W                              | AND W REGISTERS USING SHARED RAM (0x70 - 0x7F)<br>;Copy W to TEMP register (bank independent)<br>;Move STATUS register into W<br>;Save contents of STATUS register   |

# **PIC12C67X**

| BTFSS                                                                                                    | Bit Test f, Skip if Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [ label ] BTFSS f,b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Operands:                                                                                                | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Operation:                                                                                               | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Status Affected:                                                                                         | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Encoding:                                                                                                | 01 11bb bfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Description:                                                                                             | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a 2 cycle instruction.                                                                                                                                                                                                                                   |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Cycles:                                                                                                  | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Example                                                                                                  | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CO<br>TRUE • DE<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                          | PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                          | if FLAG<1> = 1,<br>PC = address TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CALL                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CALL<br>Syntax:                                                                                          | PC = address TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                          | PC = address TRUE Call Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Syntax:                                                                                                  | PC = address TRUE Call Subroutine [label] CALL k                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Syntax:<br>Operands:                                                                                     | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,                                                                                                                                                                                                                                                                                                                                                      |

| Syntax:<br>Operands:<br>Operation:                                                                       | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                                                             |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11><br>None                                                                                                                                                                                                                                                                                                     |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{l lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k \\ 0 \le k \le 2047 \\ (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \\ \hline None \\ \hline 10 0kkk kkk kkk \\ \hline kkkk \\ \hline Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits < 10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. \\ \hline \end{tabular}$ |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k \\ 0 \le k \le 2047 \\ (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<4:3>) \rightarrow PC<12:11> \\ \hline None \\ \hline 10 & 0kkk & kkkk & kkkk \\ \hline Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits < 10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. \\ 1 \\ \end{bmatrix}$                |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k$ $0 \le k \le 2047$ $(PC)+1 \rightarrow TOS, k \rightarrow PC < 12:11 >$ $None$ $\boxed{10  0kkk  kkkk  kkkk}$ Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits < 10:0 >. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. $1$ $2$ HERE CALL THER                                                                            |

| CLRF             | Clear f                                                                                |

|------------------|----------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                                         |

| Operands:        | $0 \leq f \leq 127$                                                                    |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                  |

| Status Affected: | Z                                                                                      |

| Encoding:        | 00 0001 1fff ffff                                                                      |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                         |

| Words:           | 1                                                                                      |

| Cycles:          | 1                                                                                      |

| Example          | CLRF FLAG_REG                                                                          |

|                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction<br>FLAG_REG = 0x00<br>Z = 1 |

| CLRW             | Clear W                                                               |                       |           |         |

|------------------|-----------------------------------------------------------------------|-----------------------|-----------|---------|

| Syntax:          | [ label ]                                                             | CLRW                  |           |         |

| Operands:        | None                                                                  |                       |           |         |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |                       |           |         |

| Status Affected: | Z                                                                     |                       |           |         |

| Encoding:        | 00                                                                    | 0001                  | 0000      | 0011    |

| Description:     | W registe is set.                                                     | r is clea             | red. Zero | bit (Z) |

| Words:           | 1                                                                     |                       |           |         |

| Cycles:          | 1                                                                     |                       |           |         |

| Example          | CLRW                                                                  |                       |           |         |

|                  | Before In                                                             | struction<br>W =      | 0x5A      |         |

|                  |                                                                       | ruction<br>W =<br>Z = | 0x00<br>1 |         |

| RETURN             | Return from Subroutine                                                                                                | RRF              | Rotate Right f through Carry                                                                                                                                                                          |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:            | [label] RETURN                                                                                                        | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                              |

| Operands:          | None                                                                                                                  | Operands:        | $0 \le f \le 127$                                                                                                                                                                                     |

| Operation:         | $TOS \rightarrow PC$                                                                                                  | •                | d ∈ [0,1]                                                                                                                                                                                             |

| Status Affected:   | None                                                                                                                  | Operation:       | See description below                                                                                                                                                                                 |

| Encoding:          | 00 0000 0000 1000                                                                                                     | Status Affected: | C                                                                                                                                                                                                     |

| Description:       | Return from subroutine. The stack                                                                                     | Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                     |

|                    | is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two cycle<br>instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg- |

| Words:             | 1                                                                                                                     |                  | ister 'f'.                                                                                                                                                                                            |

| Cycles:<br>Example | 2<br>RETURN                                                                                                           |                  | C Register f                                                                                                                                                                                          |

|                    | After Interrupt                                                                                                       | Words:           | 1                                                                                                                                                                                                     |

|                    | PC = TOS                                                                                                              | Cycles:          | 1                                                                                                                                                                                                     |

|                    |                                                                                                                       | Example          | rrf <b>REG1</b> ,<br>0                                                                                                                                                                                |

|                    |                                                                                                                       |                  | Before Instruction                                                                                                                                                                                    |

|                    |                                                                                                                       |                  | REG1 = 1110 0110<br>C = 0                                                                                                                                                                             |

|                    |                                                                                                                       |                  | After Instruction<br>REG1 = 1110 0110                                                                                                                                                                 |

|                    |                                                                                                                       |                  | W = 0111 0011                                                                                                                                                                                         |

|                    |                                                                                                                       |                  | <b>C</b> = 0                                                                                                                                                                                          |

| RLF              | Rotate Left f through Carry                                                                  | SLEEP                         |                                                                                                                                                                                                                                    |  |  |  |

|------------------|----------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                     | Syntax:                       | [ label ] SLEEP                                                                                                                                                                                                                    |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                           | Operands:                     | None                                                                                                                                                                                                                               |  |  |  |

| Operation:       | See description below                                                                        | Operation:                    | $00h \rightarrow WDT,$                                                                                                                                                                                                             |  |  |  |

| Status Affected: | С                                                                                            |                               | $0 \rightarrow \underline{WDT}$ prescaler,<br>1 $\rightarrow \underline{TO}$ ,                                                                                                                                                     |  |  |  |

| Encoding:        | 00 1101 dfff ffff                                                                            |                               | $0 \rightarrow PD$                                                                                                                                                                                                                 |  |  |  |

| Description:     | The contents of register 'f' are                                                             | Status Affected:<br>Encoding: | TO, PD                                                                                                                                                                                                                             |  |  |  |

|                  | rotated one bit to the left through the Carry Flag. If 'd' is 0, the result                  |                               | 00 0000 0110 0011                                                                                                                                                                                                                  |  |  |  |

|                  | is placed in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. | Description:                  | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |  |  |  |

| Words:           | 1                                                                                            | Words:                        | 1                                                                                                                                                                                                                                  |  |  |  |

| Cycles:          | 1                                                                                            | Cycles:                       | 1                                                                                                                                                                                                                                  |  |  |  |

| Example          | RLF REG1,0                                                                                   | Example:                      | SLEEP                                                                                                                                                                                                                              |  |  |  |

|                  | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                         |                               |                                                                                                                                                                                                                                    |  |  |  |

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

#### 11.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 11.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

## **PIC12C67X**

NOTES:

### 12.0 ELECTRICAL SPECIFICATIONS FOR PIC12C67X

#### Absolute Maximum Ratings †

| <b>3</b>                                                                                                       |                                    |

|----------------------------------------------------------------------------------------------------------------|------------------------------------|

| Ambient temperature under bias                                                                                 | 40° to +125°C                      |

| Storage temperature                                                                                            | –65°C to +150°C                    |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                   | –0.3V to (VDD + 0.3V)              |

| Voltage on VDD with respect to Vss                                                                             | 0 to +7.0V                         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                               | 700 mW                             |

| Maximum current out of Vss pin                                                                                 | 200 mA                             |

| Maximum current into VDD pin                                                                                   |                                    |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                   | ±20 mA                             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                 |                                    |

| Maximum output current sunk by any I/O pin                                                                     | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                  | 25 mA                              |

| Maximum current sunk by GPIO pins combined                                                                     | 100 mA                             |

| Maximum current sourced by GPIO pins combined                                                                  | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VO | OH) x IOH} + $\Sigma$ (VOI x IOL). |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

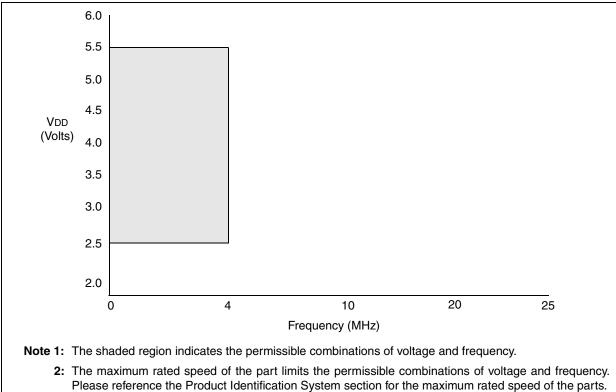

#### Standard Operating Conditions (unless otherwise specified)

#### Operating temperature

#### DC CHARACTERISTICS

$0^{\circ}C \leq TA \leq +70^{\circ}C$  (commercial)  $-40^{\circ}C \le TA \le +85^{\circ}C$  (industrial)  $-40^{\circ}C \le TA \le +125^{\circ}C$  (extended)

Operating voltage VDD range as described in DC spec Section 12.1 and Section 12.2.

| 00010112.2. |                                            |       |           |      |     |       |                                                               |

|-------------|--------------------------------------------|-------|-----------|------|-----|-------|---------------------------------------------------------------|

| Param       | Characteristic                             | Sym   | Min       | Typ† | Max | Units | Conditions                                                    |

| No.         |                                            |       |           |      |     |       |                                                               |

|             | Output High Voltage                        |       |           |      |     |       |                                                               |

| D090        | I/O ports (Note 3)                         | Voн   | Vdd - 0.7 | —    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>–40°С to +85°С                  |

| D090A       |                                            |       | Vdd - 0.7 | —    | —   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>−40°C to +125°C                 |

| D092        | OSC2/CLKOUT                                |       | Vdd - 0.7 | —    | —   | V     | ІОн = 1.3 mA, VDD = 4.5V,<br>−40°C to +85°C                   |

| D092A       |                                            |       | Vdd - 0.7 | —    | —   | V     | ІОн = 1.0 mA, VDD = 4.5V,<br>−40°C to +125°C                  |

|             | Capacitive Loading Specs on<br>Output Pins |       |           |      |     |       |                                                               |

| D100        | OSC2 pin                                   | Cosc2 | _         | —    | 15  | pF    | In XT and LP modes when external clock is used to drive OSC1. |

| D101        | All I/O pins                               | Сю    | —         | —    | 50  | pF    |                                                               |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

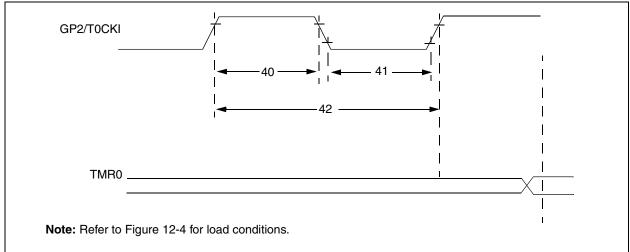

#### FIGURE 12-8: TIMER0 CLOCK TIMINGS

#### TABLE 12-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                                    |                | Min                                       | Тур† | Max       | Units | Conditions                            |

|--------------|-----------|---------------------------------------------------|----------------|-------------------------------------------|------|-----------|-------|---------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse Width                            | No Prescaler   | 0.5TCY + 20                               | —    | —         | ns    | Must also meet                        |

|              |           |                                                   | With Prescaler | 10                                        | —    | —         | ns    | parameter 42                          |

| 41*          | Tt0L      | T0CKI Low Pulse Width                             | No Prescaler   | 0.5TCY + 20                               | -    | _         | ns    | Must also meet                        |

|              |           |                                                   | With Prescaler | 10                                        | -    | _         | ns    | parameter 42                          |

| 42*          | Tt0P      | T0CKI Period                                      | No Prescaler   | TCY + 40                                  | —    | _         | ns    |                                       |

|              |           |                                                   | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | —         | ns    | N = prescale<br>value (2, 4,,<br>256) |

| 48           | TCKE2tmr1 | Delay from external clock edge to timer increment |                | 2Tosc                                     | _    | 7Tos<br>c |       |                                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 12-6: GPIO PULL-UP RESISTOR RANGES

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Max  | Units |

|-------------|------------------|------|------|------|-------|

|             |                  | GP0/ | /GP1 |      |       |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |

|             | 25               | 42K  | 48K  | 63K  | Ω     |

|             | 85               | 42K  | 49K  | 63K  | Ω     |

|             | 125              | 50K  | 55K  | 63K  | Ω     |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |

|             | 25               | 18K  | 20K  | 23K  | Ω     |

|             | 85               | 19K  | 22K  | 25K  | Ω     |

|             | 125              | 22K  | 24K  | 28K  | Ω     |

|             |                  | GI   | 23   |      |       |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |

|             | 25               | 343K | 414K | 532K | Ω     |

|             | 85               | 368K | 457K | 532K | Ω     |

|             | 125              | 431K | 504K | 593K | Ω     |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |

|             | 25               | 288K | 341K | 437K | Ω     |

|             | 85               | 306K | 371K | 448K | Ω     |

|             | 125              | 351K | 407K | 500K | Ω     |

\* These parameters are characterized but not tested.

NOTES:

| Power-down Mode (SLEEP)                        |

|------------------------------------------------|

| Prescaler, Switching Between Timer0 and WDT    |

|                                                |

| PRO MATE® II Universal Programmer              |

| Program Branches7                              |

| Program Memory                                 |

| Paging22                                       |

| Program Verification                           |

| •                                              |

| PS0 bit                                        |

| PS1 bit16                                      |

| PS2 bit                                        |

| PSA bit                                        |

| PUSH                                           |

|                                                |

| R                                              |

| RC Oscillator                                  |

|                                                |

| Read Modify Write 31                           |

| Read-Modify-Write                              |

| Register File                                  |

| Registers                                      |

| 5                                              |

| Мар                                            |

| PIC12C67X12                                    |

| Reset Conditions59                             |

| Reset                                          |

| Reset Conditions for Special Registers         |

|                                                |

| RETFIE Instruction78                           |

| RETLW Instruction78                            |

| RETURN Instruction79                           |

| RLF Instruction                                |

| RP0 bit                                        |

|                                                |

| RP1 bit                                        |

| RRF Instruction79                              |

| S                                              |

| -                                              |

| SEEVAL® Evaluation and Programming System      |

| Services                                       |

| One-Time-Programmable (OTP)5                   |

| Quick-Turnaround-Production (QTP)              |

|                                                |

| Serialized Quick-Turnaround Production (SQTP)5 |

| SFR70                                          |

| SFR As Source/Destination                      |

| SLEEP                                          |

| SLEEP Instruction                              |

|                                                |

| Software Simulator (MPLAB-SIM)                 |

| Special Features of the CPU                    |

| Special Function Register                      |

| PIC12C67X                                      |

| Special Function Registers                     |

|                                                |

| Special Function Registers, Section            |

| Stack                                          |

| Overflows                                      |

| Underflow                                      |

| STATUS Register                                |

| -                                              |

| SUBLW Instruction                              |

|                                                |

| SUBWF Instruction                              |

| T                                  |    |

|------------------------------------|----|

| TOCS bit                           | 16 |

| TAD                                | 49 |

| Timer0                             |    |

| RTCC                               | 59 |

| Timers                             |    |

| Timer0                             |    |

| Block Diagram                      | 39 |

| External Clock                     |    |

| External Clock Timing              |    |

| Increment Delay                    |    |

| Interrupt                          |    |

| Interrupt Timing                   |    |

| Prescaler                          |    |

| Prescaler Block Diagram            |    |

| Section                            |    |

| Switching Prescaler Assignment     |    |

| Synchronization                    |    |

|                                    |    |

|                                    |    |

|                                    |    |

| Timing                             |    |

| TMR0 Interrupt                     | 54 |

| Timing Diagrams                    | ~~ |

| A/D Conversion                     |    |

| CLKOUT and I/O 10                  |    |

| External Clock Timing 10           |    |

| Time-out Sequence                  |    |

| Timer0                             |    |

| Timer0 Interrupt Timing            |    |

| Timer0 with External Clock         |    |

| Wake-up from Sleep via Interrupt   |    |

| TO bit                             |    |

| TOSE bit                           |    |

| TRIS Instruction                   |    |

| TRIS Register 14, 25, 3            |    |

| Two's Complement                   | 7  |

| U                                  |    |

| UV Erasable Devices                | 5  |

|                                    | 5  |

| W                                  |    |

| W Register                         |    |

| ALU                                | 7  |

| Wake-up from SLEEP                 | 66 |

| Watchdog Timer (WDT) 53, 56, 59, 6 | 65 |

| WDT                                | 59 |

| Block Diagram                      | 65 |

| Period                             |    |

| Programming Considerations         |    |

| Timeout                            |    |

| WWW, On-Line Support               |    |

|                                    | -  |

| X                                  |    |

| XORLW Instruction                  |    |

| XORWF Instruction                  | 31 |

| Z                                  |    |

| Z bit                              | 15 |

| Zero bit                           | -  |

|                                    | '  |