Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | 16 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 8-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce674-04i-p |

TABLE 3-1: PIC12C67X PINOUT DESCRIPTION

| Name                | DIP Pin # | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|-----------|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/AN0             | 7         | I/O           | TTL/ST         | Bi-directional I/O port/serial programming data/analog input 0. Can be software programmed for internal weak pull-up and interrupt-on-pin change. This buffer is a Schmitt Trigger input when used in serial programming mode.                                                                                                                                                                     |

| GP1/AN1/VREF        | 6         | I/O           | TTL/ST         | Bi-directional I/O port/serial programming clock/analog input 1/voltage reference. Can be software programmed for internal weak pull-up and interrupt-on-pin change. This buffer is a Schmitt Trigger input when used in serial programming mode.                                                                                                                                                  |

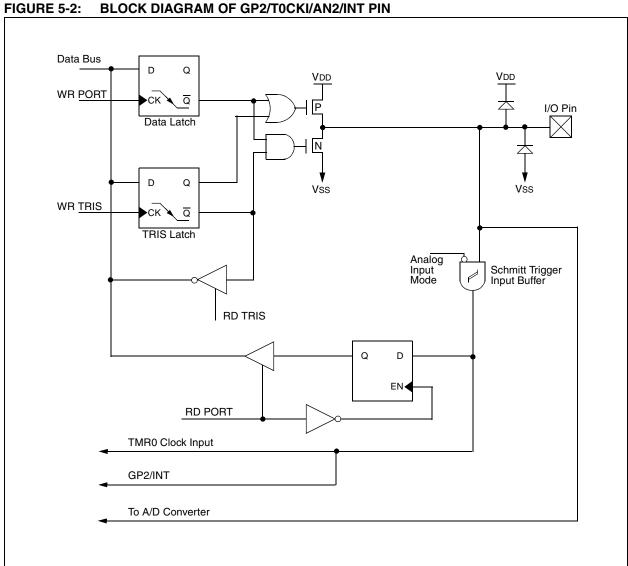

| GP2/T0CKI/AN2/INT   | 5         | 1/0           | ST             | Bi-directional I/O port/analog input 2. Can be configured as TOCKI or external interrupt.                                                                                                                                                                                                                                                                                                          |

| GP3/MCLR/VPP        | 4         | I             | TTL/ST         | Input port/master clear (reset) input/programming voltage input. When configured as MCLR, this pin is an active low reset to the device. Voltage on MCLR/VPP must not exceed VDD during normal device operation. Can be software programmed for internal weak pull-up and interrupt-on-pin change. Weak pull-up always on if configured as MCLR. This buffer is Schmitt Trigger when in MCLR mode. |

| GP4/OSC2/AN3/CLKOUT | 3         | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output/analog input 3. Connections to crystal or resonator in crystal oscillator mode (HS, XT and LP modes only, GPIO in other modes). In EXTRC and INTRC modes, the pin output can be configured to CLK-OUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                               |

| GP5/OSC1/CLKIN      | 2         | I/O           | TTL/ST         | Bi-directional IO port/oscillator crystal input/external clock<br>source input (GPIO in INTRC mode only, OSC1 in all other<br>oscillator modes). Schmitt trigger input for EXTRC oscillator<br>mode.                                                                                                                                                                                               |

| VDD                 | 1         | Р             | _              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                            |

| Vss                 | 8         | Р             | _              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                                                           |

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input.

## 4.0 MEMORY ORGANIZATION

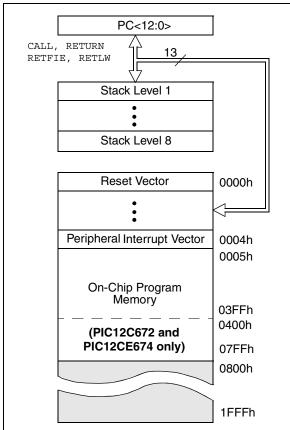

### 4.1 Program Memory Organization

The PIC12C67X has a 13-bit program counter capable of addressing an 8K x 14 program memory space.

For the PIC12C671 and the PIC12CE673, the first 1K x 14 (0000h-03FFh) is implemented.

For the PIC12C672 and the PIC12CE674, the first  $2K \times 14$  (0000h-07FFh) is implemented. Accessing a location above the physically implemented address will cause a wraparound. The reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 4-1: PIC12C67X PROGRAM

MEMORY MAP AND STACK

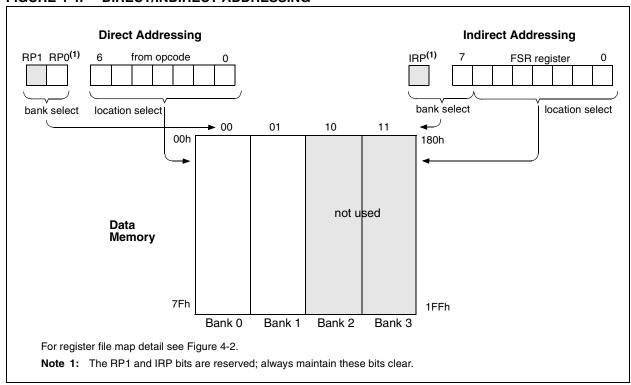

### 4.2 <u>Data Memory Organization</u>

The data memory is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow Bank 1$

RP0 (STATUS<5>) =  $0 \rightarrow Bank 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain Special Function Registers. Some "high use" Special Function Registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

Also note that F0h through FFh on the PIC12C67X is mapped into Bank 0 registers 70h-7Fh as common RAM.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register FSR (Section 4.5).

TABLE 4-1: PIC12C67X SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name   | Bit 7              | Bit 6              | Bit 5         | Bit 4        | Bit 3        | Bit 2           | Bit 1        | Bit 0       | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets <sup>(3)</sup> |

|----------------------|--------|--------------------|--------------------|---------------|--------------|--------------|-----------------|--------------|-------------|-------------------------------|------------------------------------------------|

| Bank 0               |        |                    |                    |               |              |              |                 |              |             |                               |                                                |

| 00h <sup>(1)</sup>   | INDF   | Addressing         | this location      | uses conten   | ts of FSR to | address dat  | a memory (n     | ot a physica | l register) | 0000 0000                     | 0000 0000                                      |

| 01h                  | TMR0   | Timer0 mod         | lule's registe     | r             |              |              |                 |              |             | xxxx xxxx                     | uuuu uuuu                                      |

| 02h <sup>(1)</sup>   | PCL    | Program Co         | ounter's (PC)      | Least Signif  | ficant Byte  |              |                 |              |             | 0000 0000                     | 0000 0000                                      |

| 03h <sup>(1)</sup>   | STATUS | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO           | PD           | Z               | DC           | С           | 0001 1xxx                     | 000q quuu                                      |

| 04h <sup>(1)</sup>   | FSR    | Indirect data      | a memory ac        | ddress pointe | er           |              |                 |              |             | xxxx xxxx                     | uuuu uuuu                                      |

| 05h                  | GPIO   | SCL <sup>(5)</sup> | SDA <sup>(5)</sup> | GP5           | GP4          | GP3          | GP2             | GP1          | GP0         | 11xx xxxx                     | 11uu uuuu                                      |

| 06h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 07h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 08h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 09h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 0Ah <sup>(1,2)</sup> | PCLATH | _                  | _                  | _             | Write Buffer | for the uppe | er 5 bits of th | e Program C  | Counter     | 0 0000                        | 0 0000                                         |

| 0Bh <sup>(1)</sup>   | INTCON | GIE                | PEIE               | TOIE          | INTE         | GPIE         | TOIF            | INTF         | GPIF        | 0000 000x                     | 0000 000u                                      |

| 0Ch                  | PIR1   | _                  | ADIF               | _             | _            | _            | _               | _            | _           | -0                            | -0                                             |

| 0Dh                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 0Eh                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 0Fh                  | _      | Unimpleme          | Jnimplemented      |               |              |              |                 |              |             |                               | _                                              |

| 10h                  | _      | Unimpleme          | Unimplemented      |               |              |              |                 |              |             |                               | _                                              |

| 11h                  | _      | Unimpleme          | Unimplemented      |               |              |              |                 |              |             |                               | _                                              |

| 12h                  | _      | Unimpleme          | Unimplemented      |               |              |              |                 |              |             |                               | _                                              |

| 13h                  | _      | Unimpleme          | Unimplemented      |               |              |              |                 |              |             |                               | _                                              |

| 14h                  | _      | Unimpleme          | Unimplemented      |               |              |              |                 |              |             |                               | _                                              |

| 15h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 16h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 17h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 18h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 19h                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 1Ah                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 1Bh                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 1Ch                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 1Dh                  | _      | Unimpleme          | nted               |               |              |              |                 |              |             | _                             | _                                              |

| 1Eh                  | ADRES  | A/D Result I       | Register           |               |              |              |                 |              |             | xxxx xxxx                     | uuuu uuuu                                      |

| 1Fh                  | ADCON0 | ADCS1              | ADCS0              | reserved      | CHS1         | CHS0         | GO/DONE         | reserved     | ADON        | 0000 0000                     | 0000 0000                                      |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved on the PIC12C67X; always maintain these bits clear.

- 5: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

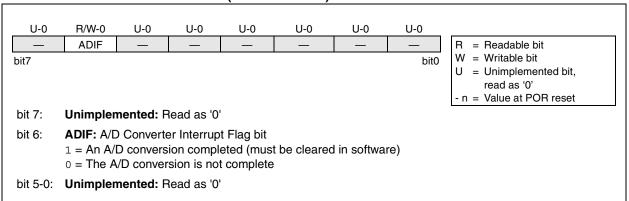

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the Peripheral interrupts.

Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0Ch)

Note:

### 4.2.2.7 OSCCAL REGISTER

The Oscillator Calibration (OSCCAL) Register is used to calibrate the internal 4 MHz oscillator. It contains four bits for fine calibration and two other bits to either increase or decrease frequency.

# REGISTER 4-7: OSCCAL REGISTER (ADDRESS 8Fh)

R/W-0 R/W-1 R/W-1 R/W-1 R/W-0 R/W-0 U-0 U-0 CAL3 CAL2 CAL1 CAL0 CALFST CALSLW R = Readable bit W = Writable bit bit7 bit0 = Unimplemented bit, read as '0' n = Value at POR reset bit 7-4: CAL<3:0>: Fine Calibration bit 3: **CALFST:** Calibration Fast 1 = Increase frequency 0 = No change bit 2: **CALSLW:** Calibration Slow 1 = Decrease frequency 0 = No change bit 1-0: Unimplemented: Read as '0' Note: If CALFST = 1 and CALSLW = 1, CALFST has precedence.

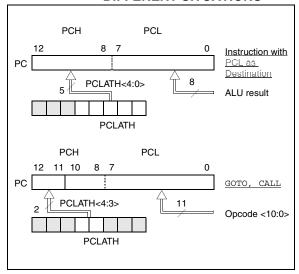

#### 4.3 PCL and PCLATH

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL Register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any reset, the PC is cleared. Figure 4-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-3: LOADING OF PC IN DIFFERENT SITUATIONS

### 4.3.1 COMPUTED GOTO

A Computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC12C67X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

## 4.4 **Program Memory Paging**

The PIC12C67X ignores both paging bits PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC12C67X is not recommended since this may affect upward compatibility with future products.

# 4.5 <u>Indirect Addressing, INDF and FSR</u> <u>Registers</u>

The INDF Register is not a physical register. Addressing the INDF Register will cause indirect addressing.

Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF Register itself indirectly (FSR = '0') will read 00h. Writing to the INDF Register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR Register and the IRP bit (STATUS<7>), as shown in Figure 4-4. However, IRP is not used in the PIC12C67X.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-1.

#### **EXAMPLE 4-1: INDIRECT ADDRESSING**

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ;to RAM              |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR,F | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ; yes continue       |

FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

FIGURE 5-2:

**NOTES:**

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)

BCF STATUS, RPO ;Bank 0

CLRF TMR0 ;Clear TMR0 & Prescaler

BSF STATUS, RPO ;Bank 1 CLRWDT ;Clears

CLRWDT ;Clears WDT

MOVLW b'xxxx1xxx' ;Select new prescale

MOVWF OPTION\_REG ;value & WDT

BCF STATUS, RPO ; Bank 0

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

# EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

CLRWDT ;Clear WDT and

;prescaler

BSF STATUS, RPO; Bank 1

MOVLW b'xxxx0xxx'; Select TMR0, new

;prescale value and

MOVWF OPTION\_REG ; clock source BCF STATUS, RPO ; Bank 0

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMERO

| Address | Name   | Bit 7  | Bit 6       | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|--------|-------------|---------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 | module's re | egister |       |       |       |       |       | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE        | TOIE    | INTE  | GPIE  | TOIF  | INTF  | GPIF  | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | GPPU   | INTEDG      | TOCS    | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111       | 1111 1111                       |

| 85h     | TRIS   | _      | _           | TRIS5   | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0 | 11 1111         | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

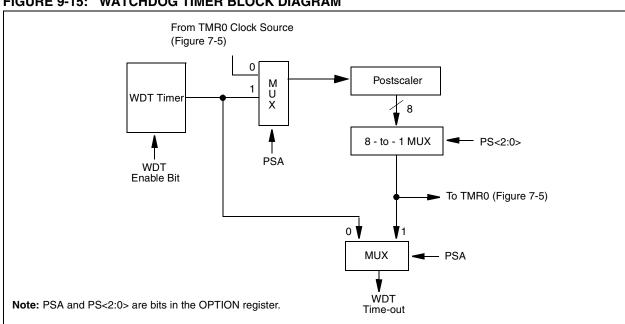

#### 9.7 **Watchdog Timer (WDT)**

The Watchdog Timer is a free running, on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 9.1).

#### 9.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out early and generating a premature device RESET condition.

The  $\overline{10}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 9.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

Note: When the prescaler is assigned to the WDT, always execute a CLRWDT instruction before changing the prescale value, otherwise a WDT reset may occur.

See Example 7-1 and Example 7-2 for changing prescaler between WDT and Timer0.

**TABLE 9-8:** SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name                        | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------------------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits <sup>(1)</sup> | MCLRE | CP1    | CP0   | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 |

| 81h     | OPTION                      | GPPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 9-1 for operation of these bits. Not all CP0 and CP1 bits are shown.

| BCF              | Bit Clear                                                          | · f        |                        |      |  |  |

|------------------|--------------------------------------------------------------------|------------|------------------------|------|--|--|

| Syntax:          | [ label ] B                                                        | BCF f,b    | )                      |      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$ | 27         |                        |      |  |  |

| Operation:       | $0 \rightarrow (f < b)$                                            | >)         |                        |      |  |  |

| Status Affected: | None                                                               |            |                        |      |  |  |

| Encoding:        | 01                                                                 | 00bb       | bfff                   | ffff |  |  |

| Description:     | Bit 'b' in r                                                       | egister 'f | ' is cleare            | ed.  |  |  |

| Words:           | 1                                                                  |            |                        |      |  |  |

| Cycles:          | 1                                                                  |            |                        |      |  |  |

| Example          | BCF                                                                | FLAG_      | REG, 7                 |      |  |  |

|                  | After Inst                                                         | FLAG_RE    | EG = 0xC7<br>EG = 0x47 |      |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                    |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                                   |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                      |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is skipped. If bit 'b' is '0', then the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead, making this a 2 cycle instruction. |

| Words:           | 1                                                                                                                                                                                                                                                      |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                   |

| Example          | HERE BTFSC FLAG,1 FALSE GOTO PROCESS_CO TRUE • DE                                                                                                                                                                                                      |

|                  | Before Instruction PC = address HERE                                                                                                                                                                                                                   |

|                  | After Instruction if FLAG<1> = 0, PC = address TRUE if FLAG<1>=1, PC = address FALSE                                                                                                                                                                   |

| BSF              | Bit Set f                                                          |            |                   |      |

|------------------|--------------------------------------------------------------------|------------|-------------------|------|

| Syntax:          | [ label ] B                                                        | SF f,b     |                   |      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$ | 27         |                   |      |

| Operation:       | $1 \rightarrow (f < b)$                                            | >)         |                   |      |

| Status Affected: | None                                                               |            |                   |      |

| Encoding:        | 01                                                                 | 01bb       | bfff              | ffff |

| Description:     | Bit 'b' in r                                                       | egister 'f | ' is set.         |      |

| Words:           | 1                                                                  |            |                   |      |

| Cycles:          | 1                                                                  |            |                   |      |

| Example          | BSF                                                                | FLAG_F     | REG, 7            |      |

|                  | Before In<br>After Inst                                            | FLAG_RE    | EG = 0x0 <i>A</i> | A.   |

$FLAG_REG = 0x8A$

| SUBLW               | Subtract W from Literal                                                                    | SUBWF                | Subtract W from f                                                                                                                                                    |

|---------------------|--------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ label ] SUBLW k                                                                          | Syntax:              | [ label ] SUBWF f,d                                                                                                                                                  |

| Operands:           | $0 \leq k \leq 255$                                                                        | Operands:            | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                   |

| Operation:          | $k - (W) \rightarrow (W)$                                                                  | 0                    |                                                                                                                                                                      |

| Status<br>Affected: | C, DC, Z                                                                                   | Operation:<br>Status | (f) - (W) $\rightarrow$ (dest)<br>C, DC, Z                                                                                                                           |

| Encoding:           | 11 110x kkkk kkkk                                                                          | Affected:            | 0, 50, 2                                                                                                                                                             |

| Description:        | The W register is subtracted (2's                                                          | Encoding:            | 00 0010 dfff ffff                                                                                                                                                    |

| ·                   | complement method) from the eight bit literal 'k'. The result is placed in the W register. | Description:         | Subtract (2's complement method) W register from register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in regis- |

| Words:              | 1                                                                                          |                      | ter 'f'.                                                                                                                                                             |

| Cycles:             | 1                                                                                          | Words:               | 1                                                                                                                                                                    |

| Example 1:          | SUBLW 0x02                                                                                 | Cycles:              | 1                                                                                                                                                                    |

|                     | Before Instruction                                                                         | Example 1:           | SUBWF REG1,1                                                                                                                                                         |

|                     | W = 1<br>C = ?                                                                             |                      | Before Instruction                                                                                                                                                   |

|                     | After Instruction                                                                          |                      | REG1 = 3                                                                                                                                                             |

|                     | W = 1                                                                                      |                      | W = 2<br>C = ?                                                                                                                                                       |

|                     | C = 1; result is positive                                                                  |                      | After Instruction                                                                                                                                                    |

| Example 2:          | Before Instruction                                                                         |                      | REG1 = 1                                                                                                                                                             |

|                     | W = 2                                                                                      |                      | W = 2<br>C = 1: result is positive                                                                                                                                   |

|                     | C = ? After Instruction                                                                    | Example 2:           | C = 1; result is positive  Before Instruction                                                                                                                        |

|                     |                                                                                            | Example 2.           | REG1 = 2                                                                                                                                                             |

|                     | W = 0<br>C = 1; result is zero                                                             |                      | W = 2                                                                                                                                                                |

| Example 3:          | Before Instruction                                                                         |                      | C = ?                                                                                                                                                                |

| ·                   | W = 3                                                                                      |                      | After Instruction                                                                                                                                                    |

|                     | C = ?                                                                                      |                      | REG1 = 0<br>W = 2                                                                                                                                                    |

|                     | After Instruction                                                                          |                      | C = 1; result is zero                                                                                                                                                |

|                     | W = 0xFF<br>C = 0; result is nega-                                                         | Example 3:           | Before Instruction                                                                                                                                                   |

|                     | tive                                                                                       |                      | REG1 = 1                                                                                                                                                             |

|                     |                                                                                            |                      | W = 2<br>C = ?                                                                                                                                                       |

|                     |                                                                                            |                      | After Instruction                                                                                                                                                    |

|                     |                                                                                            |                      | REG1 = 0xFF                                                                                                                                                          |

|                     |                                                                                            |                      | W = 2                                                                                                                                                                |

|                     |                                                                                            |                      | C = 0; result is negative                                                                                                                                            |

**NOTES:**

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 11.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials™ and secure serials. The Total Endurance™ Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

# 11.18 <u>KEELog Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

**TABLE 11-1: DEVELOPMENT TOOLS FROM MICROCHIP**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                  | PIC12CXXX  | PIC14000 | PIC16C5X | PIC16C6X | PIC16CXXX | PIC16F62X | PIC16C7X | PIC16C7XX | PIC16C8X | PIC16F8XX | PIC16C9XX   | PIC17C4X | PIC17C7XX | PIC18CXX2 | 93CXX<br>54CXX/ | нсеххх | WCBFXXX | WCP2510 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------|----------|----------|----------|-----------|-----------|----------|-----------|----------|-----------|-------------|----------|-----------|-----------|-----------------|--------|---------|---------|

| WPLAB® CRT Compiler         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  | ^          | >        | >        | >        | >         | >         | >        | >         | >        | >         | >           | >        | >         | >         |                 |        |         |         |

| MPARB* CIS Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                  |            |          |          |          |           |           |          |           |          |           |             | >        | >         |           |                 |        |         |         |

| MPASAMMELINK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |            |          |          |          |           |           |          |           |          |           |             |          |           | >         |                 |        |         |         |

| MPLAB <sup>®</sup> -LOCE   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  | >          | >        | >        | >        | >         | >         | >        | >         | >        | >         | >           | >        | >         | >         | >               | >      |         |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                  | >          | ^        | ^        | >        | >         | **^       | `        | >         | >        | >         | <b>&gt;</b> | ^        | >         | >         |                 |        |         |         |

| CEPIC*** Low-Cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                  | >          | ^        | ^        | >        | ^         |           | `        | ^         | ^        |           | <b>/</b>    | ^        | `         |           |                 |        |         |         |

| Hable B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  | >          |          | >        | >        | >         |           | >        | >         | >        |           | `           |          |           |           |                 |        |         |         |

| PICSTART® Plus         Cow-Cost Universal Dev. Kit         Cow-Cost Universal Dev. Kit         Compared to the control of |                                                  |            |          |          | *        |           |           | *>       |           |          | >         |             |          |           |           |                 |        |         |         |

| PRO MATE® III         Universal Programmer         """         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """"         """""         """"         """"         """""                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  | >          | >        | >        | >        | >         | ** >      | >        | >         | >        | >         | >           | >        | >         | >         |                 |        |         |         |

| SIMICE         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V <th></th> <td>&gt;</td> <td>&gt;</td> <td>&gt;</td> <td>&gt;</td> <td>&gt;</td> <td>**</td> <td>&gt;</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                  | >          | >        | >        | >        | >         | **        | >        | >         | >        | >         | >           | >        | >         | >         | >               | >      |         |         |

| PICDEM-1         V         V†         V†         V         P         V         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P         P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SIMICE                                           | >          |          | >        |          |           |           |          |           |          |           |             |          |           |           |                 |        |         |         |

| PICDEM-3         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T         T<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PICDEM-1                                         |            |          | >        |          | >         |           | +        |           | >        |           |             | >        |           |           |                 |        |         |         |

| PICDEM-13         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PICDEM-2                                         |            |          |          | <b>†</b> |           |           |          |           |          |           |             |          |           | >         |                 |        |         |         |