Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | 16 x 8                                                                    |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce674-10-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | General Description                              |

|-------|--------------------------------------------------|

| 2.0   | PIC12C67X Device Varieties                       |

| 3.0   | Architectural Overview                           |

|       | Memory Organization                              |

| 5.0   | I/O Port                                         |

| 6.0   | EEPROM Peripheral Operation                      |

| 7.0   | Timer0 Module                                    |

| 8.0   | Analog-to-Digital Converter (A/D) Module         |

| 9.0   | Special Features of the CPU                      |

|       | Instruction Set Summary                          |

| 11.0  | Development Support                              |

| 12.0  | Electrical Specifications                        |

| 13.0  | DC and AC Characteristics                        |

| 14.0  | Packaging Information 115                        |

| Appe  | ndix A:Compatibility                             |

| Appe  | ndix B:Code for Accessing EEPROM Data Memory 119 |

| Index |                                                  |

| On-Li | ne Support                                       |

| Read  | ne Support                                       |

| PIC12 | 2C67X Product Identification System              |

### To Our Valued Customers

### **Most Current Data Sheet**

To automatically obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

### 4.2.2.1 STATUS REGISTER

The STATUS Register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS Register, because these instructions do not affect the Z, C or DC bits from the STATUS Register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: Bits IRP and RP1 (STATUS<7:6>) are not used by the PIC12C67X and should be maintained clear. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

|             | Reserved                                                                                                                                                                                                                                                                                    | R/W-0 | R-1        | R-1 | R/W-x | R/W-x | R/W-x     |                                                                                                           |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-----|-------|-------|-----------|-----------------------------------------------------------------------------------------------------------|--|--|

| IRP<br>bit7 | RP1                                                                                                                                                                                                                                                                                         | RP0   | TO         | PD  | Z     | DC    | C<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7:      | IRP: Register Bank Select bit (used for indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)<br>The IRP bit is reserved; always maintain this bit clear.                                                                                                        |       |            |     |       |       |           |                                                                                                           |  |  |

| bit 6-5:    | <pre>: RP&lt;1:0&gt;: Register Bank Select bits (used for direct addressing)<br/>11 = Bank 3 (180h - 1FFh)<br/>10 = Bank 2 (100h - 17Fh)<br/>01 = Bank 1 (80h - FFh)<br/>00 = Bank 0 (00h - 7Fh)<br/>Each bank is 128 bytes. The RP1 bit is reserved; always maintain this bit clear.</pre> |       |            |     |       |       |           |                                                                                                           |  |  |

| bit 4:      | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                                             |       |            |     |       |       |           |                                                                                                           |  |  |

| bit 3:      | <b>PD:</b> Power-down bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                                   |       |            |     |       |       |           |                                                                                                           |  |  |

| bit 2:      | <b>Z</b> : Zero bit<br>1 = The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not zero                                                                                                                                         |       |            |     |       |       |           |                                                                                                           |  |  |

| bit 1:      | <b>DC:</b> Digit Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result                                         |       |            |     |       |       |           |                                                                                                           |  |  |

| bit 0:      | <b>C:</b> Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)<br>1 = A carry-out from the most significant bit of the result occurred<br>0 = No carry-out from the most significant bit of the result occurred                                                                       |       |            |     |       |       |           |                                                                                                           |  |  |

| Note:       | ond ope                                                                                                                                                                                                                                                                                     |       | rotate (RR |     |       |       |           | the two's complement of the sec-<br>either the high or low order bit of                                   |  |  |

### **REGISTER 4-1:** STATUS REGISTER (ADDRESS 03h, 83h)

### 4.3 PCL and PCLATH

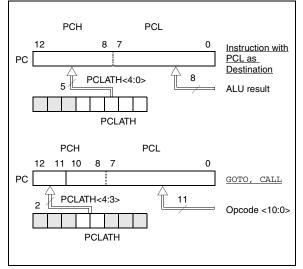

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL Register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any reset, the PC is cleared. Figure 4-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

### 4.3.1 COMPUTED GOTO

A Computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

### 4.3.2 STACK

The PIC12C67X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

### 4.4 <u>Program Memory Paging</u>

The PIC12C67X ignores both paging bits PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC12C67X is not recommended since this may affect upward compatibility with future products.

NOTES:

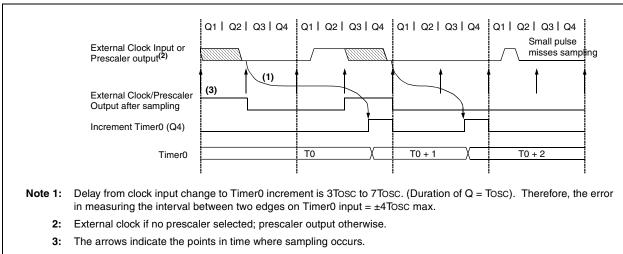

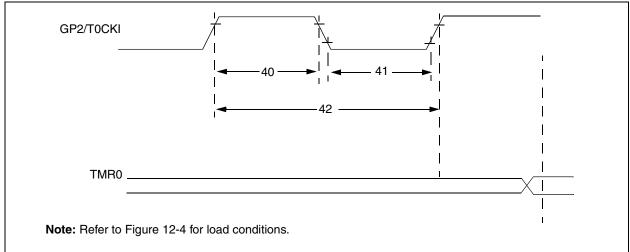

### 7.2 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is used as the clock source. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for TOCKI to be high for at least 2TOSC (and a small RC delay of 20 ns) and low for at least 2TOSC (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type pres-

caler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, (i.e., it can be changed "on-the-fly" during program execution).

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2.

# EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

### TABLE 7-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|--------|--------------------------|-------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 | Timer0 module's register |       |       |       |       |       |       | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE                     | TOIE  | INTE  | GPIE  | TOIF  | INTF  | GPIF  | 0000 000x       | 0000 000u                       |

| 81h     | OPTION | GPPU   | INTEDG                   | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111       | 1111 1111                       |

| 85h     | TRIS   | _      |                          | TRIS5 | TRIS4 | TRIS3 | TRIS2 | TRIS1 | TRIS0 | 11 1111         | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

NOTES:

# 8.5 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS<1:0> = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared, and the result loaded into the ADRES Register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS<1:0> = 11). To perform an A/D conversion in SLEEP, the GO/DONE bit must be set, followed by the SLEEP instruction.

### 8.6 <u>A/D Accuracy/Error</u>

The overall accuracy of the A/D is less than  $\pm$  1 LSb for VDD = 5V  $\pm$  10% and the analog VREF = VDD. This overall accuracy includes offset error, full scale error, and integral error. The A/D converter is monotonic over the full VDD range. The resolution and accuracy may be less when either the analog reference (VDD) is less than 5.0V or when the analog reference (VREF) is less than VDD.

The maximum pin leakage current is specified in the Device Data Sheet electrical specification, parameter #D060.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from Tosc, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

### 8.7 Effects of a Reset

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted. The value that is in the ADRES register is not modified for a Reset. The ADRES register will contain unknown data after a Power-on Reset.

### 8.8 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

| Note: | For the PIC12C67X, care must be taken       |

|-------|---------------------------------------------|

|       | when using the GP4 pin in A/D conver-       |

|       | sions due to its proximity to the OSC1 pin. |

An external RC filter is sometimes added for antialiasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

### 8.9 <u>Transfer Function</u>

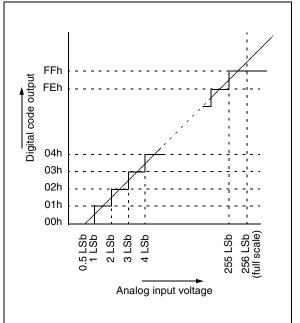

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is 1 LSb (or Analog VREF / 256) (Figure 8-3).

### FIGURE 8-3: A/D TRANSFER FUNCTION

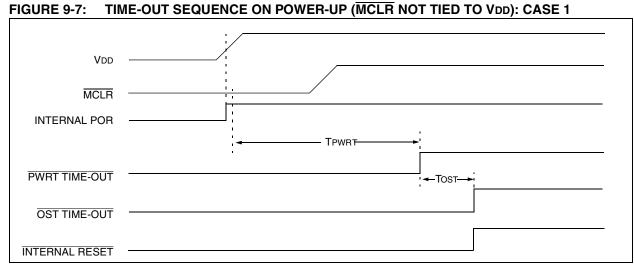

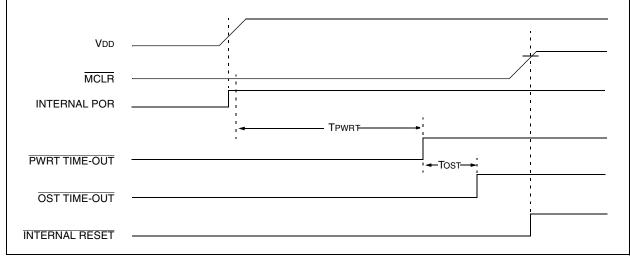

### FIGURE 9-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

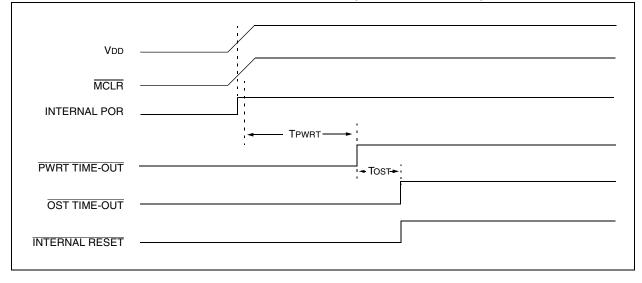

### FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

| NOP              | No Operation   |     |  |  |  |  |  |

|------------------|----------------|-----|--|--|--|--|--|

| Syntax:          | [ label ]      | NOP |  |  |  |  |  |

| Operands:        | None           |     |  |  |  |  |  |

| Operation:       | No operation   |     |  |  |  |  |  |

| Status Affected: | None           |     |  |  |  |  |  |

| Encoding:        | 0000 0xx0 0000 |     |  |  |  |  |  |

| Description:     | No operation.  |     |  |  |  |  |  |

| Words:           | 1              |     |  |  |  |  |  |

| Cycles:          | 1              |     |  |  |  |  |  |

| Example          | NOP            |     |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] RETFIE                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{TOS} \rightarrow \text{PC}, \\ 1 \rightarrow \text{GIE} \end{array}$                                                                                                                           |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global Inter-<br>rupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                 |  |  |  |  |  |  |  |

| OPTION           | Load Option Register                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] OPTION                                                                                                                                                                                                                                   |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                               |  |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                               |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                                                                                  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a read-<br>able/writable register, the user can<br>directly address it. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Example          |                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC12C67X products,<br>do not use this instruction.                                                                                                                                                |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two cycle instruction. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                   |

| Example          | CALL TABLE;W contains table                                                                                                                                                         |

| TABLE            | ;offset value<br>;W now has table value                                                                                                                                             |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |

|                  | RETLW kn ; End of table                                                                                                                                                             |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                      |

|                  | After Instruction<br>W = value of k8                                                                                                                                                |

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

# 11.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

### 11.6 <u>MPLAB-ICE High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PIC microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PIC MCU.

# 11.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PIC microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

# 11.8 <u>ICEPIC</u>

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

### 11.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

# 11.10 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In

NOTES:

| DC CH4      | ARACTERISTICS                                                                         |                                                                          | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C &\leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |  |                         |            |                                      |  |

|-------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------|------------|--------------------------------------|--|

| Parm<br>No. | Characteristic                                                                        | Characteristic Sym Min <sub>Typ<sup>(1)</sup></sub> Max Units Conditions |                                                                                                                                                                                                                                                                                                                                 |  |                         |            |                                      |  |

|             | LP Oscillator Operating<br>Frequency<br>INTRC/EXTRC Oscillator<br>Operating Frequency | Fosc                                                                     | 0                                                                                                                                                                                                                                                                                                                               |  | 200<br>4 <sup>(6)</sup> | kHz<br>MHz | All temperatures<br>All temperatures |  |

|             | XT Oscillator Operating<br>Frequency                                                  |                                                                          | 0                                                                                                                                                                                                                                                                                                                               |  | 4                       | MHz        | All temperatures                     |  |

|             | HS Oscillator Operating<br>Frequency                                                  |                                                                          | 0                                                                                                                                                                                                                                                                                                                               |  | 10                      | MHz        | All temperatures                     |  |

I hese parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD,

$\overline{MCLR} = VDD; WDT$  disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

### Standard Operating Conditions (unless otherwise specified)

### Operating temperature

### DC CHARACTERISTICS

$0^{\circ}C \leq TA \leq +70^{\circ}C$  (commercial)  $-40^{\circ}C \le TA \le +85^{\circ}C$  (industrial)  $-40^{\circ}C \le TA \le +125^{\circ}C$  (extended)

Operating voltage VDD range as described in DC spec Section 12.1 and Section 12.2.

| Param | Characteristic                             | Sym   | Min       | Typ† | Max | Units | Conditions                                                    |  |  |  |  |

|-------|--------------------------------------------|-------|-----------|------|-----|-------|---------------------------------------------------------------|--|--|--|--|

| No.   |                                            |       |           |      |     |       |                                                               |  |  |  |  |

|       | Output High Voltage                        |       |           |      |     |       |                                                               |  |  |  |  |

| D090  | I/O ports (Note 3)                         | Voн   | Vdd - 0.7 | —    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>–40°С to +85°С                  |  |  |  |  |

| D090A |                                            |       | Vdd - 0.7 | —    | —   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>−40°C to +125°C                 |  |  |  |  |

| D092  | OSC2/CLKOUT                                |       | Vdd - 0.7 | —    | —   | V     | ІОн = 1.3 mA, VDD = 4.5V,<br>−40°C to +85°C                   |  |  |  |  |

| D092A |                                            |       | Vdd - 0.7 | —    | —   | V     | ІОн = 1.0 mA, VDD = 4.5V,<br>−40°C to +125°C                  |  |  |  |  |

|       | Capacitive Loading Specs on<br>Output Pins |       |           |      |     |       |                                                               |  |  |  |  |

| D100  | OSC2 pin                                   | Cosc2 | _         | —    | 15  | pF    | In XT and LP modes when external clock is used to drive OSC1. |  |  |  |  |

| D101  | All I/O pins                               | Сю    | —         | —    | 50  | pF    |                                                               |  |  |  |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not † tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

|        |                             | Standard  | ndard Operating Conditions (unless otherwise specified)                 |      |     |       |                                                                     |  |  |  |  |

|--------|-----------------------------|-----------|-------------------------------------------------------------------------|------|-----|-------|---------------------------------------------------------------------|--|--|--|--|

|        |                             | Operating | Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) |      |     |       |                                                                     |  |  |  |  |

| DC CHA | RACTERISTICS                |           | $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)                     |      |     |       |                                                                     |  |  |  |  |

|        |                             | Operating | Operating voltage VDD range as described in DC spec Section 12.1 and    |      |     |       |                                                                     |  |  |  |  |

|        |                             | Section 1 | 2.2.                                                                    |      |     |       |                                                                     |  |  |  |  |

| Param  | Characteristic              | Sym       | Min                                                                     | Typ† | Max | Units | Conditions                                                          |  |  |  |  |

| No.    |                             |           |                                                                         |      |     |       |                                                                     |  |  |  |  |

|        | Output High Voltage         |           |                                                                         |      |     |       |                                                                     |  |  |  |  |

| D090   | I/O ports (Note 3)          | Vон       | Vdd - 0.7                                                               | —    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                        |  |  |  |  |

| D090A  |                             |           | Vdd - 0.7                                                               | -    | —   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                       |  |  |  |  |

| D092   | OSC2/CLKOUT                 |           | VDD - 0.7                                                               | —    | _   | V     | IOH = TBD, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |  |

| D092A  |                             |           | VDD - 0.7                                                               | —    | _   | V     | IOH = TBD, VDD = 4.5V,<br>-40°С to +125°С                           |  |  |  |  |

|        | Capacitive Loading Specs on |           |                                                                         |      |     |       |                                                                     |  |  |  |  |

|        | Output Pins                 |           |                                                                         |      |     |       |                                                                     |  |  |  |  |

| D100   | OSC2 pin                    | Cosc2     | _                                                                       |      | 15  | pF    | In XT and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |  |

| D101   | All I/O pins                | Cio       | _                                                                       | _    | 50  | pF    |                                                                     |  |  |  |  |

tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

### FIGURE 12-8: TIMER0 CLOCK TIMINGS

### TABLE 12-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteris                            | tic            | Min                                       | Тур†      | Max        | Units          | Conditions                            |  |

|--------------|-----------|----------------------------------------|----------------|-------------------------------------------|-----------|------------|----------------|---------------------------------------|--|

| 40*          | Tt0H      | T0CKI High Pulse Width                 | No Prescaler   | 0.5TCY + 20                               | —         | — — ns Mus | Must also meet |                                       |  |

|              |           |                                        | With Prescaler | 10                                        | —         | —          | ns             | parameter 42                          |  |

| 41* Tt0L     |           | T0CKI Low Pulse Width                  | No Prescaler   | 0.5TCY + 20                               | -         | _          | ns             | Must also meet                        |  |

|              |           |                                        | With Prescaler | 10                                        | -         | _          | ns             | parameter 42                          |  |

| 42*          | Tt0P      | T0CKI Period                           | No Prescaler   | TCY + 40                                  | —         | _          | ns             |                                       |  |

|              |           |                                        | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _         | —          | ns             | N = prescale<br>value (2, 4,,<br>256) |  |

| 48           | TCKE2tmr1 | Delay from external clock of increment | 2Tosc          | _                                         | 7Tos<br>c |            |                |                                       |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### TABLE 12-6: GPIO PULL-UP RESISTOR RANGES

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Мах  | Units |

|-------------|------------------|------|------|------|-------|

|             |                  | GP0/ | /GP1 |      |       |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |

|             | 25               | 42K  | 48K  | 63K  | Ω     |

|             | 85               | 42K  | 49K  | 63K  | Ω     |

|             | 125              | 50K  | 55K  | 63K  | Ω     |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |

|             | 25               | 18K  | 20K  | 23K  | Ω     |

|             | 85               | 19K  | 22K  | 25K  | Ω     |

|             | 125              | 22K  | 24K  | 28K  | Ω     |

|             |                  | GI   | P3   |      |       |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |

|             | 25               | 343K | 414K | 532K | Ω     |

|             | 85               | 368K | 457K | 532K | Ω     |

|             | 125              | 431K | 504K | 593K | Ω     |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |

|             | 25               | 288K | 341K | 437K | Ω     |

|             | 85               | 306K | 371K | 448K | Ω     |

|             | 125              | 351K | 407K | 500K | Ω     |

\* These parameters are characterized but not tested.

# 14.0 PACKAGING INFORMATION

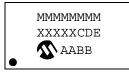

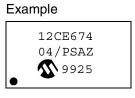

# 14.1 Package Marking Information

# 8-Lead PDIP (300 mil)

### 8-Lead SOIC (208 mil)

# 8-Lead Windowed Ceramic Side Brazed (300 mil)

| Lege | nd: MMM<br>XXX<br>AA<br>BB<br>C | Microchip part number information<br>Customer specific information*<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Facility code of the plant at which wafer is manufactured<br>O = Outside Vendor<br>C = 5" Line<br>S = 6" Line<br>H = 8" Line<br>Mask revision number<br>Assembly code of the plant or country of origin in which<br>part was assembled |

|------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note | be carried                      | nt the full Microchip part number cannot be marked on one line, it will<br>I over to the next line thus limiting the number of available characters<br>her specific information.                                                                                                                                                                                                                          |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

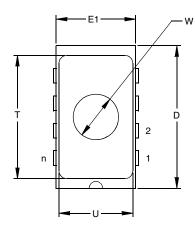

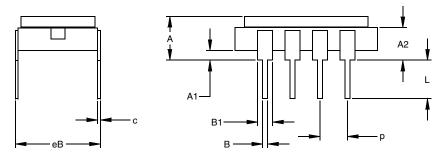

# 8-Lead Ceramic Side Brazed Dual In-line with Window (JW) - 300 mil

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                              | Units INCHES* |      |      |      | MILLIMETERS |       |       |  |

|------------------------------|---------------|------|------|------|-------------|-------|-------|--|

| Dimension                    | MIN           | NOM  | MAX  | MIN  | NOM         | MAX   |       |  |

| Number of Pins               | n             |      | 8    |      |             | 8     |       |  |

| Pitch                        | р             |      | .100 |      |             | 2.54  |       |  |

| Top to Seating Plane         | А             | .145 | .165 | .185 | 3.68        | 4.19  | 4.70  |  |

| Top of Body to Seating Plane | A2            | .103 | .123 | .143 | 2.62        | 3.12  | 3.63  |  |

| Standoff                     | A1            | .025 | .035 | .045 | 0.64        | 0.89  | 1.14  |  |

| Package Width                | E1            | .280 | .290 | .300 | 7.11        | 7.37  | 7.62  |  |

| Overall Length               | D             | .510 | .520 | .530 | 12.95       | 13.21 | 13.46 |  |

| Tip to Seating Plane         | L             | .130 | .140 | .150 | 3.30        | 3.56  | 3.81  |  |

| Lead Thickness               | С             | .008 | .010 | .012 | 0.20        | 0.25  | 0.30  |  |

| Upper Lead Width             | B1            | .050 | .055 | .060 | 1.27        | 1.40  | 1.52  |  |

| Lower Lead Width             | В             | .016 | .018 | .020 | 0.41        | 0.46  | 0.51  |  |

| Overall Row Spacing          | eB            | .296 | .310 | .324 | 7.52        | 7.87  | 8.23  |  |

| Window Diameter              | W             | .161 | .166 | .171 | 4.09        | 4.22  | 4.34  |  |

| Lid Length                   | Т             | .440 | .450 | .460 | 11.18       | 11.43 | 11.68 |  |

| Lid Width                    | U             | .260 | .270 | .280 | 6.60        | 6.86  | 7.11  |  |

\*Controlling Parameter JEDC Equivalent: MS-015 Drawing No. C04-083

# **Worldwide Sales and Service**

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 **China - Qingdao** Tel: 86-532-8502-7355

Fax: 86-532-8502-7205 China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

# EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

**France - Paris** Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12