Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | 16 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 8-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12ce674-10e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

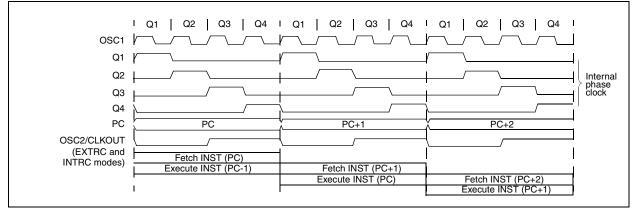

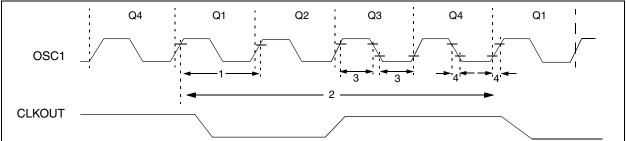

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

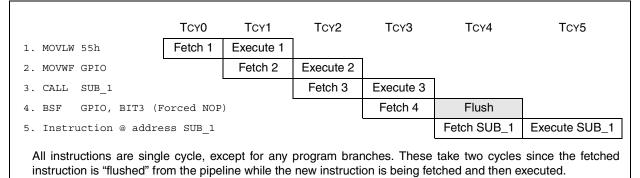

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

## **PIC12C67X**

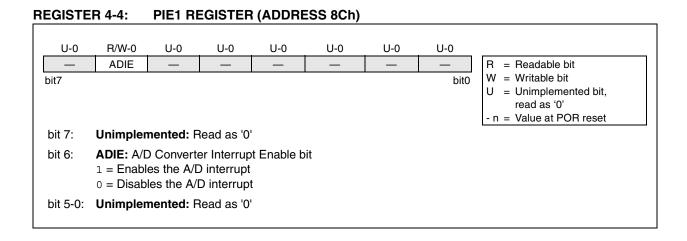

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the Peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the Peripheral interrupts.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

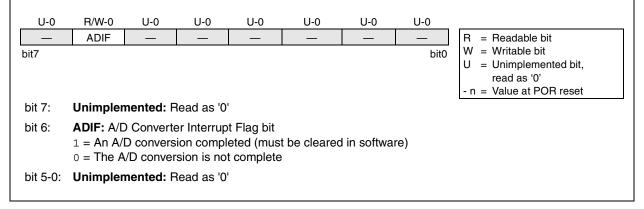

#### REGISTER 4-5: PIR1 REGISTER (ADDRESS 0Ch)

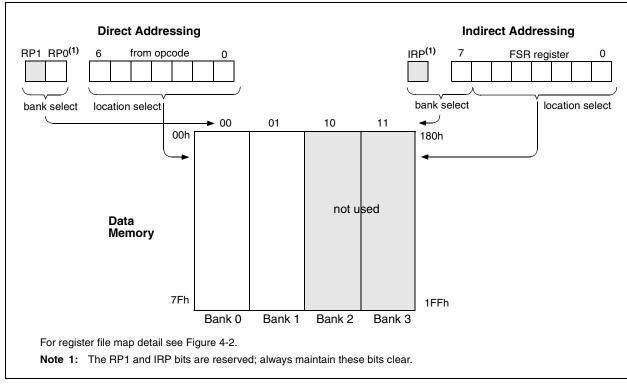

#### 4.5 Indirect Addressing, INDF and FSR Registers

The INDF Register is not a physical register. Addressing the INDF Register will cause indirect addressing.

Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF Register itself indirectly (FSR = '0') will read 00h. Writing to the INDF Register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR Register and the IRP bit (STATUS<7>), as shown in Figure 4-4. However, IRP is not used in the PIC12C67X.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-1.

#### EXAMPLE 4-1: INDIRECT ADDRESSING

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ;to RAM              |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR,F | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

#### FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

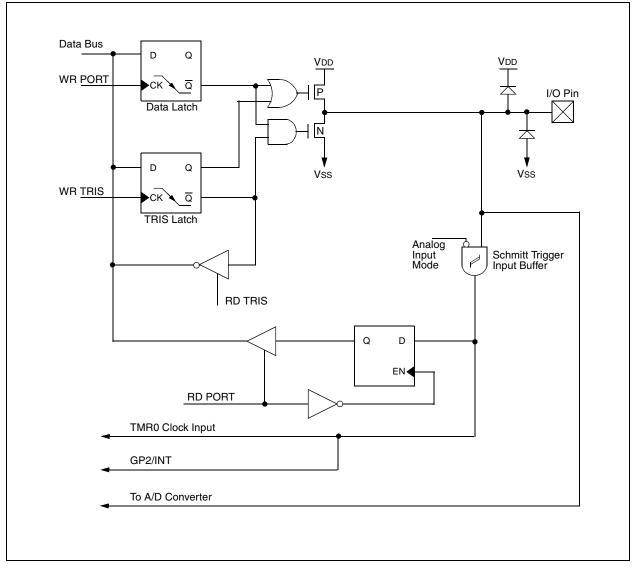

FIGURE 5-2: BLOCK DIAGRAM OF GP2/T0CKI/AN2/INT PIN

#### 6.3 Write Operations

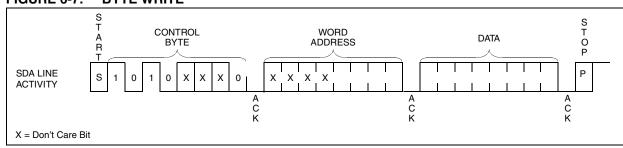

#### 6.3.1 BYTE WRITE

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the  $R/\overline{W}$  bit (which is a logic low) are placed onto the bus by the processor. This indicates to the addressed EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer. Only the lower four address bits are used by the device, and the upper four bits are don't cares. If the address byte is acknowledged, the processor will then transmit the data word to be written into the addressed memory location. The memory acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time will not generate acknowledge signals. After a byte write command, the internal address counter will not be incremented and will point to the same address location that was just written. If a stop bit sequence is transmitted to the device at any point in the write command sequence before the entire sequence is complete, then the command will abort and no data will be written. If more than 8 data bits are transmitted before the stop bit sequence is sent, then the device will clear the previously loaded byte and begin loading the data buffer again. If more than one data byte is transmitted to the device and a stop bit is sent before a full eight data bits have been transmitted, then the write command will abort and no data will be written. The EEPROM memory employs a VCC threshold detector circuit, which disables the internal erase/write logic if the Vcc is below minimum VDD. Byte write operations must be preceded and immediately followed by a bus not busy bus cycle where both SDA and SCL are held high. (See Figure 6-7 for Byte Write operation.)

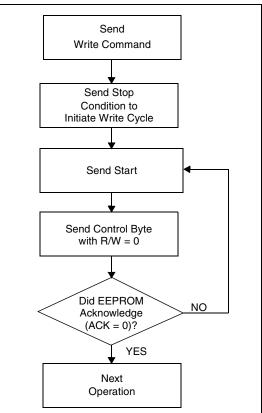

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the device initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. (See Figure 6-6 for flow diagram.)

#### FIGURE 6-6: ACKNOWLEDGE POLLING FLOW

#### FIGURE 6-7: BYTE WRITE

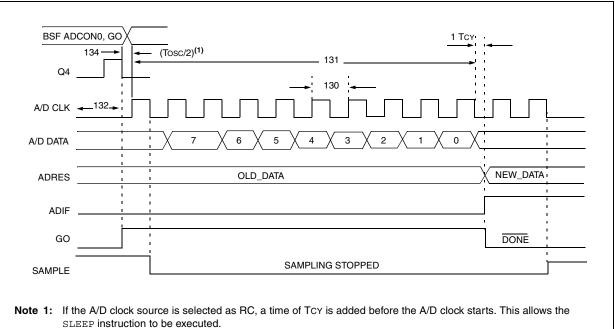

#### 8.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-To-Digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the GP1/AN1/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 Register, shown in Figure 8-1, controls the operation of the A/D module. The ADCON1 Register, shown in Figure 8-2, configures the functions of the port pins. The port pins can be configured as analog inputs (GP1 can also be a voltage reference) or as digital I/O.

- Note 1: If the port pins are configured as analog inputs (reset condition), reading the port (MOVF GPIO,W) results in reading '0's.

- 2: Changing ADCON1 Register can cause the GPIF and INTF flags to be set in the INTCON Register. These interrupts should be disabled prior to modifying ADCON1.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ADCS1 ADCS0 CHS1 CHS0 GO/DONE ADON R = Readable bit reserved reserved W = Writable bit bit0 bit7 U = Unimplemented bit, read as '0' n = Value at POR reset bit 7-6: ADCS<1:0>: A/D Conversion Clock Select bits 00 = Fosc/201 = Fosc/810 = Fosc/3211 = FRC (clock derived from an RC oscillation) Reserved bit 5: bit 4-3: CHS<1:0>: Analog Channel Select bits 00 = channel 0, (GP0/AN0) 01 = channel 1, (GP1/AN1) 10 = channel 2, (GP2/AN2) 11 = channel 3, (GP4/AN3) GO/DONE: A/D Conversion Status bit bit 2: If ADON = 11 = A/D conversion in progress (setting this bit starts the A/D conversion) 0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete) bit 1: Reserved bit 0: ADON: A/D on bit 1 = A/D converter module is operating 0 = A/D converter module is shut off and consumes no operating current

#### REGISTER 8-1: ADCON0 REGISTER (ADDRESS 1Fh)

## 9.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC12C67X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- In-circuit serial programming

The PIC12C67X has a Watchdog Timer, which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The INTRC/EXTRC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 9.1 <u>Configuration Bits</u>

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h-3FFFh), which can be accessed only during programming.

### REGISTER 9-1: CONFIGURATION WORD

|                                                                                                                                                                                                                                                                                                                                    | CD -1-0-                                                                                               |                                                                |                                                                |                                       |             |     |  |  |  |      | Address  | 2007h  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------|-------------|-----|--|--|--|------|----------|--------|

|                                                                                                                                                                                                                                                                                                                                    | 1.861.05                                                                                               | • Code                                                         | Prote                                                          | ection k                              | hit nairs(1 | 1)  |  |  |  | bit0 | 71001000 | 200711 |

| <ul> <li>bit 13-8, CP&lt;1:0&gt;: Code Protection bit pairs<sup>(1)</sup></li> <li>6-5: 11 = Code protection off</li> <li>10 = Locations 400h through 7FEh code protected (do not use for PIC12C671 and PIC12CE673)</li> <li>01 = Locations 200h through 7FEh code protected</li> <li>00 = All memory is code protected</li> </ul> |                                                                                                        |                                                                |                                                                |                                       |             |     |  |  |  |      |          |        |

|                                                                                                                                                                                                                                                                                                                                    | MCLRE:<br>1 = Mast<br>0 = Mast                                                                         | er Clea                                                        | ar Ena                                                         | bled                                  | t Enable    | bit |  |  |  |      |          |        |

|                                                                                                                                                                                                                                                                                                                                    | 4: <b>PWRTE:</b> Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                    |                                                                |                                                                |                                       |             |     |  |  |  |      |          |        |

|                                                                                                                                                                                                                                                                                                                                    | <b>WDTE:</b> W<br>1 = WDT<br>0 = WDT                                                                   | enabl                                                          | ed                                                             | ner En                                | able bit    |     |  |  |  |      |          |        |

|                                                                                                                                                                                                                                                                                                                                    | FOSC<2<br>111 = EX<br>110 = EX<br>101 = IN<br>100 = IN<br>011 = In<br>010 = HS<br>001 = XT<br>000 = LF | KTRC,<br>KTRC,<br>TRC,<br>TRC,<br>Valid S<br>S Osci<br>F Oscil | Clocko<br>OSC2<br>Clocko<br>OSC2<br>electio<br>Ilator<br>lator | out on<br>is I/O<br>ut on 0<br>is I/O | OSC2        | S   |  |  |  |      |          |        |

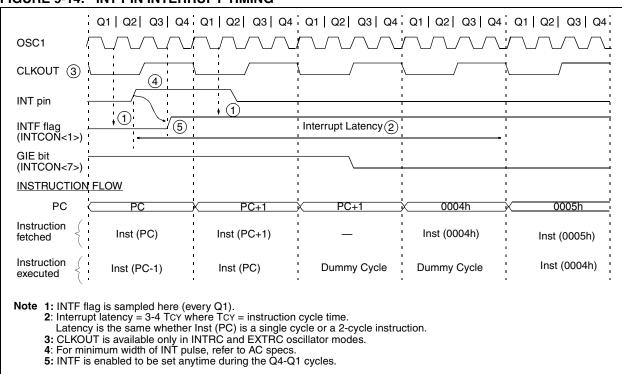

#### FIGURE 9-14: INT PIN INTERRUPT TIMING

#### 9.5.1 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 7.0). The flag bit T0IF (INTCON<2>) will be set, regardless of the state of the enable bits. If used, this flag must be cleared in software.

#### 9.5.2 INT INTERRUPT

External interrupt on GP2/INT pin is edge triggered; either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the GP2/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 9.8 for details on SLEEP mode.

#### 9.5.3 GPIO INTCON CHANGE

An input change on GP3, GP1 or GP0 sets flag bit GPIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit GPIE (INTCON<3>) (Section 5.1). This flag bit GPIF (INTCON<0>) will be set, regardless of the state of the enable bits. If used, this flag must be cleared in software.

#### 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W register and STATUS register). This will have to be implemented in software.

Example 9-1 shows the storing and restoring of the STATUS and W registers. The register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

Example 9-2 shows the saving and restoring of STA-TUS and W using RAM locations 0x70 - 0x7F. W\_TEMP is defined at 0x70 and STATUS\_TEMP is defined at 0x71.

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Executes the ISR code.

- d) Restores the STATUS register (and bank select bit).

- e) Restores the W register.

- f) Returns from interrupt.

## EXAMPLE 9-1: SAVING STATUS AND W REGISTERS USING GENERAL PURPOSE RAM (0x20 - 0x6F)

|                | W_TEMP<br>STATUS,W<br>STATUS,RP0<br>STATUS_TEMP |                                                                                                                                                                      |

|----------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>SWAPF | _<br>STATUS<br>W_TEMP,F                         | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)<br>;Move W into STATUS register<br>;Swap W_TEMP<br>;Swap W_TEMP into W<br>;Return from interrupt |

|                |                                                 |                                                                                                                                                                      |

| EXAMPLE 9-2:   | SAVING STATUS                                   | AND W REGISTERS USING SHARED RAM (0x70 - 0x7F)                                                                                                                       |

| MOVWF<br>MOVF  | W_TEMP<br>STATUS,W                              | AND W REGISTERS USING SHARED RAM (0x70 - 0x7F)<br>;Copy W to TEMP register (bank independent)<br>;Move STATUS register into W<br>;Save contents of STATUS register   |

| BCF              | Bit Clear                                                           | f       |                        |      |

|------------------|---------------------------------------------------------------------|---------|------------------------|------|

| Syntax:          | [ label ] BCF f,b                                                   |         |                        |      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |         |                        |      |

| Operation:       | $0 \rightarrow (f < b >)$                                           |         |                        |      |

| Status Affected: | None                                                                |         |                        |      |

| Encoding:        | 01                                                                  | 00bb    | bfff                   | ffff |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |         |                        |      |

| Words:           | 1                                                                   |         |                        |      |

| Cycles:          | 1                                                                   |         |                        |      |

| Example          | BCF                                                                 | FLAG_   | REG, 7                 |      |

|                  | After Inst                                                          | FLAG_RE | EG = 0xC7<br>EG = 0x47 |      |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                                        |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                        |  |  |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                                                                    |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                       |  |  |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                                          |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the<br>next instruction is skipped.<br>If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded,<br>and a NOP is executed instead,<br>making this a 2 cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                          |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                       |  |  |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CO<br>TRUE • DE<br>•                                                                                                                                                                                                               |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                                    |  |  |  |  |

|                  | After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1>=1,<br>PC = address FALSE                                                                                                                                                                           |  |  |  |  |

| BSF              | Bit Set f                                                                     |            |           |      |  |

|------------------|-------------------------------------------------------------------------------|------------|-----------|------|--|

| Syntax:          | [ <i>label</i> ] BSF f,b                                                      |            |           |      |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$           |            |           |      |  |

| Operation:       | $1 \rightarrow (f < b;$                                                       | >)         |           |      |  |

| Status Affected: | None                                                                          |            |           |      |  |

| Encoding:        | 01                                                                            | 01bb       | bfff      | ffff |  |

| Description:     | Bit 'b' in r                                                                  | egister 'f | ' is set. |      |  |

| Words:           | 1                                                                             |            |           |      |  |

| Cycles:          | 1                                                                             |            |           |      |  |

| Example          | BSF                                                                           | FLAG_F     | REG, 7    |      |  |

|                  | Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |            |           |      |  |

# **PIC12C67X**

| IORWF            | Inclusive OR W with f                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                         |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                         |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in regis-<br>ter 'f'. |

| Words:           | 1                                                                                                                                                                         |

| Cycles:          | 1                                                                                                                                                                         |

| Example          | IORWF RESULT, 0                                                                                                                                                           |

|                  | Before Instruction<br>RESULT = $0x13$<br>W = $0x91$<br>After Instruction<br>RESULT = $0x13$<br>W = $0x93$<br>Z = $1$                                                      |

| MOVLW            | Move Lite                            | eral to V      | v          |      |

|------------------|--------------------------------------|----------------|------------|------|

| Syntax:          | [ label ]                            | MOVLW          | / k        |      |

| Operands:        | $0 \le k \le 25$                     | 55             |            |      |

| Operation:       | $k \to (W)$                          |                |            |      |

| Status Affected: | None                                 |                |            |      |

| Encoding:        | 11                                   | 00xx           | kkkk       | kkkk |

| Description:     | The eight<br>into W re<br>will asser | gister. Th     | ne don't c |      |

| Words:           | 1                                    |                |            |      |

| Cycles:          | 1                                    |                |            |      |

| Example          | MOVLW                                | 0x5A           |            |      |

|                  | After Inst                           | ruction<br>W = | 0x5A       |      |

| MOVF             | Move f                                                                                                                                                                                                                                                                             |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                                                 |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                    |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                           |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                                                                                  |  |  |  |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ , des-<br>tination is W register. If $d = 1$ , the<br>destination is file register f itself.<br>d = 1 is useful to test a file register<br>since status flag Z is affected. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                  |  |  |  |

| Example          | MOVF FSR, <b>0</b>                                                                                                                                                                                                                                                                 |  |  |  |

|                  | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                                                                            |  |  |  |

| MOVWF            | Move W              | to f        |             |                                      |         |

|------------------|---------------------|-------------|-------------|--------------------------------------|---------|

| Syntax:          | [ label ]           | MOVW        | = f         |                                      |         |

| Operands:        | $0 \le f \le 127$   |             |             |                                      |         |

| Operation:       | $(W) \to (f)$       |             |             |                                      |         |

| Status Affected: | None                |             |             |                                      |         |

| Encoding:        | 0 0                 | 0000        | 1ff         | f                                    | ffff    |

| Description:     | Move dat ister 'f'. | a from V    | V regi      | ister                                | to reg- |

| Words:           | 1                   |             |             |                                      |         |

| Cycles:          | 1                   |             |             |                                      |         |

| Example          | MOVWF               | OPT         | TION        |                                      |         |

|                  | After Inst          | OPTION<br>W | =<br>=<br>= | 0xFF<br>0x4F<br>0x4F<br>0x4F<br>0x4F | :       |

# **PIC12C67X**

| NOP              | No Operation |       |      |      |

|------------------|--------------|-------|------|------|

| Syntax:          | [ label ]    | NOP   |      |      |

| Operands:        | None         |       |      |      |

| Operation:       | No opera     | ation |      |      |

| Status Affected: | None         |       |      |      |

| Encoding:        | 0 0          | 0000  | 0xx0 | 0000 |

| Description:     | No opera     | tion. |      |      |

| Words:           | 1            |       |      |      |

| Cycles:          | 1            |       |      |      |

| Example          | NOP          |       |      |      |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Operation:       | TOS $\rightarrow$ PC,<br>1 $\rightarrow$ GIE                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global Inter-<br>rupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |  |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| OPTION           | Load Option Register                                                                                |                                                              |                                                              |                                    |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] OPTION                                                                                    |                                                              |                                                              |                                    |  |  |  |  |  |  |

| Operands:        | None                                                                                                | None                                                         |                                                              |                                    |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow O$                                                                                 | PTION                                                        |                                                              |                                    |  |  |  |  |  |  |

| Status Affected: | None                                                                                                |                                                              |                                                              |                                    |  |  |  |  |  |  |

| Encoding:        | 0 0                                                                                                 | 0000                                                         | 0110                                                         | 0010                               |  |  |  |  |  |  |

| Description:     | The conte<br>loaded in<br>This instr<br>code com<br>products.<br>able/writa<br>directly a           | the OPT<br>ruction is<br>patibility<br>Since C<br>able regis | FION regi<br>supporte<br>with PIC<br>PTION is<br>ster, the u | ster.<br>d for<br>16C5X<br>a read- |  |  |  |  |  |  |

| Words:           | 1                                                                                                   |                                                              |                                                              |                                    |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                   |                                                              |                                                              |                                    |  |  |  |  |  |  |

| Example          |                                                                                                     |                                                              |                                                              |                                    |  |  |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC12C67X products,<br>do not use this instruction. |                                                              |                                                              |                                    |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two cycle instruction. |  |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Example          | CALL TABLE;W contains<br>table<br>;offset value                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| TABLE            | • ;W now has table value                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |  |  |  |  |  |  |  |  |  |

|                  | •<br>RETLW kn ;End of table                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = value of k8                                                                                                                                                |  |  |  |  |  |  |  |  |  |

#### 12.1 DC Characteristics: PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

| DC CH                        | ARACTERISTICS                                                              |       | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C &\leq Ta \leq +70^{\circ}C \mbox{ (commercial)} \\ -40^{\circ}C \leq Ta \leq +85^{\circ}C \mbox{ (industrial)} \\ -40^{\circ}C \leq Ta \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |                    |          |                  |                                                                                                                                                      |  |  |

|------------------------------|----------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parm Characteristic S<br>No. |                                                                            |       | Min                                                                                                                                                                                                                                                                                                                         | Typ <sup>(1)</sup> | Max      | Units            | s Conditions                                                                                                                                         |  |  |

| D001                         | Supply Voltage                                                             | Vdd   | 3.0                                                                                                                                                                                                                                                                                                                         |                    | 5.5      | V                |                                                                                                                                                      |  |  |

| D002                         | RAM Data Retention<br>Voltage <sup>(2)</sup>                               | Vdr   |                                                                                                                                                                                                                                                                                                                             | 1.5*               |          | V                | Device in SLEEP mode                                                                                                                                 |  |  |

| D003                         | VDD Start Voltage to ensure<br>Power-on Reset                              | VPOR  |                                                                                                                                                                                                                                                                                                                             | Vss                |          | V                | See section on Power-on Reset for details                                                                                                            |  |  |

| D004                         | VDD Rise Rate to ensure<br>Power-on Reset                                  | SVDD  | 0.05*                                                                                                                                                                                                                                                                                                                       |                    |          | V/ms             | See section on Power-on Reset for details                                                                                                            |  |  |

| D010                         | Supply Current <sup>(3)</sup>                                              | Idd   | —                                                                                                                                                                                                                                                                                                                           | 1.2                | 2.5      | mA               | Fosc = 4MHz, VDD = 3.0V<br>XT and EXTRC mode (Note 4)                                                                                                |  |  |

| D010C                        |                                                                            |       | —                                                                                                                                                                                                                                                                                                                           | 1.2                | 2.5      | mA               | Fosc = 4MHz, VDD = 3.0V<br>INTRC mode (Note 6)                                                                                                       |  |  |

|                              |                                                                            |       | —                                                                                                                                                                                                                                                                                                                           | 2.2                | 8        | mA               | Fosc = 10MHz, VDD = 5.5V<br>HS mode                                                                                                                  |  |  |

| D010A                        |                                                                            |       | _                                                                                                                                                                                                                                                                                                                           | 19                 | 29       | μA               | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Commercial Temperature                                                                            |  |  |

|                              |                                                                            |       | _                                                                                                                                                                                                                                                                                                                           | 19<br>32           | 37<br>60 | μΑ<br>μΑ         | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Industrial Temperature<br>Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Extended Temperature |  |  |

| D020                         | Power-down Current <sup>(5)</sup>                                          | IPD   |                                                                                                                                                                                                                                                                                                                             | 0.25               | 6        | μA               | VDD = 3.0V, Commercial, WDT disabled                                                                                                                 |  |  |

| D021                         |                                                                            |       | _                                                                                                                                                                                                                                                                                                                           | 0.25               | 7        | μA               | $V_{DD} = 3.0V$ , Industrial, WDT disabled                                                                                                           |  |  |

| D021B                        |                                                                            |       | —                                                                                                                                                                                                                                                                                                                           | 2                  | 14       | μA               | VDD = 3.0V, Extended, WDT disabled                                                                                                                   |  |  |

|                              |                                                                            |       | —                                                                                                                                                                                                                                                                                                                           | 0.5                | 8        | μA               | VDD = 5.5V, Commercial, WDT disabled                                                                                                                 |  |  |

|                              |                                                                            |       | _                                                                                                                                                                                                                                                                                                                           | 0.8<br>3           | 9<br>16  | μA<br>μA         | VDD = 5.5V, Industrial, WDT disabled<br>VDD = 5.5V, Extended, WDT disabled                                                                           |  |  |

| D022                         | Watchdog Timer Current                                                     | ΔIWDT |                                                                                                                                                                                                                                                                                                                             | 2.2                | 5        | μA               | VDD = 3.0V, Commercial                                                                                                                               |  |  |

|                              |                                                                            |       | _                                                                                                                                                                                                                                                                                                                           | 2.2<br>4           | 6<br>11  | μ <b>Α</b><br>μΑ | VDD = 3.0V, Industrial<br>VDD = 3.0V, Extended                                                                                                       |  |  |

| D028                         | Supply Current <sup>(3)</sup><br>During read/write to<br>EEPROM peripheral | ΔIEE  |                                                                                                                                                                                                                                                                                                                             | 0.1                | 0.2      | mA               | Fosc = 4MHz, VDD = 5.5V, SCL = 400kHz<br>For PIC12CE673/674 only                                                                                     |  |  |

These parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

**6:** INTRC calibration value is for 4MHz nominal at 5V,  $25^{\circ}$ C.

#### 12.2 DC Characteristics: PIC12LC671/672 (Commercial, Industrial) PIC12LCE673/674 (Commercial, Industrial)

| DC CHAF               | RACTERISTICS                                  |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |                  |            |                                                                                                                             |  |  |  |

|-----------------------|-----------------------------------------------|-------|------------------------------------------------------|------------|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.          | Sym                                           | Min   | lin Typ†                                             | Max        | Units            | Conditions |                                                                                                                             |  |  |  |

| D001                  | Supply Voltage                                | Vdd   | 2.5                                                  |            | 5.5              | V          |                                                                                                                             |  |  |  |

| D002                  | RAM Data Retention<br>Voltage <sup>(2)</sup>  | Vdr   |                                                      | 1.5*       |                  | V          | Device in SLEEP mode                                                                                                        |  |  |  |

| D003                  | VDD Start Voltage to<br>ensure Power-on Reset | VPOR  |                                                      | Vss        |                  | V          | See section on Power-on Reset for details                                                                                   |  |  |  |

| D004                  | VDD Rise Rate to ensure<br>Power-on Reset     | Svdd  | 0.05*                                                |            |                  | V/ms       | See section on Power-on Reset for details                                                                                   |  |  |  |

| D010                  | Supply Current <sup>(3)</sup>                 | IDD   | —                                                    | 0.4        | 2.1              | mA         | Fosc = 4MHz, VDD = 2.5V<br>XT and EXTRC mode (Note 4)                                                                       |  |  |  |

| D010C<br>D010A        |                                               |       | _                                                    | 0.4<br>15  | 2.1<br>33        | mA<br>μA   | Fosc = 4MHz, VDD = 2.5V<br>INTRC mode (Note 6)<br>Fosc = 32kHz, VDD = 2.5V, WDT disabled<br>LP mode, Industrial Temperature |  |  |  |

| D020<br>D021<br>D021B | Power-down Current <sup>(5)</sup>             | IPD   | _                                                    | 0.2<br>0.2 | 5<br>6           | μΑ<br>μΑ   | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                                                                            |  |  |  |

|                       | Watchdog Timer Current                        | ΔIWDT | —                                                    | 2.0<br>2.0 | 4<br>6           | μΑ<br>μΑ   | VDD = 2.5V, Commercial<br>VDD = 2.5V, Industrial                                                                            |  |  |  |

|                       | LP Oscillator Operating<br>Frequency          | Fosc  | 0                                                    |            | 200              | kHz        | All temperatures                                                                                                            |  |  |  |

|                       | INTRC/EXTRC Oscillator<br>Operating Frequency |       | -                                                    |            | 4 <sup>(6)</sup> | MHz        | All temperatures                                                                                                            |  |  |  |

|                       | XT Oscillator Operating<br>Frequency          |       | 0                                                    |            | 4                | MHz        | All temperatures                                                                                                            |  |  |  |

|                       | HS Oscillator Operating<br>Frequency          |       | 0                                                    |            | 10               | MHz        | All temperatures                                                                                                            |  |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

- 4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

#### 12.6 <u>Timing Diagrams and Specifications</u>

#### TABLE 12-1: CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                  | Min  | Тур† | Max    | Units | Conditions                  |

|------------------|-------|---------------------------------|------|------|--------|-------|-----------------------------|

|                  | Fosc  | External CLKIN Frequency        |      | _    | 4      | MHz   | XT and EXTRC osc mode       |

|                  |       | (Note 1)                        | DC   | —    | 4      | MHz   | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | DC   | —    | 10     | MHz   | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | DC   | _    | 200    | kHz   | LP osc mode                 |

|                  |       | Oscillator Frequency            | DC   | _    | 4      | MHz   | EXTRC osc mode              |

|                  |       | (Note 1)                        | .455 | —    | 4      | MHz   | XT osc mode                 |

|                  |       |                                 | 4    | —    | 4      | MHz   | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 4    | —    | 10     | MHz   | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | —    | 200    | kHz   | LP osc mode                 |

| 1                | Tosc  | External CLKIN Period           | 250  | _    | _      | ns    | XT and EXTRC osc mode       |

|                  |       | (Note 1)                        | 250  | _    | _      | ns    | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 100  | —    |        | ns    | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | _    | _      | μs    | LP osc mode                 |

|                  |       | Oscillator Period               | 250  | —    | —      | ns    | EXTRC osc mode              |

|                  |       | (Note 1)                        | 250  | —    | 10,000 | ns    | XT osc mode                 |

|                  |       |                                 | 250  | —    | 250    | ns    | HS osc mode (PIC12CE67X-04) |

|                  |       |                                 | 100  | —    | 250    | ns    | HS osc mode (PIC12CE67X-10) |

|                  |       |                                 | 5    | —    | —      | μs    | LP osc mode                 |

| 2                | Тсү   | Instruction Cycle Time (Note 1) | 400  | —    | DC     | ns    | TCY = 4/FOSC                |

| 3                | TosL, | External Clock in (OSC1) High   | 50   | —    | —      | ns    | XT oscillator               |

|                  | TosH  | or Low Time                     | 2.5  | —    | —      | μS    | LP oscillator               |

|                  |       |                                 | 10   | —    | —      | ns    | HS oscillator               |

| 4                | TosR, | External Clock in (OSC1) Rise   | —    | —    | 25     | ns    | XT oscillator               |

|                  | TosF  | or Fall Time                    | —    | —    | 50     | ns    | LP oscillator               |

|                  |       |                                 | —    | —    | 15     | ns    | HS oscillator               |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. OSC2 is disconnected (has no loading) for the PIC12C67X.

# TABLE 12-7:A/D CONVERTER CHARACTERISTICS:<br/>PIC12C671/672-04/PIC12CE673/674-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC12C671/672-10/PIC12CE673/674-10 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC12LC671/672-04/PIC12LCE673/674-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym  | Characteristic                       |                    | Min       | Тур†                   | Max        | Units | Conditions                                                                                                 |

|--------------|------|--------------------------------------|--------------------|-----------|------------------------|------------|-------|------------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                           |                    | _         | _                      | 8-bits     | bit   | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                             |

| A02          | Eabs | Total absolute erro                  | r                  | _         | _                      | < ±1       | LSb   | VREF = VDD = 5.12V,<br>VSS $\leq$ VAIN $\leq$ VREF                                                         |

| A03          | EIL  | Integral linearity er                | ror                | _         | _                      | < ±1       | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$               |

| A04          | Edl  | Differential linearity               | / error            | _         | _                      | < ±1       | LSb   | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                             |

| A05          | EFS  | Full scale error                     |                    | _         | _                      | < ±1       | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                       |

| A06          | EOFF | Offset error                         |                    | —         | _                      | < ±1       | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                       |

| A10          | _    | Monotonicity                         |                    | _         | guaranteed<br>(Note 3) | _          | —     | $Vss \leq Vain \leq Vref$                                                                                  |

| A20          | VREF | Reference voltage                    |                    | 2.5V      | —                      | VDD + 0.3  | V     |                                                                                                            |

| A25          | VAIN | Analog input voltag                  | je                 | Vss - 0.3 | _                      | VREF + 0.3 | V     |                                                                                                            |

| A30          | ZAIN | Recommended im<br>analog voltage sou |                    | _         | _                      | 10.0       | kΩ    |                                                                                                            |

| A40          | IAD  | A/D conversion                       | PIC12 <b>C</b> 67X | _         | 180                    | —          | μA    | Average current con-                                                                                       |