#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               |                                                                           |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 8-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc671-04-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC12C67X devices are low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converter and EEPROM data memory (EEPROM on PIC12CE67X versions only).

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC12C67X microcontrollers have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches, which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC12C67X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC12C67X devices have 128 bytes of RAM, 16 bytes of EEPROM data memory (PIC12CE67X only), 5 I/O pins and 1 input pin. In addition a timer/counter is available. Also a 4-channel, high-speed, 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, (i.e., thermostat control, pressure sensing, etc.)

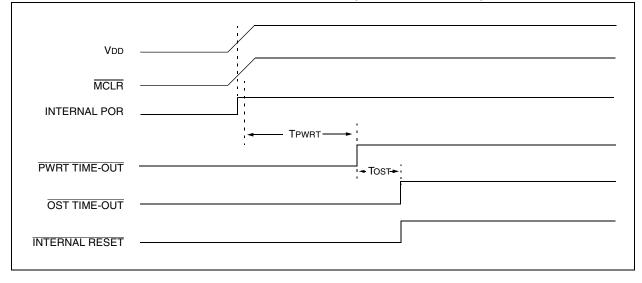

The PIC12C67X devices have special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. The Power-On Reset (POR), Power-up Timer (PWRT), and Oscillator Start-up Timer (OST) eliminate the need for external reset circuitry. There are five oscillator configurations to choose from, including INTRC precision internal oscillator mode and the power-saving LP (Low Power) oscillator mode. Power-saving SLEEP mode, Watchdog Timer and code protection features improve system cost, power and reliability. The SLEEP (power-down) feature provides a power-saving mode. The user can wake-up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock-up.

A UV erasable windowed package version is ideal for code development, while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

## 1.1 <u>Applications</u>

The PIC12C67X series fits perfectly in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The EPROM technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient, while the EEPROM data memory (PIC12CE67X only) technology allows for the changing of calibration factors and security codes. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC12C67X series very versatile even in areas where no microcontroller use has been considered before (i.e., timer functions, replacement of "glue" logic and PLD's in larger systems, coprocessor applications).

## 1.2 Family and Upward Compatibility

The PIC12C67X products are compatible with other members of the 14-bit PIC16CXXX families.

## 1.3 Development Support

The PIC12C67X devices are supported by a fullfeatured macro assembler, a software simulator, an incircuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

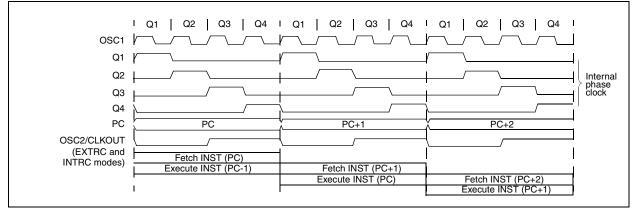

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

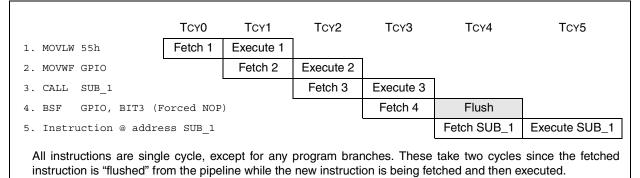

### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

### **EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW**

## 4.0 MEMORY ORGANIZATION

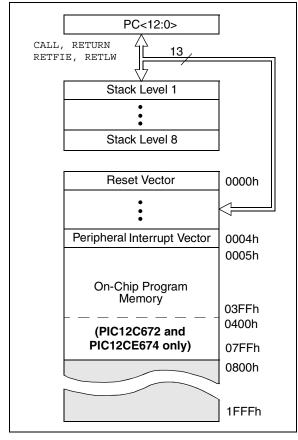

## 4.1 Program Memory Organization

The PIC12C67X has a 13-bit program counter capable of addressing an 8K x 14 program memory space.

For the PIC12C671 and the PIC12CE673, the first 1K x 14 (0000h-03FFh) is implemented.

For the PIC12C672 and the PIC12CE674, the first 2K x 14 (0000h-07FFh) is implemented. Accessing a location above the physically implemented address will cause a wraparound. The reset vector is at 0000h and the interrupt vector is at 0004h.

### FIGURE 4-1: PIC12C67X PROGRAM MEMORY MAP AND STACK

## 4.2 Data Memory Organization

The data memory is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. Bit RP0 is the bank select bit.

RP0 (STATUS<5>) =  $1 \rightarrow \text{Bank } 1$

RP0 (STATUS<5>) =  $0 \rightarrow Bank 0$

Each Bank extends up to 7Fh (128 bytes). The lower locations of each Bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers implemented as static RAM. Both Bank 0 and Bank 1 contain Special Function Registers. Some "high use" Special Function Registers from Bank 0 are mirrored in Bank 1 for code reduction and quicker access.

Also note that F0h through FFh on the PIC12C67X is mapped into Bank 0 registers 70h-7Fh as common RAM.

4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register FSR (Section 4.5).

## 4.3 PCL and PCLATH

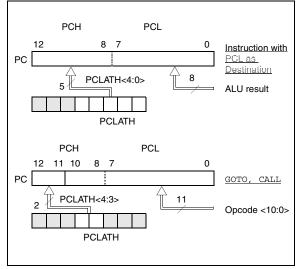

The Program Counter (PC) is 13-bits wide. The low byte comes from the PCL Register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any reset, the PC is cleared. Figure 4-3 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### 4.3.1 COMPUTED GOTO

A Computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

### 4.3.2 STACK

The PIC12C67X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

## 4.4 <u>Program Memory Paging</u>

The PIC12C67X ignores both paging bits PCLATH<4:3>, which are used to access program memory when more than one page is available. The use of PCLATH<4:3> as general purpose read/write bits for the PIC12C67X is not recommended since this may affect upward compatibility with future products.

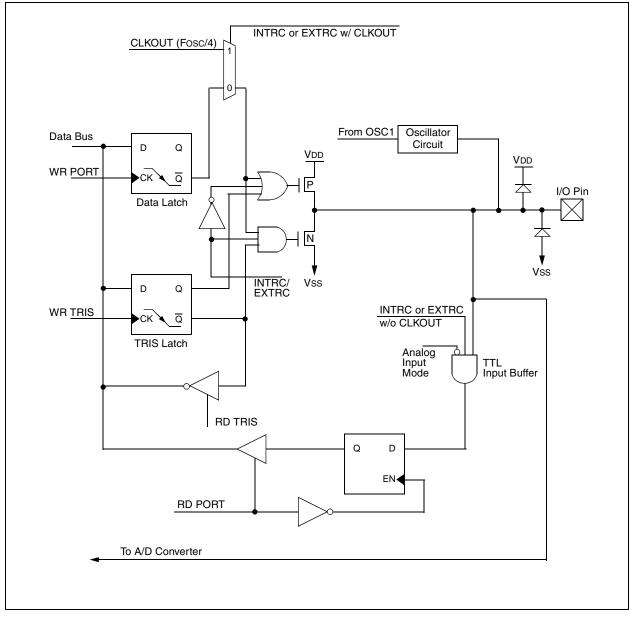

FIGURE 5-4: BLOCK DIAGRAM OF GP4/OSC2/AN3/CLKOUT PIN

### 7.3 <u>Prescaler</u>

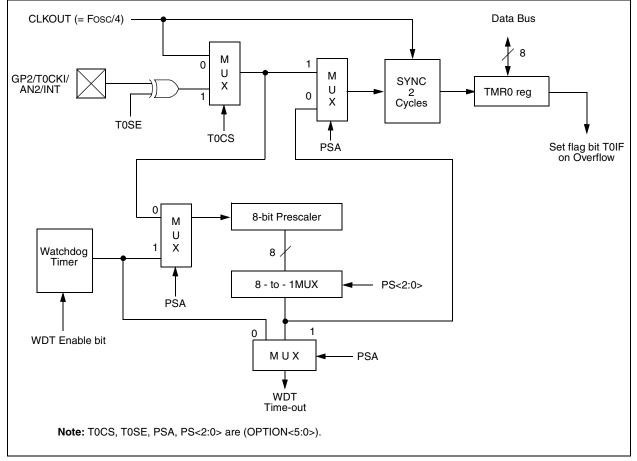

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x..., etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

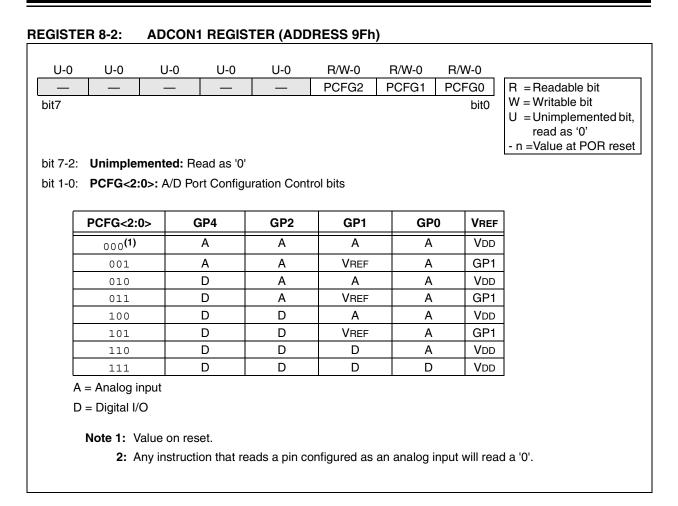

## 8.4 <u>A/D Conversions</u>

;

;

;

Example 8-2 shows how to perform an A/D conversion. The GPIO pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled and the A/D conversion clock is FRC. The conversion is performed on the GP0 channel.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

## EXAMPLE 8-2: DOING AN A/D CONVERSION

| BSF        | STATUS,   | RP0          | ;  | Select Page 1                                       |

|------------|-----------|--------------|----|-----------------------------------------------------|

| CLRF       | ADCON1    |              | ;  | Configure A/D inputs                                |

| BSF        | PIE1,     | ADIE         | ;  | Enable A/D interrupts                               |

| BCF        | STATUS,   | RP0          | ;  | Select Page 0                                       |

| MOVLW      | 0xC1      |              | ;  | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF      | ADCON0    |              | ;  |                                                     |

| BCF        | PIR1,     | ADIF         | ;  | Clear A/D interrupt flag bit                        |

| BSF        | INTCON,   | PEIE         | ;  | Enable peripheral interrupts                        |

| BSF        | INTCON,   | GIE          | ;  | Enable all interrupts                               |

|            |           |              |    |                                                     |

| Ensure tha | at the re | equired samp | li | ng time for the selected input channel has elapsed. |

Then the conversion may be started.

| BSF | ADCON0, GO | ; Start A/D Conversion                             |

|-----|------------|----------------------------------------------------|

| :   |            | ; The ADIF bit will be set and the GO/DONE bit     |

| :   |            | ; is cleared upon completion of the A/D Conversion |

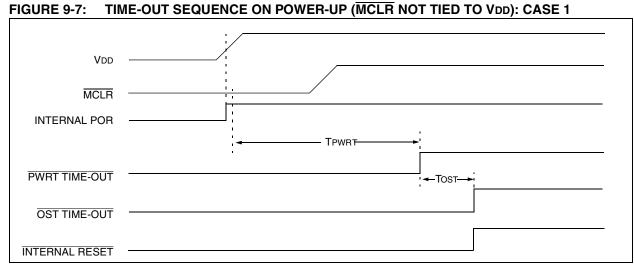

### FIGURE 9-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

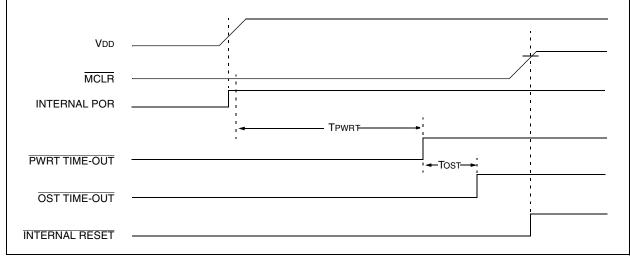

## FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

| TABLE 10-2: INSTRUCTION SET S |

|-------------------------------|

|-------------------------------|

| Mnemonic,<br>Operands |         | Description                  | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------------------|---------|------------------------------|--------|---------------|------|------|------|----------|-------|

|                       |         |                              |        | MSb           |      |      | LSb  | Affected |       |

| BYTE-ORIE             |         | FILE REGISTER OPERATIONS     |        |               |      |      |      |          |       |

| ADDWF                 | f, d    | Add W and f                  | 1      | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF                 | f, d    | AND W with f                 | 1      | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF                  | f       | Clear f                      | 1      | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                  | -       | Clear W                      | 1      | 00            | 0001 | 0000 | 0011 | Z        |       |

| COMF                  | f, d    | Complement f                 | 1      | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF                  | f, d    | Decrement f                  | 1      | 00            | 0011 | dfff |      | Z        | 1,2   |

| DECFSZ                | f, d    | Decrement f, Skip if 0       | 1(2)   | 00            | 1011 | dfff | ffff |          | 1,2,3 |

| INCF                  | f, d    | Increment f                  | 1      | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ                | f, d    | Increment f, Skip if 0       | 1(2)   | 00            | 1111 | dfff | ffff |          | 1,2,3 |

| IORWF                 | f, d    | Inclusive OR W with f        | 1      | 00            | 0100 |      | ffff | Z        | 1,2   |

| MOVF                  | f, d    | Move f                       | 1      | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF                 | f       | Move W to f                  | 1      | 00            | 0000 | lfff | ffff |          |       |

| NOP                   | -       | No Operation                 | 1      | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF                   | f, d    | Rotate Left f through Carry  | 1      | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF                   | f, d    | Rotate Right f through Carry | 1      | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF                 | f, d    | Subtract W from f            | 1      | 00            | 0010 |      | ffff | C,DC,Z   | 1,2   |

| SWAPF                 | f, d    | Swap nibbles in f            | 1      | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF                 | f, d    | Exclusive OR W with f        | 1      | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BIT-ORIEN             | TED FIL | E REGISTER OPERATIONS        |        |               |      |      |      |          |       |

| BCF                   | f, b    | Bit Clear f                  | 1      | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF                   | f, b    | Bit Set f                    | 1      | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC                 | f, b    | Bit Test f, Skip if Clear    | 1 (2)  | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS                 | f, b    | Bit Test f, Skip if Set      | 1 (2)  | 01            | 11bb | bfff | ffff |          | 3     |

| LITERAL A             | ND CO   | NTROL OPERATIONS             |        |               |      |      |      |          |       |

| ADDLW                 | k       | Add literal and W            | 1      | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW                 | k       | AND literal with W           | 1      | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL                  | k       | Call subroutine              | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT                | -       | Clear Watchdog Timer         | 1      | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO                  | k       | Go to address                | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| IORLW                 | k       | Inclusive OR literal with W  | 1      | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW                 | k       | Move literal to W            | 1      | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE                | -       | Return from interrupt        | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                 | k       | Return with literal in W     | 2      | 11            | 01xx | kkkk | kkkk |          |       |

| RETURN                | -       | Return from Subroutine       | 2      | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP                 | -       | Go into standby mode         | 1      | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SUBLW                 | k       | Subtract W from literal      | 1      | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |

| XORLW                 | k       | Exclusive OR literal with W  | 1      | 11            | 1010 | kkkk | kkkk | Z        |       |

**Note 1:** When an I/O register is modified as a function of itself (i.e., MOVF PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BTFSS                                                                                                    | Bit Test f, Skip if Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                                                                  | [ label ] BTFSS f,b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Operands:                                                                                                | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Operation:                                                                                               | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Status Affected:                                                                                         | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Encoding:                                                                                                | 01 11bb bfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:                                                                                             | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a 2 cycle instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Words:                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Cycles:                                                                                                  | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Example                                                                                                  | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CO<br>TRUE • DE<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                          | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                                                                                                          | PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                          | if FLAG<1> = 1,<br>PC = address TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| CALL                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| CALL<br>Syntax:                                                                                          | PC = address TRUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                                                                                          | PC = address TRUE Call Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Syntax:                                                                                                  | PC = address TRUE Call Subroutine [label] CALL k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                                     | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                                       | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                                                   | PC = address TRUE<br><b>Call Subroutine</b><br>[ <i>label</i> ] CALL k<br>$0 \le k \le 2047$<br>(PC)+ 1 $\rightarrow$ TOS,<br>$k \rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11><br>None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                      | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                      | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k \\ 0 \le k \le 2047 \\ (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \\ \hline None \\ \hline 10 0kkk kkk kkk \\ \hline kkkk \\ \hline Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits < 10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. \\ \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:            | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k \\ 0 \le k \le 2047 \\ (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<4:3>) \rightarrow PC<12:11> \\ \hline None \\ \hline 10 0kkk kkkk kkkk \\ \hline 0 \le 100 \\ \hline 10 0kkk kkkk kkkk \\ \hline 0 \le 100 \\ \hline 10 0kkk kkkk kkkk \\ \hline 10 0kkk kkk kkkk \\ \hline 10 0kkk kkkk kkkk \\ \hline 10 0kkk kkkk kkkk \\ \hline 10 0kkk kkkk kkk \\ \hline 10 0kkk kkk kkk \\ \hline 10 0kkk kkkk kkkk \\ \hline 10 0kkk kkkk kkkk \\ \hline 10 0kkk kkk kkk kkk \\ \hline 10 0kkk kkk kkk \\ \hline 10 0kkk kkk kkk kkk \\ \hline 10 0kk k kkk kkk kkk kkk kkk \\ \hline 10 0kk kkk kkk kkk kkk kkk kkk kkk kkk $ |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:<br>Words:<br>Cycles: | $PC = address TRUE$ $\begin{bmatrix} label \end{bmatrix} CALL k$ $0 \le k \le 2047$ $(PC)+1 \rightarrow TOS, k \rightarrow PC < 12:11 >$ $None$ $\boxed{10  0kkk  kkkk  kkkk}$ Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits < 10:0 >. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. $1$ $2$ HERE CALL THER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| CLRF             | Clear f                                                                                    |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] CLRF f                                                                             |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                        |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                      |  |  |  |  |  |  |

| Status Affected: | Z                                                                                          |  |  |  |  |  |  |

| Encoding:        | 00 0001 1fff ffff                                                                          |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                             |  |  |  |  |  |  |

| Words:           | 1                                                                                          |  |  |  |  |  |  |

| Cycles:          | 1                                                                                          |  |  |  |  |  |  |

| Example          | CLRF FLAG_REG                                                                              |  |  |  |  |  |  |

|                  | Before Instruction<br>$FLAG_REG = 0x5A$<br>After Instruction<br>$FLAG_REG = 0x00$<br>Z = 1 |  |  |  |  |  |  |

| CLRW             | Clear W                                                               |                       |           |         |  |

|------------------|-----------------------------------------------------------------------|-----------------------|-----------|---------|--|

| Syntax:          | [ label ]                                                             | CLRW                  |           |         |  |

| Operands:        | None                                                                  |                       |           |         |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |                       |           |         |  |

| Status Affected: | Z                                                                     |                       |           |         |  |

| Encoding:        | 00                                                                    | 0001                  | 0000      | 0011    |  |

| Description:     | W registe is set.                                                     | r is clea             | red. Zero | bit (Z) |  |

| Words:           | 1                                                                     |                       |           |         |  |

| Cycles:          | 1                                                                     |                       |           |         |  |

| Example          | CLRW                                                                  |                       |           |         |  |

|                  | Before In                                                             | struction<br>W =      | 0x5A      |         |  |

|                  |                                                                       | ruction<br>W =<br>Z = | 0x00<br>1 |         |  |

## 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- · Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- · Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

### 11.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

### 11.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

### 11.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

### 11.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

### Standard Operating Conditions (unless otherwise specified)

### Operating temperature

### DC CHARACTERISTICS

$0^{\circ}C \leq TA \leq +70^{\circ}C$  (commercial)  $-40^{\circ}C \le TA \le +85^{\circ}C$  (industrial)  $-40^{\circ}C \le TA \le +125^{\circ}C$  (extended)

Operating voltage VDD range as described in DC spec Section 12.1 and Section 12.2.

| Param | Characteristic                             | Sym   | Min       | Typ† | Max | Units | Conditions                                                    |  |  |

|-------|--------------------------------------------|-------|-----------|------|-----|-------|---------------------------------------------------------------|--|--|

| No.   |                                            |       |           |      |     |       |                                                               |  |  |

|       | Output High Voltage                        |       |           |      |     |       |                                                               |  |  |

| D090  | I/O ports (Note 3)                         | Voн   | Vdd - 0.7 | —    | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>–40°С to +85°С                  |  |  |

| D090A |                                            |       | Vdd - 0.7 | —    | —   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>−40°C to +125°C                 |  |  |

| D092  | OSC2/CLKOUT                                |       | Vdd - 0.7 | -    | —   | V     | ІОн = 1.3 mA, VDD = 4.5V,<br>−40°C to +85°C                   |  |  |

| D092A |                                            |       | Vdd - 0.7 | -    | —   | V     | ІОн = 1.0 mA, VDD = 4.5V,<br>−40°C to +125°C                  |  |  |

|       | Capacitive Loading Specs on<br>Output Pins |       |           |      |     |       |                                                               |  |  |

| D100  | OSC2 pin                                   | Cosc2 | _         | —    | 15  | pF    | In XT and LP modes when external clock is used to drive OSC1. |  |  |

| D101  | All I/O pins                               | Сю    | —         | —    | 50  | pF    |                                                               |  |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

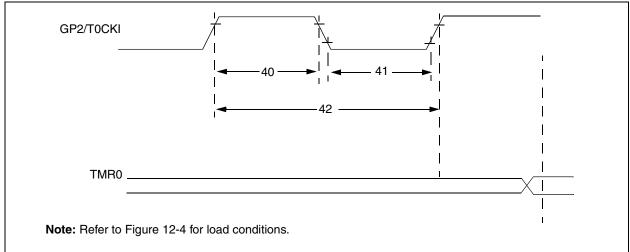

## FIGURE 12-8: TIMER0 CLOCK TIMINGS

## TABLE 12-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       | Characteristic                         |                | Min                                       | Тур† | Max       | Units | Conditions                            |

|--------------|-----------|----------------------------------------|----------------|-------------------------------------------|------|-----------|-------|---------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse Width                 | No Prescaler   | 0.5TCY + 20                               | —    | —         | ns    | Must also meet                        |

|              |           |                                        | With Prescaler | 10                                        | —    | —         | ns    | parameter 42                          |

| 41*          | Tt0L      | T0CKI Low Pulse Width                  | No Prescaler   | 0.5TCY + 20                               | -    | _         | ns    | Must also meet                        |

|              |           |                                        | With Prescaler | 10                                        | -    | _         | ns    | parameter 42                          |

| 42*          | Tt0P      | T0CKI Period                           | No Prescaler   | TCY + 40                                  | —    | _         | ns    |                                       |

|              |           |                                        | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _    | —         | ns    | N = prescale<br>value (2, 4,,<br>256) |

| 48           | TCKE2tmr1 | Delay from external clock of increment | edge to timer  | 2Tosc                                     | _    | 7Tos<br>c |       |                                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## TABLE 12-6: GPIO PULL-UP RESISTOR RANGES

| VDD (Volts) | Temperature (°C) | Min  | Тур  | Мах  | Units |

|-------------|------------------|------|------|------|-------|

|             |                  | GP0/ | /GP1 |      |       |

| 2.5         | -40              | 38K  | 42K  | 63K  | Ω     |

|             | 25               | 42K  | 48K  | 63K  | Ω     |

|             | 85               | 42K  | 49K  | 63K  | Ω     |

|             | 125              | 50K  | 55K  | 63K  | Ω     |

| 5.5         | -40              | 15K  | 17K  | 20K  | Ω     |

|             | 25               | 18K  | 20K  | 23K  | Ω     |

|             | 85               | 19K  | 22K  | 25K  | Ω     |

|             | 125              | 22K  | 24K  | 28K  | Ω     |

|             |                  | GI   | P3   |      |       |

| 2.5         | -40              | 285K | 346K | 417K | Ω     |

|             | 25               | 343K | 414K | 532K | Ω     |

|             | 85               | 368K | 457K | 532K | Ω     |

|             | 125              | 431K | 504K | 593K | Ω     |

| 5.5         | -40              | 247K | 292K | 360K | Ω     |

|             | 25               | 288K | 341K | 437K | Ω     |

|             | 85               | 306K | 371K | 448K | Ω     |

|             | 125              | 351K | 407K | 500K | Ω     |

\* These parameters are characterized but not tested.

### TABLE 12-9: EEPROM MEMORY BUS TIMING REQUIREMENTS - PIC12CE673/674 ONLY.

| AC Characteristics                                                                   | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ , Vcc = 3.0V to 5.5V (commercial)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ , Vcc = 3.0V to 5.5V (industrial)<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ , Vcc = 4.5V to 5.5V (extended) |                      |                     |        |                                                                                                                                     |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operating Voltage VDD range is described in Section 12.1                             |                                                                                                                                                                                                                                                                                                                   |                      |                     |        |                                                                                                                                     |  |  |