Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 5                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 8-SOIJ                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc671-04i-sm |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

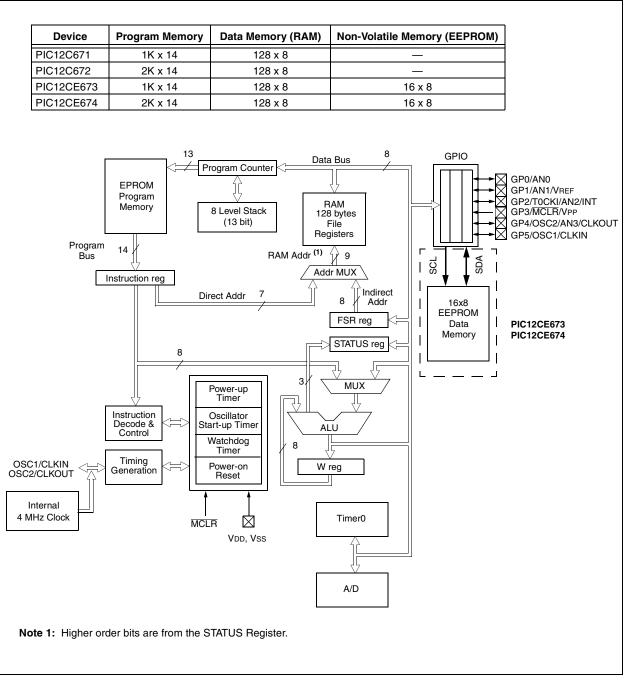

#### FIGURE 3-1: PIC12C67X BLOCK DIAGRAM

#### 4.2.2.2 OPTION REGISTER

The OPTION Register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0 and the weak pull-ups on GPIO. Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

# REGISTER 4-2: OPTION REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1                                                                                                                                                                                                                                                               | R/W-1       | R/W-1       | R/W-1      | R/W-1                  | R/W-1 | R/W-1 |                                                                                       |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------|------------------------|-------|-------|---------------------------------------------------------------------------------------|--|--|

| GPPU     | INTEDG                                                                                                                                                                                                                                                              | T0CS        | T0SE        | PSA        | PS2                    | PS1   | PS0   | R = Readable bit                                                                      |  |  |

| bit7     |                                                                                                                                                                                                                                                                     |             |             |            |                        |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7:   |                                                                                                                                                                                                                                                                     |             |             |            |                        |       |       |                                                                                       |  |  |

| bit 6:   |                                                                                                                                                                                                                                                                     | pt on risi  | ng edge of  |            | KI/AN2/IN<br>KI/AN2/IN |       |       |                                                                                       |  |  |

| bit 5:   | <b>TOCS:</b> TM<br>1 = Transit<br>0 = Interna                                                                                                                                                                                                                       | ion on Gl   | P2/T0CKI/   | AN2/INT    |                        |       |       |                                                                                       |  |  |

| bit 4:   |                                                                                                                                                                                                                                                                     | nent on hi  | gh-to-low   | transition | on GP2/T0<br>on GP2/T0 |       |       |                                                                                       |  |  |

| bit 3:   | PSA: Pres<br>1 = Presca<br>0 = Presca                                                                                                                                                                                                                               | aler is ass | signed to t | he WDT     | module                 |       |       |                                                                                       |  |  |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> :                                                                                                                                                                                                                                              | Prescaler   | Rate Sel    | ect bits   |                        |       |       |                                                                                       |  |  |

|          | Bit Value                                                                                                                                                                                                                                                           | TMR0 R      | ate WD      | Γ Rate     |                        |       |       |                                                                                       |  |  |

|          | 000       1:2       1:1         001       1:4       1:2         010       1:8       1:4         011       1:16       1:8         100       1:32       1:16         101       1:64       1:32         110       1:128       1:64         111       1:256       1:128 |             |             |            |                        |       |       |                                                                                       |  |  |

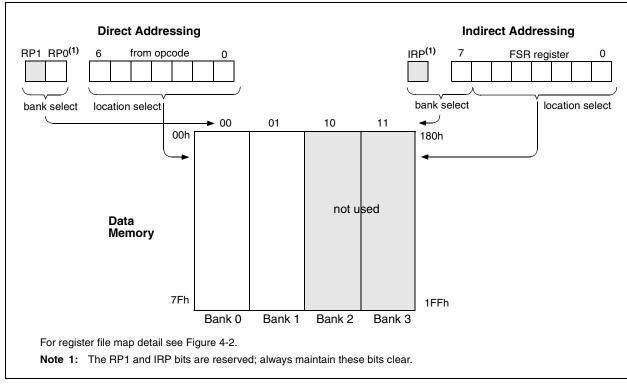

#### 4.5 Indirect Addressing, INDF and FSR Registers

The INDF Register is not a physical register. Addressing the INDF Register will cause indirect addressing.

Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF Register itself indirectly (FSR = '0') will read 00h. Writing to the INDF Register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR Register and the IRP bit (STATUS<7>), as shown in Figure 4-4. However, IRP is not used in the PIC12C67X.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-1.

#### EXAMPLE 4-1: INDIRECT ADDRESSING

|          | movlw | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ;to RAM              |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR,F | ;inc pointer         |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

#### FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

NOTES:

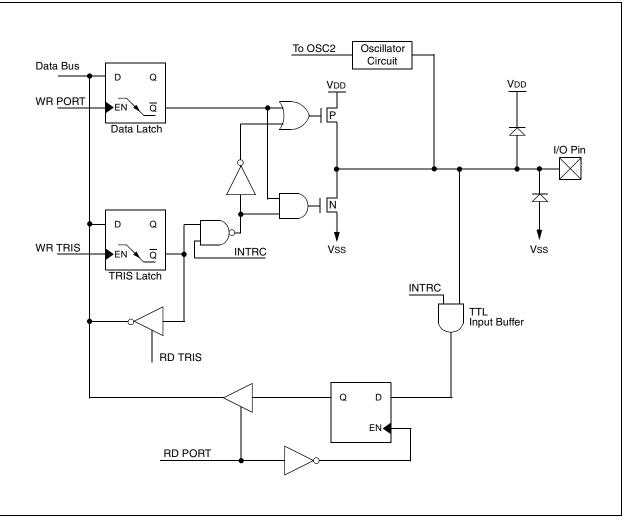

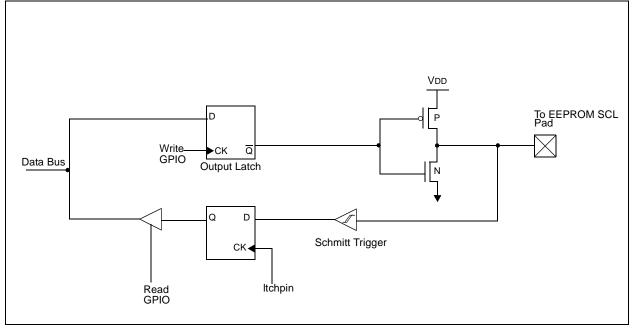

#### FIGURE 5-5: BLOCK DIAGRAM OF GP5/OSC1/CLKIN PIN

#### 6.1.5 ACKNOWLEDGE

The EEPROM, when addressed, will generate an acknowledge after the reception of each byte. The processor must generate an extra clock pulse which is associated with this acknowledge bit.

**Note:** Acknowledge bits are not generated if an internal programming cycle is in progress.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. The processor must signal an end of data to the EEPROM by not generating an acknowledge bit on the last byte that has been clocked out of the EEPROM. In this case, the EEPROM must leave the data line HIGH to enable the processor to generate the STOP condition (Figure 6-4).

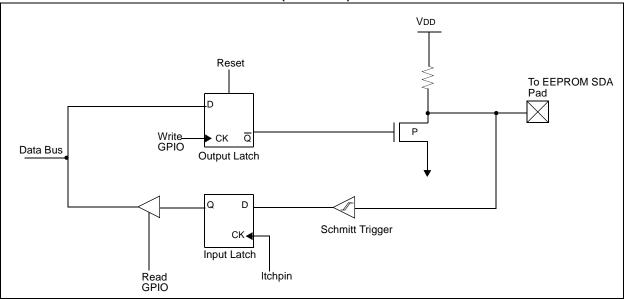

FIGURE 6-1: BLOCK DIAGRAM OF GPIO6 (SDA LINE)

FIGURE 6-2: BLOCK DIAGRAM OF GPIO7 (SCL LINE)

## 8.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-To-Digital (A/D) converter module has four analog inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the GP1/AN1/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 Register, shown in Figure 8-1, controls the operation of the A/D module. The ADCON1 Register, shown in Figure 8-2, configures the functions of the port pins. The port pins can be configured as analog inputs (GP1 can also be a voltage reference) or as digital I/O.

- Note 1: If the port pins are configured as analog inputs (reset condition), reading the port (MOVF GPIO,W) results in reading '0's.

- 2: Changing ADCON1 Register can cause the GPIF and INTF flags to be set in the INTCON Register. These interrupts should be disabled prior to modifying ADCON1.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ADCS1 ADCS0 CHS1 CHS0 GO/DONE ADON R = Readable bit reserved reserved W = Writable bit bit0 bit7 U = Unimplemented bit, read as '0' n = Value at POR reset bit 7-6: ADCS<1:0>: A/D Conversion Clock Select bits 00 = Fosc/201 = Fosc/810 = Fosc/3211 = FRC (clock derived from an RC oscillation) Reserved bit 5: bit 4-3: CHS<1:0>: Analog Channel Select bits 00 = channel 0, (GP0/AN0) 01 = channel 1, (GP1/AN1) 10 = channel 2, (GP2/AN2) 11 = channel 3, (GP4/AN3) GO/DONE: A/D Conversion Status bit bit 2: If ADON = 11 = A/D conversion in progress (setting this bit starts the A/D conversion) 0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete) bit 1: Reserved bit 0: ADON: A/D on bit 1 = A/D converter module is operating 0 = A/D converter module is shut off and consumes no operating current

#### REGISTER 8-1: ADCON0 REGISTER (ADDRESS 1Fh)

#### 8.4 <u>A/D Conversions</u>

;

;

;

Example 8-2 shows how to perform an A/D conversion. The GPIO pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled and the A/D conversion clock is FRC. The conversion is performed on the GP0 channel.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

#### EXAMPLE 8-2: DOING AN A/D CONVERSION

| BSF         | STATUS,   | RP0          | ;  | Select Page 1                                       |

|-------------|-----------|--------------|----|-----------------------------------------------------|

| CLRF        | ADCON1    |              | ;  | Configure A/D inputs                                |

| BSF         | PIE1,     | ADIE         | ;  | Enable A/D interrupts                               |

| BCF         | STATUS,   | RP0          | ;  | Select Page 0                                       |

| MOVLW       | 0xC1      |              | ;  | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF       | ADCON0    |              | ;  |                                                     |

| BCF         | PIR1,     | ADIF         | ;  | Clear A/D interrupt flag bit                        |

| BSF         | INTCON,   | PEIE         | ;  | Enable peripheral interrupts                        |

| BSF         | INTCON,   | GIE          | ;  | Enable all interrupts                               |

|             |           |              |    |                                                     |

| Ensure that | at the re | equired samp | li | ng time for the selected input channel has elapsed. |

Then the conversion may be started.

| BSF | ADCON0, GO | ; Start A/D Conversion                             |

|-----|------------|----------------------------------------------------|

| :   |            | ; The ADIF bit will be set and the GO/DONE bit     |

| :   |            | ; is cleared upon completion of the A/D Conversion |

#### 9.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create a Poweron Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See Table 11-4.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 9.4.4 TIME-OUT SEQUENCE

On power-up, the Time-out Sequence is as follows: first, PWRT time-out is invoked after the POR time delay has expired; then, OST is activated. The total time-out will vary, based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-7, Figure 9-8, and Figure 9-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC12C67X device operating in parallel.

# 9.4.5 POWER CONTROL (PCON)/STATUS REGISTER

The Power Control/Status Register, PCON (address 8Eh), has one bit. See Register 4-6 for register.

Bit1 is POR (Power-on Reset). It is cleared on a Poweron Reset and is unaffected otherwise. The user sets this bit following a Power-on Reset. On subsequent resets, if POR is '0', it will indicate that a Power-on Reset must have occurred.

| <b>Oscillator Configuration</b> | Power            | Wake-up from SLEEP |          |

|---------------------------------|------------------|--------------------|----------|

|                                 | <b>PWRTE</b> = 0 | PWRTE = 1          |          |

| XT, HS, LP                      | 72 ms + 1024Tosc | 1024Tosc           | 1024Tosc |

| INTRC, EXTRC                    | 72 ms            | _                  | —        |

#### TABLE 9-4: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 9-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | то | PD |                                                         |

|-----|----|----|---------------------------------------------------------|

| 0   | 1  | 1  | Power-on Reset                                          |

| 0   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0  | u  | WDT Reset                                               |

| 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

Legend: u = unchanged, x = unknown.

#### 9.8 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input, if enabled, should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on GPIO should be considered.

The  $\overline{\text{MCLR}}$  pin, if enabled, must be at a logic high level (VIHMC).

#### 9.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. GP2/INT interrupt, interrupt GPIO port change or some Peripheral Interrupts.

External MCLR Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device reset. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupt can wake the device from SLEEP:

1. A/D conversion (when A/D clock source is RC).

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 9.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

#### 11.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 11.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

# 12.0 ELECTRICAL SPECIFICATIONS FOR PIC12C67X

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                  | –40° to +125°C                     |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                             | –65°C to +150°C                    |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                    | –0.3V to (VDD + 0.3V)              |

| Voltage on VDD with respect to Vss                                                                              | 0 to +7.0V                         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                    | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                                | 700 mW                             |

| Maximum current out of Vss pin                                                                                  | 200 mA                             |

| Maximum current into VDD pin                                                                                    |                                    |

| Input clamp current, liк (Vi < 0 or Vi > VDD)                                                                   | ± 20 mA                            |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                  |                                    |

| Maximum output current sunk by any I/O pin                                                                      | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                   | 25 mA                              |

| Maximum current sunk by GPIO pins combined                                                                      | 100 mA                             |

| Maximum current sourced by GPIO pins combined                                                                   | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VC) | ЭН) х ІОН} + $\Sigma$ (VOI х ІОL). |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| DC CH4      | ARACTERISTICS                                                                                                       |                                                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |  |                         |            |                                      |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|--|-------------------------|------------|--------------------------------------|--|--|

| Parm<br>No. | Characteristic                                                                                                      | stic Sym Min <sub>Typ</sub> <sup>(1)</sup> Max Units Conditions |                                                      |  |                         |            |                                      |  |  |

|             | LP Oscillator Operating<br>Frequency<br>INTRC/EXTRC Oscillator<br>Operating Frequency                               | Fosc                                                            | 0                                                    |  | 200<br>4 <sup>(6)</sup> | kHz<br>MHz | All temperatures<br>All temperatures |  |  |

|             | XT Oscillator Operating<br>Frequency                                                                                |                                                                 | 0                                                    |  | 4                       | MHz        | All temperatures                     |  |  |

|             | HS Oscillator Operating     0     10     MHz     All temperatures       Frequency     0     10     10     10     10 |                                                                 |                                                      |  |                         |            |                                      |  |  |

I hese parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern, and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD,

$\overline{MCLR} = VDD; WDT$  disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

6: INTRC calibration value is for 4MHz nominal at 5V, 25°C.

# TABLE 12-7:A/D CONVERTER CHARACTERISTICS:<br/>PIC12C671/672-04/PIC12CE673/674-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC12C671/672-10/PIC12CE673/674-10 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC12LC671/672-04/PIC12LCE673/674-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym  | Characteristic                       |                    | Min       | Тур†                   | Max        | Units | Conditions                                                                                                 |

|--------------|------|--------------------------------------|--------------------|-----------|------------------------|------------|-------|------------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                           |                    | _         | _                      | 8-bits     | bit   | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                             |

| A02          | Eabs | Total absolute erro                  | r                  | _         | _                      | < ±1       | LSb   | VREF = VDD = 5.12V,<br>VSS $\leq$ VAIN $\leq$ VREF                                                         |

| A03          | EIL  | Integral linearity er                | ror                | _         | _                      | < ±1       | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$               |

| A04          | Edl  | Differential linearity               | / error            | _         | _                      | < ±1       | LSb   | VREF = VDD = 5.12V,<br>$VSS \le VAIN \le VREF$                                                             |

| A05          | EFS  | Full scale error                     |                    | _         | _                      | < ±1       | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                       |

| A06          | EOFF | Offset error                         |                    | —         | _                      | < ±1       | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                       |

| A10          | _    | Monotonicity                         |                    | _         | guaranteed<br>(Note 3) | _          | —     | $Vss \leq Vain \leq Vref$                                                                                  |

| A20          | VREF | Reference voltage                    |                    | 2.5V      | —                      | VDD + 0.3  | V     |                                                                                                            |

| A25          | VAIN | Analog input voltag                  | je                 | Vss - 0.3 | _                      | VREF + 0.3 | V     |                                                                                                            |

| A30          | ZAIN | Recommended im<br>analog voltage sou |                    | _         | _                      | 10.0       | kΩ    |                                                                                                            |

| A40          | IAD  | A/D conversion                       | PIC12 <b>C</b> 67X | _         | 180                    | —          | μA    | Average current con-                                                                                       |

|              |      | current (VDD) PIC12LC67X             |                    | _         | 90                     | _          | μA    | sumption when A/D is on.<br>(Note 1)                                                                       |

| A50          | IREF | VREF input current (Note 2)          |                    | 10        | _                      | 1000       | μA    | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 8.1. |

|              |      |                                      |                    | —         |                        | 10         | μA    | During A/D Conversion<br>cycle                                                                             |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from GP1 pin or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the Input Voltage, and has no missing codes.

#### TABLE 12-9: EEPROM MEMORY BUS TIMING REQUIREMENTS - PIC12CE673/674 ONLY.

| AC Characteristics                                                                   | AC CharacteristicsStandard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ , Vcc = 3.0V to 5.5V (commerci-<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ , Vcc = 3.0V to 5.5V (industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ , Vcc = 4.5V to 5.5V (extended) |                      |                     |        |                                                                                                                                              |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                      | Operating                                                                                                                                                                                                                                                                                                                        | Voltage V            |                     |        | ibed in Section 12.1                                                                                                                         |  |  |  |

| Parameter                                                                            | Symbol                                                                                                                                                                                                                                                                                                                           | Min                  | Max                 | Units  | Conditions                                                                                                                                   |  |  |  |

| Clock frequency                                                                      | FCLK                                                                                                                                                                                                                                                                                                                             |                      | 100<br>100<br>400   | kHz    | $\begin{array}{l} 4.5 V \leq V cc \leq 5.5 V \text{ (E Temp range)} \\ 3.0 V \leq V cc \leq 4.5 V \\ 4.5 V \leq V cc \leq 5.5 V \end{array}$ |  |  |  |

| Clock high time                                                                      | Тнідн                                                                                                                                                                                                                                                                                                                            | 4000<br>4000<br>600  |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| Clock low time                                                                       | TLOW                                                                                                                                                                                                                                                                                                                             | 4700<br>4700<br>1300 |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| SDA and SCL rise time (Note 1)                                                       | TR                                                                                                                                                                                                                                                                                                                               |                      | 1000<br>1000<br>300 | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| SDA and SCL fall time                                                                | TF                                                                                                                                                                                                                                                                                                                               | —                    | 300                 | ns     | (Note 1)                                                                                                                                     |  |  |  |

| START condition hold time                                                            | THD:STA                                                                                                                                                                                                                                                                                                                          | 4000<br>4000<br>600  |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| START condition setup time                                                           | TSU:STA                                                                                                                                                                                                                                                                                                                          | 4700<br>4700<br>600  |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| Data input hold time                                                                 | THD:DAT                                                                                                                                                                                                                                                                                                                          | 0                    | _                   | ns     | (Note 2)                                                                                                                                     |  |  |  |

| Data input setup time                                                                | TSU:DAT                                                                                                                                                                                                                                                                                                                          | 250<br>250<br>100    |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| STOP condition setup time                                                            | Tsu:sto                                                                                                                                                                                                                                                                                                                          | 4000<br>4000<br>600  |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| Output valid from clock (Note 2)                                                     | ΤΑΑ                                                                                                                                                                                                                                                                                                                              |                      | 3500<br>3500<br>900 | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| Bus free time: Time the bus must<br>be free before a new transmis-<br>sion can start | TBUF                                                                                                                                                                                                                                                                                                                             | 4700<br>4700<br>1300 |                     | ns     | $\begin{array}{l} 4.5V \leq Vcc \leq 5.5V \text{ (E Temp range)} \\ 3.0V \leq Vcc \leq 4.5V \\ 4.5V \leq Vcc \leq 5.5V \end{array}$          |  |  |  |

| Output fall time from VIH<br>minimum to VIL maximum                                  | Tof                                                                                                                                                                                                                                                                                                                              | 20+0.1<br>CB         | 250                 | ns     | (Note 1), CB ≤ 100 pF                                                                                                                        |  |  |  |

| Input filter spike suppression (SDA and SCL pins)                                    | TSP                                                                                                                                                                                                                                                                                                                              | —                    | 50                  | ns     | (Notes 1, 3)                                                                                                                                 |  |  |  |

| Write cycle time                                                                     | Twc                                                                                                                                                                                                                                                                                                                              |                      | 4                   | ms     |                                                                                                                                              |  |  |  |

| Endurance                                                                            |                                                                                                                                                                                                                                                                                                                                  | 1M                   | _                   | cycles | 25°C, Vcc = 5.0V, Block Mode (Note 4)                                                                                                        |  |  |  |

Note 1: Not 100% tested. CB = total capacitance of one bus line in pF.

2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL and avoid unintended generation of START or STOP conditions.

**3:** The combined TSP and VHYS specifications are due to new Schmitt Trigger inputs which provide improved noise spike suppression. This eliminates the need for a TI specification for standard operation.

4: This parameter is not tested but ensured by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be obtained on Microchip's website.

## 14.0 PACKAGING INFORMATION

#### 14.1 Package Marking Information

#### 8-Lead PDIP (300 mil)

#### 8-Lead SOIC (208 mil)

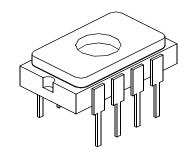

#### 8-Lead Windowed Ceramic Side Brazed (300 mil)

| Legen | d: MMM<br>XXX<br>AA<br>BB<br>C                                                                                                                                                                      | Microchip part number information<br>Customer specific information*<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Facility code of the plant at which wafer is manufactured<br>O = Outside Vendor<br>C = 5" Line<br>S = 6" Line<br>H = 8" Line<br>Mask revision number<br>Assembly code of the plant or country of origin in which<br>part was assembled |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Note: | In the event the full Microchip part number cannot be marked on one line, it we be carried over to the next line thus limiting the number of available character for customer specific information. |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

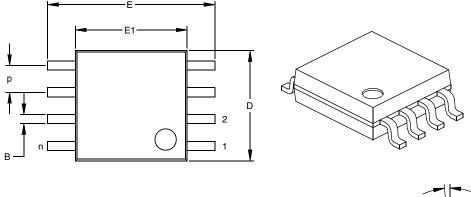

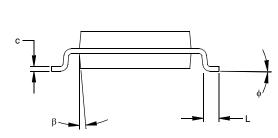

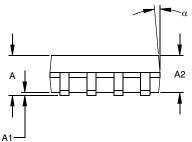

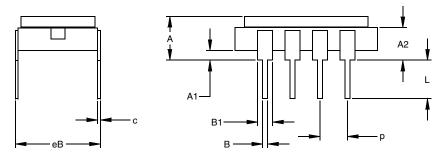

#### 8-Lead Plastic Small Outline (SM) – Medium, 208 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | INCHES* |      |      | MILLIMETERS |      |      |

|--------------------------|----------|---------|------|------|-------------|------|------|

| Dimensio                 | n Limits | MIN     | NOM  | MAX  | MIN         | NOM  | MAX  |

| Number of Pins           | n        |         | 8    |      |             | 8    |      |

| Pitch                    | р        |         | .050 |      |             | 1.27 |      |

| Overall Height           | А        | .070    | .075 | .080 | 1.78        | 1.97 | 2.03 |

| Molded Package Thickness | A2       | .069    | .074 | .078 | 1.75        | 1.88 | 1.98 |

| Standoff                 | A1       | .002    | .005 | .010 | 0.05        | 0.13 | 0.25 |

| Overall Width            | Е        | .300    | .313 | .325 | 7.62        | 7.95 | 8.26 |

| Molded Package Width     | E1       | .201    | .208 | .212 | 5.11        | 5.28 | 5.38 |

| Overall Length           | D        | .202    | .205 | .210 | 5.13        | 5.21 | 5.33 |

| Foot Length              | L        | .020    | .025 | .030 | 0.51        | 0.64 | 0.76 |

| Foot Angle               | ¢        | 0       | 4    | 8    | 0           | 4    | 8    |

| Lead Thickness           | С        | .008    | .009 | .010 | 0.20        | 0.23 | 0.25 |

| Lead Width               | В        | .014    | .017 | .020 | 0.36        | 0.43 | 0.51 |

| Mold Draft Angle Top     | α        | 0       | 12   | 15   | 0           | 12   | 15   |

| Mold Draft Angle Bottom  | β        | 0       | 12   | 15   | 0           | 12   | 15   |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

Drawing No. C04-056

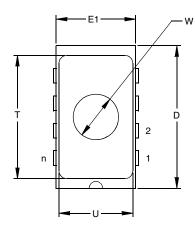

#### 8-Lead Ceramic Side Brazed Dual In-line with Window (JW) - 300 mil

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                              | Units    | INCHES* |      |      | MILLIMETERS |       |       |

|------------------------------|----------|---------|------|------|-------------|-------|-------|

| Dimension                    | I Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins               | n        |         | 8    |      |             | 8     |       |

| Pitch                        | р        |         | .100 |      |             | 2.54  |       |

| Top to Seating Plane         | А        | .145    | .165 | .185 | 3.68        | 4.19  | 4.70  |

| Top of Body to Seating Plane | A2       | .103    | .123 | .143 | 2.62        | 3.12  | 3.63  |

| Standoff                     | A1       | .025    | .035 | .045 | 0.64        | 0.89  | 1.14  |

| Package Width                | E1       | .280    | .290 | .300 | 7.11        | 7.37  | 7.62  |

| Overall Length               | D        | .510    | .520 | .530 | 12.95       | 13.21 | 13.46 |

| Tip to Seating Plane         | L        | .130    | .140 | .150 | 3.30        | 3.56  | 3.81  |

| Lead Thickness               | С        | .008    | .010 | .012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width             | B1       | .050    | .055 | .060 | 1.27        | 1.40  | 1.52  |

| Lower Lead Width             | В        | .016    | .018 | .020 | 0.41        | 0.46  | 0.51  |

| Overall Row Spacing          | eB       | .296    | .310 | .324 | 7.52        | 7.87  | 8.23  |

| Window Diameter              | W        | .161    | .166 | .171 | 4.09        | 4.22  | 4.34  |

| Lid Length                   | Т        | .440    | .450 | .460 | 11.18       | 11.43 | 11.68 |

| Lid Width                    | U        | .260    | .270 | .280 | 6.60        | 6.86  | 7.11  |

\*Controlling Parameter JEDC Equivalent: MS-015 Drawing No. C04-083

#### INDEX

#### **A** A/D

| A/D                                             |    |

|-------------------------------------------------|----|

| Accuracy/Error                                  |    |

| ADCON0 Register                                 |    |

| ADIF bit                                        |    |

| Analog Input Model Block Diagram                |    |

| Analog-to-Digital Converter                     |    |

| Configuring Analog Port Pins                    |    |

| Configuring the Interrupt                       |    |

| Configuring the Module                          |    |

| Connection Considerations                       |    |

| Conversion Clock                                | -  |

| Conversions                                     |    |

| Converter Characteristics                       |    |

| Delays                                          |    |

| Effects of a Reset                              |    |

| Equations                                       |    |

| Flowchart of A/D Operation                      |    |

| GO/DONE bit                                     |    |

| Internal Sampling Switch (Rss) Impedence        |    |

| Operation During Sleep<br>Sampling Requirements |    |

| Sampling Time                                   |    |

| Source Impedence                                |    |

| Time Delays                                     |    |

| Transfer Function                               |    |

| Absolute Maximum Ratings                        |    |

| ADDLW Instruction                               |    |

| ADDWF Instruction                               |    |

| ADIE bit                                        |    |

| ADIF bit                                        |    |

| ADRES Register                                  |    |

| ALU                                             |    |

| ANDLW Instruction                               |    |

| ANDWF Instruction                               |    |

| Application Notes                               |    |

| AN546                                           |    |

| AN556                                           |    |

| Architecture                                    |    |

| Harvard                                         | 7  |

| Overview                                        |    |

| von Neumann                                     | 7  |

| Assembler                                       |    |

| MPASM Assembler                                 |    |

| В                                               |    |

| BCF Instruction                                 | 73 |

| Ber Instruction                                 |    |

| Block Diagrams                                  |    |

| Analog Input Model                              | 48 |

| On-Chip Reset Circuit                           |    |

| Timer0                                          |    |

| Timer0/WDT Prescaler                            |    |

| Watchdog Timer                                  |    |

| BSF Instruction                                 |    |

| BTFSC Instruction                               |    |

| BTFSS Instruction                               | -  |

|                                                 |    |

## С

| C bit 1                                  | 5  |

|------------------------------------------|----|

| CAL0 bit 2                               | 21 |

| CAL1 bit 2                               | 21 |

| CAL2 bit                                 | 21 |

| CAL3 bit                                 | 21 |

| CALFST bit 2                             | 21 |

| CALL Instruction                         | 74 |

| CALSLW bit                               |    |

| Carry bit                                |    |

| Clocking Scheme                          |    |

| CLRF Instruction                         |    |

| CLRW Instruction                         |    |

| CLRWDT Instruction                       |    |

| Code Examples                            | 5  |

| Changing Prescaler (Timer0 to WDT) 4     | 10 |

|                                          |    |

| Changing Prescaler (WDT to Timer0)       |    |

| Indirect Addressing                      |    |

| Code Protection                          |    |

| COMF Instruction                         |    |

| Computed GOTO                            |    |

| Configuration Bits 5                     | 53 |

| D                                        |    |

| DC and AC Characteristics10              | )9 |

| DC bit1                                  |    |

| DC Characteristics                       |    |

| PIC12C671/672, PIC12CE673/674            | 22 |

| PIC12LC671/672, PIC12LCE673/674          |    |

| DECF Instruction                         |    |

| DECFSZ Instruction                       | -  |

| Development Support                      |    |

| Development Support                      |    |

| Digit Carly bit                          |    |

| -                                        | 20 |

| E                                        |    |

| EEPROM Peripheral Operation              | 33 |

| Electrical Characteristics - PIC12C67X 8 |    |

| Errata                                   | 2  |

| External Brown-out Protection Circuit    | 51 |

| External Power-on Reset Circuit6         | 51 |

| F                                        |    |

| Family of Devices                        | 4  |

| Features                                 | 1  |

| FSR Register 13, 14, 2                   |    |

| G                                        |    |

| General Description                      | ~  |

|                                          |    |

| GIE bit                                  |    |

| GOTO Instruction                         |    |

| GPIF bit                                 |    |

| GPIO                                     |    |

| GPIO Register 1                          |    |

| GPPU bit 1                               | 6  |

|                                          |    |