Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

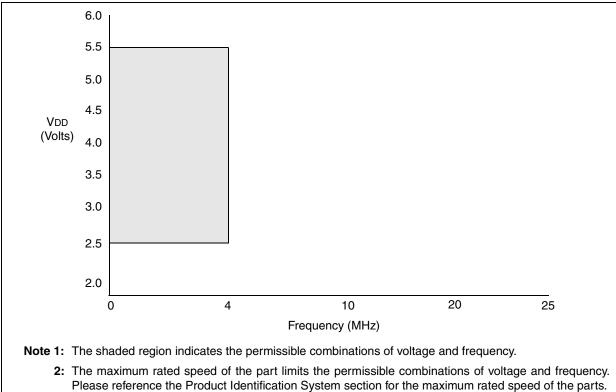

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

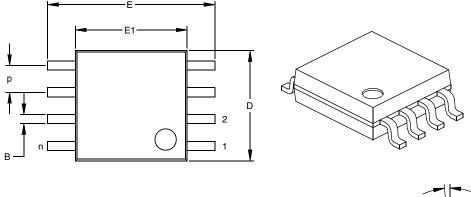

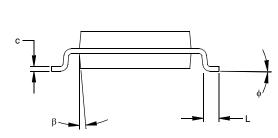

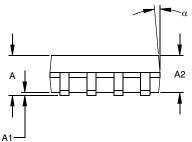

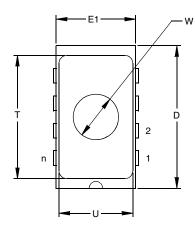

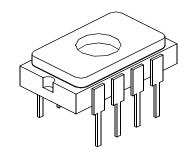

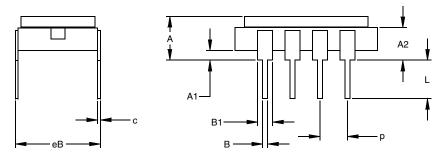

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 8-SOIJ                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc672-04-sm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

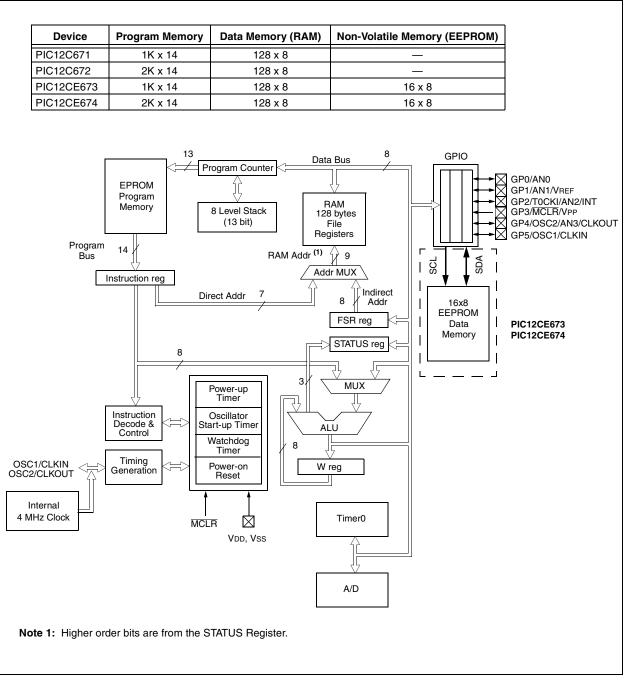

## FIGURE 3-1: PIC12C67X BLOCK DIAGRAM

# FIGURE 4-2: PIC12C67X REGISTER FILE MAP

|                 | WAF                  |                     |                 |

|-----------------|----------------------|---------------------|-----------------|

| File<br>Address | 6                    |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                 | OPTION              | 81h             |

| 02h             | PCL                  | PCL                 | 82h             |

| 02h             | STATUS               | STATUS              | 83h             |

| 03h             | FSR                  | FSR                 | 84h             |

| 0411<br>05h     | GPIO                 | TRIS                | 85h             |

|                 | GFIO                 | INIS                | _               |

| 06h<br>07h      |                      |                     | 86h<br>87h      |

| 07h<br>08h      |                      |                     | 88h             |

|                 |                      |                     |                 |

| 09h             |                      |                     | 89h             |

| 0Ah             | PCLATH               | PCLATH              | 8Ah             |

| 0Bh             | INTCON               | INTCON              | 8Bh             |

| 0Ch             | PIR1                 | PIE1                | 8Ch             |

| 0Dh             |                      |                     | 8Dh             |

| 0Eh             |                      | PCON                | 8Eh             |

| 0Fh             |                      | OSCCAL              | 8Fh             |

| 10h             |                      |                     | 90h             |

| 11h             |                      |                     | 91h             |

| 12h             |                      |                     | 92h             |

| 13h             |                      |                     | 93h             |

| 14h             |                      |                     | 94h             |

| 15h             |                      |                     | 95h             |

| 16h             |                      |                     | 96h             |

| 17h             |                      |                     | 97h             |

| 18h             |                      |                     | 98h             |

| 19h             |                      |                     | 99h             |

| 1Ah             |                      |                     | 9Ah             |

| 1Bh             |                      |                     | 9Bh             |

| 1Ch             |                      |                     | 9Ch             |

| 1Dh             |                      |                     | 9Dh             |

| 1Eh             | ADRES                |                     | 9Eh             |

| 1Fh             | ADCON0               | ADCON1              | 9Fh             |

| 20h             |                      |                     | A0h             |

| 2011            |                      | General             | AUII            |

|                 |                      | Purpose             |                 |

|                 | General              | Register            | BFh             |

|                 | Purpose              |                     | C0h             |

|                 | Register             |                     |                 |

|                 |                      |                     | EFh             |

| 70h             |                      | Mapped              | F0h             |

|                 |                      | in Bank 0           |                 |

| 7Fh             | Bank 0               | Bank 1              | _ FFh           |

|                 | Banko                | Dunki               |                 |

|                 | Unimplemented dat    | ta memory locatio   | ns, read        |

|                 | as '0'.              |                     |                 |

| Note 1:         | Not a physical regis | ster.               |                 |

|                 |                      |                     |                 |

## 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM.

The Special Function Registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

## 4.2.2.2 OPTION REGISTER

The OPTION Register is a readable and writable register, which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0 and the weak pull-ups on GPIO. Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

# REGISTER 4-2: OPTION REGISTER (ADDRESS 81h)

| R/W-1    | R/W-1                                                | R/W-1                                                                                                 | R/W-1                 | R/W-1      | R/W-1                  | R/W-1 | R/W-1 |                  |

|----------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------|------------|------------------------|-------|-------|------------------|

| GPPU     | INTEDG                                               | T0CS                                                                                                  | T0SE                  | PSA        | PS2                    | PS1   | PS0   | R = Readable bit |

| bit7     |                                                      | bit0<br>bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |                       |            |                        |       |       |                  |

| bit 7:   | <b>GPPU:</b> We 1 = Weak 0 = Weak                    | pull-ups o                                                                                            | disabled              | 3P0, GP1,  | GP3)                   |       |       |                  |

| bit 6:   |                                                      | pt on risi                                                                                            | ng edge of            |            | KI/AN2/IN<br>KI/AN2/IN |       |       |                  |

| bit 5:   | <b>TOCS:</b> TM<br>1 = Transit<br>0 = Interna        | ion on Gl                                                                                             | P2/T0CKI/             | AN2/INT    |                        |       |       |                  |

| bit 4:   |                                                      | nent on hi                                                                                            | gh-to-low             | transition | on GP2/T0<br>on GP2/T0 |       |       |                  |

| bit 3:   | PSA: Pres<br>1 = Presca<br>0 = Presca                | aler is ass                                                                                           | signed to t           | he WDT     | module                 |       |       |                  |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> :                               | Prescaler                                                                                             | Rate Sel              | ect bits   |                        |       |       |                  |

|          | Bit Value                                            | TMR0 R                                                                                                | ate WD                | Γ Rate     |                        |       |       |                  |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 12<br>1 : 25                             | 2 1:<br>4 1:<br>28 1: | 2<br>4     |                        |       |       |                  |

## 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 Register overflow, GPIO port change and external GP2/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

## REGISTER 4-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                 | R/W-0       | R/W-0      | R/W-0                    | R/W-0 | R/W-x |                        |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|--------------------------|-------|-------|------------------------|--|

| GIE<br>bit7 | PEIE                                                                                                                                                                                                                                                                               | PEIE     TOIE     INTE     GPIE     TOIF     INTF     GPIF     R     = Readable bit       bit0     W     Writable bit     U     U     Unimplemented bit, read as '0'       - n     Value at POR reset |             |            |                          |       |       |                        |  |

| bit 7:      | <b>GIE:</b> Glob<br>1 = Enabl<br>0 = Disab                                                                                                                                                                                                                                         | es all un-r                                                                                                                                                                                           | nasked in   |            |                          |       |       |                        |  |

| bit 6:      | 1 = Enabl                                                                                                                                                                                                                                                                          | PEIE: Peripheral Interrupt Enable bit<br>1 = Enables all un-masked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                    |             |            |                          |       |       |                        |  |

| bit 5:      | 1 = Enabl                                                                                                                                                                                                                                                                          | <b>FOIE:</b> TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>2 = Disables the TMR0 interrupt                                                                                  |             |            |                          |       |       |                        |  |

| bit 4:      |                                                                                                                                                                                                                                                                                    | es the ext                                                                                                                                                                                            | ernal inter | rupt on GI | P2/INT/T00<br>P2/INT/T00 |       |       |                        |  |

| bit 3:      | <b>GPIE:</b> GPIO Interrupt on Change Enable bit<br>1 = Enables the GPIO Interrupt on Change<br>0 = Disables the GPIO Interrupt on Change                                                                                                                                          |                                                                                                                                                                                                       |             |            |                          |       |       |                        |  |

| bit 2:      | <b>TOIF:</b> TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                                                              |                                                                                                                                                                                                       |             |            |                          |       |       |                        |  |

| bit 1:      |                                                                                                                                                                                                                                                                                    | xternal int                                                                                                                                                                                           | errupt on   | GP2/INT/1  |                          |       |       | e cleared in software) |  |

| bit 0:      | <ul> <li>0 = The external interrupt on GP2/INT/T0CKI/AN2 pin did not occur</li> <li>GPIF: GPIO Interrupt on Change Flag bit</li> <li>1 = GP0, GP1 or GP3 pins changed state (must be cleared in software)</li> <li>0 = Neither GP0, GP1 nor GP3 pins have changed state</li> </ul> |                                                                                                                                                                                                       |             |            |                          |       |       |                        |  |

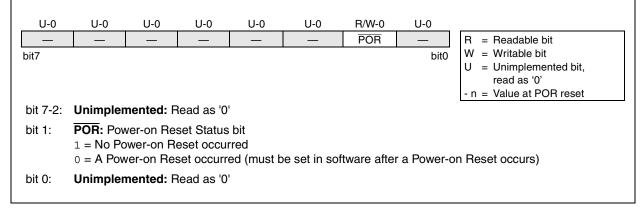

### 4.2.2.6 PCON REGISTER

The Power Control (PCON) Register contains a flag bit to allow differentiation between a Power-on Reset (POR), an external MCLR Reset and a WDT Reset.

## REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

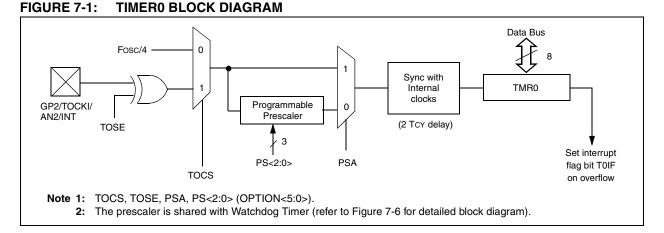

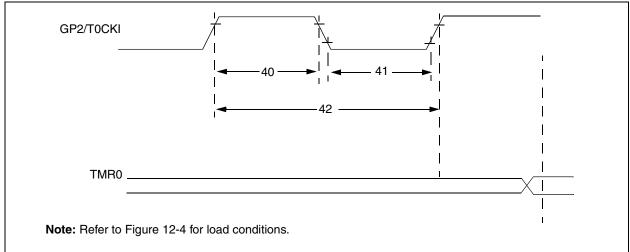

## 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

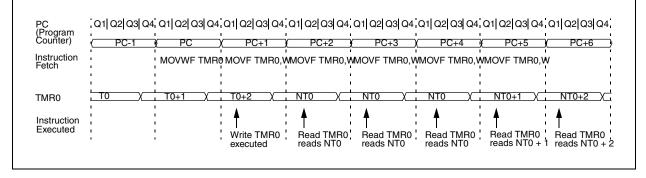

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/TOCKI. The incrementing edge is determined by the bit TOSE

(OPTION<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

## 7.1 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

## TABLE 8-2: SUMMARY OF A/D REGISTERS

| Address | Name                  | Bit 7              | Bit 6              | Bit 5    | Bit 4 | Bit 3 | Bit 2   | Bit 1    | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|-----------------------|--------------------|--------------------|----------|-------|-------|---------|----------|-------|-------------------------------|---------------------------------|

| 0Bh/8Bh | INTCON <sup>(1)</sup> | GIE                | PEIE               | TOIE     | INTE  | GPIE  | T0IF    | INTF     | GPIF  | x000 000x                     | 0000 000u                       |

| 0Ch     | PIR1                  | —                  | ADIF               | _        | —     | —     | -       | —        | —     | -0                            | -0                              |

| 8Ch     | PIE1                  | —                  | ADIE               | —        | _     | _     | _       | —        | —     | -0                            | -0                              |

| 1Eh     | ADRES                 | A/D Res            | sult Regist        | er       |       |       |         |          |       | xxxx xxxx                     | uuuu uuuu                       |

| 1Fh     | ADCON0                | ADCS1              | ADCS0              | reserved | CHS1  | CHS0  | GO/DONE | reserved | ADON  | 0000 0000                     | 0000 0000                       |

| 9Fh     | ADCON1                | _                  | _                  | _        |       | -     | PCFG2   | PCFG1    | PCFG0 | 000                           | 000                             |

| 05h     | GPIO                  | SCL <sup>(2)</sup> | SDA <sup>(2)</sup> | GP5      | GP4   | GP3   | GP2     | GP1      | GP0   | 11xx xxxx                     | 11uu uuuu                       |

| 85h     | TRIS                  | _                  | _                  | TRIS5    | TRIS4 | TRIS3 | TRIS2   | TRIS1    | TRIS0 | 11 1111                       | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers can be addressed from either bank.

2: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

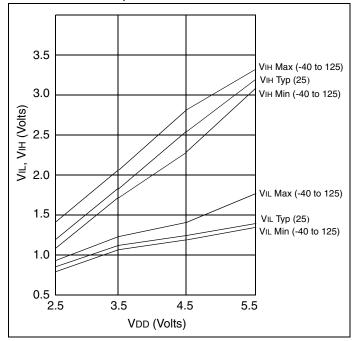

## 9.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at  $V_{DD} = 5V$  and  $25^{\circ}$ C. See Section 13.0 for information on variation over voltage and temperature.

In addition, a calibration instruction is programmed into the last address of the program memory which contains the calibration value for the internal RC oscillator. This value is programmed as a RETLW XX instruction where XX is the calibration value. In order to retrieve the calibration value, issue a CALL YY instruction where YY is the last location in program memory (03FFh for the PIC12C671 and the PIC12CE673, 07FFh for the PIC12C672 and the PIC12CE674). Control will be returned to the user's program with the calibration value loaded into the W register. The program should then perform a MOVWF OSCCAL instruction to load the value into the internal RC oscillator trim register.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency. Bits <7:4>, CAL<3:0> are used for fine calibration, while bit 3, CALFST, and bit 2, CALSLW, are used for more coarse adjustment. Adjusting CAL<3:0> from 0000 to 1111 yields a higher clock speed. Set CALFST = 1 for greater increase in frequency or set CALSLW = 1 for greater decrease in frequency. Note that bits 1 and 0 of OSCCAL are unimplemented and should be written as 0 when modifying OSCCAL for compatibility with future devices.

| Note: | Please note that erasing the device will       |

|-------|------------------------------------------------|

|       | also erase the pre-programmed internal         |

|       | calibration value for the internal oscillator. |

|       | The calibration value must be saved prior      |

|       | to erasing the part.                           |

## 9.2.6 CLKOUT

The PIC12C67X can be configured to provide a clock out signal (CLKOUT) on pin 3 when the configuration word address (2007h) is programmed with Fosc2, Fosc1, and Fosc0, equal to 101 for INTRC or 111 for EXTRC. The oscillator frequency, divided by 4, can be used for test purposes or to synchronize other logic.

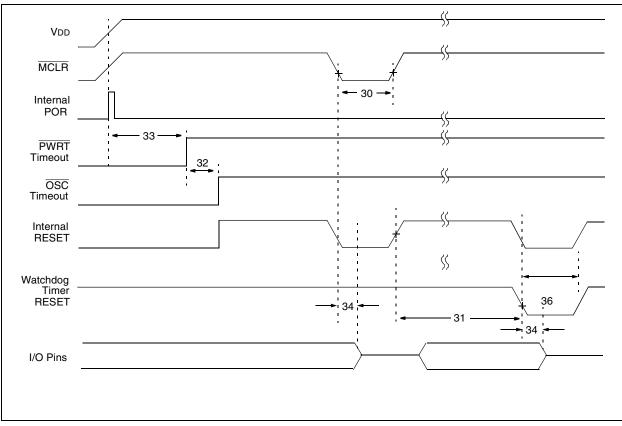

## 9.3 <u>Reset</u>

The PIC12C67X differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), MCLR Reset, WDT Reset, and MCLR Reset during SLEEP. They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations, as indicated in Table 9-5. These bits are used in software to determine the nature of the reset. See Table 9-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 9-6.

The PIC12C67X has a MCLR noise filter in the MCLR reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

When MCLR is asserted, the state of the OSC1/CLKIN and CLKOUT/OSC2 pins are as follows:

# TABLE 9-3:CLKIN/CLKOUT PIN STATESWHEN MCLR ASSERTED

| Oscillator Mode          | OSC1/CLKIN Pin                                                | OSC2/CLKout Pin               |

|--------------------------|---------------------------------------------------------------|-------------------------------|

| EXTRC, CLKOUT<br>on OSC2 | OSC1 pin is<br>tristated and<br>driven by external<br>circuit | OSC2 pin is driven<br>low     |

| EXTRC, OSC2 is<br>I/O    | OSC1 pin is<br>tristated and<br>driven by external<br>circuit | OSC2 pin is<br>tristate input |

| INTRC, CLKOUT<br>on OSC2 | OSC1 pin is<br>tristate input                                 | OSC2 pin is driven<br>low     |

| INTRC, OSC2 is<br>I/O    | OSC1 pin is<br>tristate input                                 | OSC2 pin is tristate input    |

## TABLE 9-6: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | u-               |

| WDT Reset during normal operation  | 000h                  | 0000 uuuu          | u-               |

| WDT Wake-up from SLEEP             | PC + 1                | uuu0 0uuu          | u-               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-               |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

## TABLE 9-7: INITIALIZATION CON\DITIONS FOR ALL REGISTERS

| Power-on Reset | MCLR Resets<br>WDT Reset                                                                                                                                                                                                                                                                       | Wake-up via<br>WDT or Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xxxx xxxx      | <u>uuuu</u> uuuu                                                                                                                                                                                                                                                                               | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| xxxx xxxx      | นนนน นนนน                                                                                                                                                                                                                                                                                      | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                      | PC + 1 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                                                                                                                                                                                                                                       | uuuq quuu <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| xxxx xxxx      | นนนน นนนน                                                                                                                                                                                                                                                                                      | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11xx xxxx      | 11uu uuuu                                                                                                                                                                                                                                                                                      | 11uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| xx xxxx        | uu uuuu                                                                                                                                                                                                                                                                                        | uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0 0000         | 0 0000                                                                                                                                                                                                                                                                                         | u uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0000 000x      | 0000 000u                                                                                                                                                                                                                                                                                      | uuuu uqqq <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -0             | -0                                                                                                                                                                                                                                                                                             | - <u>q</u> (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0000 0000      | 0000 0000                                                                                                                                                                                                                                                                                      | uuuu uquu <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1111 1111      | 1111 1111                                                                                                                                                                                                                                                                                      | սսսս սսսս                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11 1111        | 11 1111                                                                                                                                                                                                                                                                                        | uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -0             | -0                                                                                                                                                                                                                                                                                             | -u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0-             | u-                                                                                                                                                                                                                                                                                             | u-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0111 00        | uuuu uu                                                                                                                                                                                                                                                                                        | uuuu uu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 000            | 000                                                                                                                                                                                                                                                                                            | uuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | xxxx xxxx         0000 0000         xxxx xxxx         0000 0000         0001 1xxx         xxxx xxxx         11xx xxx         11xx xxxx        xx xxxx        xx xxxx        0 0000         0000 000x         -0         0000 0000         1111 1111        11 1111         -0         0.011 00 | WDT Reset           xxxx xxxx         uuuu uuuu           0000 0000         0000 0000           xxxx xxxx         uuuu uuuu           0000 0000         0000 0000           xxxx xxxx         uuuu uuuu           0001 1xxx         000q quuu <sup>(3)</sup> xxxx xxxx         uuuu uuuu           11xx xxxx         11uu uuuu           11xx xxxx         11uu uuuu          xx xxxx        uu uuuu          xx xxxx        uu uuuu          0 0000        0 0000           0000 000x         0000 000u           -0         -0           0000 0000         0000 0000           1111 111         1111 111          11 111        11 1111           -0            -0            -0            -0            -0            -0            -0            -0            -0            -0            -0            0111 00         uuuu uu |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: One or more bits in INTCON and PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 9-5 for reset value for specific condition.

4: If wake-up was due to A/D completing then bit 6 = 1, all other interrupts generating a wake-up will cause bit 6 = u.

5: If wake-up was due to A/D completing then bit 3 = 0, all other interrupts generating a wake-up will cause bit 3 = u.

# **PIC12C67X**

| NOP              | No Oper   | ation  |      |      |

|------------------|-----------|--------|------|------|

| Syntax:          | [ label ] | NOP    |      |      |

| Operands:        | None      |        |      |      |

| Operation:       | No opera  | ation  |      |      |

| Status Affected: | None      |        |      |      |

| Encoding:        | 0 0       | 0000   | 0xx0 | 0000 |

| Description:     | No opera  | ation. |      |      |

| Words:           | 1         |        |      |      |

| Cycles:          | 1         |        |      |      |

| Example          | NOP       |        |      |      |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RETFIE                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} \text{TOS} \rightarrow \text{PC}, \\ 1 \rightarrow \text{GIE} \end{array}$                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                   |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                      |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global Inter-<br>rupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                      |

| Cycles:          | 2                                                                                                                                                                                                                      |

| Example          | RETFIE                                                                                                                                                                                                                 |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                 |

| OPTION           | Load Option Register                                                                                                                                                                                                                               |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] OPTION                                                                                                                                                                                                                                   |

| Operands:        | None                                                                                                                                                                                                                                               |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                               |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                                                                                  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a read-<br>able/writable register, the user can<br>directly address it. |

| Words:           | 1                                                                                                                                                                                                                                                  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |

| Example          |                                                                                                                                                                                                                                                    |

|                  |                                                                                                                                                                                                                                                    |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |  |  |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two cycle instruction. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Example          | CALL TABLE;W contains<br>table<br>:offset value                                                                                                                                     |  |  |  |  |  |  |  |

| TABLE            | • ;W now has table value                                                                                                                                                            |  |  |  |  |  |  |  |

|                  | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |  |  |  |  |  |  |  |

|                  | RETLW kn ;End of table                                                                                                                                                              |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                      |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = value of k8                                                                                                                                                |  |  |  |  |  |  |  |

| RETURN             | N Return from Subroutine RRF                                                                                          | RRF              | Rotate Right f through Carry                                                                                                                                                                  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:            | [label] RETURN                                                                                                        | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                      |  |  |  |  |

| Operands:          | None                                                                                                                  | Operands:        | $0 \le f \le 127$                                                                                                                                                                             |  |  |  |  |

| Operation:         | $TOS \rightarrow PC$                                                                                                  | Operation:       | d ∈ [0,1]                                                                                                                                                                                     |  |  |  |  |

| Status Affected:   | None                                                                                                                  |                  | See description below                                                                                                                                                                         |  |  |  |  |

| Encoding:          | 00 0000 0000 1000                                                                                                     | Status Affected: | C                                                                                                                                                                                             |  |  |  |  |

| Description:       | Return from subroutine. The stack                                                                                     | Encoding:        | 00 1100 dfff ffff                                                                                                                                                                             |  |  |  |  |

|                    | is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two cycle<br>instruction. | Description:     | The contents of register 'f' are<br>rotated one bit to the right throug<br>the Carry Flag. If 'd' is 0, the resu<br>is placed in the W register. If 'd'<br>1, the result is placed back in re |  |  |  |  |

| Words:             | 1                                                                                                                     | ister 'f'.       |                                                                                                                                                                                               |  |  |  |  |

| Cycles:<br>Example | 2<br>RETURN                                                                                                           |                  | C Register f                                                                                                                                                                                  |  |  |  |  |

|                    | After Interrupt                                                                                                       | Words:           | 1                                                                                                                                                                                             |  |  |  |  |

|                    | PC = TOS                                                                                                              | Cycles:          | 1                                                                                                                                                                                             |  |  |  |  |

|                    |                                                                                                                       | Example          | rrf <b>REG1</b> ,<br>0                                                                                                                                                                        |  |  |  |  |

|                    |                                                                                                                       |                  | Before Instruction                                                                                                                                                                            |  |  |  |  |

|                    |                                                                                                                       |                  | REG1 = 1110 0110<br>C = 0                                                                                                                                                                     |  |  |  |  |

|                    |                                                                                                                       |                  | After Instruction<br>REG1 = 1110 0110                                                                                                                                                         |  |  |  |  |

|                    |                                                                                                                       |                  | W = 0111 0011                                                                                                                                                                                 |  |  |  |  |

|                    |                                                                                                                       |                  | <b>C</b> = 0                                                                                                                                                                                  |  |  |  |  |

| RLF              | Rotate Left f through Carry                                                                  | SLEEP            |                                                                                                                                                                                                                                    |  |  |

|------------------|----------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                     | Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                    |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                           | Operands:        | None                                                                                                                                                                                                                               |  |  |

| Operation:       | See description below                                                                        | Operation:       | $00h \rightarrow WDT,$                                                                                                                                                                                                             |  |  |

| Status Affected: | С                                                                                            |                  | $0 \rightarrow \underline{WDT}$ prescaler,<br>1 $\rightarrow \underline{TO}$ ,                                                                                                                                                     |  |  |

| Encoding:        | 00 1101 dfff ffff                                                                            |                  | $0 \rightarrow PD$                                                                                                                                                                                                                 |  |  |

| Description:     | The contents of register 'f' are                                                             | Status Affected: |                                                                                                                                                                                                                                    |  |  |

|                  | rotated one bit to the left through the Carry Flag. If 'd' is 0, the result                  | Encoding:        | 00 0000 0110 0011                                                                                                                                                                                                                  |  |  |

|                  | is placed in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. | Description:     | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |  |  |

| Words:           | 1                                                                                            | Words:           | 1                                                                                                                                                                                                                                  |  |  |

| Cycles:          | 1                                                                                            | Cycles:          | 1                                                                                                                                                                                                                                  |  |  |

| Example          | RLF REG1,0                                                                                   | Example:         | SLEEP                                                                                                                                                                                                                              |  |  |

|                  | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                         |                  |                                                                                                                                                                                                                                    |  |  |

## 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- · Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- · Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

#### 11.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

#### 11.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

### 11.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

## 11.4 MPLINK/MPLIB Linker/Librarian