# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 5                                                                            |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-VDFN Exposed Pad                                                           |

| Supplier Device Package    | 8-DFN-S (6x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12lc672t-04i-mf |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | General Description                              |

|-------|--------------------------------------------------|

| 2.0   | PIC12C67X Device Varieties                       |

| 3.0   | Architectural Overview                           |

|       | Memory Organization                              |

| 5.0   | I/O Port                                         |

| 6.0   | EEPROM Peripheral Operation                      |

| 7.0   | Timer0 Module                                    |

| 8.0   | Analog-to-Digital Converter (A/D) Module         |

| 9.0   | Special Features of the CPU                      |

|       | Instruction Set Summary                          |

| 11.0  | Development Support                              |

| 12.0  | Electrical Specifications                        |

| 13.0  | DC and AC Characteristics                        |

| 14.0  | Packaging Information 115                        |

| Appe  | ndix A:Compatibility                             |

| Appe  | ndix B:Code for Accessing EEPROM Data Memory 119 |

| Index |                                                  |

| On-Li | ne Support                                       |

| Read  | ne Support                                       |

| PIC12 | 2C67X Product Identification System              |

#### To Our Valued Customers

#### **Most Current Data Sheet**

To automatically obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

# FIGURE 4-2: PIC12C67X REGISTER FILE MAP

|                 | WAF                  |                     |                 |

|-----------------|----------------------|---------------------|-----------------|

| File<br>Address | 6                    |                     | File<br>Address |

| 00h             | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                 | OPTION              | 81h             |

| 02h             | PCL                  | PCL                 | 82h             |

| 02h             | STATUS               | STATUS              | 83h             |

| 03h             | FSR                  | FSR                 | 84h             |

| 0411<br>05h     | GPIO                 | TRIS                | 85h             |

|                 | GFIO                 | INIS                | _               |

| 06h<br>07h      |                      |                     | 86h<br>87h      |

| 07h<br>08h      |                      |                     | 88h             |

|                 |                      |                     |                 |

| 09h             |                      |                     | 89h             |

| 0Ah             | PCLATH               | PCLATH              | 8Ah             |

| 0Bh             | INTCON               | INTCON              | 8Bh             |

| 0Ch             | PIR1                 | PIE1                | 8Ch             |

| 0Dh             |                      |                     | 8Dh             |

| 0Eh             |                      | PCON                | 8Eh             |

| 0Fh             |                      | OSCCAL              | 8Fh             |

| 10h             |                      |                     | 90h             |

| 11h             |                      |                     | 91h             |

| 12h             |                      |                     | 92h             |

| 13h             |                      |                     | 93h             |

| 14h             |                      |                     | 94h             |

| 15h             |                      |                     | 95h             |

| 16h             |                      |                     | 96h             |

| 17h             |                      |                     | 97h             |

| 18h             |                      |                     | 98h             |

| 19h             |                      |                     | 99h             |

| 1Ah             |                      |                     | 9Ah             |

| 1Bh             |                      |                     | 9Bh             |

| 1Ch             |                      |                     | 9Ch             |

| 1Dh             |                      |                     | 9Dh             |

| 1Eh             | ADRES                |                     | 9Eh             |

| 1Fh             | ADCON0               | ADCON1              | 9Fh             |

| 20h             |                      |                     | A0h             |

| 2011            |                      | General             | AUII            |

|                 |                      | Purpose             |                 |

|                 | General              | Register            | BFh             |

|                 | Purpose              |                     | C0h             |

|                 | Register             |                     |                 |

|                 |                      |                     | EFh             |

| 70h             |                      | Mapped              | F0h             |

|                 |                      | in Bank 0           |                 |

| 7Fh             | Bank 0               | Bank 1              | _ FFh           |

|                 | Banko                | Dunki               |                 |

|                 | Unimplemented dat    | ta memory locatio   | ns, read        |

|                 | as '0'.              |                     |                 |

| Note 1:         | Not a physical regis | ster.               |                 |

|                 |                      |                     |                 |

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM.

The Special Function Registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

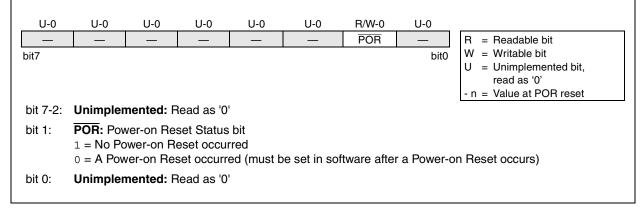

#### 4.2.2.6 PCON REGISTER

The Power Control (PCON) Register contains a flag bit to allow differentiation between a Power-on Reset (POR), an external MCLR Reset and a WDT Reset.

#### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

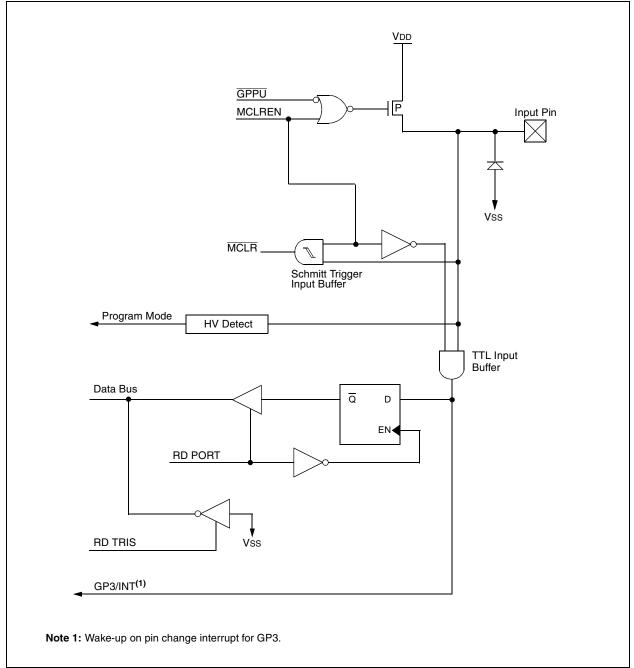

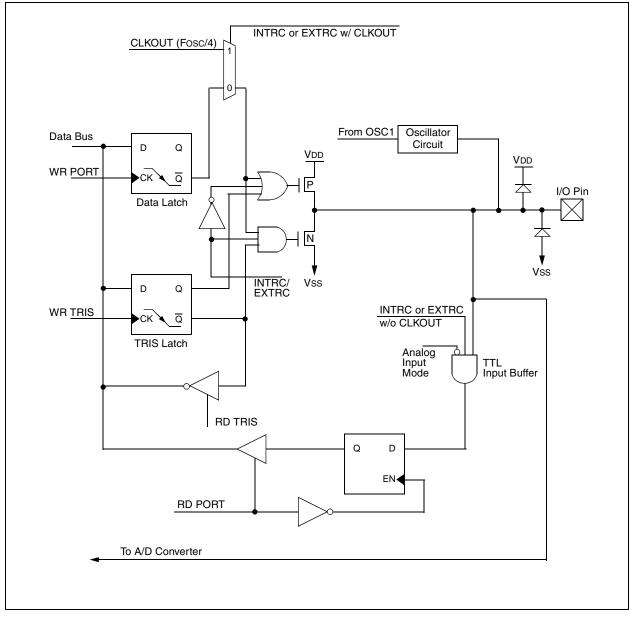

FIGURE 5-4: BLOCK DIAGRAM OF GP4/OSC2/AN3/CLKOUT PIN

NOTES:

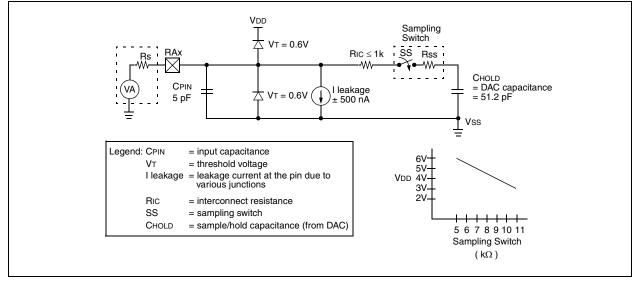

### 8.1 A/D Sampling Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 8-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 8-2. The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 8-1 may be used. This equation assumes that 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

# EQUATION 8-1: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/512)) \bullet (1 - e^{(-Tc/CHOLD(Ric + Rss + Rs))})$ or

$Tc = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 8-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

Rs = 10 kΩ

1/2 LSb error

$\text{VDD}=\text{5V}\rightarrow\text{Rss}=\text{7 k}\Omega$

Temp (system max.) = 50°C

VHOLD = 0 @ t = 0

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0 TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### EXAMPLE 8-1: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

TACQ = Internal Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

TACQ =  $5 \,\mu s + Tc + [(Temp - 25^{\circ}C)(0.05 \,\mu s/^{\circ}C)]$

Tc = -CHOLD (Ric + Rss + Rs) ln(1/512)-51.2 pF (1 kΩ + 7 kΩ + 10 kΩ) ln(0.0020) -51.2 pF (18 kΩ) ln(0.0020) -0.921 µs (-6.2146) 5.724 µs TACQ = 5 µs + 5.724 µs + [(50°C - 25°C)(0.05 µs/°C)]

10.724 μs + 1.25 μs

11.974 μs

### FIGURE 8-2: ANALOG INPUT MODEL

# 8.5 A/D Operation During Sleep

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS<1:0> = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared, and the result loaded into the ADRES Register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS<1:0> = 11). To perform an A/D conversion in SLEEP, the GO/DONE bit must be set, followed by the SLEEP instruction.

## 8.6 <u>A/D Accuracy/Error</u>

The overall accuracy of the A/D is less than  $\pm$  1 LSb for VDD = 5V  $\pm$  10% and the analog VREF = VDD. This overall accuracy includes offset error, full scale error, and integral error. The A/D converter is monotonic over the full VDD range. The resolution and accuracy may be less when either the analog reference (VDD) is less than 5.0V or when the analog reference (VREF) is less than VDD.

The maximum pin leakage current is specified in the Device Data Sheet electrical specification, parameter #D060.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from Tosc, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

### 8.7 Effects of a Reset

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted. The value that is in the ADRES register is not modified for a Reset. The ADRES register will contain unknown data after a Power-on Reset.

#### 8.8 Connection Considerations

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

| Note: | For the PIC12C67X, care must be taken       |

|-------|---------------------------------------------|

|       | when using the GP4 pin in A/D conver-       |

|       | sions due to its proximity to the OSC1 pin. |

An external RC filter is sometimes added for antialiasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

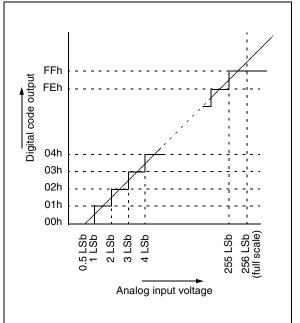

#### 8.9 <u>Transfer Function</u>

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is 1 LSb (or Analog VREF / 256) (Figure 8-3).

#### FIGURE 8-3: A/D TRANSFER FUNCTION

#### 9.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 9.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create a Poweron Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

#### 9.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See Table 11-4.

#### 9.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 9.4.4 TIME-OUT SEQUENCE

On power-up, the Time-out Sequence is as follows: first, PWRT time-out is invoked after the POR time delay has expired; then, OST is activated. The total time-out will vary, based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-7, Figure 9-8, and Figure 9-9 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 9-9). This is useful for testing purposes or to synchronize more than one PIC12C67X device operating in parallel.

# 9.4.5 POWER CONTROL (PCON)/STATUS REGISTER

The Power Control/Status Register, PCON (address 8Eh), has one bit. See Register 4-6 for register.

Bit1 is POR (Power-on Reset). It is cleared on a Poweron Reset and is unaffected otherwise. The user sets this bit following a Power-on Reset. On subsequent resets, if POR is '0', it will indicate that a Power-on Reset must have occurred.

| <b>Oscillator Configuration</b> | Power            | Wake-up from SLEEP |          |

|---------------------------------|------------------|--------------------|----------|

|                                 | <b>PWRTE</b> = 0 | PWRTE = 1          |          |

| XT, HS, LP                      | 72 ms + 1024Tosc | 1024Tosc           | 1024Tosc |

| INTRC, EXTRC                    | 72 ms            | _                  | —        |

## TABLE 9-4: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 9-5: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | то | PD |                                                         |  |  |  |  |

|-----|----|----|---------------------------------------------------------|--|--|--|--|

| 0   | 1  | 1  | Power-on Reset                                          |  |  |  |  |

| 0   | 0  | х  | legal, TO is set on POR                                 |  |  |  |  |

| 0   | x  | 0  | llegal, PD is set on POR                                |  |  |  |  |

| 1   | 0  | u  | WDT Reset                                               |  |  |  |  |

| 1   | 0  | 0  | VDT Wake-up                                             |  |  |  |  |

| 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |  |

Legend: u = unchanged, x = unknown.

NOTES:

| RETURN             | Return from Subroutine                                                                                                | RRF                                | Rotate Right f through Carry                                                                                                                                                                          |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:            | [label] RETURN                                                                                                        | Syntax:<br>Operands:<br>Operation: | [ <i>label</i> ] RRF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>See description below<br>C                                                                                                          |  |  |  |

| Operands:          | None                                                                                                                  |                                    |                                                                                                                                                                                                       |  |  |  |

| Operation:         | $TOS \rightarrow PC$                                                                                                  |                                    |                                                                                                                                                                                                       |  |  |  |

| Status Affected:   | None                                                                                                                  |                                    |                                                                                                                                                                                                       |  |  |  |

| Encoding:          | 00 0000 0000 1000                                                                                                     | Status Affected:                   |                                                                                                                                                                                                       |  |  |  |

| Description:       | Return from subroutine. The stack                                                                                     | Encoding:                          | 00 1100 dfff ffff                                                                                                                                                                                     |  |  |  |

|                    | is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two cycle<br>instruction. | Description:                       | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg- |  |  |  |

| Words:             | 1                                                                                                                     |                                    | ister 'f'.                                                                                                                                                                                            |  |  |  |

| Cycles:<br>Example | 2<br>RETURN                                                                                                           |                                    | C Register f                                                                                                                                                                                          |  |  |  |

|                    | After Interrupt                                                                                                       | Words:<br>Cycles:<br>Example       | 1                                                                                                                                                                                                     |  |  |  |

|                    | PC = TOS                                                                                                              |                                    | 1                                                                                                                                                                                                     |  |  |  |

|                    |                                                                                                                       |                                    | rrf <b>REG1</b> ,<br>0                                                                                                                                                                                |  |  |  |

|                    |                                                                                                                       |                                    | Before Instruction                                                                                                                                                                                    |  |  |  |

|                    |                                                                                                                       |                                    | REG1 = 1110 0110<br>C = 0                                                                                                                                                                             |  |  |  |

|                    |                                                                                                                       |                                    | After Instruction<br>REG1 = 1110 0110                                                                                                                                                                 |  |  |  |

|                    |                                                                                                                       |                                    | W = 0111 0011                                                                                                                                                                                         |  |  |  |

|                    |                                                                                                                       |                                    | <b>C</b> = 0                                                                                                                                                                                          |  |  |  |

| RLF              | Rotate Left f through Carry                                                                  | SLEEP            |                                                                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                     | Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                           | Operands:        | None                                                                                                                                                                                                                               |

| Operation:       | See description below                                                                        | Operation:       | $00h \rightarrow WDT,$                                                                                                                                                                                                             |

| Status Affected: | С                                                                                            |                  | $0 \rightarrow \underline{WDT}$ prescaler,<br>1 $\rightarrow \underline{TO}$ ,                                                                                                                                                     |

| Encoding:        | 00 1101 dfff ffff                                                                            |                  | $0 \rightarrow PD$                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are                                                             | Status Affected: |                                                                                                                                                                                                                                    |

| ·                | rotated one bit to the left through the Carry Flag. If 'd' is 0, the result                  | Encoding:        | 00 0000 0110 0011                                                                                                                                                                                                                  |

|                  | is placed in the W register. If 'd' is<br>1, the result is stored back in reg-<br>ister 'f'. | Description:     | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |

| Words:           | 1                                                                                            | Words:           | 1                                                                                                                                                                                                                                  |

| Cycles:          | 1                                                                                            | Cycles:          | 1                                                                                                                                                                                                                                  |

| Example          | RLF REG1,0                                                                                   | Example:         | SLEEP                                                                                                                                                                                                                              |

|                  | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                         |                  |                                                                                                                                                                                                                                    |

stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

#### 11.11 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PIC devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

#### 11.12 <u>SIMICE Entry-Level</u> <u>Hardware Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB-SIM. Both SIMICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PIC 8-bit microcontrollers. SIM-ICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entry-level system development.

# 11.13 <u>PICDEM-1 Low-Cost PIC MCU</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

# 11.14 <u>PICDEM-2 Low-Cost PIC16CXX</u> <u>Demonstration Board</u>

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

## 11.15 <u>PICDEM-3 Low-Cost PIC16CXXX</u> <u>Demonstration Board</u>

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

# 11.16 PICDEM-17

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756, PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug

<sup>© 1997-2013</sup> Microchip Technology Inc.

# **PIC12C67X**

NOTES:

# 12.0 ELECTRICAL SPECIFICATIONS FOR PIC12C67X

# Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                  | –40° to +125°C                     |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                             | –65°C to +150°C                    |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                    | –0.3V to (VDD + 0.3V)              |

| Voltage on VDD with respect to Vss                                                                              | 0 to +7.0V                         |

| Voltage on MCLR with respect to Vss (Note 2)                                                                    | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                                | 700 mW                             |

| Maximum current out of Vss pin                                                                                  | 200 mA                             |

| Maximum current into VDD pin                                                                                    |                                    |

| Input clamp current, liк (Vi < 0 or Vi > VDD)                                                                   | ± 20 mA                            |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                  |                                    |

| Maximum output current sunk by any I/O pin                                                                      | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                   | 25 mA                              |

| Maximum current sunk by GPIO pins combined                                                                      | 100 mA                             |

| Maximum current sourced by GPIO pins combined                                                                   | 100 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VC) | ЭН) х ІОН} + $\Sigma$ (VOI х ІОL). |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 12.1 DC Characteristics: PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS      |                                                                            |               |        | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C &\leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ -40^{\circ}C &\leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ -40^{\circ}C &\leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |              |          |                                                                                                                     |  |  |

|-------------------------|----------------------------------------------------------------------------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|---------------------------------------------------------------------------------------------------------------------|--|--|

| Parm Characteristic No. |                                                                            | Sym           | Min    | Typ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                            | Max          | Units    | Conditions                                                                                                          |  |  |

| D001                    | Supply Voltage                                                             | Vdd           | 3.0    |                                                                                                                                                                                                                                                                                                                               | 5.5          | V        |                                                                                                                     |  |  |

| D002                    | RAM Data Retention<br>Voltage <sup>(2)</sup>                               | Vdr           |        | 1.5*                                                                                                                                                                                                                                                                                                                          |              | V        | Device in SLEEP mode                                                                                                |  |  |

| D003                    | VDD Start Voltage to ensure<br>Power-on Reset                              | VPOR          |        | Vss                                                                                                                                                                                                                                                                                                                           |              | V        | See section on Power-on Reset for details                                                                           |  |  |

| D004                    | VDD Rise Rate to ensure<br>Power-on Reset                                  | SVDD          | 0.05*  |                                                                                                                                                                                                                                                                                                                               |              | V/ms     | See section on Power-on Reset for details                                                                           |  |  |

| D010                    | Supply Current <sup>(3)</sup>                                              | Idd           | _      | 1.2                                                                                                                                                                                                                                                                                                                           | 2.5          | mA       | Fosc = 4MHz, VDD = 3.0V<br>XT and EXTRC mode (Note 4)                                                               |  |  |

| D010C                   |                                                                            |               | -      | 1.2                                                                                                                                                                                                                                                                                                                           | 2.5          | mA       | Fosc = 4MHz, VDD = 3.0V<br>INTRC mode (Note 6)                                                                      |  |  |

|                         |                                                                            |               | —      | 2.2                                                                                                                                                                                                                                                                                                                           | 8            | mA       | Fosc = 10MHz, VDD = 5.5V<br>HS mode                                                                                 |  |  |

| D010A                   |                                                                            |               | —      | 19                                                                                                                                                                                                                                                                                                                            | 29           | μA       | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Commercial Temperature                                           |  |  |

|                         |                                                                            |               | _      | 19<br>32                                                                                                                                                                                                                                                                                                                      | 37<br>60     | μΑ<br>μΑ | Fosc = 32kHz, VDD = 3.0V, WDT disabled<br>LP mode, Industrial Temperature<br>Fosc = 32kHz, VDD = 3.0V, WDT disabled |  |  |

|                         |                                                                            |               |        |                                                                                                                                                                                                                                                                                                                               |              | •        | LP mode, Extended Temperature                                                                                       |  |  |

| D020<br>D021<br>D021B   | Power-down Current <sup>(5)</sup>                                          | IPD           | _<br>_ | 0.25<br>0.25<br>2                                                                                                                                                                                                                                                                                                             | 6<br>7<br>14 | μΑ<br>μΑ | VDD = 3.0V, Commercial, WDT disabled<br>VDD = 3.0V, Industrial, WDT disabled<br>VDD = 3.0V, Extended, WDT disabled  |  |  |

| DUZID                   |                                                                            |               |        | 2<br>0.5                                                                                                                                                                                                                                                                                                                      | 8            | μΑ<br>μΑ | VDD = 5.5V, Extended, WDT disabled $VDD = 5.5V$ , Commercial, WDT disabled                                          |  |  |

|                         |                                                                            |               | —      | 0.8                                                                                                                                                                                                                                                                                                                           | 9            | μA       | $V_{DD} = 5.5V$ , Industrial, WDT disabled                                                                          |  |  |

|                         |                                                                            |               | —      | 3                                                                                                                                                                                                                                                                                                                             | 16           | μA       | VDD = 5.5V, Extended, WDT disabled                                                                                  |  |  |

| D022                    | Watchdog Timer Current                                                     | $\Delta$ IWDT |        | 2.2                                                                                                                                                                                                                                                                                                                           | 5            | μA       | VDD = 3.0V, Commercial                                                                                              |  |  |

|                         |                                                                            |               | _      | 2.2<br>4                                                                                                                                                                                                                                                                                                                      | 6<br>11      | μΑ<br>μΑ | VDD = 3.0V, Industrial<br>VDD = 3.0V, Extended                                                                      |  |  |

| D028                    | Supply Current <sup>(3)</sup><br>During read/write to<br>EEPROM peripheral | ΔIEE          | —      | 0.1                                                                                                                                                                                                                                                                                                                           | 0.2          | mA       | Fosc = 4MHz, VDD = 5.5V, SCL = 400kHz<br>For PIC12CE673/674 only                                                    |  |  |

These parameters are characterized but not tested.

Note 1: Data in Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT disabled.

b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode.

4: For EXTRC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula:

Ir = VDD/2REXT (mA) with REXT in kOhm.

5: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

**6:** INTRC calibration value is for 4MHz nominal at 5V,  $25^{\circ}$ C.

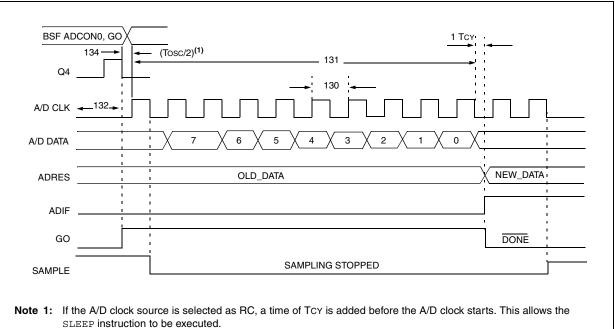

#### FIGURE 12-9: A/D CONVERSION TIMING

| Param<br>No. | Sym  | Characteristic                             |                     | Min    | Тур†     | Max | Units | Conditions                                                                                                                                                                                                                      |

|--------------|------|--------------------------------------------|---------------------|--------|----------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | Tad  | A/D clock period                           | PIC12 <b>C</b> 67X  | 1.6    | _        |     | μS    | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                                    |

|              |      |                                            | PIC12 <b>LC</b> 67X | 2.0    | _        | _   | μS    | TOSC based, VREF full range                                                                                                                                                                                                     |

|              |      |                                            | PIC12 <b>C</b> 67X  | 2.0    | 4.0      | 6.0 | μS    | A/D RC Mode                                                                                                                                                                                                                     |

|              |      |                                            | PIC12 <b>LC</b> 67X | 3.0    | 6.0      | 9.0 | μS    | A/D RC Mode                                                                                                                                                                                                                     |

| 131          | TCNV | Conversion time (not ind<br>time) (Note 1) | cluding S/H         | 11     | —        | 11  | Tad   |                                                                                                                                                                                                                                 |

| 132          | TACQ | Acquisition time                           |                     | Note 2 | 20       |     | μS    |                                                                                                                                                                                                                                 |

|              |      |                                            |                     | 5*     | _        | _   | μS    | The minimum time is the<br>amplifier setting time. This<br>may be used if the "new"<br>input voltage has not<br>changed by more than 1 LSt<br>(i.e., 20.0 mV @ 5.12V) from<br>the last sampled voltage (as<br>stated on CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                      |                     | _      | Tosc/2 § | _   |       | If the A/D clock source is<br>selected as RC, a time of<br>TCY is added before the A/D<br>clock starts. This allows the<br>SLEEP instruction to be exe<br>cuted.                                                                |

| 135          | Tswc | Switching from convert                     | 1.5 §               |        | _        | TAD |       |                                                                                                                                                                                                                                 |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

This specification ensured by design. §

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 8.1 for min. conditions.

# **PIC12C67X**

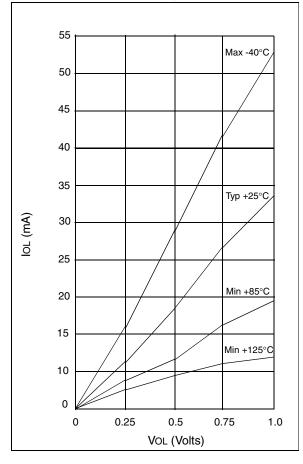

### FIGURE 13-9: IOL vs. VOL, VDD = 5.5 V

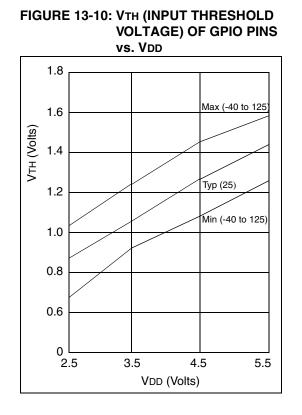

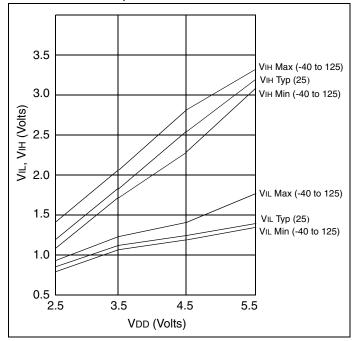

FIGURE 13-11: VIL, VIH OF NMCLR AND TOCKI vs. VDD

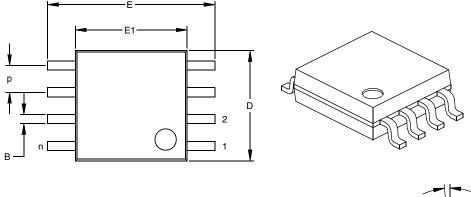

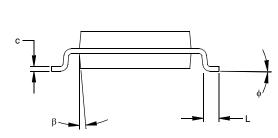

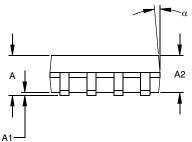

# 8-Lead Plastic Small Outline (SM) – Medium, 208 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |      | INCHES* |      |      | MILLIMETERS |      |  |

|--------------------------|-------|------|---------|------|------|-------------|------|--|

| Dimension Limits         |       | MIN  | NOM     | MAX  | MIN  | NOM         | MAX  |  |

| Number of Pins           | n     |      | 8       |      |      | 8           |      |  |

| Pitch                    | р     |      | .050    |      |      | 1.27        |      |  |

| Overall Height           | А     | .070 | .075    | .080 | 1.78 | 1.97        | 2.03 |  |

| Molded Package Thickness | A2    | .069 | .074    | .078 | 1.75 | 1.88        | 1.98 |  |

| Standoff                 | A1    | .002 | .005    | .010 | 0.05 | 0.13        | 0.25 |  |

| Overall Width            | Е     | .300 | .313    | .325 | 7.62 | 7.95        | 8.26 |  |

| Molded Package Width     | E1    | .201 | .208    | .212 | 5.11 | 5.28        | 5.38 |  |

| Overall Length           | D     | .202 | .205    | .210 | 5.13 | 5.21        | 5.33 |  |

| Foot Length              | L     | .020 | .025    | .030 | 0.51 | 0.64        | 0.76 |  |

| Foot Angle               | ¢     | 0    | 4       | 8    | 0    | 4           | 8    |  |

| Lead Thickness           | С     | .008 | .009    | .010 | 0.20 | 0.23        | 0.25 |  |

| Lead Width               | В     | .014 | .017    | .020 | 0.36 | 0.43        | 0.51 |  |

| Mold Draft Angle Top     | α     | 0    | 12      | 15   | 0    | 12          | 15   |  |

| Mold Draft Angle Bottom  | β     | 0    | 12      | 15   | 0    | 12          | 15   |  |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

Drawing No. C04-056

# **PIC12C67X**

NOTES: