# E·XFL

#### Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                            |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 60MHz                                                               |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, SSI, SSP, UART/USART, USB            |

| Peripherals                | DMA, PWM, WDT                                                       |

| Number of I/O              | 72                                                                  |

| Program Memory Size        | 128KB (128K x 8)                                                    |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 100-LQFP                                                            |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str750fv1t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Serial memory interface (SMI)

The Serial Memory interface is directly able to access up to 4 serial FLASH devices. It can be used to access data, execute code directly or boot the application from external memory. The memory is addressed as 4 banks of up to 16 Mbytes each.

### **Clocks and start-up**

After RESET or when exiting from Low Power Mode, the CPU is clocked immediately by an internal RC oscillator (FREEOSC) at a frequency centered around 5 MHz, so the application code can start executing without delay. In parallel, the 4/8 MHz Oscillator is enabled and its stabilization time is monitored using a dedicated counter.

An oscillator failure detection is implemented: when the clock disappears on the XT1 pin, the circuit automatically switches to the FREEOSC oscillator and an interrupt is generated.

In Run mode, the AHB and APB clock speeds can be set at a large number of different frequencies thanks to the PLL and various prescalers: up to 60 MHz for AHB and up to 32 MHz for APB when fetching from Flash (64 MHz and 32 MHz when fetching from SRAM).

In SLOW mode, the AHB clock can be significantly decreased to reduce power consumption.

The built-in Clock Controller also provides the 48 MHz USB clock directly without any extra oscillators or PLL. For instance, starting from the 4 MHz crystal source, it is possible to obtain in parallel 60 MHz for the AHB clock, 48 MHz for the USB clock and 30 MHz for the APB peripherals.

### **Boot modes**

At start-up, boot pins are used to select one of five boot options:

- Boot from internal flash

- Boot from external serial Flash memory

- Boot from internal boot loader

- Boot from internal SRAM

Booting from SMI memory allows booting from a serial flash. This way, a specific boot monitor can be implemented. Alternatively, the STR750F can boot from the internal boot loader that implements a boot from UART.

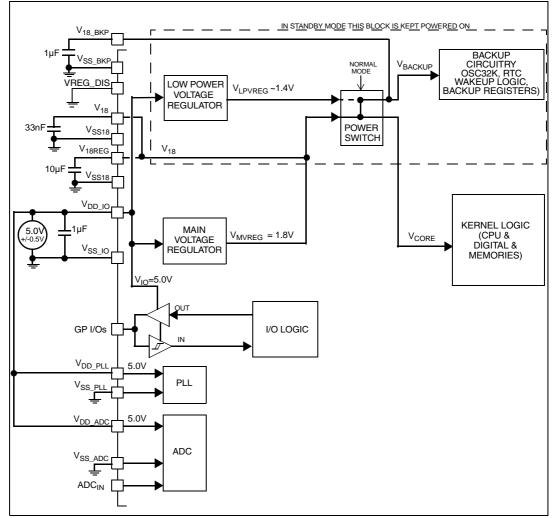

### **Power supply schemes**

You can connect the device in any of the following ways depending on your application.

- Power Scheme 1: Single external 3.3V power source. In this configuration the V<sub>CORE</sub> supply required for the internal logic is generated internally by the main voltage regulator and the V<sub>BACKUP</sub> supply is generated internally by the low power voltage regulator. This scheme has the advantage of requiring only one 3.3V power source.

- Power Scheme 2: Dual external 3.3V and 1.8V power sources. In this configuration, the internal voltage regulators are switched off by forcing the VREG\_DIS pin to high level. V<sub>CORE</sub> is provided externally through the V<sub>18</sub> and V<sub>18REG</sub> power pins and V<sub>BACKUP</sub> through the V<sub>18\_BKP</sub> pin. This scheme is intended to save power consumption for applications which already provide an 1.8V power supply.

- Power Scheme 3: Single external 5.0V power source. In this configuration the V<sub>CORE</sub> supply required for the internal logic is generated internally by the main voltage

periodic interrupt. It is clocked by an external 32.768 kHz oscillator or the internal low power RC oscillator. The RC has a typical frequency of 300 kHz and can be calibrated.

### WDG (watchdog timer)

The watchdog timer is based on a 16-bit downcounter and 8-bit prescaler. It can be used as watchdog to reset the device when a problem occurs, or as free running timer for application time out management.

### Timebase timer (TB)

The timebase timer is based on a 16-bit auto-reload counter and not connected to the I/O pins. It can be used for software triggering, or to implement the scheduler of a real-time operating system.

### Synchronizable standard timers (TIM2:0)

The three standard timers are based on a 16-bit auto-reload counter and feature up to 2 input captures and 2 output compares (for external triggering or time base / time out management). They can work together with the PWM timer via the Timer Link feature for synchronization or event chaining. In reset state, timer Alternate Function I/Os are connected to the same

I/O ports in both 64-pin and 100-pin devices. To optimize timer functions in 64-pin devices, timer Alternate Function I/Os can be connected, or "remapped", to other I/O ports as summarized in *Table 3* and detailed in *Table 6*. This remapping is done by the application via a control register.

|          |                       | Nu      | Number of alternate function I/Os |          |  |  |  |  |  |  |

|----------|-----------------------|---------|-----------------------------------|----------|--|--|--|--|--|--|

| Star     | ndard timer functions | 100-pin | 64-pin package                    |          |  |  |  |  |  |  |

|          |                       |         | Default mapping                   | Remapped |  |  |  |  |  |  |

| ΤΙΜ Ο    | Input Capture         | 2       | 1                                 | 2        |  |  |  |  |  |  |

| T IIVI O | Output Compare/PWM    | 2       | 1                                 | 2        |  |  |  |  |  |  |

| TIM 1    | Input Capture         | 2       | 1                                 | 1        |  |  |  |  |  |  |

|          | Output Compare/PWM    | 2       | 1                                 | 1        |  |  |  |  |  |  |

| TIM 2    | Input Capture         | 2       | 2                                 | 2        |  |  |  |  |  |  |

| 111112   | Output Compare/PWM    | 2       | 1                                 | 2        |  |  |  |  |  |  |

### Table 3. Standard timer alternate function I/Os

Any of the standard timers can be used to generate PWM outputs. One timer (TIM0) is mapped to a DMA channel.

### Motor control PWM timer (PWM)

The Motor Control PWM Timer (PWM) can be seen as a three-phase PWM multiplexed on 6 channels. The 16-bit PWM generator has full modulation capability (0...100%), edge or centre-aligned patterns and supports dead-time insertion. It has many features in common with the standard TIM timers which has the same architecture and it can work together with the TIM timers via the Timer Link feature for synchronization or event chaining. The PWM timer is mapped to a DMA channel.

### GPIOs (general purpose input/output)

Each of the 72 GPIO pins (38 GPIOs in 64-pin devices) can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as Peripheral Alternate Function. Port 1.15 is an exception, it can be used as general-purpose input only or wake-up from STANDBY mode (WKP\_STDBY). Most of the GPIO pins are shared with digital or analog alternate functions.

ADC\_IN13 / P1.12 ADC\_IN13 / P1.12 ADC\_IN14 P0.03 / TIM2\_T11 / ADC\_IN1 ADC\_IN14 P0.03 / TIM2\_T11 / ADC\_IN14 ADC\_IN16 P0.03 / TIM2\_T11 / ADC\_IN16 ADC\_IN17 SSP0\_IN28 ADC\_IN17 SSP0\_IN28 ADC\_IN17 SSP0\_IN28 ADC\_IN16 P0.06 / SMI\_DIN7 SSP0\_IN28 ADC\_IN16 P0.06 / SMI\_DIN7 SSP0\_IN28 ADC\_IN17 / SSP0\_IN28 ADDC\_IN17 / SSP0\_IN18 ADDC\_IN17 / SSP0\_IN18 ADDC\_IN17 / SSP0\_IN18 ADDC\_IN17 / SSP 49 47 → V<sub>REG\_DIS</sub> 47 → V<sub>SS\_IO\_2</sub> 46 → V<sub>SSA\_ADC</sub> 45 → V<sub>DDA\_ADC</sub> 44 → V<sub>DD\_IO\_2</sub> 43 → P1.03 / TIM2\_TI2 43 → P1.03 / TIM2\_TI2 BOOT0 / TIM0\_OC1 / P0.00 4 ADC\_IN8 / TIM1\_TI1 / P0.29 5 TIM1\_OC1 / P0.28 G P0.14 / CAN\_RX or USB\_DP

P0.15 / CAN\_TX or USB\_DN TEST 7 ⊲42 V<sub>SS\_IO\_4</sub> [ 8 UART1\_TX / P0.21 [ 9 41 LQFP64 □ NRSTIN *(*40 UART1\_IX / P0.20 [ 10 JTMS / P1.19 [ 11 JTCK / P1.18 [ 12 JTDO / P1.17 [ 13 JTDI / P1.16 [ 14 NRSTOUT 39 XRTC2 38 V<sub>18BKP</sub> I/Os 37 □ XRTC1 36 □ V<sub>18BKP</sub> 35 □ V<sub>SSBKP</sub> 34 □ V<sub>SS18</sub> 33 U V<sub>18REG</sub> V<sub>DDD\_IO\_3</sub> C V<sub>DDA\_PLL</sub> C XT2 C XT1 C V<sub>SS\_I0\_3</sub> | SMI\_CS1 / ADC\_IN2 / UART0\_CTS / UART2\_RX /P0.12 SSA\_PLL

Figure 3. LQFP64 pinout

# 4.1 Pin description table

# Legend / abbreviations for Table 6:

| Туре:                              | I = input, O = output, S = supply,                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input levels:                      | All Inputs are LVTTL at $V_{DD_IO} = 3.3V+/-0.3V$ or TTL at $V_{DD_IO} = 5V\pm 0.5V$ . In both cases, $T_T$ means $V_{ILmax} = 0.8V V_{IHmin} = 2.0V$                                                                                                                                                                                                                                 |

| Inputs:                            | All inputs can be configured as floating or with internal weak pull-up or pull down (pu/pd)                                                                                                                                                                                                                                                                                           |

| Outputs:                           | <ul> <li>All Outputs can be configured as Open Drain (OD) or<br/>Push-Pull (PP) (see also note 6 below <i>Table 6</i>).</li> <li>There are 3 different types of Output with different<br/>drives and speed characteristics:</li> <li>- O8: f<sub>max</sub> = 40 MHz on C<sub>L</sub>=50pF and 8 mA static<br/>drive capability for V<sub>OL</sub>=0.4V and up to 20 mA for</li> </ul> |

|                                    | <ul> <li>V<sub>OL</sub>=1.3V (see<i>Output driving current on page 55</i>)</li> <li>O4: f<sub>max</sub> = 20 MHz on C<sub>L</sub>=50pF and 4 mA static drive capability for V<sub>OL</sub>=0.4V (see<i>Output driving</i>)</li> </ul>                                                                                                                                                 |

|                                    | <i>current on page 55</i> )<br>- O2: $f_{max} = 10 \text{ MHz on } C_L=50 \text{pF}$ and 2 mA static                                                                                                                                                                                                                                                                                  |

|                                    | drive capability of for V <sub>OL</sub> =0.4V (see <i>Output driving current on page 55</i> )                                                                                                                                                                                                                                                                                         |

| External interrupts/wake-up lines: | EITx                                                                                                                                                                                                                                                                                                                                                                                  |

|                        | Pin                     | n°                    |                        |                                         |      |                | In       | put   |                   | C          | )utpu     | ıt | y                 |                                                  |                                                  |                                                                     |

|------------------------|-------------------------|-----------------------|------------------------|-----------------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                                | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)             | Alternate                                        | e function                                                          |

| 7                      | D1                      | 5                     | D1                     | P0.29 / TIM1_TI1<br>/ ADC_IN8           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.29                                        | TIM1: Input<br>Capture 1                         | ADC: Analog<br>input 8                                              |

| 8                      | E1                      | 6                     | D2                     | P0.28 /<br>TIM1_OC1                     | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 0.28                                        | TIM1: Output Cor                                 | npare 1                                                             |

| 9                      | E5                      | 7                     | D3                     | TEST                                    | Ι    |                |          |       |                   |            |           |    |                   | Reserved, mu                                     | ist be tied to groun                             | d                                                                   |

| 10                     | E4                      | 8                     | D4                     | VSS_IO                                  | S    |                |          |       |                   |            |           |    |                   | Ground Voltag                                    | ge for digital I/Os                              |                                                                     |

| 11                     | E2                      |                       |                        | P0.23 /<br>UART1_RTS /<br>ADC_IN6       | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O2         | x         | x  |                   | Port 0.23                                        | UART1: Ready<br>To Send<br>output <sup>(4)</sup> | ADC analog input<br>6                                               |

| 12                     | F5                      |                       |                        | P2.04 /<br>TIM2_OC1                     | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 2.04                                        | TIM2: Output<br>Compare 1 <sup>(4)</sup>         |                                                                     |

| 13                     | F1                      |                       |                        | P2.03 /<br>UART1_RTS                    | I/O  | т <sub>т</sub> | x        | x     |                   | 02         | x         | x  |                   | Port 2.03                                        | UART1: Ready<br>To Send<br>output <sup>(4)</sup> |                                                                     |

| 14                     | F4                      |                       |                        | P2.02                                   | I/O  | Τ <sub>T</sub> | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.02                                        |                                                  |                                                                     |

| 15                     | E3                      |                       |                        | P0.22 /<br>UART1_CTS /<br>ADC_IN5       | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O2         | x         | x  |                   | Port 0.22                                        | UART1: Clear To<br>Send input                    | ADC: Analog<br>input 5                                              |

| 16                     | F2                      | 9                     | E4                     | P0.21 /<br>UART1_TX                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.21                                        | UART1: Transmit<br>(remappable to P              | data output<br>0.15) <sup>(4)</sup>                                 |

| 17                     | F3                      | 10                    | E3                     | P0.20 /<br>UART1_RX                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.20                                        | UART1: Receive (remappable to P                  | data input<br>0.14) <sup>(4)</sup>                                  |

| 18                     | G3                      | 11                    | E2                     | P1.19 / JTMS                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | O2         | х         | х  |                   | JTAG mode<br>selection<br>input <sup>(6)</sup>   | Port 1.19                                        |                                                                     |

| 19                     | G2                      | 12                    | E1                     | P1.18 / JTCK                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | JTAG clock<br>input <sup>(6)</sup>               | Port 1.18                                        |                                                                     |

| 20                     | H3                      | 13                    | F4                     | P1.17 / JTDO                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | O8         | х         | х  |                   | JTAG data<br>output <sup>(6)</sup>               | Port 1.17                                        |                                                                     |

| 21                     | H2                      | 14                    | F3                     | P1.16 / JTDI                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | JTAG data<br>input <sup>(6)</sup>                | Port 1.16                                        |                                                                     |

| 22                     | G1                      | 15                    | F2                     | NJTRST                                  | Ι    | TT             |          |       |                   |            |           |    |                   | JTAG reset in                                    | put <sup>(5)</sup>                               |                                                                     |

| 23                     | G4                      |                       |                        | P2.01                                   | I/O  | $T_T$          | х        | х     |                   | 02         | х         | Х  |                   | Port 2.01                                        |                                                  |                                                                     |

| 24                     | G5                      |                       |                        | P2.00                                   | I/O  | TT             | X        | х     |                   | O2         | х         | х  |                   | Port 2.00                                        |                                                  |                                                                     |

|                        |                         |                       |                        |                                         |      |                |          |       |                   |            |           |    |                   | ITAC                                             | Port 0.13                                        |                                                                     |

| 25                     | H1                      | 16                    | F1                     | P0.13 / RTCK /<br>UART0_RTS<br>UART2_TX | I/O  | Τ <sub>Τ</sub> | х        | x     |                   | O8         | х         | х  |                   | JTAG<br>return<br>clock<br>output <sup>(6)</sup> | UART0: Ready<br>To Send<br>output <sup>(4)</sup> | UART2: Transmit<br>Data output<br>(when<br>remapped) <sup>(8)</sup> |

# Table 6. STR750F pin description (continued)

| Tab                    | le 6.                   |                       | ST                     | R750F pin de                                      | escri | ptic           | on (o    | con   | tinue             | d)         |           |    |                   |                                                   |                                                                              |                                                                |

|------------------------|-------------------------|-----------------------|------------------------|---------------------------------------------------|-------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|---------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------|

|                        | Pin                     | n°                    |                        |                                                   |       |                | In       | put   |                   | C          | )utpu     | ıt | λ                 |                                                   |                                                                              |                                                                |

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                                          | Type  | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)              | Alternate                                                                    | e function                                                     |

|                        |                         |                       |                        | P0.12 /                                           |       |                |          |       |                   |            |           |    |                   |                                                   | UART0: Clear To<br>Send input                                                | ADC: Analog<br>input 2                                         |

| 26                     | J2                      | 17                    | G2                     | UART2_RX /<br>UART0_CTS /<br>ADC_IN2 /<br>SMI_CS1 | I/O   | Τ <sub>Τ</sub> | x        | х     |                   | 04         | x         | х  |                   | Port 0.12                                         | Serial Memory<br>Interface: chip<br>select output 1                          | UART2: Receive<br>Data input (when<br>remapped) <sup>(8)</sup> |

| 27                     | J1                      | 18                    | G1                     | P0.11 /<br>UART0_TX /<br>BOOT1 /<br>SMI_CS2       | I/O   | Τ <sub>Τ</sub> | x        | x     |                   | O4         | x         | x  |                   | Port<br>0.11/Boot<br>mode<br>selection<br>input 1 | UART0: Transmit<br>data output                                               | Serial Memory<br>Interface: chip<br>select output 2            |

| 28                     | K1                      | 19                    | H1                     | P0.10 /<br>UART0_RX /<br>SMI_CS3                  | I/O   | Τ <sub>Τ</sub> | x        | x     | EIT4              | 02         | x         | x  |                   | Port 0.10                                         | UART0: Receive<br>Data input                                                 | Serial Memory<br>Interface: chip<br>select output 3            |

| 29                     | K2                      | 20                    | H2                     | P0.09 / I2C_SDA                                   | I/O   | TT             | х        | Х     |                   | 04         | Х         | Х  |                   | Port 0.09                                         | I2C: Serial Data                                                             |                                                                |

| 30                     | K3                      | 21                    | НЗ                     | P0.08 / I2C_SCL                                   | I/O   | TT             | х        | х     | EIT3              | O4         | х         | Х  |                   | Port 0.08                                         | I2C: Serial clock                                                            |                                                                |

| 31                     | H4                      |                       |                        | P2.19                                             | I/O   | TT             | х        | Х     |                   | 02         | Х         | Х  |                   | Port 2.19                                         |                                                                              |                                                                |

| 32                     | H5                      |                       |                        | P2.18                                             | I/O   | TT             | х        | х     |                   | O2         | х         | Х  |                   | Port 2.18                                         |                                                                              |                                                                |

| 33                     | H6                      |                       |                        | P2.17 /<br>UART2_RTS                              | I/O   | TT             | x        | х     |                   | O2         | х         | х  |                   | Port 2.17                                         | UART2: Ready To                                                              | Send output <sup>(4)</sup>                                     |

| 34                     | J3                      | 22                    | G3                     | P1.11<br>/UART0_RTS<br>ADC_IN12                   | I/O   | Τ <sub>Τ</sub> | x        | х     | EIT11             | O8         | x         | х  |                   | Port 1.11                                         | UART0: Ready<br>To Send<br>output <sup>(4)</sup>                             | ADC: Analog<br>input 12                                        |

| 35                     | J4                      |                       |                        | P0.27 /<br>UART2_RTS /<br>ADC_IN7                 | I/O   | Τ <sub>Τ</sub> | x        | х     |                   | 02         | x         | x  |                   | Port 0.27                                         | UART2: Ready<br>To Send<br>output <sup>(8)</sup>                             | ADC: Analog<br>input 7                                         |

| 36                     | J6                      |                       |                        | P0.26 /<br>UART2_CTS                              | I/O   | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.26                                         | UART2: Clear To                                                              | Send input                                                     |

| 37                     | J7                      |                       |                        | P0.25 /<br>UART2_TX                               | I/O   | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.25                                         | UART2: Transmit<br>(remappable to P                                          |                                                                |

| 38                     | H7                      |                       |                        | P0.24 /<br>UART2_RX                               | I/O   | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.24                                         | UART2: Receive (<br>(remappable to P                                         |                                                                |

| 39                     | J5                      | 23                    | G4                     | P0.19/USB_CK/<br>SSP1_NSS/                        | I/O   | T <sub>T</sub> | x        | x     | EIT6              | O2         | x         | x  |                   | Port 0.19                                         | SSP1: Slave<br>select input<br>(remappable to<br>P0.11) <sup>(8)</sup>       | ADC: Analog<br>input 4                                         |

|                        |                         |                       |                        | ADC_IN4                                           |       |                |          |       |                   |            |           |    |                   |                                                   | USB:<br>48 MHz Clock<br>input                                                |                                                                |

| 40                     | K4                      | 24                    | H5                     | P0.18 /<br>SSP1_MOSI                              | I/O   | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.18                                         | SSP1: Master out<br>(remappable to P                                         |                                                                |

| 41                     | K5                      | 25                    | H4                     | P0.17 /<br>SSP1_MISO /<br>ADC_IN3                 | I/O   | Τ <sub>Τ</sub> | x        | х     |                   | O2         | x         | x  |                   | Port 0.17                                         | SSP1: Master<br>in/slave out data<br>(remappable to<br>P0.09) <sup>(8)</sup> | ADC: Analog<br>input 3                                         |

| 42                     | K6                      | 26                    | H6                     | P0.16 /<br>SSP1_SCLK                              | I/O   | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.16                                         | SSP1: serial clock<br>P0.08) <sup>(8)</sup>                                  | (remappable to                                                 |

| Table 6. | STR750F pin description (continued) |

|----------|-------------------------------------|

|----------|-------------------------------------|

|                        | Pin                     | n°                    |                        |                                    |      |                | In       | put   |                   | C          | )utpu     | ıt | Š                 |                                      |                                                     |                                                    |

|------------------------|-------------------------|-----------------------|------------------------|------------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------|-----------------------------------------------------|----------------------------------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                           | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset) | Alternate                                           | e function                                         |

| 68                     | A10                     |                       |                        | P1.02 /<br>TIM2_OC2                | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 1.02                            | TIM2: Output con<br>(remappable to P                | npare 2<br>0.06) <sup>(8)</sup>                    |

| 69                     | D7                      | 44                    | C6                     | VDD_IO                             | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                        | e for digital I/Os                                  |                                                    |

| 70                     | D8                      | 45                    | D6                     | VDDA_ADC                           | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                        | e for A/D converte                                  | r                                                  |

| 71                     | C9                      |                       |                        | P2.11                              | I/O  | TT             | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.11                            |                                                     |                                                    |

| 72                     | B10                     |                       |                        | P2.10                              | I/O  | TT             | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.10                            |                                                     |                                                    |

| 73                     | C8                      | 46                    | D7                     | VSSA_ADC                           | S    |                |          |       |                   |            |           |    |                   | Ground Volta                         | ge for A/D converte                                 | er                                                 |

| 74                     | C7                      | 47                    | C7                     | VSS_IO                             | S    |                |          |       |                   |            |           |    |                   | Ground Volta                         | ge for digital I/Os                                 |                                                    |

| 75                     | E8                      | 48                    | D5                     | VREG_DIS                           | I    | TT             |          |       |                   |            |           |    |                   | Voltage Regu                         | lator Disable input                                 |                                                    |

| 76                     | A9                      | 49                    | A8                     | P0.07 /<br>SMI_DOUT /<br>SSP0_MOSI | I/O  | TT             | x        | x     | EIT2              | O4         | x         | x  |                   | Port 0.07                            | Serial Memory<br>Interface: data<br>output          | SSP0: Master out<br>Slave in data                  |

| 77                     | A8                      | 50                    | A7                     | P0.06 / SMI_DIN<br>/ SSP0_MISO     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O4         | x         | х  |                   | Port 0.06                            | Serial Memory<br>Interface: data<br>input           | SSP0: Master in Slave out data                     |

| 78                     | A7                      | 51                    | A6                     | P0.05 /<br>SSP0_SCLK /<br>SMI_CK   | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT1              | 04         | x         | x  |                   | Port 0.05                            | SSP0: Serial<br>clock                               | Serial Memory<br>Interface: Serial<br>clock output |

| 79                     | B7                      | 52                    | B6                     | P0.04 / SMI_CS0<br>/ SSP0_NSS      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O4         | x         | x  |                   | Port 0.04                            | Serial Memory<br>Interface: chip<br>select output 0 | SSP0: Slave select input                           |

| 80                     | C5                      | 53                    | B7                     | P1.10<br>PWM_EMERGE<br>NCY         | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT10             | O2         | x         | x  |                   | Port 1.10                            | PWM: Emergency                                      | y input                                            |

| 81                     | B6                      | 54                    | B5                     | P1.09 / PWM1                       | I/O  | TT             | х        | х     | EIT9              | 04         | Х         | Х  |                   | Port 1.09                            | PWM: PWM1 out                                       | put                                                |

| 82                     | C6                      |                       |                        | P2.09 / PWM1N                      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 2.09                            | PWM: PWM1 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 83                     | G7                      |                       |                        | P2.08 / PWM2                       | I/O  | TT             | х        | х     |                   | 02         | х         | Х  |                   | Port 2.08                            | PWM: PWM2 out                                       | put <sup>(4)</sup>                                 |

| 84                     | G6                      |                       |                        | P2.07 / PWM2N                      | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 2.07                            | PWM: PWM2 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 85                     | F7                      |                       |                        | P2.06 / PWM3                       | I/O  | TT             | х        | х     |                   | 02         | х         | х  |                   | Port 2.06                            | PWM: PWM3 out                                       | put <sup>(4)</sup>                                 |

| 86                     | F6                      |                       |                        | P2.05 / PWM3N                      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 2.05                            | PWM: PWM3 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 87                     | A6                      | 55                    | A5                     | P1.08 / PWM1N /<br>ADC_IN11        | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | х         | х  |                   | Port 1.08                            | PWM: PWM1<br>complementary<br>output <sup>(8)</sup> | ADC: analog<br>input 11                            |

| 88                     | B5                      | 56                    | B4                     | P1.07 / PWM2                       | I/O  | TT             | х        | х     | EIT8              | 04         | х         | Х  |                   | Port 1.07                            | PWM: PWM2 out                                       | put <sup>(4)</sup>                                 |

| 89                     | A5                      | 57                    | A4                     | P1.06 / PWM2N /<br>ADC_IN10        | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | x         | х  |                   | Port 1.06                            | PWM: PWM2<br>complementary<br>output <sup>(4)</sup> | ADC: analog<br>input 10                            |

| 90                     | B4                      | 58                    | B3                     | P1.05 / PWM3                       | I/O  | TT             | х        | х     | EIT7              | O4         | х         | Х  |                   | Port 1.05                            | PWM: PWM3 out                                       | put <sup>(4)</sup>                                 |

# Table 6. STR750F pin description (continued)

# 6 Electrical parameters

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_Amax$  (given by the selected temperature range).

Data based on product characterisation, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A=25^{\circ}$  C,  $V_{DD_{-}IO}=3.3$  V (for the 3.0 V $\leq$ V\_{DD\_{-}IO} $\leq$ 3.6 V voltage range) and V<sub>18</sub>=1.8 V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

Power supply scheme 3: Single external 5 V power source

# Figure 10. Power supply scheme 3

|                 |                      |                                                                                      |                                            |                    |                        | Max <sup>(3)</sup>     |                         |      |

|-----------------|----------------------|--------------------------------------------------------------------------------------|--------------------------------------------|--------------------|------------------------|------------------------|-------------------------|------|

| Symbol          | Parameter            | Conditions <sup>(1)</sup>                                                            |                                            | Тур <sup>(2)</sup> | T <sub>A</sub><br>25°C | Т <sub>А</sub><br>85°С | Т <sub>А</sub><br>105°С | Unit |

|                 |                      | LP_PARAM bits: ALL OFF <sup>(4)</sup><br>Single supply scheme see <i>Figure 12</i> . | 3.3V<br>range                              | 12                 | 16                     | 117                    | 250                     | μA   |

|                 | Supply<br>current in | LP_PARAM bits: ALL OFF<br>Dual supply scheme see <i>Figure 13</i> .                  | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 5<br><1            | 8<br>3                 | 60<br>20               | 110<br>26               | μA   |

| I <sub>DD</sub> | STOP mode            | LP_PARAM bits: ALL OFF <sup>(4)</sup><br>Single supply scheme see <i>Figure 10</i>   | 5V<br>range                                | 15                 | 22                     | 160                    | 310                     | μA   |

| .00             |                      | LP_PARAM bits: ALL OFF<br>Dual supply scheme see <i>Figure 11</i>                    | I <sub>DD_V18</sub><br>I <sub>DD_V50</sub> | 5<br>3             | 86                     | 60<br>50               | 110<br>65               |      |

|                 | Supply current in    | RTC OFF                                                                              | 3.3 V<br>range                             | 10                 | 20                     | 25                     | 28                      | μA   |

|                 | STANDBY<br>mode      |                                                                                      | 5V<br>range                                | 15                 | 25                     | 30                     | 33                      |      |

Table 14. Maximum power consumption in STOP and STANDBY modes

1. The conditions for these consumption measurements are described at the beginning of Section 6.3.4.

2. Typical data are based on  $T_A=25^\circ C,\,V_{DD\_IO}=3.3V$  or 5.0V and  $V_{18}=1.8V$  unless otherwise specified.

3. Data based on product characterisation, tested in production at  $V_{DD_{-IO}}$  max and  $V_{18}$  max (1.95V in dual supply mode or regulator output value in single supply mode).

4. In this mode, the whole digital circuitry is powered internally by the LPVREG at approximately 1.4V, which significantly reduces the leakage currents.

### Typical power consumption

The following measurement conditions apply to Table 15, Table 16 and Table 17.

In RUN mode:

- Program is executed from Flash (except if especially mentioned). The program consists

of an infinite loop. When f<sub>HCLK</sub> > 32 MHz, burst mode is activated.

- A standard 4 MHz crystal source is used.

- In all cases the PLL is used to multiply the frequency.

- All measurements are done in the single supply scheme with internal regulators used (see *Figure 12*)

In WFI Mode:

- In WFI Mode the measurement conditions are similar to RUN mode (OSC4M and PLL enabled). In addition, the Flash can be disabled depending on burst mode activation:

- For AHB frequencies greater than 32 MHz, burst mode is activated and the Flash is kept enabled by setting the WFI\_FLASH\_EN bit (this bit cannot be reset when burst mode is activated).

- For AHB frequencies less than or equal to 32 MHz, burst mode is deactivated, WFI\_FLASH\_EN is reset and the LP\_PARAM14 bit is set (Flash is disabled in WFI mode).

In SLOW mode:

The same program as in RUN mode is executed from Flash. The CPU is clocked by the FREEOSC, OSC4M, LPOSC or OSC32K. Only EXTIT peripheral is enabled in the MRCC\_PCLKEN register.

In SLOW-WFI mode:

In SLOW-WFI, the measurement conditions are similar to SLOW mode (CPU clocked by a low frequency clock). In addition, the LP\_PARAM14 bit is set (FLASH is OFF). The WFI routine itself is executed from SRAM (it is not allowed to execute a WFI from the internal FLASH)

In STOP mode:

• Several measurements are given: in the single supply scheme with internal regulators used (see *Figure 12*): and in the dual supply scheme (see *Figure 13*).

In STANDBY mode:

- Three measurements are given:

- The RTC is disabled, only the consumption of the LPVREG and RSM remain (almost no leakage currents)

- The RTC is running, clocked by a standard 32.768 kHz crystal.

- The RTC is running, clocked by the internal Low Power RC oscillator (LPOSC)

- STANDBY mode is only supported in the single supply scheme (see Figure 12)

### Electro magnetic interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Symbo<br>I       | Parameter  | Conditions                                                                 | Monitored         | Max vs. [f <sub>O</sub> | Unit    |           |  |

|------------------|------------|----------------------------------------------------------------------------|-------------------|-------------------------|---------|-----------|--|

|                  | Farameter  | Conditions                                                                 | Frequency Band    | 4/32MHz                 | 4/60MHz | onit      |  |

|                  |            | Flash devices:                                                             | 0.1 MHz to 30 MHz | 22                      | 26      |           |  |

|                  |            | $V_{DD_{-}IO}$ =3.3 V or 5 V,<br>T <sub>A</sub> =+25° C,<br>LQFP64 package | 30 MHz to 130 MHz | 31                      | 26      | $dB\mu V$ |  |

| S <sub>EMI</sub> | Peak level |                                                                            | 130 MHz to 1 GHz  | 19                      | 23      |           |  |

|                  |            | conforming to SAE J<br>1752/3                                              | SAE EMI Level     | >4                      | >4      | -         |  |

Table 29. EMI characteristics

### Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### Electro-Static discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

| Table 30. Absolute maximum ra | ratings |

|-------------------------------|---------|

|-------------------------------|---------|

| Symbol                | Ratings                                                   | Conditions             | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-----------------------------------------------------------|------------------------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model)    |                        | 2000                            |      |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage<br>(Machine Model)       | T <sub>A</sub> =+25° C | 200                             | V    |

| V <sub>ESD(CDM)</sub> | Electro-static discharge voltage<br>(Charge Device Model) |                        | 750                             |      |

1. Data based on product characterisation, not tested in production.

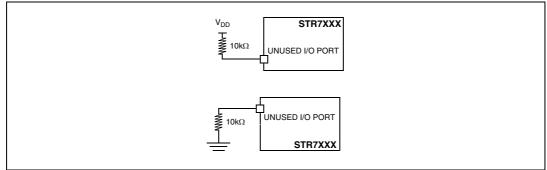

### Figure 25. Connecting unused I/O pins

### Output driving current

The GP I/Os have different drive capabilities:

- O2 outputs can sink or source up to +/-2 mA.

- O4 outputs can sink or source up to +/-4 mA.

- outputs can sink or source up to +/-8 mA or can sink +20 mA (with a relaxed V<sub>OL</sub>).

In the application, the user must limit the number of I/O pins which can drive current to respect the absolute maximum rating specified in *Section 6.2.2*:

- The sum of the current sourced by all the I/Os on V<sub>DD\_IO</sub>, plus the maximum RUN consumption of the MCU sourced on V<sub>DD\_IO</sub>, can not exceed the absolute maximum rating IV<sub>DD\_IO</sub>.

- The sum of the current sunk by all the I/Os on V<sub>SS\_IO</sub> plus the maximum RUN consumption of the MCU sunk on V<sub>SS\_IO</sub> can not exceed the absolute maximum rating IV<sub>SS\_IO</sub>.

Subject to general operating conditions for  $V_{\text{DD}\ \text{IO}}$  and  $T_{\text{A}}$  unless otherwise specified.

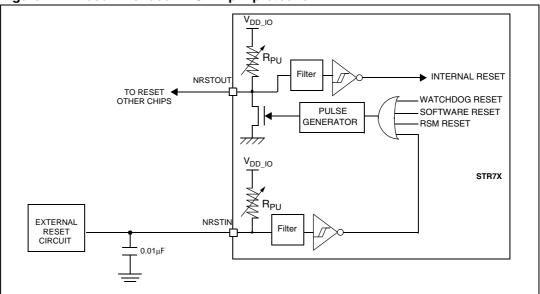

Figure 27. Recommended NRSTIN pin protection

1. The user must ensure that the level on the NRSTIN pin can go below the V<sub>IL(NRSTIN)</sub> max. level specified in NRSTIN and NRSTOUT pins on page 58. Otherwise the reset will not be taken into account internally.

# 6.3.9 TB and TIM timer characteristics

Subject to general operating conditions for  $V_{DD\_IO},\,f_{CK\_SYS},$  and  $T_A$  unless otherwise specified.

Refer to *Section 6.3.8: I/O port pin characteristics on page 54* for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

| Symbol                 | Parameter                                                          |          | Conditions                                            | Min                 | Тур | Max                    | Unit                |

|------------------------|--------------------------------------------------------------------|----------|-------------------------------------------------------|---------------------|-----|------------------------|---------------------|

| t <sub>w(ICAP)in</sub> | Input capture<br>pulse time                                        | TIM0,1,2 |                                                       | 2                   |     |                        | t <sub>CK_TIM</sub> |

|                        |                                                                    |          | f <sub>CK_TIM(MAX)</sub> = f <sub>CK_SYS</sub>        | 1                   |     |                        | t <sub>CK_TIM</sub> |

| ÷                      | Timer<br>resolution                                                | ТВ       | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz | 16.6 <sup>(1)</sup> |     |                        | ns                  |

| t <sub>res(TIM)</sub>  | time <sup>(1)</sup>                                                |          | f <sub>CK_TIM(MAX)</sub> = f <sub>CK_SYS</sub>        | 1                   |     |                        | t <sub>CK_TIM</sub> |

|                        |                                                                    | TIM0,1,2 | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60MHz  | 16.6 <sup>(1)</sup> |     |                        | ns                  |

|                        | Timer                                                              |          | f <sub>CK_TIM(MAX)</sub> = f <sub>CK_SYS</sub>        | 0                   |     | f <sub>CK_TIM</sub> /4 | MHz                 |

| f <sub>EXT</sub>       | f <sub>EXT</sub><br>f <sub>EXT</sub><br>frequency on<br>TI1 or TI2 | TIM0,1,2 | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz | 0                   |     | 15                     | MHz                 |

| Res <sub>TIM</sub>     | Timer<br>resolution                                                |          |                                                       |                     |     | 16                     | bit                 |

|                        | 16-bit<br>Counter clock<br>period when                             |          |                                                       | 1                   |     | 65536                  | t <sub>CK_TIM</sub> |

| toourren               |                                                                    | ТВ       | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz | 0.0166              |     | 1092                   | μs                  |

| t <sub>COUNTER</sub>   | internal clock<br>is selected                                      |          |                                                       | 1                   |     | 65536                  | t <sub>CK_TIM</sub> |

|                        | (16-bit<br>Prescaler)                                              | TIM0,1,2 | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz | 0.0166              |     | 1092                   | μs                  |

|                        |                                                                    |          |                                                       |                     |     | 65536x65536            | t <sub>CK_TIM</sub> |

|                        | Maximum                                                            | ТВ       | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz |                     |     | 71.58                  | S                   |

| t <sub>MAX_COUNT</sub> | Count                                                              |          |                                                       |                     |     | 65536x65536            | t <sub>CK_TIM</sub> |

|                        |                                                                    | TIM0,1,2 | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz |                     |     | 71.58                  | s                   |

Table 36. TB and TIM timers

1. Take into account the frequency limitation due to the I/O speed capability when outputting the PWM to I/O pin, described in : *Output speed on page 57*.

| Symbol                         | Parameter                                                | Conditions                                            | Min                 | Тур               | Мах             | Unit                |

|--------------------------------|----------------------------------------------------------|-------------------------------------------------------|---------------------|-------------------|-----------------|---------------------|

| t <sub>res(PWM)</sub>          | PWM resolution time                                      | $f_{CK_TIM(MAX)} = f_{CK_SYS}$                        | 1                   |                   |                 | $t_{\rm CK_TIM}$    |

|                                |                                                          | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz | 16.6 <sup>(1)</sup> |                   |                 | ns                  |

| Res <sub>PWM</sub>             | PWM resolution                                           |                                                       |                     |                   | 16              | bit                 |

| V <sub>OS</sub> <sup>(1)</sup> | PWM/DAC output step voltage                              | V <sub>DD_IO</sub> =3.3 V, Res=16-bits                |                     | 50 <sup>(1)</sup> |                 | μV                  |

|                                |                                                          | V <sub>DD_IO</sub> =5.0 V, Res=16-bits                |                     | 76 <sup>(1)</sup> |                 | μV                  |

| <sup>t</sup> COUNTER           | Timer clock period<br>when internal clock is<br>selected |                                                       | 1                   |                   | 65536           | t <sub>CK_TIM</sub> |

|                                |                                                          | f <sub>CK_TIM</sub> =60 MHz                           | 0.0166              |                   | 1087            | μs                  |

| <sup>t</sup> MAX_COUNT         | Maximum Possible<br>Count                                |                                                       |                     |                   | 65536x<br>65536 | <sup>t</sup> ск_тім |

|                                |                                                          | $f_{CK_{TIM}} = f_{CK_{SYS}} =$<br>60 MHz             |                     |                   | 71.58           | S                   |

Table 37. PWM Timer (PWM)

1. Take into account the frequency limitation due to the I/O speed capability when outputting the PWM to an I/O pin, as described in : *Output speed on page 57*.

## 6.3.10 Communication interface characteristics

### SSP synchronous serial peripheral in master mode (SPI or TI mode)

General operating conditions: V\_{33}, 3.0V to 3.3V, V18 ~=1.8V,  $C_L\approx 45$  pF.

| Symbol               | Parameter                                 | Condi    | tions | Min | Мах                       | Unit |

|----------------------|-------------------------------------------|----------|-------|-----|---------------------------|------|

| f <sub>SCK</sub>     | SPI clock frequency <sup>(2)</sup>        |          | SSP0  |     | 16                        | MHz  |

|                      | SPI Clock frequency                       |          | SSP1  |     | 8                         |      |

| t <sub>r(SCK)</sub>  | SPI clock rise time                       |          | SSP0  |     | 14                        |      |

|                      |                                           |          | SSP1  |     | 33                        |      |

| +                    | SPI clock fall time                       |          | SSP0  |     | 11                        |      |

| t <sub>f(SCK)</sub>  |                                           |          | SSP1  |     | 30                        |      |

| t <sub>w(SCKH)</sub> | SCK high and low time                     |          | SSP0  |     | 19                        |      |

| t <sub>w(SCKL)</sub> | SOIT High and low time                    |          | SSP1  |     | 30                        |      |

| t <sub>NSSLQV</sub>  | NSS low to Data Output<br>MOSI valid time |          | SSP0  |     | 0.5t <sub>SCK</sub> +15ns |      |

|                      |                                           |          | SSP1  |     | 0.5t <sub>SCK</sub> +30ns |      |

| t <sub>SCKNSSH</sub> | SCK last edge to NSS high                 | CPHA = 0 | SSP0  |     | 0.5t <sub>SCK</sub> +15ns |      |

|                      |                                           |          | SSP1  |     | 0.5t <sub>SCK</sub> +30ns |      |

|                      |                                           | CPHA = 1 | SSP0  |     | t <sub>SCK</sub> +15ns    | ns   |

|                      |                                           |          | SSP1  |     | t <sub>SCK</sub> +30ns    |      |

| taavav               | SCK trigger edge to data                  |          | SSP0  |     | 15                        |      |

| t <sub>sckqv</sub>   | output MOSI valid time                    |          | SSP1  |     | 30                        |      |

| <sup>t</sup> scкqx   | SCK trigger edge to data                  |          | SSP0  | 0   |                           |      |

|                      | output MOSI invalid time                  |          | SSP1  | 0   |                           |      |

| _                    | Data input (MISO) setup                   |          | SSP0  | 25  |                           |      |

| t <sub>su</sub>      | time w.r.t SCK sampling edge              |          | SSP1  | 25  |                           |      |

| t <sub>h</sub>       | Data input (MISO) hold time               |          | SSP0  | 0   |                           |      |

|                      | w.r.t SCK sampling edge                   |          | SSP1  | 0   |                           |      |

Table 38.

SSP master mode characteristics<sup>(1)</sup>

1. Data based on characterisation results, not tested in production.

2. Max frequency for the 2 SSPs is  $f_{PCLK}/2$ ;  $f_{PCLK}$  max = 32 MHz. This takes into account the frequency limitation due to I/O speed capability. SSP0 uses IO4 type while SSP1 uses IO2 type I/Os.

57

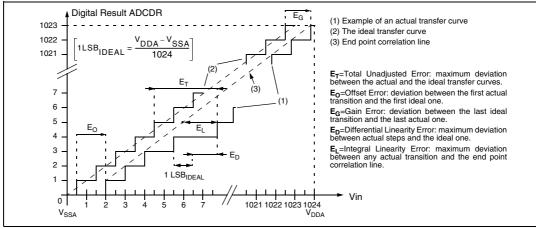

| ADC accuracy with $f_{CK_SYS}$ = 20 MHz, $f_{ADC}$ =8 MHz, $R_{AIN}$ < 10 k $\Omega$<br>This assumes that the ADC is calibrated <sup>(1)</sup> |                                                 |                             |      |      |      |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------|------|------|------|--|

| Symbol                                                                                                                                         | Parameter                                       | Conditions                  | Тур  | Max  | Unit |  |

| IE <sub>T</sub> I                                                                                                                              | Total unadjusted error <sup>(2) (3)</sup>       | V <sub>DDA_ADC</sub> =3.3 V | 1    | 1.2  |      |  |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | 1    | 1.2  |      |  |

| IE <sub>O</sub> I                                                                                                                              | Offset error <sup>(2) (3)</sup>                 | V <sub>DDA_ADC</sub> =3.3 V | 0.15 | 0.5  |      |  |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | 0.15 | 0.5  |      |  |

| E <sub>G</sub>                                                                                                                                 | Gain Error <sup>(2) (3)</sup>                   | V <sub>DDA_ADC</sub> =3.3 V | -0.8 | -0.2 | LSB  |  |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | -0.8 | -0.2 | LOD  |  |

| IE <sub>D</sub> I                                                                                                                              | Differential linearity error <sup>(2) (3)</sup> | V <sub>DDA_ADC</sub> =3.3 V | 0.7  | 0.9  |      |  |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | 0.7  | 0.9  |      |  |

| IELI                                                                                                                                           | Integral linearity error <sup>(2) (3)</sup>     | V <sub>DDA_ADC</sub> =3.3 V | 0.6  | 0.8  |      |  |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | 0.6  | 0.8  |      |  |

#### Table 47. ADC accuracy

1. Calibration is needed once after each power-up.

2. Refer to ADC accuracy vs. negative injection current on page 73

3. ADC Accuracy vs. MCO (Main Clock Output): the ADC accuracy can be significantly degraded when activating the MCO on pin P0.01 while converting an analog channel (especially those which are close to the MCO pin). To avoid this, when an ADC conversion is launched, it is strongly recommended to disable the MCO.

75/84

# 8 Order codes

| Table 49. | Order codes |  |  |

|-----------|-------------|--|--|

|           |             |  |  |

| Order code  | Flash Prog.<br>Memory<br>(Bank 0)<br>Kbytes | Package        | CAN<br>Periph | USB<br>Periph | Nominal<br>Temp. Range<br>(T <sub>A</sub> ) |

|-------------|---------------------------------------------|----------------|---------------|---------------|---------------------------------------------|

| STR750FV0T6 | 64                                          |                |               |               | -40 to +85°C                                |

| STR750FV1T6 | 128                                         | LQFP100 14x14  |               | Yes           |                                             |

| STR750FV2T6 | 256                                         |                | Vee           |               |                                             |

| STR750FV0H6 | 64                                          |                | Yes           |               |                                             |

| STR750FV1H6 | 128                                         | LFBGA100 10x10 |               |               |                                             |

| STR750FV2H6 | 256                                         |                |               |               |                                             |

| STR751FR0T6 | 64                                          |                |               |               |                                             |

| STR751FR1T6 | 128                                         | LQFP64 10x10   |               | Yes           | -40 to +85°C                                |

| STR751FR2T6 | 256                                         |                |               |               |                                             |

| STR751FR0H6 | 64                                          |                | -             |               |                                             |

| STR751FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR751FR2H6 | 256                                         |                |               |               |                                             |

| STR752FR0T6 | 64                                          |                | Yes           | -             | -40 to +85°C                                |

| STR752FR1T6 | 128                                         | LQFP64 10x10   |               |               |                                             |

| STR752FR2T6 | 256                                         |                |               |               |                                             |

| STR752FR0H6 | 64                                          |                |               |               |                                             |

| STR752FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR752FR2H6 | 256                                         |                |               |               |                                             |

| STR752FR0T7 | 64                                          |                |               |               |                                             |

| STR752FR1T7 | 128                                         | LQFP64 10x10   |               | -             |                                             |

| STR752FR2T7 | 256                                         |                | Vaa           |               | -40 to +105°C                               |

| STR752FR0H7 | 64                                          |                | Yes           |               |                                             |

| STR752FR1H7 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR752FR2H7 | 256                                         |                |               |               |                                             |

| STR755FR0T6 | 64                                          |                |               | -             |                                             |

| STR755FR1T6 | 128                                         | LQFP64 10x10   |               |               |                                             |

| STR755FR2T6 | 256                                         |                |               |               | -40 to +85°C                                |

| STR755FR0H6 | 64                                          |                |               |               | -40 10 +00 0                                |

| STR755FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR755FR2H6 | 256                                         |                |               |               |                                             |