Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 60MHz                                                               |

| Connectivity               | I <sup>2</sup> C, SPI, SSI, SSP, UART/USART, USB                    |

| Peripherals                | DMA, PWM, WDT                                                       |

| Number of I/O              | 38                                                                  |

| Program Memory Size        | 64KB (64K x 8)                                                      |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | A/D 11x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-LQFP                                                             |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str751fr0t6 |

|                            |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

periodic interrupt. It is clocked by an external 32.768 kHz oscillator or the internal low power RC oscillator. The RC has a typical frequency of 300 kHz and can be calibrated.

### WDG (watchdog timer)

The watchdog timer is based on a 16-bit downcounter and 8-bit prescaler. It can be used as watchdog to reset the device when a problem occurs, or as free running timer for application time out management.

### Timebase timer (TB)

The timebase timer is based on a 16-bit auto-reload counter and not connected to the I/O pins. It can be used for software triggering, or to implement the scheduler of a real-time operating system.

### Synchronizable standard timers (TIM2:0)

The three standard timers are based on a 16-bit auto-reload counter and feature up to 2 input captures and 2 output compares (for external triggering or time base / time out management). They can work together with the PWM timer via the Timer Link feature for synchronization or event chaining. In reset state, timer Alternate Function I/Os are connected to the same

I/O ports in both 64-pin and 100-pin devices. To optimize timer functions in 64-pin devices, timer Alternate Function I/Os can be connected, or "remapped", to other I/O ports as summarized in *Table 3* and detailed in *Table 6*. This remapping is done by the application via a control register.

|        |                          | Nu      | Number of alternate function I/Os |          |  |  |  |  |  |

|--------|--------------------------|---------|-----------------------------------|----------|--|--|--|--|--|

| Star   | Standard timer functions |         | 64-pin package                    |          |  |  |  |  |  |

|        |                          | package | Default mapping                   | Remapped |  |  |  |  |  |

| ТІМ О  | Input Capture            | 2       | 1                                 | 2        |  |  |  |  |  |

|        | Output Compare/PWM       | 2       | 1                                 | 2        |  |  |  |  |  |

| TIM 1  | Input Capture            | 2       | 1                                 | 1        |  |  |  |  |  |

|        | Output Compare/PWM       | 2       | 1                                 | 1        |  |  |  |  |  |

| TIM 2  | Input Capture            |         | 2                                 | 2        |  |  |  |  |  |

| 111112 | Output Compare/PWM       | 2       | 1                                 | 2        |  |  |  |  |  |

#### Table 3. Standard timer alternate function I/Os

Any of the standard timers can be used to generate PWM outputs. One timer (TIM0) is mapped to a DMA channel.

### Motor control PWM timer (PWM)

The Motor Control PWM Timer (PWM) can be seen as a three-phase PWM multiplexed on 6 channels. The 16-bit PWM generator has full modulation capability (0...100%), edge or centre-aligned patterns and supports dead-time insertion. It has many features in common with the standard TIM timers which has the same architecture and it can work together with the TIM timers via the Timer Link feature for synchronization or event chaining. The PWM timer is mapped to a DMA channel.

|                        | Pin                     | n°                    |                        |                                         |      |                | In       | put   |                   | C          | )utpu     | ıt | y                 |                                                  |                                                  |                                                                     |

|------------------------|-------------------------|-----------------------|------------------------|-----------------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                                | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)             | Alternate                                        | e function                                                          |

| 7                      | D1                      | 5                     | D1                     | P0.29 / TIM1_TI1<br>/ ADC_IN8           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.29                                        | TIM1: Input<br>Capture 1                         | ADC: Analog<br>input 8                                              |

| 8                      | E1                      | 6                     | D2                     | P0.28 /<br>TIM1_OC1                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.28                                        | TIM1: Output Cor                                 | npare 1                                                             |

| 9                      | E5                      | 7                     | D3                     | TEST                                    | Ι    |                |          |       |                   |            |           |    |                   | Reserved, mu                                     | ist be tied to groun                             | d                                                                   |

| 10                     | E4                      | 8                     | D4                     | VSS_IO                                  | S    |                |          |       |                   |            |           |    |                   | Ground Voltag                                    | ge for digital I/Os                              |                                                                     |

| 11                     | E2                      |                       |                        | P0.23 /<br>UART1_RTS /<br>ADC_IN6       | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O2         | x         | x  |                   | Port 0.23                                        | UART1: Ready<br>To Send<br>output <sup>(4)</sup> | ADC analog input<br>6                                               |

| 12                     | F5                      |                       |                        | P2.04 /<br>TIM2_OC1                     | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 2.04                                        | TIM2: Output<br>Compare 1 <sup>(4)</sup>         |                                                                     |

| 13                     | F1                      |                       |                        | P2.03 /<br>UART1_RTS                    | I/O  | т <sub>т</sub> | x        | x     |                   | 02         | x         | x  |                   | Port 2.03                                        | UART1: Ready<br>To Send<br>output <sup>(4)</sup> |                                                                     |

| 14                     | F4                      |                       |                        | P2.02                                   | I/O  | Τ <sub>T</sub> | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.02                                        |                                                  |                                                                     |

| 15                     | E3                      |                       |                        | P0.22 /<br>UART1_CTS /<br>ADC_IN5       | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O2         | x         | x  |                   | Port 0.22                                        | UART1: Clear To<br>Send input                    | ADC: Analog<br>input 5                                              |

| 16                     | F2                      | 9                     | E4                     | P0.21 /<br>UART1_TX                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.21                                        | UART1: Transmit<br>(remappable to P              | data output<br>0.15) <sup>(4)</sup>                                 |

| 17                     | F3                      | 10                    | E3                     | P0.20 /<br>UART1_RX                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.20                                        | UART1: Receive (remappable to P                  | data input<br>0.14) <sup>(4)</sup>                                  |

| 18                     | G3                      | 11                    | E2                     | P1.19 / JTMS                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | O2         | х         | х  |                   | JTAG mode<br>selection<br>input <sup>(6)</sup>   | Port 1.19                                        |                                                                     |

| 19                     | G2                      | 12                    | E1                     | P1.18 / JTCK                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | JTAG clock<br>input <sup>(6)</sup>               | Port 1.18                                        |                                                                     |

| 20                     | H3                      | 13                    | F4                     | P1.17 / JTDO                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | O8         | х         | х  |                   | JTAG data<br>output <sup>(6)</sup>               | Port 1.17                                        |                                                                     |

| 21                     | H2                      | 14                    | F3                     | P1.16 / JTDI                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | JTAG data<br>input <sup>(6)</sup>                | Port 1.16                                        |                                                                     |

| 22                     | G1                      | 15                    | F2                     | NJTRST                                  | Ι    | TT             |          |       |                   |            |           |    |                   | JTAG reset in                                    | G reset input <sup>(5)</sup>                     |                                                                     |

| 23                     | G4                      |                       |                        | P2.01                                   | I/O  | $T_T$          | х        | х     |                   | 02         | х         | Х  |                   | Port 2.01                                        |                                                  |                                                                     |

| 24                     | G5                      |                       |                        | P2.00                                   | I/O  | TT             | X        | х     |                   | O2         | х         | х  |                   | Port 2.00                                        |                                                  |                                                                     |

|                        |                         |                       |                        |                                         |      |                |          |       |                   |            |           |    |                   | ITAC                                             | Port 0.13                                        |                                                                     |

| 25                     | H1                      | 16                    | F1                     | P0.13 / RTCK /<br>UART0_RTS<br>UART2_TX | I/O  | Τ <sub>Τ</sub> | х        | x     |                   | O8         | х         | х  |                   | JTAG<br>return<br>clock<br>output <sup>(6)</sup> | UART0: Ready<br>To Send<br>output <sup>(4)</sup> | UART2: Transmit<br>Data output<br>(when<br>remapped) <sup>(8)</sup> |

## Table 6. STR750F pin description (continued)

|                        | Pin                     | n°                    |                        |                      |      |                | In       | put   |                   | С          | utpu      | ıt | ۲<br>ک            |                                                                                                                                                                                                                                              |                                                                                                                                                                                                |  |

|------------------------|-------------------------|-----------------------|------------------------|----------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name             | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)                                                                                                                                                                                                         | Alternate function                                                                                                                                                                             |  |

| 43                     | H9                      |                       |                        | P2.16                | I/O  | Τ <sub>T</sub> | х        | Х     |                   | 02         | Х         | Х  |                   | Port 2.16                                                                                                                                                                                                                                    |                                                                                                                                                                                                |  |

| 44                     | J9                      | 27                    | G5                     | VDD_IO               | S    |                |          |       |                   |            |           |    |                   | Supply voltag                                                                                                                                                                                                                                | e for digital I/Os                                                                                                                                                                             |  |

| 45                     | K9                      | 28                    | G7                     | VDDA_PLL             | S    |                |          |       |                   |            |           |    |                   | Supply voltag                                                                                                                                                                                                                                | e for PLL                                                                                                                                                                                      |  |

| 46                     | K8                      | 29                    | H7                     | XT2                  |      |                |          |       |                   |            |           |    |                   | 4 MHz main c                                                                                                                                                                                                                                 | oscillator                                                                                                                                                                                     |  |

| 47                     | K7                      | 30                    | H8                     | XT1                  |      |                |          |       |                   |            |           |    |                   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                |  |

| 48                     | J10                     | 31                    | G6                     | VSS_IO               | S    |                |          |       |                   |            |           |    |                   | Ground voltag                                                                                                                                                                                                                                | ge for digital I/Os                                                                                                                                                                            |  |

| 49                     | K10                     | 32                    | G8                     | VSSA_PLL             | S    |                |          |       |                   |            |           |    |                   | Ground voltag                                                                                                                                                                                                                                | ge for PLL                                                                                                                                                                                     |  |

| 50                     | J8                      |                       |                        | P2.15                | I/O  | $T_T$          | х        | х     |                   | O2         | Х         | Х  |                   | Port 2.15                                                                                                                                                                                                                                    |                                                                                                                                                                                                |  |

| 51                     | H8                      |                       |                        | P2.14                | I/O  | Τ <sub>T</sub> | х        | х     |                   | O2         | Х         | Х  |                   | Port 2.14                                                                                                                                                                                                                                    |                                                                                                                                                                                                |  |

| 52                     | G8                      | 33                    | F5                     | V18REG               | S    |                |          |       |                   |            |           |    |                   | Stabilization for main voltage regulator. Requires<br>external capacitors of at least 10µF between<br>V18REG and VSS18. See <i>Figure 4.2</i> .<br>To be connected to the 1.8V external power supp<br>when embedded regulators are not used, |                                                                                                                                                                                                |  |

| 53                     | F8                      | 34                    | F6                     | VSS18                | S    |                |          |       |                   |            |           |    |                   | Ground Voltage for the main voltage regulator                                                                                                                                                                                                |                                                                                                                                                                                                |  |

| 54                     | F9                      | 35                    | F7                     | VSSBKP               | S    |                |          |       |                   |            |           |    |                   | Stabilization f                                                                                                                                                                                                                              | or low power voltage regulator.                                                                                                                                                                |  |

| 55                     | G9                      | 36                    | E7                     | V18BKP               | S    |                |          |       |                   |            |           |    |                   | Requires extended<br>between V18<br>To be connect                                                                                                                                                                                            | ge for the low power voltage regulator.<br>ernal capacitors of at least 1µF<br>BKP and VSSBKP. See <i>Figure 4.2.</i><br>ted to the 1.8V external power supply<br>ded regulators are not used, |  |

| 56                     | H10                     | 37                    | F8                     | XRTC1                |      |                |          |       |                   |            |           |    | х                 |                                                                                                                                                                                                                                              |                                                                                                                                                                                                |  |

| 57                     | G10                     | 38                    | E8                     | XRTC2                |      |                |          |       |                   |            |           |    | х                 | 32 KHZ OSCIII                                                                                                                                                                                                                                | ator for Realtime Clock                                                                                                                                                                        |  |

| 58                     | E7                      | 39                    | E5                     | NRSTOUT              | 0    |                |          |       |                   |            |           |    | х                 | Reset output                                                                                                                                                                                                                                 |                                                                                                                                                                                                |  |

| 59                     | E9                      | 40                    | E6                     | NRSTIN               | I    | Τ <sub>Τ</sub> |          |       |                   |            |           |    | х                 | Reset input                                                                                                                                                                                                                                  |                                                                                                                                                                                                |  |

| 60                     | D6                      |                       |                        | P1.15 /<br>WKP_STDBY | I    | Τ <sub>Τ</sub> | х        |       | EIT15             |            |           |    | х                 | Port 1.15                                                                                                                                                                                                                                    | Wake-up from STANDBY input pin                                                                                                                                                                 |  |

| 61                     | B8                      |                       |                        | P2.13                | I/O  | Τ <sub>T</sub> | х        | х     |                   | O2         | Х         | Х  |                   | Port 2.13                                                                                                                                                                                                                                    |                                                                                                                                                                                                |  |

| 62                     | D9                      |                       |                        | P2.12                | I/O  | TT             | x        | х     |                   | 02         | Х         | Х  |                   | Port 2.12                                                                                                                                                                                                                                    |                                                                                                                                                                                                |  |

| 63                     | F10                     | 41<br>(7)             | D8<br>(7)              | P0.15 / CAN_TX       | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.15                                                                                                                                                                                                                                    | CAN: Transmit data output                                                                                                                                                                      |  |

| 64                     | E10                     | 42<br>(7)             | C8<br>(7)              | P0.14 / CAN_RX       | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT5              | O2         | х         | х  |                   | Port 0.14 CAN: Receive data input                                                                                                                                                                                                            |                                                                                                                                                                                                |  |

| 65                     | D10                     | 41<br>(7)             | D8<br>(7)              | USB_DN               | I/O  |                |          |       |                   |            |           |    |                   | USB: bidirectional data (data -)                                                                                                                                                                                                             |                                                                                                                                                                                                |  |

| 66                     | C10                     | 42<br>(7)             | C8<br>(7)              | USB_DP               | I/O  |                |          |       |                   |            |           |    |                   | USB: bidirectional data (data +)                                                                                                                                                                                                             |                                                                                                                                                                                                |  |

| 67                     | B9                      | 43                    | B8                     | P1.03 / TIM2_TI2     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | x         | x  |                   | Port 1.03                                                                                                                                                                                                                                    | TIM2: Input Capture / trigger /<br>external clock 2 (remappable to<br>P0.07) <sup>(8)</sup>                                                                                                    |  |

## Table 6. STR750F pin description (continued)

|                        | Pin                     | n°                    |                        |                               |      |                | In       | put   |                   | C          | )utpu     | ıt | y                 |                                                       |                                                                                                                                                                                                                           |                        |

|------------------------|-------------------------|-----------------------|------------------------|-------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                      | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)                  | Alternate                                                                                                                                                                                                                 | e function             |

| 91                     | A4                      | 59                    | A3                     | P1.04 / PWM3N /<br>ADC_IN9    | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | х         | х  |                   | Port 1.04                                             | PWM: PWM3<br>complementary<br>output <sup>(4)</sup>                                                                                                                                                                       | ADC: analog<br>input 9 |

| 92                     | A3                      |                       |                        | P1.14 /<br>ADC_IN15           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O8         | х         | х  |                   | Port 1.14                                             | ADC: analog inpu                                                                                                                                                                                                          | t 15                   |

| 93                     | A2                      |                       |                        | P1.13 /<br>ADC_IN14           | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT13             | O8         | х         | х  |                   | Port 1.13                                             | ADC: analog input 14                                                                                                                                                                                                      |                        |

| 94                     | D5                      |                       |                        | P1.01 / TIM0_TI2              | I/O  | TT             | x        | х     |                   | 02         | x         | x  |                   | Port 1.01                                             | TIM0: Input Capture / trigger /<br>external clock 2 (remappable to<br>P0.05) <sup>(8)</sup>                                                                                                                               |                        |

| 95                     | E6                      |                       |                        | P1.00 /<br>TIM0_OC2           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 1.00                                             | TIM0: Output com<br>(remappable to Po                                                                                                                                                                                     |                        |

| 96                     | C4                      | 60                    | C4                     | V18                           | S    |                |          |       |                   |            |           |    |                   | external capa<br>See <i>Figure 4.</i><br>To be connec | tabilization for main voltage regulator. Requires<br>tternal capacitors 33nF between V18 and VSS18.<br>ee <i>Figure 4.2.</i><br>b be connected to the 1.8V external power supply<br>hen embedded regulators are not used. |                        |

| 97                     | D4                      | 61                    | C5                     | VSS18                         | S    |                |          |       |                   |            |           |    |                   | Ground Voltage for the main voltage regulator.        |                                                                                                                                                                                                                           | age regulator.         |

| 98                     | D3                      | 62                    | A2                     | VSS_IO                        | S    |                |          |       |                   |            |           |    |                   | Ground Voltage for digital I/Os                       |                                                                                                                                                                                                                           |                        |

| 99                     | C3                      | 63                    | B2                     | VDD_IO                        | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                                         | Supply Voltage for digital I/Os                                                                                                                                                                                           |                        |

| 100                    | A1                      | 64                    | A1                     | P0.03 / TIM2_TI1<br>/ ADC_IN1 | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | 02         | x         | x  |                   | Port 0.03                                             | TIM2: Input<br>Capture / trigger<br>/ external clock 1                                                                                                                                                                    | ADC: analog<br>input 1 |

Table 6. STR750F pin description (continued)

1. For STR755FVx part numbers, the USB pins must be left unconnected.

2. The non available pins on LQPFP64 and LFBGA64 packages are internally tied to low level.

3. None of the I/Os are True Open Drain: when configured as Open Drain, there is always a protection diode between the I/O pin and VDD\_IO.

4. In the 100-pin package, this Alternate Function is duplicated on two ports. You can configure one port to use this AF, the other port is then free for general purpose I/O (GPIO), external interrupt/wake-up lines, or analog input (ADC\_IN) where these functions are listed in the table.

5. It is mandatory that the NJTRST pin is reset to ground during the power-up phase. It is recommended to connect this pin to NRSTOUT pin (if available) or NRSTIN.

After reset, these pins are enabled as JTAG alternate function see (*Port reset state on page 16*). To use these ports as general purpose I/O (GPIO), the DBGOFF control bit in the GPIO\_REMAPOR register must be set by software (in this case, debugging these I/Os via JTAG is not possible).

7. There are two different TQFP and BGA 64-pin packages: in the first one, pins 41 and 42 are mapped to USB DN/DP while for the second one, they are mapped to P0.15/CAN\_TX and P0.14/CAN\_RX.

8. For details on remapping these alternate functions, refer to the GPIO\_REMAPOR register description.

# 6 Electrical parameters

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_Amax$  (given by the selected temperature range).

Data based on product characterisation, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A=25^{\circ}$  C,  $V_{DD_{-}IO}=3.3$  V (for the 3.0 V $\leq$ V\_{DD\_{-}IO} $\leq$ 3.6 V voltage range) and V<sub>18</sub>=1.8 V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

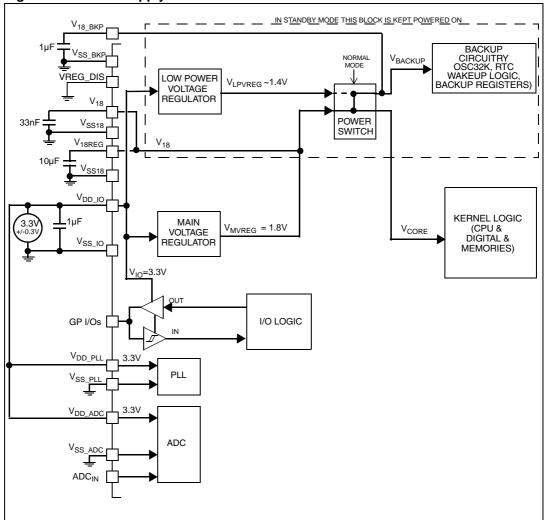

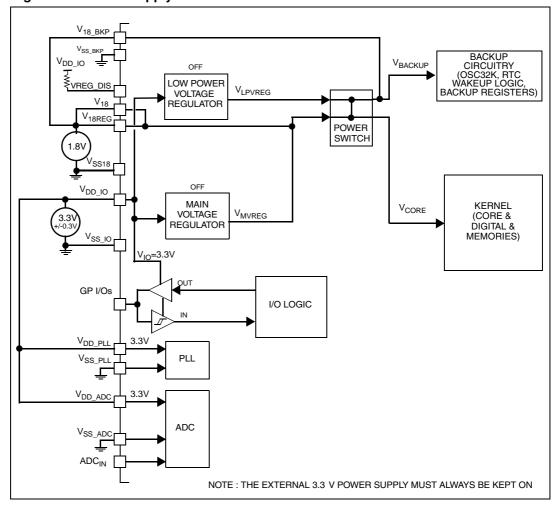

### 6.1.6 Power supply schemes

When mentioned, some electrical parameters can refer to a dedicated power scheme among the four possibilities. The four different power schemes are described below.

### Power supply scheme 1: Single external 3.3 V power source

Figure 8. Power supply scheme 1

### Figure 9. Power supply scheme 2

Power supply scheme 2: Dual external 1.8V and 3.3V supply

### 6.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

|                     | oporating contained                           | no at ponor ap / ponor ao    |                    |     |                    |      |

|---------------------|-----------------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| Symbol              | Parameter                                     | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

| turn in             | V <sub>DD IO</sub> rise time rate             |                              | 20                 |     |                    | μs/V |

| t <sub>VDD_IO</sub> | VDD_IO lise time late                         |                              |                    |     | 20                 | ms/V |

| t                   | V <sub>18</sub> rise time rate <sup>(1)</sup> | When 1.8 V power is supplied | 20                 |     |                    | μs/V |

| t <sub>V18</sub>    |                                               | externally                   |                    |     | 20                 | ms/V |

#### Table 11. Operating conditions at power-up / power-down

1. Data guaranteed by characterization, not tested in production.

## 6.3.3 Embedded voltage regulators

Subject to general operating conditions for  $V_{DD \ IO}$ , and  $T_A$

| Symbol                      | Parameter                                                                  | Conditions                                 | Min  | Тур  | Max  | Unit |

|-----------------------------|----------------------------------------------------------------------------|--------------------------------------------|------|------|------|------|

| V <sub>MVREG</sub>          | MVREG power supply <sup>(1)</sup>                                          | load <150 mA                               | 1.65 | 1.80 | 1.95 | V    |

| V <sub>LPVREG</sub>         | LPVREG power supply <sup>(2)</sup>                                         | load <10 mA                                | 1.30 | 1.40 | 1.50 | V    |

| t                           | Voltage Regulators start-up<br>time (to reach 90% of final V <sub>18</sub> | V <sub>DD_IO</sub> rise<br>slope = 20 μs/V |      | 80   |      | μs   |

| t <sub>vreg_pwrup</sub> (1) | value) at $V_{DD_{IO}}$ power-up <sup>(3)</sup>                            | V <sub>DD_IO</sub> rise<br>slope = 20 ms/V |      | 35   |      | ms   |

V<sub>MVREG</sub> is observed on the V<sub>18</sub>, V<sub>18REG</sub> and V<sub>18BKP</sub> pins except in the following case:

In STOP mode with MVREG OFF (LP\_PARAM13 bit). See note 2.

In STANDBY mode. See note 2.

2. In STANDBY mode,  $V_{LPVREG}$  is observed on the  $V_{18BKP}$  pin In STOP mode,  $V_{LPVREG}$  is observed on the  $V_{18}, V_{18REG}$  and  $V_{18BKP}$  pins.

Once V<sub>DD\_IO</sub> has reached 3.0 V, the RSM (Regulator Startup Monitor) generates an internal RESET during this start-up time.

300

250

200

150 100

50

0

-40

25

IStop (uA)

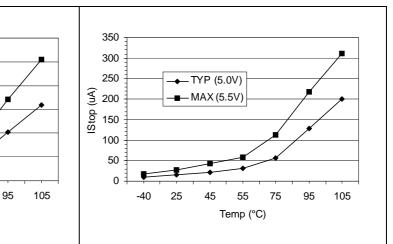

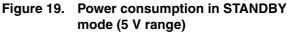

Figure 16. Power consumption in STOP mode Figure 17. Pow in Single supply scheme (3.3 V Sing range)

Figure 18. Power consumption in STANDBY mode (3.3 V range)

-TYP (3.3V)

MAX (3.6V)

45

55

Temp (°C)

75

7. Power consumption in STOP mode Single supply scheme (5 V range)

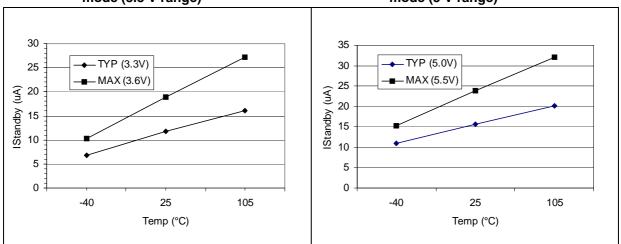

### XRTC1 external clock source

Subject to general operating conditions for  $V_{\text{DD}\_\text{IO}}\text{,}$  and  $T_{\text{A}}\text{.}$

Table 21. XRTC1 external clock source

| Symbol                                           | Parameter                                 | Conditions <sup>(1)</sup>                                | Min                    | Тур    | Max                    | Unit |

|--------------------------------------------------|-------------------------------------------|----------------------------------------------------------|------------------------|--------|------------------------|------|

| f <sub>XRTC1</sub>                               | External clock source<br>frequency        |                                                          |                        | 32.768 | 500                    | kHz  |

| V <sub>XRTC1H</sub>                              | XRTC1 input pin high<br>level voltage     |                                                          | 0.7xV <sub>DD_IO</sub> |        | V <sub>DD_IO</sub>     | V    |

| V <sub>XRTC1L</sub>                              | XRTC1 input pin low<br>level voltage      | see Figure 20                                            | V <sub>SS</sub>        |        | 0.3xV <sub>DD_IO</sub> | v    |

| t <sub>w(XRTC1H)</sub><br>t <sub>w(XRTC1L)</sub> | XRTC1 high or low<br>time <sup>(2)</sup>  |                                                          | 900                    |        |                        | ns   |

| t <sub>r(XRTC1)</sub><br>t <sub>f(XRTC1)</sub>   | XRTC1 rise or fall time <sup>(2)</sup>    |                                                          |                        |        | 50                     | 115  |

| ΙL                                               | XRTCx Input leakage<br>current            | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD_I</sub><br>o |                        |        | ±1                     | μA   |

| C <sub>IN(RTC1)</sub>                            | XRTC1 input<br>capacitance <sup>(2)</sup> |                                                          |                        | 5      |                        | pF   |

| DuCy <sub>(RTC1)</sub>                           | Duty cycle                                |                                                          | 30                     |        | 70                     | %    |

1. Data based on typical application software.

2. Data based on design simulation and/or technology characteristics, not tested in production.

#### Figure 20. Typical application with an external clock source

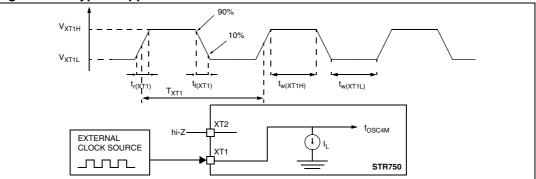

### 4/8 MHz crystal / ceramic resonator oscillator (XT1/XT2)

The STR750 system clock or the input of the PLL can be supplied by a OSC4M which is a 4 MHz clock generated from a 4 MHz or 8 MHz crystal or ceramic resonator. If using an 8 MHz oscillator, software set the XTDIV bit to enable a divider by 2 and generate a 4 MHz OSC4M clock. All the information given in this paragraph are based on product characterisation with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                                            | Parameter                                                                                                                   | Conditions                                                                                                                                     | Min | Тур | Max | Unit |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC4M</sub>                                | Oscillator frequency                                                                                                        | 4 MHz Crystal/Resonator Oscillator<br>connected on XT1/XT2 XTDIV=0<br>or<br>8 MHz Crystal/Resonator Oscillator<br>connected on XT1/XT2 XTDIV=1 |     | 4   |     | MHz  |

| R <sub>F</sub>                                    | Feedback resistor                                                                                                           |                                                                                                                                                | 200 | 240 | 270 | kΩ   |

| C <sub>L1</sub> <sup>(2)</sup><br>C <sub>L2</sub> | Recommended load<br>capacitance versus equivalent<br>serial resistance of the crystal or<br>ceramic resonator $(R_S)^{(3)}$ | R <sub>S</sub> =200Ω                                                                                                                           |     |     | 60  | pF   |

| i <sub>2</sub>                                    | XT2 driving current                                                                                                         | V <sub>DD_IO</sub> =3.3 V or 5.0 V                                                                                                             |     | 425 |     | μA   |

| t <sub>SU(OSC4M)</sub> <sup>(4)</sup>             | Startup time at V <sub>DD_IO</sub> power-up                                                                                 |                                                                                                                                                |     | 1   |     | ms   |

| Table 22. | 4/8 MHz crystal | / ceramic resonator oscillato | or (XT1/XT2) <sup>(1)</sup> |

|-----------|-----------------|-------------------------------|-----------------------------|

|-----------|-----------------|-------------------------------|-----------------------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5-pF to 25-pF range (typ.) designed for high-frequency applications and selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the 2. same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included when sizing  $C_{L1}$  and  $C_{L2}$  (10 pF can be used as a rough estimate of the combined pin and board capacitance).

- 3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- $t_{SU(OSC4M)}$  is the typical start-up time measured from the moment  $V_{DD \ IO}$  is powered (with a quick  $V_{DD \ IO}$  ramp-up from 0 to 3.3V (<50µs) to a stabilized 4MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal/ceramic resonator manufacturer.

Figure 21. Typical application with a 4 or 8 MHz crystal or ceramic resonator

### **PLL characteristics**

Subject to general operating conditions for  $V_{DD \ IO}$ , and  $T_A$ .

| Table 24. PLL characteristics | Table 24. | PLL | characteristics |

|-------------------------------|-----------|-----|-----------------|

|-------------------------------|-----------|-----|-----------------|

| Symbol                                  | Parameter                                          | Test Conditions                                                     | Value |     |                    | Unit |

|-----------------------------------------|----------------------------------------------------|---------------------------------------------------------------------|-------|-----|--------------------|------|

| Symbol                                  | Falameter                                          | Test Conditions                                                     | Min   | Тур | Max <sup>(1)</sup> | Unit |

| f                                       | PLL input clock                                    |                                                                     |       | 4.0 |                    | MHz  |

| f <sub>PLL_IN</sub>                     | PLL input clock duty cycle                         |                                                                     | 40    |     | 60                 | %    |

| f <sub>PLL_OUT</sub>                    | PLL multiplier output clock                        | f <sub>PLL_IN</sub> x 24                                            |       |     | 165                | MHz  |

| f <sub>VCO</sub>                        | VCO frequency range                                | When PLL<br>operates (locked)                                       | 336   |     | 960                | MHz  |

| t <sub>LOCK</sub>                       | PLL lock time                                      |                                                                     |       |     | 300                | μs   |

| ∆t <sub>JITTER1</sub> <sup>(2)(3)</sup> | Single period jitter (+/-3 $\Sigma$ peak to peak)  | $f_{PLL_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable  |       |     | +/-250             | ps   |

| ∆t <sub>JITTER2</sub> <sup>(2)(3)</sup> | Long term jitter (+/- $3\Sigma$ peak to peak)      | $f_{PLL_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable  |       |     | +/-2.5             | ns   |

| ∆t <sub>JITTER3</sub> <sup>(2)(3)</sup> | Cycle to cycle jitter (+/- $3\Sigma$ peak to peak) | $f_{PLL\_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable |       |     | +/-500             | ps   |

1. Data based on product characterisation, not tested in production.

2. Refer to jitter terminology in : PLL characteristics on page 47 for details on how jitter is specified.

The jitter specification holds true only up to 50mV (peak-to-peak) noise on V<sub>DDA\_PLL</sub> and V<sub>18</sub> supplies. Jitter will increase if the noise is more than 50mV. In addition, it assumes that the input clock has no jitter.

4. The PLL parameters (MX1, MX0, PRESC1, PRESC2) must respect the constraints described in: PLL characteristics on page 47.

### Internal RC oscillators (FREEOSC & LPOSC)

Subject to general operating conditions for  $V_{DD}$  IO, and  $T_A$ .

### Table 25. Internal RC oscillators (FREEOSC & LPOSC)

| Symbol                  | Parameter                    | Conditions | Min | Тур | Max | Unit |

|-------------------------|------------------------------|------------|-----|-----|-----|------|

| f <sub>CK_FREEOSC</sub> | FREEOSC Oscillator Frequency |            | 3   | 5   | 8   | MHz  |

| f <sub>CK_LPOSC</sub>   | LPOSC Oscillator Frequency   |            | 150 | 300 | 500 | kHz  |

| Symbol                                               | Parameter                   | Conditions                                            | Min                 | Тур               | Max             | Unit                |

|------------------------------------------------------|-----------------------------|-------------------------------------------------------|---------------------|-------------------|-----------------|---------------------|

| t <sub>res(PWM)</sub>                                | PWM resolution time         | $f_{CK_TIM(MAX)} = f_{CK_SYS}$                        | 1                   |                   |                 | $t_{\rm CK_TIM}$    |

|                                                      |                             | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz | 16.6 <sup>(1)</sup> |                   |                 | ns                  |

| Res <sub>PWM</sub>                                   | PWM resolution              |                                                       |                     |                   | 16              | bit                 |

| V <sub>OS</sub> <sup>(1)</sup>                       | PWM/DAC output step voltage | V <sub>DD_IO</sub> =3.3 V, Res=16-bits                |                     | 50 <sup>(1)</sup> |                 | μV                  |

|                                                      |                             | V <sub>DD_IO</sub> =5.0 V, Res=16-bits                |                     | 76 <sup>(1)</sup> |                 | μV                  |

|                                                      | Timer clock period          |                                                       | 1                   |                   | 65536           | t <sub>CK_TIM</sub> |

| t <sub>COUNTER</sub> when internal clock is selected | f <sub>CK_TIM</sub> =60 MHz | 0.0166                                                |                     | 1087              | μs              |                     |

| <sup>t</sup> MAX_COUNT                               | Maximum Possible            |                                                       |                     |                   | 65536x<br>65536 | <sup>t</sup> ск_тім |

|                                                      | Count                       | $f_{CK_{TIM}} = f_{CK_{SYS}} =$<br>60 MHz             |                     |                   | 71.58           | S                   |

Table 37. PWM Timer (PWM)

1. Take into account the frequency limitation due to the I/O speed capability when outputting the PWM to an I/O pin, as described in : *Output speed on page 57*.

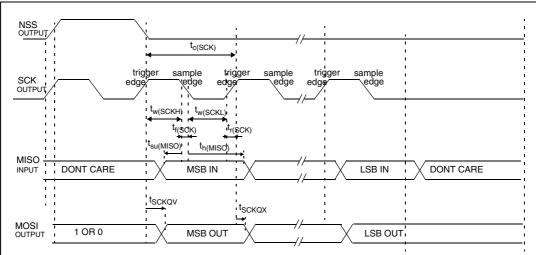

Figure 31. TI configuration - master mode, single transfer

| t <sub>c(S0</sub>           | СК)                              | t <sub>c(SCK)</sub>           |                               |          |

|-----------------------------|----------------------------------|-------------------------------|-------------------------------|----------|

| NSS OUTPUT                  | //                               |                               |                               | 1<br>1   |

| SCK OUTPUT                  | e trigger, sample trigger sample | trigger sample trigger sample | trigger sample trigger sample |          |

|                             | XXX                              |                               |                               | OUT      |

| MISO INPUT DONT CARE MSB IN | X/X                              |                               | N X // LSB                    |          |

|                             | FRAME 1                          | <b>.</b>                      | FRAME 2                       | <b>→</b> |

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |

|------------------|---------------------------------|--------------------------------|-----|-----|------|

| t <sub>rfm</sub> | Rise/ Fall Time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |

| V <sub>CRS</sub> | Output signal Crossover Voltage |                                | 1.3 | 2.0 | V    |

Table 44. USB: Full speed electrical characteristics

Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

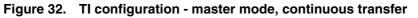

### **General PCB design guidelines**

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

- Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

- Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing 0.1 μF and optionally, if needed 10 pF capacitors as close as possible to the STR7 power supply pins and a 1 to 10 μF capacitor close to the power source (see *Figure 43*).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>DDA\_ADC</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs near the A/D input being converted.

#### Software filtering of spurious conversion results

For EMC performance reasons, it is recommended to filter A/D conversion outliers using software filtering techniques.

#### Figure 43. Power supply filtering

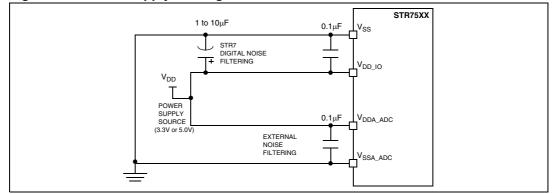

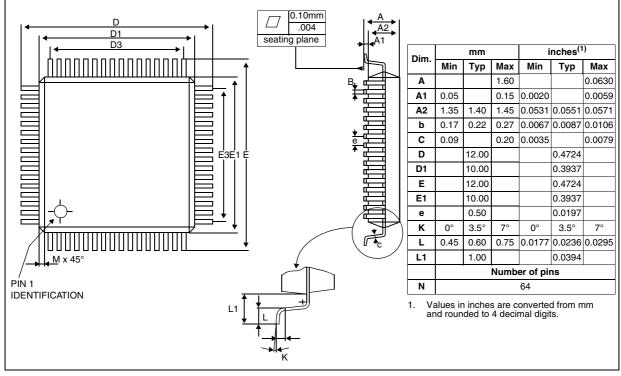

# 7 Package characteristics

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 7.1 Package mechanical data

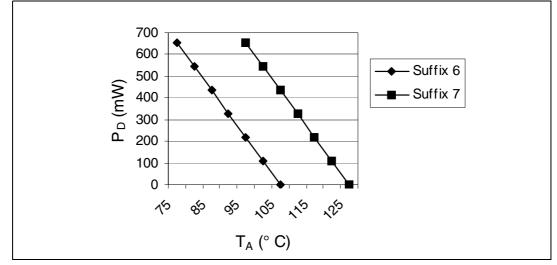

## 7.2 Thermal characteristics

The maximum chip junction temperature (T<sub>Jmax</sub>) must never exceed the values given in *Table 10: General operating conditions on page 34*.

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

Where:

- T<sub>Amax</sub> is the maximum Ambient Temperature in °C,

- $\Theta_{JA}$  is the Package Junction-to-Ambient Thermal Resistance, in ° C/W,

- $P_{Dmax}$  is the sum of  $P_{INTmax}$  and  $P_{I/Omax} (P_{Dmax} = P_{INTmax} + P_{I/Omax})$ ,

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum Power Dissipation on Output Pins. Where:

$\mathsf{P}_{\mathsf{I}/\mathsf{Omax}} = \Sigma (\mathsf{V}_{\mathsf{OL}}^* \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}}^* \mathsf{V}_{\mathsf{OH}})^* \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

Table 48.Thermal characteristics<sup>(1)</sup>

| Symbol        | Parameter                                                                   | Value | Unit |

|---------------|-----------------------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LQFP 100 - 14 x 14 mm / 0.5 mm pitch | 46    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LQFP 64 - 10 x 10 mm / 0.5 mm pitch  | 45    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LFBGA 64 - 8 x 8 x 1.7mm             | 58    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LFBGA 100 - 10 x 10 x 1.7mm          | 41    | °C/W |

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

### 7.2.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

### 7.2.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the order code *Table 49: Order codes on page 81*.

The following example shows how to calculate the temperature range needed for a given application.

Assuming the following application conditions:

Maximum ambient temperature T<sub>Amax</sub>= 82 °C (measured according to JESD51-2), I<sub>DDmax</sub>=8 mA, V<sub>DD</sub> = 5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V

$P_{INTmax} = 8 \text{ mA x 5 V} = 400 \text{ mW}$

$$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{V} = 64 \text{ mW}$$

This gives: P<sub>INTmax</sub>= 400 mW and P<sub>IOmax</sub> 64 mW:

$P_{Dmax} = 400 \text{ mW} + 64 \text{ mW}$

Thus:  $P_{Dmax} = 464 \text{ mW}$

Using the values obtained in Table 48  $T_{Jmax}$  is calculated as follows:

For LQFP100, 46°C/W

$T_{\text{lmax}} = 82^{\circ} \text{ C} + (46^{\circ} \text{ C/W x } 464 \text{ mW}) = 82^{\circ} \text{C} + 21^{\circ} \text{C} = 103^{\circ} \text{ C}$

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105^\circ$  C). In this case, parts must be ordered at least with the temperature range suffix 6 (see *Table 49: Order codes on page 81*).

- For BGA64, 58°C/W

$T_{Jmax} = 82^{\circ} \text{ C} + (58^{\circ} \text{ C/W x } 464 \text{ mW}) = 82^{\circ} \text{C} + 27^{\circ} \text{C} = 109^{\circ} \text{ C}$

This is within the range of the suffix 7 version parts (-40 <  $T_J$  < 125° C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 49: Order codes on page 81*).

#### Figure 50. LQFP100 P<sub>Dmax</sub> vs T<sub>A</sub>

# 8 Order codes

| Order code  | Flash Prog.<br>Memory<br>(Bank 0)<br>Kbytes | Package        | CAN<br>Periph | USB<br>Periph | Nominal<br>Temp. Range<br>(T <sub>A</sub> ) |

|-------------|---------------------------------------------|----------------|---------------|---------------|---------------------------------------------|

| STR750FV0T6 | 64                                          |                |               |               |                                             |

| STR750FV1T6 | 128                                         | LQFP100 14x14  |               |               |                                             |

| STR750FV2T6 | 256                                         |                |               | Vaa           | 40 to . 95°C                                |

| STR750FV0H6 | 64                                          |                | Yes           | Yes           | -40 to +85°C                                |

| STR750FV1H6 | 128                                         | LFBGA100 10x10 |               |               |                                             |

| STR750FV2H6 | 256                                         |                |               |               |                                             |

| STR751FR0T6 | 64                                          |                |               |               |                                             |

| STR751FR1T6 | 128                                         | LQFP64 10x10   |               | Yes           |                                             |

| STR751FR2T6 | 256                                         |                |               |               | -40 to +85°C                                |

| STR751FR0H6 | 64                                          |                | -             |               | -40 10 +85 C                                |

| STR751FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR751FR2H6 | 256                                         |                |               |               |                                             |

| STR752FR0T6 | 64                                          |                |               | -             |                                             |

| STR752FR1T6 | 128                                         | LQFP64 10x10   | No            |               |                                             |

| STR752FR2T6 | 256                                         |                |               |               |                                             |

| STR752FR0H6 | 64                                          |                | Yes           |               |                                             |

| STR752FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR752FR2H6 | 256                                         |                |               |               |                                             |

| STR752FR0T7 | 64                                          |                |               |               |                                             |

| STR752FR1T7 | 128                                         | LQFP64 10x10   |               | -             |                                             |

| STR752FR2T7 | 256                                         |                | Yes           |               | -40 to +105°C                               |

| STR752FR0H7 | 64                                          |                | 165           |               | -40 10 + 105 C                              |

| STR752FR1H7 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR752FR2H7 | 256                                         |                |               |               |                                             |

| STR755FR0T6 | 64                                          |                |               |               |                                             |

| STR755FR1T6 | 128                                         | LQFP64 10x10   |               |               |                                             |

| STR755FR2T6 | 256                                         |                |               |               | -40 to +85°C                                |

| STR755FR0H6 | 64                                          | -              |               |               | -40 IO +00 O                                |

| STR755FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR755FR2H6 | 256                                         |                |               |               |                                             |