Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 60MHz                                                               |

| Connectivity               | I <sup>2</sup> C, SPI, SSI, SSP, UART/USART, USB                    |

| Peripherals                | DMA, PWM, WDT                                                       |

| Number of I/O              | 38                                                                  |

| Program Memory Size        | 256KB (256K x 8)                                                    |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K × 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | A/D 11x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-LQFP                                                             |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str751fr2t6 |

|                            |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### I<sup>2</sup>C bus

The I<sup>2</sup>C bus interface can operate in multi-master and slave mode. It can support standard and fast modes (up to 400KHz).

#### High speed universal asynch. receiver transmitter (UART)

The three UART interfaces are able to communicate at speeds of up to 2 Mbit/s. They provide hardware management of the CTS and RTS signals and have LIN Master capability.

To optimize the data transfer between the processor and the peripheral, two FIFOs (receive/transmit) of 16 bytes each have been implemented.

One UART can be served by the DMA controller (UART0).

#### Synchronous serial peripheral (SSP)

The two SSPs are able to communicate up to 8 Mbit/s (SSP1) or up to 16 Mbit/s (SSP0) in standard full duplex 4-pin interface mode as a master device or up to 2.66 Mbit/s as a slave device. To optimize the data transfer between the processor and the peripheral, two FIFOs (receive/transmit) of 8 x 16 bit words have been implemented. The SSPs support the Motorola SPI or TI SSI protocols.

One SSP can be served by the DMA controller (SSP0).

#### Controller area network (CAN)

The CAN is compliant with the specification 2.0 part B (active) with a bit rate up to 1Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Up to 32 message objects are handled through an internal RAM buffer. In LQFP64 devices, CAN and USB cannot be connected simultaneously.

#### Universal serial bus (USB)

The STR750F embeds a USB device peripheral compatible with the USB Full speed 12Mbs. The USB interface implements a full speed (12 Mbit/s) function interface. It has software configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock source is generated from the internal main PLL.  $V_{DD}$  must be in the range 3.3V±10% for USB operation.

#### ADC (analog to digital converter)

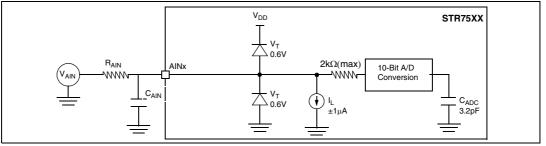

The 10-bit Analog to Digital Converter, converts up to 16 external channels (11 channels in 64-pin devices) in single-shot or scan modes. In scan mode, continuous conversion is performed on a selected group of analog inputs. The minimum conversion time is  $3.75 \ \mu s$  (including the sampling time).

The ADC can be served by the DMA controller.

An analog watchdog feature allows you to very precisely monitor the converted voltage of up to four channels. An IRQ is generated when the converted voltage is outside the programmed thresholds.

The events generated by TIM0, TIM2 and PWM timers can be internally connected to the ADC start trigger, injection trigger, and DMA trigger respectively, to allow the application to synchronize A/D conversion and timers.

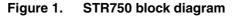

# 3.2 Block diagram

|                        | Pin                     | n°                    |                        |                                         |      |                | In       | put   |                   | C          | )utpu     | ıt | y                 |                                                  |                                                  |                                                                     |

|------------------------|-------------------------|-----------------------|------------------------|-----------------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                                | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)             | Alternate                                        | e function                                                          |

| 7                      | D1                      | 5                     | D1                     | P0.29 / TIM1_TI1<br>/ ADC_IN8           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.29                                        | TIM1: Input<br>Capture 1                         | ADC: Analog<br>input 8                                              |

| 8                      | E1                      | 6                     | D2                     | P0.28 /<br>TIM1_OC1                     | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 0.28                                        | TIM1: Output Cor                                 | npare 1                                                             |

| 9                      | E5                      | 7                     | D3                     | TEST                                    | Ι    |                |          |       |                   |            |           |    |                   | Reserved, mu                                     | ist be tied to groun                             | d                                                                   |

| 10                     | E4                      | 8                     | D4                     | VSS_IO                                  | S    |                |          |       |                   |            |           |    |                   | Ground Voltag                                    | ge for digital I/Os                              |                                                                     |

| 11                     | E2                      |                       |                        | P0.23 /<br>UART1_RTS /<br>ADC_IN6       | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O2         | x         | x  |                   | Port 0.23                                        | UART1: Ready<br>To Send<br>output <sup>(4)</sup> | ADC analog input<br>6                                               |

| 12                     | F5                      |                       |                        | P2.04 /<br>TIM2_OC1                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 2.04                                        | TIM2: Output<br>Compare 1 <sup>(4)</sup>         |                                                                     |

| 13                     | F1                      |                       |                        | P2.03 /<br>UART1_RTS                    | I/O  | т <sub>т</sub> | x        | x     |                   | 02         | x         | x  |                   | Port 2.03                                        | UART1: Ready<br>To Send<br>output <sup>(4)</sup> |                                                                     |

| 14                     | F4                      |                       |                        | P2.02                                   | I/O  | Τ <sub>T</sub> | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.02                                        |                                                  |                                                                     |

| 15                     | E3                      |                       |                        | P0.22 /<br>UART1_CTS /<br>ADC_IN5       | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O2         | x         | x  |                   | Port 0.22                                        | UART1: Clear To<br>Send input                    | ADC: Analog<br>input 5                                              |

| 16                     | F2                      | 9                     | E4                     | P0.21 /<br>UART1_TX                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.21                                        | UART1: Transmit<br>(remappable to P              | data output<br>0.15) <sup>(4)</sup>                                 |

| 17                     | F3                      | 10                    | E3                     | P0.20 /<br>UART1_RX                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.20                                        | UART1: Receive (remappable to P                  | data input<br>0.14) <sup>(4)</sup>                                  |

| 18                     | G3                      | 11                    | E2                     | P1.19 / JTMS                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | O2         | х         | х  |                   | JTAG mode<br>selection<br>input <sup>(6)</sup>   | Port 1.19                                        |                                                                     |

| 19                     | G2                      | 12                    | E1                     | P1.18 / JTCK                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | JTAG clock<br>input <sup>(6)</sup>               | Port 1.18                                        |                                                                     |

| 20                     | H3                      | 13                    | F4                     | P1.17 / JTDO                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | O8         | х         | х  |                   | JTAG data<br>output <sup>(6)</sup>               | Port 1.17                                        |                                                                     |

| 21                     | H2                      | 14                    | F3                     | P1.16 / JTDI                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | JTAG data<br>input <sup>(6)</sup>                | Port 1.16                                        |                                                                     |

| 22                     | G1                      | 15                    | F2                     | NJTRST                                  | Ι    | TT             |          |       |                   |            |           |    |                   | JTAG reset in                                    | put <sup>(5)</sup>                               |                                                                     |

| 23                     | G4                      |                       |                        | P2.01                                   | I/O  | $T_T$          | х        | х     |                   | 02         | х         | Х  |                   | Port 2.01                                        |                                                  |                                                                     |

| 24                     | G5                      |                       |                        | P2.00                                   | I/O  | TT             | X        | х     |                   | O2         | х         | х  |                   | Port 2.00                                        |                                                  |                                                                     |

|                        |                         |                       |                        |                                         |      |                |          |       |                   |            |           |    |                   | ITAC                                             | Port 0.13                                        |                                                                     |

| 25                     | H1                      | 16                    | F1                     | P0.13 / RTCK /<br>UART0_RTS<br>UART2_TX | I/O  | Τ <sub>Τ</sub> | х        | x     |                   | O8         | х         | х  |                   | JTAG<br>return<br>clock<br>output <sup>(6)</sup> | UART0: Ready<br>To Send<br>output <sup>(4)</sup> | UART2: Transmit<br>Data output<br>(when<br>remapped) <sup>(8)</sup> |

# Table 6. STR750F pin description (continued)

|                        | Pin                     | n°                    |                        |                      |      |                | In       | put   |                   | С          | utpu      | ıt | ۲<br>ک            |                                                   |                                                                                                                                                                                                |

|------------------------|-------------------------|-----------------------|------------------------|----------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name             | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)              | Alternate function                                                                                                                                                                             |

| 43                     | H9                      |                       |                        | P2.16                | I/O  | Τ <sub>T</sub> | х        | Х     |                   | 02         | Х         | Х  |                   | Port 2.16                                         |                                                                                                                                                                                                |

| 44                     | J9                      | 27                    | G5                     | VDD_IO               | S    |                |          |       |                   |            |           |    |                   | Supply voltag                                     | e for digital I/Os                                                                                                                                                                             |

| 45                     | K9                      | 28                    | G7                     | VDDA_PLL             | S    |                |          |       |                   |            |           |    |                   | Supply voltag                                     | e for PLL                                                                                                                                                                                      |

| 46                     | K8                      | 29                    | H7                     | XT2                  |      |                |          |       |                   |            |           |    |                   | 4 MHz main c                                      | oscillator                                                                                                                                                                                     |

| 47                     | K7                      | 30                    | H8                     | XT1                  |      |                |          |       |                   |            |           |    |                   |                                                   |                                                                                                                                                                                                |

| 48                     | J10                     | 31                    | G6                     | VSS_IO               | S    |                |          |       |                   |            |           |    |                   | Ground voltag                                     | ge for digital I/Os                                                                                                                                                                            |

| 49                     | K10                     | 32                    | G8                     | VSSA_PLL             | S    |                |          |       |                   |            |           |    |                   | Ground voltag                                     | ge for PLL                                                                                                                                                                                     |

| 50                     | J8                      |                       |                        | P2.15                | I/O  | $T_T$          | х        | х     |                   | O2         | Х         | Х  |                   | Port 2.15                                         |                                                                                                                                                                                                |

| 51                     | H8                      |                       |                        | P2.14                | I/O  | Τ <sub>T</sub> | х        | х     |                   | O2         | Х         | Х  |                   | Port 2.14                                         |                                                                                                                                                                                                |

| 52                     | G8                      | 33                    | F5                     | V18REG               | S    |                |          |       |                   |            |           |    |                   | external capa<br>V18REG and<br>To be connec       | or main voltage regulator. Requires<br>icitors of at least 10µF between<br>VSS18. See <i>Figure 4.2.</i><br>ted to the 1.8V external power supply<br>ded regulators are not used,              |

| 53                     | F8                      | 34                    | F6                     | VSS18                | S    |                |          |       |                   |            |           |    |                   | Ground Volta                                      | ge for the main voltage regulator                                                                                                                                                              |

| 54                     | F9                      | 35                    | F7                     | VSSBKP               | S    |                |          |       |                   |            |           |    |                   | Stabilization f                                   | or low power voltage regulator.                                                                                                                                                                |

| 55                     | G9                      | 36                    | E7                     | V18BKP               | S    |                |          |       |                   |            |           |    |                   | Requires extended<br>between V18<br>To be connect | ge for the low power voltage regulator.<br>ernal capacitors of at least 1µF<br>BKP and VSSBKP. See <i>Figure 4.2.</i><br>ted to the 1.8V external power supply<br>ded regulators are not used, |

| 56                     | H10                     | 37                    | F8                     | XRTC1                |      |                |          |       |                   |            |           |    | х                 |                                                   |                                                                                                                                                                                                |

| 57                     | G10                     | 38                    | E8                     | XRTC2                |      |                |          |       |                   |            |           |    | х                 | 32 KHZ OSCIII                                     | ator for Realtime Clock                                                                                                                                                                        |

| 58                     | E7                      | 39                    | E5                     | NRSTOUT              | 0    |                |          |       |                   |            |           |    | х                 | Reset output                                      |                                                                                                                                                                                                |

| 59                     | E9                      | 40                    | E6                     | NRSTIN               | I    | Τ <sub>Τ</sub> |          |       |                   |            |           |    | х                 | Reset input                                       |                                                                                                                                                                                                |

| 60                     | D6                      |                       |                        | P1.15 /<br>WKP_STDBY | I    | Τ <sub>Τ</sub> | х        |       | EIT15             |            |           |    | х                 | Port 1.15                                         | Wake-up from STANDBY input pin                                                                                                                                                                 |

| 61                     | B8                      |                       |                        | P2.13                | I/O  | Τ <sub>T</sub> | х        | х     |                   | O2         | Х         | Х  |                   | Port 2.13                                         |                                                                                                                                                                                                |

| 62                     | D9                      |                       |                        | P2.12                | I/O  | TT             | x        | х     |                   | 02         | Х         | Х  |                   | Port 2.12                                         |                                                                                                                                                                                                |

| 63                     | F10                     | 41<br>(7)             | D8<br>(7)              | P0.15 / CAN_TX       | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.15                                         | CAN: Transmit data output                                                                                                                                                                      |

| 64                     | E10                     | 42<br>(7)             | C8<br>(7)              | P0.14 / CAN_RX       | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT5              | O2         | х         | х  |                   | Port 0.14                                         | CAN: Receive data input                                                                                                                                                                        |

| 65                     | D10                     | 41<br>(7)             | D8<br>(7)              | USB_DN               | I/O  |                |          |       |                   |            |           |    |                   | USB: bidirect                                     | ional data (data -)                                                                                                                                                                            |

| 66                     | C10                     | 42<br>(7)             | C8<br>(7)              | USB_DP               | I/O  |                |          |       |                   |            |           |    |                   | USB: bidirect                                     | ional data (data +)                                                                                                                                                                            |

| 67                     | B9                      | 43                    | B8                     | P1.03 / TIM2_TI2     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | x         | x  |                   | Port 1.03                                         | TIM2: Input Capture / trigger /<br>external clock 2 (remappable to<br>P0.07) <sup>(8)</sup>                                                                                                    |

# Table 6. STR750F pin description (continued)

|                        | Pin                     | n°                    |                        |                                    |      |                | In       | put   |                   | C          | )utpu     | ıt | Š                 |                                      |                                                     |                                                    |

|------------------------|-------------------------|-----------------------|------------------------|------------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------|-----------------------------------------------------|----------------------------------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                           | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset) | Alternate                                           | e function                                         |

| 68                     | A10                     |                       |                        | P1.02 /<br>TIM2_OC2                | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 1.02                            | TIM2: Output con<br>(remappable to P                | npare 2<br>0.06) <sup>(8)</sup>                    |

| 69                     | D7                      | 44                    | C6                     | VDD_IO                             | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                        | e for digital I/Os                                  |                                                    |

| 70                     | D8                      | 45                    | D6                     | VDDA_ADC                           | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                        | e for A/D converte                                  | r                                                  |

| 71                     | C9                      |                       |                        | P2.11                              | I/O  | TT             | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.11                            |                                                     |                                                    |

| 72                     | B10                     |                       |                        | P2.10                              | I/O  | TT             | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.10                            |                                                     |                                                    |

| 73                     | C8                      | 46                    | D7                     | VSSA_ADC                           | S    |                |          |       |                   |            |           |    |                   | Ground Volta                         | ge for A/D converte                                 | er                                                 |

| 74                     | C7                      | 47                    | C7                     | VSS_IO                             | S    |                |          |       |                   |            |           |    |                   | Ground Volta                         | ge for digital I/Os                                 |                                                    |

| 75                     | E8                      | 48                    | D5                     | VREG_DIS                           | I    | TT             |          |       |                   |            |           |    |                   | Voltage Regu                         | lator Disable input                                 |                                                    |

| 76                     | A9                      | 49                    | A8                     | P0.07 /<br>SMI_DOUT /<br>SSP0_MOSI | I/O  | TT             | x        | х     | EIT2              | O4         | x         | x  |                   | Port 0.07                            | Serial Memory<br>Interface: data<br>output          | SSP0: Master out<br>Slave in data                  |

| 77                     | A8                      | 50                    | A7                     | P0.06 / SMI_DIN<br>/ SSP0_MISO     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O4         | х         | х  |                   | Port 0.06                            | Serial Memory<br>Interface: data<br>input           | SSP0: Master in Slave out data                     |

| 78                     | A7                      | 51                    | A6                     | P0.05 /<br>SSP0_SCLK /<br>SMI_CK   | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT1              | 04         | x         | x  |                   | Port 0.05                            | SSP0: Serial<br>clock                               | Serial Memory<br>Interface: Serial<br>clock output |

| 79                     | B7                      | 52                    | B6                     | P0.04 / SMI_CS0<br>/ SSP0_NSS      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O4         | x         | x  |                   | Port 0.04                            | Serial Memory<br>Interface: chip<br>select output 0 | SSP0: Slave select input                           |

| 80                     | C5                      | 53                    | B7                     | P1.10<br>PWM_EMERGE<br>NCY         | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT10             | O2         | x         | x  |                   | Port 1.10                            | PWM: Emergency                                      | y input                                            |

| 81                     | B6                      | 54                    | B5                     | P1.09 / PWM1                       | I/O  | TT             | х        | х     | EIT9              | 04         | Х         | Х  |                   | Port 1.09                            | PWM: PWM1 out                                       | put                                                |

| 82                     | C6                      |                       |                        | P2.09 / PWM1N                      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 2.09                            | PWM: PWM1 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 83                     | G7                      |                       |                        | P2.08 / PWM2                       | I/O  | $T_T$          | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.08                            | PWM: PWM2 out                                       | put <sup>(4)</sup>                                 |

| 84                     | G6                      |                       |                        | P2.07 / PWM2N                      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 2.07                            | PWM: PWM2 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 85                     | F7                      |                       |                        | P2.06 / PWM3                       | I/O  | TT             | х        | х     |                   | 02         | х         | х  |                   | Port 2.06                            | PWM: PWM3 out                                       | put <sup>(4)</sup>                                 |

| 86                     | F6                      |                       |                        | P2.05 / PWM3N                      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 2.05                            | PWM: PWM3 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 87                     | A6                      | 55                    | A5                     | P1.08 / PWM1N /<br>ADC_IN11        | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | х         | х  |                   | Port 1.08                            | PWM: PWM1<br>complementary<br>output <sup>(8)</sup> | ADC: analog<br>input 11                            |

| 88                     | B5                      | 56                    | B4                     | P1.07 / PWM2                       | I/O  | TT             | х        | х     | EIT8              | 04         | х         | Х  |                   | Port 1.07                            | PWM: PWM2 out                                       | put <sup>(4)</sup>                                 |

| 89                     | A5                      | 57                    | A4                     | P1.06 / PWM2N /<br>ADC_IN10        | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | x         | х  |                   | Port 1.06                            | PWM: PWM2<br>complementary<br>output <sup>(4)</sup> | ADC: analog<br>input 10                            |

| 90                     | B4                      | 58                    | B3                     | P1.05 / PWM3                       | I/O  | TT             | х        | х     | EIT7              | O4         | х         | Х  |                   | Port 1.05                            | PWM: PWM3 out                                       | put <sup>(4)</sup>                                 |

# Table 6. STR750F pin description (continued)

|                        | Pin                     | n°                    |                        |                               |      |                | In       | put   |                   | C          | )utpu     | ıt | y                 |                                                       |                                                                                                   |                                        |

|------------------------|-------------------------|-----------------------|------------------------|-------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                      | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)                  | Alternate                                                                                         | e function                             |

| 91                     | A4                      | 59                    | A3                     | P1.04 / PWM3N /<br>ADC_IN9    | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | х         | х  |                   | Port 1.04                                             | PWM: PWM3<br>complementary<br>output <sup>(4)</sup>                                               | ADC: analog<br>input 9                 |

| 92                     | A3                      |                       |                        | P1.14 /<br>ADC_IN15           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O8         | х         | х  |                   | Port 1.14                                             | ADC: analog inpu                                                                                  | t 15                                   |

| 93                     | A2                      |                       |                        | P1.13 /<br>ADC_IN14           | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT13             | O8         | х         | х  |                   | Port 1.13                                             | ADC: analog input 14                                                                              |                                        |

| 94                     | D5                      |                       |                        | P1.01 / TIM0_TI2              | I/O  | TT             | x        | х     |                   | 02         | x         | x  |                   | Port 1.01                                             | TIM0: Input Capture / trigger /<br>external clock 2 (remappable to<br>P0.05) <sup>(8)</sup>       |                                        |

| 95                     | E6                      |                       |                        | P1.00 /<br>TIM0_OC2           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 1.00                                             | TIM0: Output com<br>(remappable to Po                                                             |                                        |

| 96                     | C4                      | 60                    | C4                     | V18                           | S    |                |          |       |                   |            |           |    |                   | external capa<br>See <i>Figure 4.</i><br>To be connec | for main voltage reg<br>citors 33nF betwee<br>.2.<br>ted to the 1.8V exte<br>ded regulators are i | n V18 and VSS18.<br>ernal power supply |

| 97                     | D4                      | 61                    | C5                     | VSS18                         | S    |                |          |       |                   |            |           |    |                   | Ground Volta                                          | ge for the main volt                                                                              | age regulator.                         |

| 98                     | D3                      | 62                    | A2                     | VSS_IO                        | S    |                |          |       |                   |            |           |    |                   | Ground Volta                                          | ge for digital I/Os                                                                               |                                        |

| 99                     | C3                      | 63                    | B2                     | VDD_IO                        | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                                         | e for digital I/Os                                                                                |                                        |

| 100                    | A1                      | 64                    | A1                     | P0.03 / TIM2_TI1<br>/ ADC_IN1 | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | 02         | x         | x  |                   | Port 0.03                                             | TIM2: Input<br>Capture / trigger<br>/ external clock 1                                            | ADC: analog<br>input 1                 |

Table 6. STR750F pin description (continued)

1. For STR755FVx part numbers, the USB pins must be left unconnected.

2. The non available pins on LQPFP64 and LFBGA64 packages are internally tied to low level.

3. None of the I/Os are True Open Drain: when configured as Open Drain, there is always a protection diode between the I/O pin and VDD\_IO.

4. In the 100-pin package, this Alternate Function is duplicated on two ports. You can configure one port to use this AF, the other port is then free for general purpose I/O (GPIO), external interrupt/wake-up lines, or analog input (ADC\_IN) where these functions are listed in the table.

5. It is mandatory that the NJTRST pin is reset to ground during the power-up phase. It is recommended to connect this pin to NRSTOUT pin (if available) or NRSTIN.

After reset, these pins are enabled as JTAG alternate function see (*Port reset state on page 16*). To use these ports as general purpose I/O (GPIO), the DBGOFF control bit in the GPIO\_REMAPOR register must be set by software (in this case, debugging these I/Os via JTAG is not possible).

7. There are two different TQFP and BGA 64-pin packages: in the first one, pins 41 and 42 are mapped to USB DN/DP while for the second one, they are mapped to P0.15/CAN\_TX and P0.14/CAN\_RX.

8. For details on remapping these alternate functions, refer to the GPIO\_REMAPOR register description.

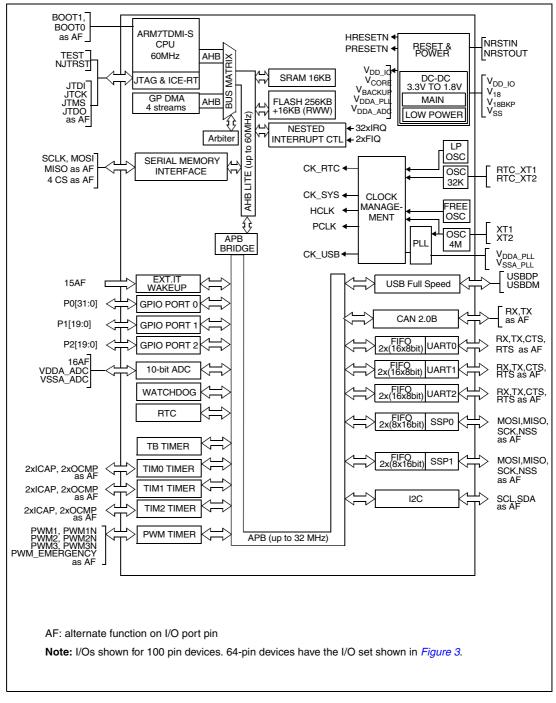

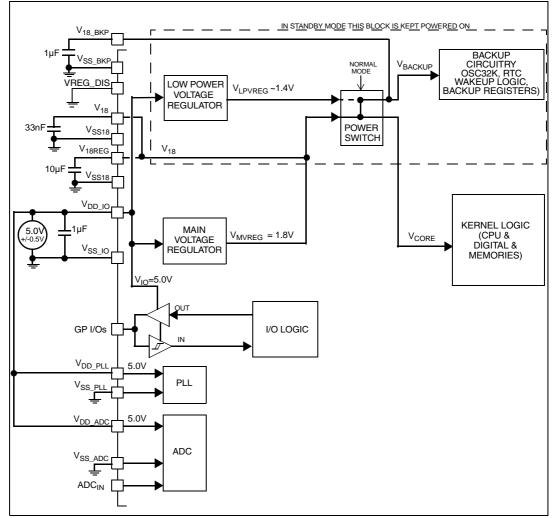

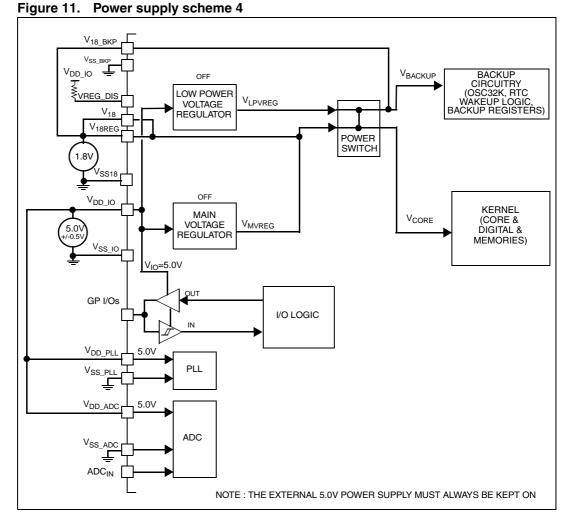

# 6.1.6 Power supply schemes

When mentioned, some electrical parameters can refer to a dedicated power scheme among the four possibilities. The four different power schemes are described below.

# Power supply scheme 1: Single external 3.3 V power source

Figure 8. Power supply scheme 1

Power supply scheme 3: Single external 5 V power source

# Figure 10. Power supply scheme 3

Power supply scheme 4: Dual external 1.8 V and 5.0 V supply

# 6.1.7 I/O characteristics versus the various power schemes (3.3V or 5.0V)

Unless otherwise mentioned, all the I/O characteristics are valid for both

- V<sub>DD IO</sub>=3.0 V to 3.6 V with bit EN33=1

- V<sub>DD IO</sub>=4.5 V to 5.5 V with bit EN33=0

When  $V_{DD \ IO}$ =3.0 V to 3.6 V, I/Os are not 5V tolerant.

# 6.1.8 Current consumption measurements

All the current consumption measurements mentioned below refer to Power scheme 1 and 2 as described in *Figure 12* and *Figure 13*

# 6.2.2 Current characteristics

#### Table 8.Current characteristics

| Symbol                                         | Ratings                                                                 | Maximum<br>value | Unit |

|------------------------------------------------|-------------------------------------------------------------------------|------------------|------|

| I <sub>VDD_IO</sub> <sup>(1)</sup>             | Total current into $V_{DD_{IO}}$ power lines (source) <sup>(2)</sup>    | 150              |      |

| I <sub>VSS_IO</sub> <sup>(1)</sup>             | Total current out of $V_{SS}$ ground lines (sink) <sup>(2)</sup>        | 150              |      |

|                                                | Output current sunk by any I/O and control pin                          | 25               |      |

| IIO                                            | Output current source by any I/Os and control pin                       | - 25             | mA   |

|                                                | Injected current on NRSTIN pin                                          | ± 5              | ША   |

| I <sub>INJ(PIN)</sub> <sup>(3) &amp; (4)</sup> | Injected current on XT1 and XT2 pins                                    | ± 5              |      |

|                                                | Injected current on any other pin <sup>(5)</sup>                        | ± 5              |      |

| $\Sigma I_{\rm INJ(PIN)}^{(3)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ± 25             |      |

1. The user can use GPIOs to source or sink high current (up to 20 mA for O8 type High Sink I/Os). In this case, the user must ensure that these absolute max. values are not exceeded (taking into account the RUN power consumption) and must follow the rules described in *Section 6.3.8: I/O port pin characteristics on page 54*.

- 2. All 3.3 V or 5.0 V power ( $V_{DD\_IO}$ ,  $V_{DDA\_ADC}$ ,  $V_{DDA\_PLL}$ ) and ground ( $V_{SS\_IO}$ ,  $V_{SSA\_ADC}$ ,  $V_{DDA\_ADC}$ ) pins must always be connected to the external 3.3V or 5.0V supply.

- 3. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. Data based on T<sub>A</sub>=25°C.

- 4. Negative injection disturbs the analog performance of the device. See note in *Section 6.3.12: 10-bit ADC characteristics on page 72.*

- 5. When several inputs are submitted to a current injection, the maximum Σl<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with Σl<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

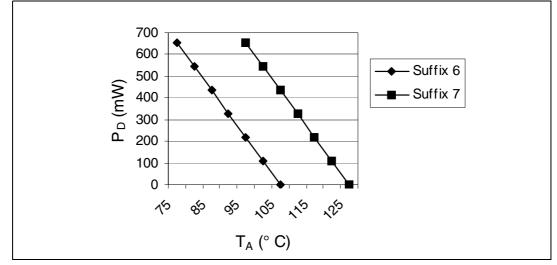

# 6.2.3 Thermal characteristics

#### Table 9. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

# Table 16.Dual supply supply typical power consumption in Run, WFI, Slow and<br/>Slow-WFI modes

To calculate the power consumption in Dual supply mode, refer to the values given in *Table 15*. and consider that this consumption is split as follows:  $I_{DD}(single supply) \sim I_{DD}(dual supply) = I_{DD} \vee 18 + I_{DD}(VDD_{IO})$

For 3.3V range:  $I_{DD(VDD_IO)} \sim 1$  to 2 mA For 5V range:  $I_{DD(VDD_IO)} \sim 2$  to 3 mA Therefore most of the consumption is sunk on the V<sub>18</sub> power supply This formula does not apply in STOP and STANDBY modes, refer to *Table 17*.

Subject to general operating conditions for  $V_{\text{DD\_IO}}\text{,}$  and  $T_{\text{A}}$

Table 17. Typical power consumption in STOP and STANDBY modes

| Symbol                         | Parameter                         | Conditions                                                   |                                            | 3.3V<br>Typ <sup>(1)</sup> | 5V<br>Typ <sup>(2)</sup> | Unit |

|--------------------------------|-----------------------------------|--------------------------------------------------------------|--------------------------------------------|----------------------------|--------------------------|------|

|                                |                                   | LP_PARAM bits: ALL OFF <sup>(5)</sup>                        |                                            | 12                         | 15                       |      |

|                                | Supply current                    | LP_PARAM bits : MVREG ON, OSC4M OFF, F<br>OFF <sup>(6)</sup> | LASH                                       | 130                        | 135                      |      |

|                                | in STOP<br>mode <sup>(4)</sup>    | LP_PARAM bits: MVREG ON, OSC4M ON , FI                       | _ASH                                       | 1950                       | 1930                     | μA   |

|                                |                                   | LP_PARAM bits: MVREG ON, OSC4M OFF, FL                       | _ASH ON <sup>(6)</sup>                     | 630                        | 635                      |      |

|                                |                                   | LP_PARAM bits: MVREG ON, OSC4M ON, FL                        | ASH ON <sup>(6)</sup>                      | 2435                       | 2425                     |      |

| I <sub>DD</sub> <sup>(3)</sup> |                                   | LPPARAM bits: ALL OFF, with V <sub>18</sub> =1.8 V           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 5<br><1                    | 5<br><1                  |      |

|                                | Supply current                    | LP_PARAM bits: OSC4M ON, FLASH OFF                           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 410<br>1475                | 410<br>1435              | μA   |

|                                | mode <sup>(7)</sup>               | LP_PARAM bits: OSC4M OFF, FLASH ON                           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 550<br><1                  | 550<br>1                 | μΛ   |

|                                |                                   | LP_PARAM bits: OSC4M ON, FLASH ON                            | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 910<br>1475                | 910<br>1445              |      |

|                                | Supply current                    | RTC OFF                                                      |                                            | 11                         | 14                       |      |

|                                | in STANDBY<br>mode <sup>(4)</sup> | RTC ON clocked by OSC32K                                     |                                            | 14                         | 18                       | μA   |

1. Typical data are based on  $T_A=25^{\circ}$ C,  $V_{DD IO}=3.3$  V and  $V_{18}=1.8$  V unless otherwise indicated in the table.

2. Typical data are based on  $T_A=25^{\circ}C$ ,  $V_{DD\_IO}=5.0$  V and  $V_{18}=1.8$  V unless otherwise indicated in the table.

3. The conditions for these consumption measurements are described at the beginning of Section 6.3.4 on page 36.

4. Single supply scheme see Figure 12.

5. In this mode, the whole digital circuitry is powered internally by the LPVREG at approximately 1.4 V, which significantly reduces the leakage currents.

6. In this mode, the whole digital circuitry is powered internally by the MVREG at 1.8 V.

7. Dual supply scheme see Figure 13.

### **PLL characteristics**

Subject to general operating conditions for  $V_{DD \ IO}$ , and  $T_A$ .

| Table 24. PLL characteristics | Table 24. | PLL | characteristics |

|-------------------------------|-----------|-----|-----------------|

|-------------------------------|-----------|-----|-----------------|

| Symbol                                  | Parameter                                          | Test Conditions                                                     |     | Value | )                  | Unit |

|-----------------------------------------|----------------------------------------------------|---------------------------------------------------------------------|-----|-------|--------------------|------|

| Symbol                                  | Falameter                                          | Test Conditions                                                     | Min | Тур   | Max <sup>(1)</sup> | Unit |

| f                                       | PLL input clock                                    |                                                                     |     | 4.0   |                    | MHz  |

| f <sub>PLL_IN</sub>                     | PLL input clock duty cycle                         |                                                                     | 40  |       | 60                 | %    |

| f <sub>PLL_OUT</sub>                    | PLL multiplier output clock                        | f <sub>PLL_IN</sub> x 24                                            |     |       | 165                | MHz  |

| f <sub>VCO</sub>                        | VCO frequency range                                | When PLL<br>operates (locked)                                       | 336 |       | 960                | MHz  |

| t <sub>LOCK</sub>                       | PLL lock time                                      |                                                                     |     |       | 300                | μs   |

| ∆t <sub>JITTER1</sub> <sup>(2)(3)</sup> | Single period jitter (+/-3 $\Sigma$ peak to peak)  | $f_{PLL_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable  |     |       | +/-250             | ps   |

| ∆t <sub>JITTER2</sub> <sup>(2)(3)</sup> | Long term jitter (+/- $3\Sigma$ peak to peak)      | $f_{PLL_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable  |     |       | +/-2.5             | ns   |

| ∆t <sub>JITTER3</sub> <sup>(2)(3)</sup> | Cycle to cycle jitter (+/- $3\Sigma$ peak to peak) | $f_{PLL\_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable |     |       | +/-500             | ps   |

1. Data based on product characterisation, not tested in production.

2. Refer to jitter terminology in : PLL characteristics on page 47 for details on how jitter is specified.

The jitter specification holds true only up to 50mV (peak-to-peak) noise on V<sub>DDA\_PLL</sub> and V<sub>18</sub> supplies. Jitter will increase if the noise is more than 50mV. In addition, it assumes that the input clock has no jitter.

4. The PLL parameters (MX1, MX0, PRESC1, PRESC2) must respect the constraints described in: PLL characteristics on page 47.

#### Internal RC oscillators (FREEOSC & LPOSC)

Subject to general operating conditions for  $V_{DD}$  IO, and  $T_A$ .

#### Table 25. Internal RC oscillators (FREEOSC & LPOSC)

| Symbol                  | Parameter                    | Conditions | Min | Тур | Max | Unit |

|-------------------------|------------------------------|------------|-----|-----|-----|------|

| f <sub>CK_FREEOSC</sub> | FREEOSC Oscillator Frequency |            | 3   | 5   | 8   | MHz  |

| f <sub>CK_LPOSC</sub>   | LPOSC Oscillator Frequency   |            | 150 | 300 | 500 | kHz  |

# 6.3.6 Memory characteristics

# **Flash memory**

Subject to general operating conditions for  $V_{DD\_IO}$  and  $V_{18},\,T_A$  = -40 to 105  $^\circ C$  unless otherwise specified.

| Sumbel           | Parameter               | Test Condition-                                    | Va            | lue                                        | Unit |

|------------------|-------------------------|----------------------------------------------------|---------------|--------------------------------------------|------|

| Symbol           | Parameter               | Test Conditions                                    | Тур           | Max <sup>(1)</sup>                         | Unit |

| t <sub>PW</sub>  | Word Program            |                                                    | 35            |                                            | μs   |

| t <sub>PDW</sub> | Double Word Program     |                                                    | 60            |                                            | μS   |

| t <sub>PB0</sub> | Bank 0 Program (256K)   | Single Word programming of a checker-board pattern | 2             | 4.9 <sup>(2)</sup>                         | S    |

| t <sub>PB1</sub> | Bank 1 Program (16K)    | Single Word programming of a checker-board pattern | 125           | 224 <sup>(2)</sup>                         | ms   |

| t <sub>ES</sub>  | Sector Erase (64K)      | Not preprogrammed (all 1)<br>Preprogrammed (all 0) | 1.54<br>1.176 | 2.94 <sup>(2)</sup><br>2.38 <sup>(2)</sup> | S    |

| t <sub>ES</sub>  | Sector Erase (8K)       | Not preprogrammed (all 1)<br>Preprogrammed (all 0) | 392<br>343    | 560 <sup>(2)</sup><br>532 <sup>(2)</sup>   | ms   |

| t <sub>ES</sub>  | Bank 0 Erase (256K)     | Not preprogrammed (all 1)<br>Preprogrammed (all 0) | 8.0<br>6.6    | 13.7<br>11.2                               | s    |

| t <sub>ES</sub>  | Bank 1 Erase (16K)      | Not preprogrammed (all 1)<br>Preprogrammed (all 0) | 0.9<br>0.8    | 1.5<br>1.3                                 | S    |

| t <sub>RPD</sub> | Recovery when disabled  |                                                    |               | 20                                         | μs   |

| t <sub>PSL</sub> | Program Suspend Latency |                                                    |               | 10                                         | μS   |

| t <sub>ESL</sub> | Erase Suspend Latency   |                                                    |               | 300                                        | μs   |

Table 26.

Flash memory characteristics

1. Data based on characterisation not tested in production

2. 10K program/erase cycles.

Table 27.

Flash memory endurance and data retention

| Symbol              | Parameter                  | Conditions                                             | Value              |     |     | Unit    |

|---------------------|----------------------------|--------------------------------------------------------|--------------------|-----|-----|---------|

| Symbol              | Farameter                  | Conditions                                             | Min <sup>(1)</sup> | Тур | Max | Unit    |

| N <sub>END_B0</sub> | Endurance (Bank 0 sectors) |                                                        | 10                 |     |     | kcycles |

| N <sub>END_B1</sub> | Endurance (Bank 1 sectors) |                                                        | 100                |     |     | kcycles |

| Y <sub>RET</sub>    | Data Retention             | T <sub>A</sub> =85° C                                  | 20                 |     |     | Years   |

| t <sub>ESR</sub>    | Erase Suspend Rate         | Min time from Erase<br>Resume to next Erase<br>Suspend | 20                 |     |     | ms      |

1. Data based on characterisation not tested in production.

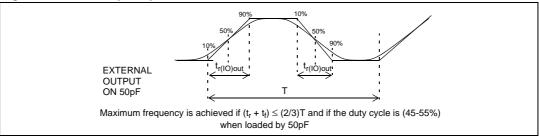

### **Output speed**

Subject to general operating conditions for  $V_{\text{DD}\_\text{IO}}$  and  $T_{\text{A}}$  unless otherwise specified.

|  | Table | 34. | Output s | peed |

|--|-------|-----|----------|------|

|--|-------|-----|----------|------|

|                                               | I/O dynamic characteristics for $V_{DD_{-}IO} = 3.0$ to 3.6V and EN33 bit =1 or $V_{DD_{-}IO} = 4.5$ to 5.5V and EN33 bit =0 |                                                   |                       |  |     |      |     |  |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------|--|-----|------|-----|--|--|

| I/O<br>TypeSymbolParameterConditionsMinTypMin |                                                                                                                              |                                                   |                       |  | Max | Unit |     |  |  |

|                                               | f <sub>max(IO)out</sub>                                                                                                      | Maximum Frequency <sup>(1)</sup>                  | C <sub>L</sub> =50 pF |  |     | 10   | MHz |  |  |

| O2                                            | t <sub>f(IO)out</sub>                                                                                                        | Output high to low level fall time <sup>(2)</sup> | С <sub>L</sub> =50 рF |  |     | 30   |     |  |  |

|                                               | t <sub>r(IO)out</sub>                                                                                                        | Output low to high level rise time <sup>(2)</sup> | Between 10% and 90%   |  |     | 33   | ns  |  |  |

| 04                                            | f <sub>max(IO)out</sub>                                                                                                      | Maximum Frequency <sup>(1)</sup>                  | C <sub>L</sub> =50 pF |  |     | 25   | MHz |  |  |

|                                               | t <sub>f(IO)out</sub>                                                                                                        | Output high to low level fall time <sup>(2)</sup> | С <sub>L</sub> =50 рF |  |     | 12   | ns  |  |  |

|                                               | t <sub>r(IO)out</sub>                                                                                                        | Output low to high level rise time <sup>(2)</sup> | Between 10% and 90%   |  |     | 14   | 113 |  |  |

| O8                                            | f <sub>max(IO)out</sub>                                                                                                      | Maximum Frequency <sup>(1)</sup>                  | C <sub>L</sub> =50pF  |  |     | 40   | MHz |  |  |

|                                               | t <sub>f(IO)out</sub>                                                                                                        | Output high to low level fall time <sup>(2)</sup> | С <sub>L</sub> =50 рF |  |     | 6    | ns  |  |  |

|                                               | t <sub>r(IO)out</sub>                                                                                                        | Output low to high level rise time <sup>(2)</sup> | Between 10% and 90%   |  |     | 6    | ns  |  |  |

1. The maximum frequency is defined as described in *Figure 26*.

2. Data based on product characterisation, not tested in production.

#### Figure 26. I/O output speed definition

# 6.3.10 Communication interface characteristics

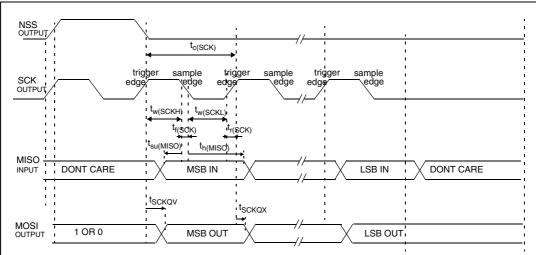

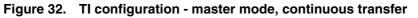

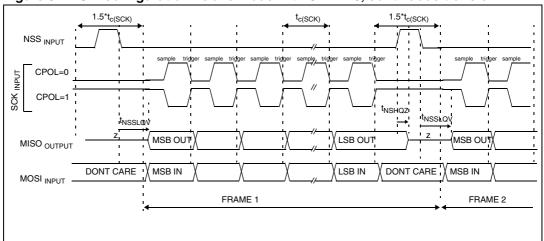

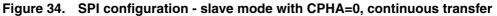

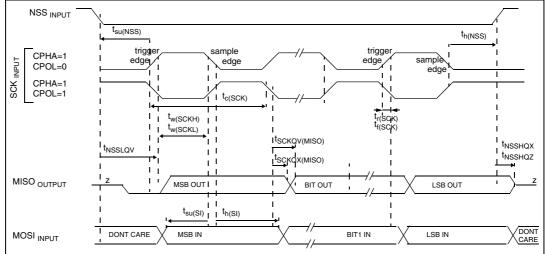

# SSP synchronous serial peripheral in master mode (SPI or TI mode)

General operating conditions: V\_{33}, 3.0V to 3.3V, V18 ~=1.8V,  $C_L\approx 45$  pF.

| Symbol               | Parameter                                              | Condi                | tions | Min | Мах                       | Unit |

|----------------------|--------------------------------------------------------|----------------------|-------|-----|---------------------------|------|

| f                    | SPI clock frequency <sup>(2)</sup>                     |                      | SSP0  |     | 16                        | MHz  |

| ISCK                 | f <sub>SCK</sub> SPI clock frequency <sup>(2)</sup>    |                      | SSP1  |     | 8                         |      |

| t (agu)              | SPI clock rise time                                    |                      | SSP0  |     | 14                        |      |

| t <sub>r(SCK)</sub>  |                                                        |                      | SSP1  |     | 33                        |      |

| tuoou                | SPI clock fall time                                    |                      | SSP0  |     | 11                        |      |

| t <sub>f(SCK)</sub>  |                                                        |                      | SSP1  |     | 30                        |      |

| t <sub>w(SCKH)</sub> | SCK high and low time                                  |                      | SSP0  |     | 19                        |      |

| t <sub>w(SCKL)</sub> | SOIT High and low time                                 |                      | SSP1  |     | 30                        |      |

| tuccució             | NSS low to Data Output                                 |                      | SSP0  |     | 0.5t <sub>SCK</sub> +15ns |      |

| t <sub>NSSLQV</sub>  | MOSI valid time                                        |                      | SSP1  |     | 0.5t <sub>SCK</sub> +30ns |      |

| t <sub>SCKNSSH</sub> | SCK last edge to NSS high                              | CPHA = 0<br>CPHA = 1 | SSP0  |     | 0.5t <sub>SCK</sub> +15ns |      |

|                      |                                                        |                      | SSP1  |     | 0.5t <sub>SCK</sub> +30ns |      |

|                      |                                                        |                      | SSP0  |     | t <sub>SCK</sub> +15ns    | ns   |

|                      |                                                        |                      | SSP1  |     | t <sub>SCK</sub> +30ns    |      |

| taavav               | SCK trigger edge to data                               |                      | SSP0  |     | 15                        |      |

| t <sub>sckav</sub>   | output MOSI valid time                                 |                      | SSP1  |     | 30                        |      |

| t                    | SCK trigger edge to data                               |                      | SSP0  | 0   |                           |      |

| t <sub>SCKQX</sub>   | output MOSI invalid time                               |                      | SSP1  | 0   |                           |      |

|                      | Data input (MISO) setup                                |                      | SSP0  | 25  |                           |      |

| t <sub>su</sub>      | time w.r.t SCK sampling edge                           |                      | SSP1  | 25  |                           |      |

| t.                   | Data input (MISO) hold time<br>w.r.t SCK sampling edge |                      | SSP0  | 0   |                           |      |

| t <sub>h</sub>       |                                                        |                      | SSP1  | 0   |                           |      |

Table 38.

SSP master mode characteristics<sup>(1)</sup>

1. Data based on characterisation results, not tested in production.

2. Max frequency for the 2 SSPs is  $f_{PCLK}/2$ ;  $f_{PCLK}$  max = 32 MHz. This takes into account the frequency limitation due to I/O speed capability. SSP0 uses IO4 type while SSP1 uses IO2 type I/Os.

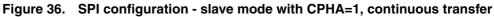

Figure 31. TI configuration - master mode, single transfer

| t <sub>c(S0</sub>           | CK)                              | t <sub>c(SCK)</sub>           |                               |          |

|-----------------------------|----------------------------------|-------------------------------|-------------------------------|----------|

| NSS OUTPUT                  | //                               |                               |                               | 1<br>1   |

| SCK OUTPUT                  | e trigger, sample trigger sample | trigger sample trigger sample | trigger sample trigger sample |          |

|                             | XXX                              |                               |                               | OUT      |

| MISO INPUT DONT CARE MSB IN | X/X                              |                               | N X // LSB                    |          |

|                             | FRAME 1                          | <b>.</b>                      | FRAME 2                       | <b>→</b> |

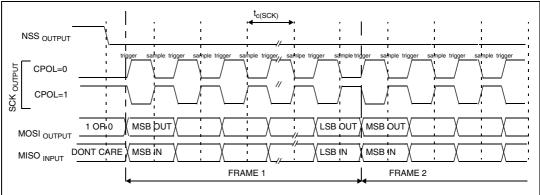

not possible to power off the STR7x while some another I<sup>2</sup>C master node remains powered on: otherwise, the STR7x will be powered by the protection diode.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standard mode<br>I <sup>2</sup> C |                    | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    | Unit |

|--------------------------------------------|-----------------------------------------|-----------------------------------|--------------------|-------------------------------------------|--------------------|------|

|                                            |                                         |                                   | Max <sup>(2)</sup> | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> |      |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                               |                    | 1.3                                       |                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                               |                    | 0.6                                       |                    | μS   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                               |                    | 100                                       |                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(3)</sup>                  |                    | 0 <sup>(4)</sup>                          | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                                   | 1000               | 20+0.1C <sub>b</sub>                      | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                                   | 300                | 20+0.1C <sub>b</sub>                      | 300                |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                               |                    | 0.6                                       |                    |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                               |                    | 0.6                                       |                    | μS   |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                               |                    | 0.6                                       |                    | μs   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                               |                    | 1.3                                       |                    | μs   |

| Cb                                         | Capacitive load for each bus line       |                                   | 400                |                                           | 400                | pF   |

Table 41.

SDA and SCL characteristics

1.  $f_{PCLK}$ , must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

3. The maximum hold time  $t_{h(SDA)}$  is not applicable

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

# Figure 40. Typical application with I<sup>2</sup>C bus and timing diagram

1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

# ADC accuracy vs. negative injection current

Injecting negative current on specific pins listed in *Table 46* (generally adjacent to the analog input pin being converted) should be avoided as this significantly reduces the accuracy of the conversion being performed. It is recommended to add a Schottky diode (pin to ground) to pins which may potentially inject negative current.

| Table 46. List of adjacent pi |

|-------------------------------|

|-------------------------------|

| Analog input | Related adjacent pins |

|--------------|-----------------------|

| a            | None                  |

| AIN1/P0.03   | None                  |

| AIN2/P0.12   | P0.11                 |

| AIN3/P0.17   | P0.18 and P0.16       |

| AIN4/P0.19   | P0.24                 |

| AIN5/P0.22   | None                  |

| AIN6/P0.23   | P2.04                 |

| AIN7/P0.27   | P1.11 and P0.26       |

| AIN8/P0.29   | P0.30 and P0.28       |

| AIN9/P1.04   | None                  |

| AIN10/P1.06  | P1.05                 |

| AIN11/P1.08  | P1.04 and P1.13       |

| AIN12/P1.11  | P2.17 and P0.27       |

| AIN13/P1.12  | None                  |

| AIN14/P1.13  | P1.14 and P1.01       |

| AIN15/P1.14  | None                  |

#### Figure 42. Typical application with ADC

#### Analog power supply and reference pins

The  $V_{DDA\_ADC}$  and  $V_{SSA\_ADC}$  pins are the analog power supply of the A/D converter cell.