Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                              |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 60MHz                                                               |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, SSI, SSP, UART/USART                 |

| Peripherals                | DMA, PWM, WDT                                                       |

| Number of I/O              | 38                                                                  |

| Program Memory Size        | 64KB (64K x 8)                                                      |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K × 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | A/D 11x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-LQFP                                                             |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str752fr0t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

periodic interrupt. It is clocked by an external 32.768 kHz oscillator or the internal low power RC oscillator. The RC has a typical frequency of 300 kHz and can be calibrated.

#### WDG (watchdog timer)

The watchdog timer is based on a 16-bit downcounter and 8-bit prescaler. It can be used as watchdog to reset the device when a problem occurs, or as free running timer for application time out management.

#### Timebase timer (TB)

The timebase timer is based on a 16-bit auto-reload counter and not connected to the I/O pins. It can be used for software triggering, or to implement the scheduler of a real-time operating system.

#### Synchronizable standard timers (TIM2:0)

The three standard timers are based on a 16-bit auto-reload counter and feature up to 2 input captures and 2 output compares (for external triggering or time base / time out management). They can work together with the PWM timer via the Timer Link feature for synchronization or event chaining. In reset state, timer Alternate Function I/Os are connected to the same

I/O ports in both 64-pin and 100-pin devices. To optimize timer functions in 64-pin devices, timer Alternate Function I/Os can be connected, or "remapped", to other I/O ports as summarized in *Table 3* and detailed in *Table 6*. This remapping is done by the application via a control register.

|          |                       |         | Number of alternate function I/Os |          |  |  |  |

|----------|-----------------------|---------|-----------------------------------|----------|--|--|--|

| Star     | ndard timer functions | 100-pin | 64-pin package                    |          |  |  |  |

|          |                       | package | Default mapping                   | Remapped |  |  |  |

| ТІМ О    | Input Capture         | 2       | 1                                 | 2        |  |  |  |

| T IIVI O | Output Compare/PWM    | 2       | 1                                 | 2        |  |  |  |

| TIM 1    | Input Capture         | 2       | 1                                 | 1        |  |  |  |

|          | Output Compare/PWM    | 2       | 1                                 | 1        |  |  |  |

| TIM 2    | Input Capture         | 2       | 2                                 | 2        |  |  |  |

| T TIVI Z | Output Compare/PWM    | 2       | 1                                 | 2        |  |  |  |

#### Table 3. Standard timer alternate function I/Os

Any of the standard timers can be used to generate PWM outputs. One timer (TIM0) is mapped to a DMA channel.

#### Motor control PWM timer (PWM)

The Motor Control PWM Timer (PWM) can be seen as a three-phase PWM multiplexed on 6 channels. The 16-bit PWM generator has full modulation capability (0...100%), edge or centre-aligned patterns and supports dead-time insertion. It has many features in common with the standard TIM timers which has the same architecture and it can work together with the TIM timers via the Timer Link feature for synchronization or event chaining. The PWM timer is mapped to a DMA channel.

#### GPIOs (general purpose input/output)

Each of the 72 GPIO pins (38 GPIOs in 64-pin devices) can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as Peripheral Alternate Function. Port 1.15 is an exception, it can be used as general-purpose input only or wake-up from STANDBY mode (WKP\_STDBY). Most of the GPIO pins are shared with digital or analog alternate functions.

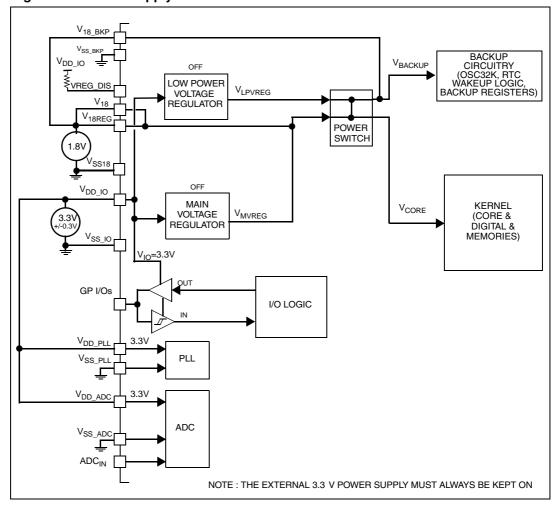

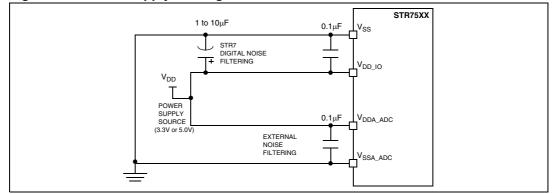

#### Figure 9. Power supply scheme 2

Power supply scheme 2: Dual external 1.8V and 3.3V supply

57

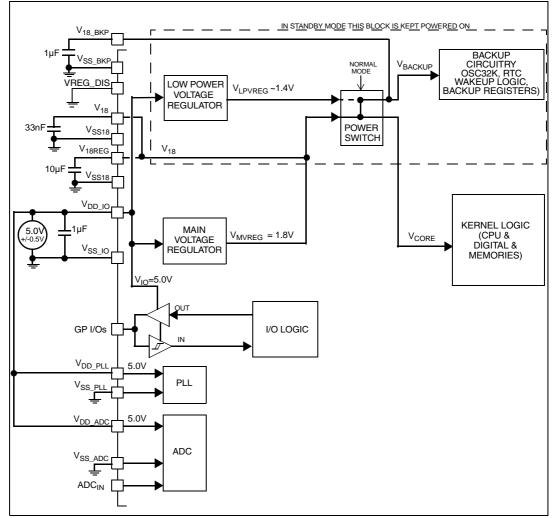

Power supply scheme 3: Single external 5 V power source

### Figure 10. Power supply scheme 3

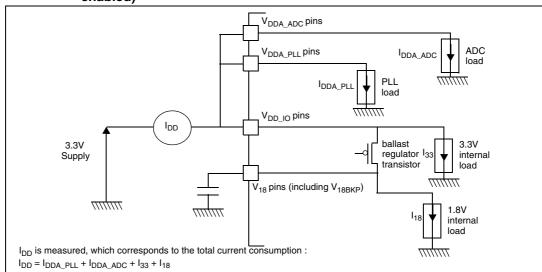

# Figure 12. Power consumption measurements in power scheme 1 (regulators enabled)

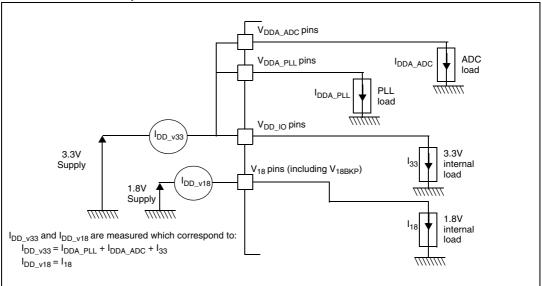

Figure 13. Power consumption measurements in power scheme 2 (regulators disabled)

## 6.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 6.2.1 Voltage characteristics

| Symbol                                | Ratings                                                                                                  | Min                                                  | Max                                                  | Unit |

|---------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------|

| $V_{DD_x} - V_{SS_x}^{(1)}$           | Including $V_{DDA\_ADC}$ and $V_{DDA\_PLL}$                                                              | -0.3                                                 | 6.5                                                  | V    |

| V <sub>18</sub> - V <sub>SS18</sub>   | Digital 1.8 V Supply voltage on all V <sub>18</sub><br>power pins (when 1.8 V is provided<br>externally) | -0.3                                                 | 2.0                                                  |      |

| V <sub>IN</sub>                       | Input voltage on any pin <sup>(2)</sup>                                                                  | V <sub>SS</sub> -0.3 to<br>V <sub>DD_IO</sub> +0.3   | V <sub>SS</sub> -0.3 to<br>V <sub>DD_IO</sub> +0.3   |      |

| ا∆V <sub>DDx</sub> I                  | Variations between different 3.3 V or 5.0 V power pins                                                   |                                                      | 50                                                   |      |

| l∆V <sub>18x</sub> l                  | Variations between different 1.8 V power pins <sup>(3)</sup>                                             |                                                      | 25                                                   | mV   |

| IV <sub>SSX</sub> - V <sub>SS</sub> I | Variations between all the different ground pins                                                         |                                                      | 50                                                   |      |

| V <sub>ESD(HBM)</sub>                 | Electro-static discharge voltage (Human<br>Body Model)                                                   | see : Absolute<br>maximum                            | see : Absolute<br>maximum                            |      |

| V <sub>ESD(MM)</sub>                  | Electro-static discharge voltage (Machine Model)                                                         | ratings<br>(electrical<br>sensitivity) on<br>page 52 | ratings<br>(electrical<br>sensitivity) on<br>page 52 |      |

#### Table 7. Voltage characteristics

All 3.3 V or 5.0 V power (V<sub>DD\_IO</sub>, V<sub>DDA\_ADC</sub>, V<sub>DDA\_PLL</sub>) and ground (V<sub>SS\_IO</sub>, V<sub>SSA\_ADC</sub>, V<sub>DDA\_ADC</sub>) pins must always be connected to the external 3.3V or 5.0V supply. When powered by 3.3V, I/Os are not 5V tolerant.

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

Only when using external 1.8 V power supply. All the power (V<sub>18</sub>, V<sub>18REG</sub>, V<sub>18BKP</sub>) and ground (V<sub>SS18</sub>, V<sub>SSBKP</sub>) pins must always be connected to the external 1.8 V supply.

# 6.3 Operating conditions

### 6.3.1 General operating conditions

Subject to general operating conditions for  $V_{\text{DD}\ \text{IO}}$  , and  $T_{\text{A}}$  unless otherwise specified.

| Table 10. General | operating conditions |

|-------------------|----------------------|

|-------------------|----------------------|

| Symbol             | Parameter                                                  | Conditions                                                | Min  | Max  | Unit |  |

|--------------------|------------------------------------------------------------|-----------------------------------------------------------|------|------|------|--|

|                    |                                                            | Accessing SRAM with 0 wait states                         | 0    | 64   |      |  |

|                    |                                                            | Accessing Flash in burst<br>mode, T <sub>A</sub> ≤85° C   | 0    | 60   | MHz  |  |

| <sup>f</sup> нсlк  | Internal AHB Clock frequency                               | Accessing Flash in burst<br>mode<br>T <sub>A</sub> >85° C |      | 56   |      |  |

| HOLK               |                                                            | Accessing Flash with 0 wait states                        | 0    | 32   |      |  |

|                    |                                                            | Write access to Flash registers <sup>(1)</sup>            | 0    | 30   |      |  |

|                    |                                                            | Accessing Flash in RWW mode                               | 0    | 16   |      |  |

| f <sub>PCLK</sub>  | Internal APB Clock frequency                               | nternal APB Clock frequency                               |      | 32   | MHz  |  |

| M                  | Standard Operating Voltage<br>Power Scheme 1 & 2           |                                                           | 3.0  | 3.6  |      |  |

| V <sub>DD_IO</sub> | Standard Operating Voltage<br>Power Scheme 3 & 4           |                                                           | 4.5  | 5.5  | V    |  |

| V <sub>18</sub>    | Standard Operating Voltage<br>Power Scheme 2 & 4           |                                                           | 1.65 | 1.95 |      |  |

|                    |                                                            | LQFP100                                                   |      | 434  |      |  |

| Р                  | Power dissipation at $T_A = 85^\circ$ C                    | LQFP64                                                    |      | 444  | 1    |  |

| PD                 | for suffix 6 or $T_A$ = 105° C for suffix 7 <sup>(2)</sup> | LFBGA100                                                  |      | 487  | mW   |  |

|                    |                                                            | LFBGA64                                                   |      | 344  |      |  |

|                    | Ambient temperature for 6 suffix                           | Maximum power dissipation                                 | -40  | 85   | °C   |  |

| т                  | version                                                    | Low power dissipation <sup>(3)</sup>                      | -40  | 105  | °C   |  |

| T <sub>A</sub>     | Ambient temperature for 7 suffix                           | Maximum power dissipation                                 | -40  | 105  | °C   |  |

|                    | version                                                    | Low power dissipation <sup>(3)</sup>                      | -40  | 125  | °C   |  |

| ТJ                 | Junction temperature range                                 | 6 Suffix Version                                          | -40  | 105  | °C   |  |

| ۰J                 |                                                            | 7 Suffix Version                                          | -40  | 125  | °C   |  |

1. Write access to Flash registers is either a program, erase, set protection or un-set protection operation.

2. If  $T_A$  is lower, higher PD values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.2: Thermal characteristics on page 79).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.2: Thermal characteristics on page 79).

#### 6.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for T<sub>A</sub>.

| Symbol              | Parameter                            | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------|--------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| turn in             | IO V <sub>DD_IO</sub> rise time rate | V rico timo rato             | 20                 |     |                    | μs/V |

| t <sub>VDD_IO</sub> |                                      |                              |                    |     | 20                 | ms/V |

| t <sub>V18</sub> V  | $V_{18}$ rise time rate $^{(1)}$     | When 1.8 V power is supplied | 20                 |     |                    | μs/V |

|                     |                                      | externally                   |                    |     | 20                 | ms/V |

#### Table 11. Operating conditions at power-up / power-down

1. Data guaranteed by characterization, not tested in production.

### 6.3.3 Embedded voltage regulators

Subject to general operating conditions for  $V_{DD \ IO}$ , and  $T_A$

| Symbol                      | Parameter                                                                  | Conditions                                 | Min  | Тур  | Max  | Unit |

|-----------------------------|----------------------------------------------------------------------------|--------------------------------------------|------|------|------|------|

| V <sub>MVREG</sub>          | MVREG power supply <sup>(1)</sup>                                          | load <150 mA                               | 1.65 | 1.80 | 1.95 | V    |

| V <sub>LPVREG</sub>         | LPVREG power supply <sup>(2)</sup>                                         | load <10 mA                                | 1.30 | 1.40 | 1.50 | V    |

| t <sub>vreg_pwrup</sub> (1) | Voltage Regulators start-up<br>time (to reach 90% of final V <sub>18</sub> | V <sub>DD_IO</sub> rise<br>slope = 20 μs/V |      | 80   |      | μs   |

|                             | value) at $V_{DD_{IO}}$ power-up <sup>(3)</sup>                            | V <sub>DD_IO</sub> rise<br>slope = 20 ms/V |      | 35   |      | ms   |

V<sub>MVREG</sub> is observed on the V<sub>18</sub>, V<sub>18REG</sub> and V<sub>18BKP</sub> pins except in the following case:

In STOP mode with MVREG OFF (LP\_PARAM13 bit). See note 2.

In STANDBY mode. See note 2.

2. In STANDBY mode,  $V_{LPVREG}$  is observed on the  $V_{18BKP}$  pin In STOP mode,  $V_{LPVREG}$  is observed on the  $V_{18}, V_{18REG}$  and  $V_{18BKP}$  pins.

Once V<sub>DD\_IO</sub> has reached 3.0 V, the RSM (Regulator Startup Monitor) generates an internal RESET during this start-up time.

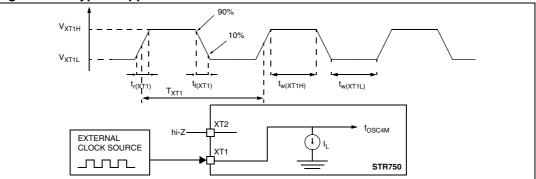

#### XRTC1 external clock source

Subject to general operating conditions for  $V_{\text{DD}\_\text{IO}}\text{,}$  and  $T_{\text{A}}\text{.}$

Table 21. XRTC1 external clock source

| Symbol                                           | Parameter                                 | Conditions <sup>(1)</sup>            | Min                    | Тур    | Max                    | Unit |

|--------------------------------------------------|-------------------------------------------|--------------------------------------|------------------------|--------|------------------------|------|

| f <sub>XRTC1</sub>                               | External clock source<br>frequency        |                                      |                        | 32.768 | 500                    | kHz  |

| V <sub>XRTC1H</sub>                              | XRTC1 input pin high<br>level voltage     |                                      | 0.7xV <sub>DD_IO</sub> |        | V <sub>DD_IO</sub>     | V    |

| V <sub>XRTC1L</sub>                              | XRTC1 input pin low<br>level voltage      | see Figure 20                        | V <sub>SS</sub>        |        | 0.3xV <sub>DD_IO</sub> | v    |

| t <sub>w(XRTC1H)</sub><br>t <sub>w(XRTC1L)</sub> | XRTC1 high or low<br>time <sup>(2)</sup>  |                                      | 900                    |        |                        | ns   |

| t <sub>r(XRTC1)</sub><br>t <sub>f(XRTC1)</sub>   | XRTC1 rise or fall time <sup>(2)</sup>    |                                      |                        |        | 50                     | 115  |

| ΙL                                               | XRTCx Input leakage<br>current            | $V_{SS} \leq V_{IN} \leq V_{DD_{I}}$ |                        | ±1     | μA                     |      |

| C <sub>IN(RTC1)</sub>                            | XRTC1 input<br>capacitance <sup>(2)</sup> |                                      |                        | 5      |                        | pF   |

| DuCy <sub>(RTC1)</sub>                           | Duty cycle                                |                                      | 30                     |        | 70                     | %    |

1. Data based on typical application software.

2. Data based on design simulation and/or technology characteristics, not tested in production.

#### Figure 20. Typical application with an external clock source

### 6.3.7 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electro magnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                                    | Level/<br>Class | l |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|---|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | $V_{DD\_IO}{=}3.3$ V or 5 V, $T_{A}{=}{+}25^{\circ}$ C, $f_{CK\_SYS}{=}32$ MHz conforms to IEC 1000-4-2       | Class A         |   |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD_IO}$ =3.3 V or 5 V,<br>T <sub>A</sub> =+25° C, f <sub>CK_SYS</sub> =32 MHz<br>conforms to IEC 1000-4-4 | Class A         | ] |

### 6.3.8 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD_{-}IO}$  and  $T_A$  unless otherwise specified.

#### Table 32.General characteristics

|                                         | I/O static characteristics                                 |                                     |                           |    |     |      |                      |

|-----------------------------------------|------------------------------------------------------------|-------------------------------------|---------------------------|----|-----|------|----------------------|

| Symbol                                  | Parameter                                                  | Con                                 | Conditions                |    | Тур | Мах  | Unit                 |

| V <sub>IL</sub>                         | Input low level voltage                                    |                                     |                           |    |     | 0.8  | v                    |

| V <sub>IH</sub>                         | Input high level voltage                                   | TTL ports                           |                           | 2  |     |      | v                    |

| V <sub>hys</sub>                        | Schmitt trigger voltage<br>hysteresis <sup>(1)</sup>       |                                     |                           |    | 400 |      | mV                   |

| I <sub>INJ(PIN)</sub>                   | Injected Current on any I/O pin                            |                                     |                           |    |     | ± 4  |                      |

| ΣI <sub>INJ(PIN</sub><br>(2)            | Total injected current (sum of all I/O and control pins)   |                                     |                           |    |     | ± 25 | mA                   |

| I <sub>lkg</sub>                        | Input leakage current on robust pins                       | See Section 6.3.12 on page 7        |                           | 72 |     |      |                      |

| , i i i i i i i i i i i i i i i i i i i | Input leakage current <sup>(3)</sup>                       | $V_{SS} \leq V_{IN} \leq V_{DI}$    | 0_10                      |    |     | ±1   |                      |

| ۱ <sub>S</sub>                          | Static current consumption <sup>(4)</sup>                  | Floating inpu                       | t mode                    |    | 200 |      | μA                   |

| Б                                       | Weak pull-up equivalent                                    | V V                                 | V <sub>DD_IO</sub> =3.3 V | 50 | 95  | 200  | kΩ                   |

| R <sub>PU</sub>                         | resistor <sup>(5)</sup>                                    | V <sub>IN</sub> =V <sub>SS</sub>    | V <sub>DD_IO</sub> =5 V   | 20 | 58  | 150  | kΩ                   |

| Б                                       | Weak pull-down equivalent                                  | V V                                 | V <sub>DD_IO</sub> =3.3 V | 25 | 80  | 180  | kΩ                   |

| R <sub>PD</sub>                         | resistor <sup>(5)</sup>                                    | V <sub>IN</sub> =V <sub>DD_IO</sub> | V <sub>DD_IO</sub> =5 V   | 20 | 50  | 120  | kΩ                   |

| C <sub>IO</sub>                         | I/O pin capacitance                                        |                                     |                           |    | 5   |      | pF                   |

| t <sub>w(IT)in</sub>                    | External interrupt/wake-up lines pulse time <sup>(6)</sup> |                                     |                           | 2  |     |      | Т <sub>АР</sub><br>в |

1. Hysteresis voltage between Schmitt trigger switching levels.

When the current limitation is not possible, the V<sub>IN</sub> absolute maximum rating must be respected, otherwise refer to I<sub>INJ(PIN)</sub> specification. A positive injection is induced by V<sub>IN</sub>>V<sub>DD\_IO</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. Refer to *Section 6.2 on page 32* for more details.

3. Leakage could be higher than max. if negative current is injected on adjacent pins.

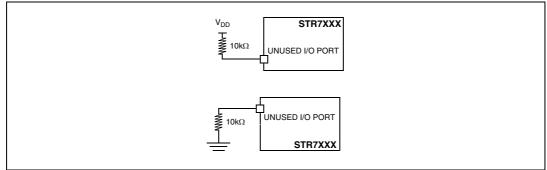

4. Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor (see *Figure 25*). Data based on design simulation and/or technology characteristics, not tested in production.

5. The R<sub>PU</sub> pull-up and R<sub>PD</sub> pull-down equivalent resistor are based on a resistive transistor.

6. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

#### Figure 25. Connecting unused I/O pins

#### Output driving current

The GP I/Os have different drive capabilities:

- O2 outputs can sink or source up to +/-2 mA.

- O4 outputs can sink or source up to +/-4 mA.

- outputs can sink or source up to +/-8 mA or can sink +20 mA (with a relaxed V<sub>OL</sub>).

In the application, the user must limit the number of I/O pins which can drive current to respect the absolute maximum rating specified in *Section 6.2.2*:

- The sum of the current sourced by all the I/Os on V<sub>DD\_IO</sub>, plus the maximum RUN consumption of the MCU sourced on V<sub>DD\_IO</sub>, can not exceed the absolute maximum rating IV<sub>DD\_IO</sub>.

- The sum of the current sunk by all the I/Os on V<sub>SS\_IO</sub> plus the maximum RUN consumption of the MCU sunk on V<sub>SS\_IO</sub> can not exceed the absolute maximum rating IV<sub>SS\_IO</sub>.

Subject to general operating conditions for  $V_{\text{DD}\ \text{IO}}$  and  $T_{\text{A}}$  unless otherwise specified.

| I/O Output drive characteristics for $V_{DD_{IO}} = 3.0$ to 3.6 V and EN33 bit =1 or $V_{DD_{IO}} = 4.5$ to 5.5 V and EN33 bit =0 |                                |                                                                                          |                                                                          |                         |            |      |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------|------------|------|--|--|

| l/O<br>Type                                                                                                                       | Symbol                         | Parameter                                                                                | Conditions                                                               | Min                     | Max        | Unit |  |  |

| O2                                                                                                                                | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for a standard<br>I/O pin when 8 pins are sunk at same<br>time  | I <sub>IO</sub> =+2 mA                                                   |                         | 0.4        |      |  |  |

|                                                                                                                                   | V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time            | I <sub>IO</sub> =-2 mA                                                   | V <sub>DD_IO</sub> -0.8 |            |      |  |  |

| O4                                                                                                                                | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for a standard<br>I/O pin when 8 pins are sunk at same<br>time  | I <sub>IO</sub> =+4 mA                                                   |                         | 0.4        |      |  |  |

|                                                                                                                                   | V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time            | I <sub>IO</sub> =-4 mA                                                   | V <sub>DD_IO</sub> -0.8 |            | V    |  |  |

|                                                                                                                                   | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for a standard<br>I/O pin when 8 pins are sunk at same<br>time  | I <sub>IO</sub> =+8 mA                                                   |                         | 0.4        |      |  |  |

| O8                                                                                                                                |                                | Output low level voltage for a high sink<br>I/O pin when 4 pins are sunk at same<br>time | I <sub>IO</sub> =+20 mA,<br>T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C |                         | 1.3<br>1.5 |      |  |  |

|                                                                                                                                   |                                |                                                                                          | I <sub>IO</sub> =+8 mA                                                   |                         | 0.4        |      |  |  |

|                                                                                                                                   | V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time            | I <sub>IO</sub> =-8 mA                                                   | V <sub>DD_IO</sub> -0.8 |            |      |  |  |

#### Table 33.Output driving current

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 6.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS\_IO</sub>.

The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 6.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD\_IO</sub>.

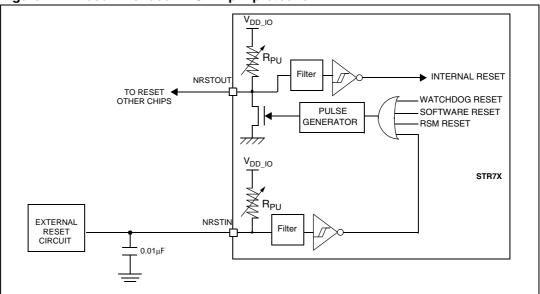

Figure 27. Recommended NRSTIN pin protection

1. The user must ensure that the level on the NRSTIN pin can go below the V<sub>IL(NRSTIN)</sub> max. level specified in NRSTIN and NRSTOUT pins on page 58. Otherwise the reset will not be taken into account internally.

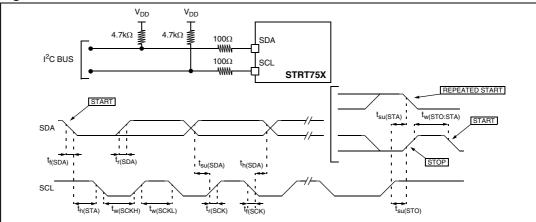

not possible to power off the STR7x while some another I<sup>2</sup>C master node remains powered on: otherwise, the STR7x will be powered by the protection diode.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standard mode<br>I <sup>2</sup> C |                    | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    | Unit |

|--------------------------------------------|-----------------------------------------|-----------------------------------|--------------------|-------------------------------------------|--------------------|------|

|                                            |                                         | Min <sup>(2)</sup>                | Max <sup>(2)</sup> | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> |      |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                               |                    | 1.3                                       |                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                               |                    | 0.6                                       |                    | μS   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                               |                    | 100                                       |                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(3)</sup>                  |                    | 0 <sup>(4)</sup>                          | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                                   | 1000               | 20+0.1C <sub>b</sub>                      | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                                   | 300                | 20+0.1C <sub>b</sub>                      | 300                |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                               |                    | 0.6                                       |                    |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                               |                    | 0.6                                       |                    | μS   |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                               |                    | 0.6                                       |                    | μs   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                               |                    | 1.3                                       |                    | μs   |

| Cb                                         | Capacitive load for each bus line       |                                   | 400                |                                           | 400                | pF   |

Table 41.

SDA and SCL characteristics

1.  $f_{PCLK}$ , must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

3. The maximum hold time  $t_{h(SDA)}$  is not applicable

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

### Figure 40. Typical application with I<sup>2</sup>C bus and timing diagram

1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

### 6.3.12 10-bit ADC characteristics

Subject to general operating conditions for  $V_{DDA\_ADC},\,f_{PCLK},$  and  $T_A$  unless otherwise specified.

| Symbol            | Parameter                                            | Conditions                                                                               | Min                                                       | Typ <sup>(1)</sup> | Max                | Unit               |

|-------------------|------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------|--------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                  |                                                                                          | 0.4                                                       |                    | 8                  | MHz                |

| V <sub>AIN</sub>  | Conversion voltage range <sup>(2)</sup>              |                                                                                          | $V_{SSA\_ADC}$                                            |                    | $V_{DDA\_ADC}$     | V                  |

| R <sub>AIN</sub>  | External input impedance <sup>(3)(4)</sup>           |                                                                                          |                                                           |                    | 10                 | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input <sup>(3)(4)</sup> |                                                                                          |                                                           |                    | 6.8                | pF                 |

| l <sub>ikg</sub>  |                                                      | +400 µA injected on any pin                                                              |                                                           |                    | 1                  | μA                 |

|                   | Induced input leakage current                        | -400 μA injected<br>on any pin<br>except specific<br>adjacent pins in<br><i>Table 46</i> |                                                           |                    | 1                  | μΑ                 |

|                   |                                                      | -400µA injected<br>on specific<br>adjacent pins in<br><i>Table 46</i>                    |                                                           | 40                 |                    | μA                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                   |                                                                                          |                                                           | 3.5                |                    | pF                 |

| +                 | Colibration Time                                     | f <sub>CK_ADC</sub> =8 MHz                                                               | 725.25                                                    |                    | μs                 |                    |

| t <sub>CAL</sub>  | Calibration Time                                     |                                                                                          | 5802                                                      |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>CONV</sub> | Total Conversion time                                | f <sub>CK_ADC</sub> =8 MHz                                                               | 3.75                                                      |                    | μs                 |                    |

|                   | (including sampling time)                            |                                                                                          | 30 (11 for sampling + 19 for<br>Successive Approximation) |                    | 1/f <sub>ADC</sub> |                    |

| I <sub>ADC</sub>  |                                                      | Sunk on<br>V <sub>DDA_ADC</sub>                                                          |                                                           | 3.7                |                    | mA                 |

Table 45.10-bit ADC characteristics

1. Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$ . They are given only as design guidelines and are not tested.

2. Calibration is needed once after each power-up.

C<sub>PARASITIC</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (3 pF). A high C<sub>PARASITIC</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

4. Depending on the input signal variation ( $f_{AIN}$ ),  $C_{AIN}$  can be increased for stabilization time and reduced to allow the use of a larger serial resistor ( $R_{AIN}$ ). It is valid for all  $f_{ADC}$  frequencies  $\leq 8$  MHz.

#### **General PCB design guidelines**

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

- Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

- Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing 0.1 μF and optionally, if needed 10 pF capacitors as close as possible to the STR7 power supply pins and a 1 to 10 μF capacitor close to the power source (see *Figure 43*).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>DDA\_ADC</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs near the A/D input being converted.

#### Software filtering of spurious conversion results

For EMC performance reasons, it is recommended to filter A/D conversion outliers using software filtering techniques.

#### Figure 43. Power supply filtering

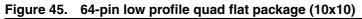

# 7 Package characteristics

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 7.1 Package mechanical data

# 8 Order codes

| Table 49. | Order codes |  |  |

|-----------|-------------|--|--|

|           |             |  |  |

| Order code  | Flash Prog.<br>Memory<br>(Bank 0)<br>Kbytes | Package        | CAN<br>Periph | USB<br>Periph | Nominal<br>Temp. Range<br>(T <sub>A</sub> ) |

|-------------|---------------------------------------------|----------------|---------------|---------------|---------------------------------------------|

| STR750FV0T6 | 64                                          |                |               |               |                                             |

| STR750FV1T6 | 128                                         | LQFP100 14x14  |               | Yes           |                                             |

| STR750FV2T6 | 256                                         |                | Vee           |               | 40 to . 05°C                                |

| STR750FV0H6 | 64                                          |                | Yes           |               | -40 to +85°C                                |

| STR750FV1H6 | 128                                         | LFBGA100 10x10 |               |               |                                             |

| STR750FV2H6 | 256                                         |                |               |               |                                             |

| STR751FR0T6 | 64                                          |                |               |               |                                             |

| STR751FR1T6 | 128                                         | LQFP64 10x10   |               | Yes           | 40.1 0.500                                  |

| STR751FR2T6 | 256                                         |                |               |               |                                             |

| STR751FR0H6 | 64                                          |                | -             |               | -40 to +85°C                                |

| STR751FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR751FR2H6 | 256                                         |                |               |               |                                             |

| STR752FR0T6 | 64                                          |                |               | íes -         |                                             |

| STR752FR1T6 | 128                                         | LQFP64 10x10   |               |               |                                             |

| STR752FR2T6 | 256                                         |                | Yes           |               | -40 to +85°C                                |

| STR752FR0H6 | 64                                          |                |               |               | -40 10 +65 C                                |

| STR752FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR752FR2H6 | 256                                         |                |               |               |                                             |

| STR752FR0T7 | 64                                          |                |               |               |                                             |

| STR752FR1T7 | 128                                         | LQFP64 10x10   |               |               |                                             |

| STR752FR2T7 | 256                                         |                | Vaa           | ies -         | -40 to +105°C                               |

| STR752FR0H7 | 64                                          |                | ies           |               |                                             |

| STR752FR1H7 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR752FR2H7 | 256                                         |                |               |               |                                             |

| STR755FR0T6 | 64                                          |                |               |               |                                             |

| STR755FR1T6 | 128                                         | LQFP64 10x10   |               |               |                                             |

| STR755FR2T6 | 256                                         |                |               |               | -40 to +85°C                                |

| STR755FR0H6 | 64                                          |                |               | -             | -40 10 +00 0                                |

| STR755FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |

| STR755FR2H6 | 256                                         |                |               |               |                                             |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com