Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                              |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 60MHz                                                               |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, SSI, SSP, UART/USART                 |

| Peripherals                | DMA, PWM, WDT                                                       |

| Number of I/O              | 38                                                                  |

| Program Memory Size        | 128KB (128K x 8)                                                    |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | A/D 11x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-LQFP                                                             |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str752fr1t7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3 Introduction

This Datasheet contains the description of the STR750F family features, pinout, Electrical Characteristics, Mechanical Data and Ordering information.

For complete information on the Microcontroller memory, registers and peripherals. Please refer to the STR750F Reference Manual.

For information on the ARM7TDMI-S core please refer to the ARM7TDMI-S Technical Reference Manual available from Arm Ltd.

For information on programming, erasing and protection of the internal Flash memory please refer to the STR7 Flash Programming Reference Manual

For information on third-party development tools, please refer to the http://www.st.com/mcu website.

# 3.1 Functional description

The STR750F family includes devices in 2 package sizes: 64-pin and 100-pin. Both types have the following common features:

### ARM7TDMI-S™ core with embedded Flash & RAM

STR750F family has an embedded ARM core and is therefore compatible with all ARM tools and software. It combines the high performance ARM7TDMI-S<sup>™</sup> CPU with an extensive range of peripheral functions and enhanced I/O capabilities. All devices have on-chip high-speed single voltage FLASH memory and high-speed RAM.

*Figure 1* shows the general block diagram of the device family.

## **Embedded Flash memory**

Up to 256 KBytes of embedded Flash is available in Bank 0 for storing programs and data. An additional Bank 1 provides 16 Kbytes of RWW (Read While Write) memory allowing it to be erased/programmed on-the-fly. This partitioning feature is ideal for storing application parameters.

- When configured in burst mode, access to Flash memory is performed at CPU clock speed with 0 wait states for sequential accesses and 1 wait state for random access (maximum 60 MHz).

- When not configured in burst mode, access to Flash memory is performed at CPU clock speed with 0 wait states (maximum 32 MHz)

### Embedded SRAM

16 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

### Enhanced interrupt controller (EIC)

In addition to the standard ARM interrupt controller, the STR750F embeds a nested interrupt controller able to handle up to 32 vectors and 16 priority levels. This additional hardware block provides flexible interrupt management features with minimal interrupt latency.

# GPIOs (general purpose input/output)

Each of the 72 GPIO pins (38 GPIOs in 64-pin devices) can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as Peripheral Alternate Function. Port 1.15 is an exception, it can be used as general-purpose input only or wake-up from STANDBY mode (WKP\_STDBY). Most of the GPIO pins are shared with digital or analog alternate functions.

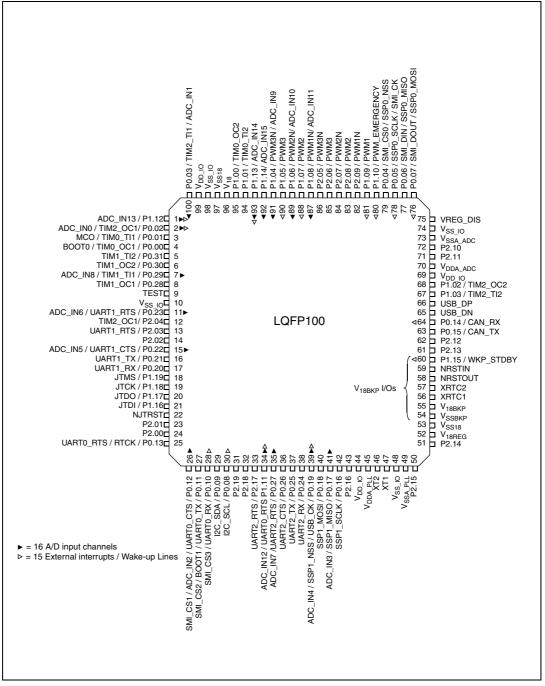

# 4 Pin description

### Port reset state

The reset state of the I/O ports is GPIO input floating. Exceptions are P1[19:16] and P0.13 which are configured as JTAG alternate functions:

- The JTAG inputs (JTDI, JTMS and JTDI) are configured as input floating and are ready to accept JTAG sequences.

- The JTAG output JTDO is configured as floating when idle (no JTAG operation) and is configured in output push-pull only when serial JTAG data must be output.

- The JTAG output RTCK is always configured as output push-pull. It outputs '0' level during the reset phase and then outputs the JTCK input signal resynchronized 3 times by the internal AHB clock.

- The GPIO\_PCx registers do not control JTAG AF selection, so the reset values of GPIO\_PCx for P1[19:16] and P0. 13 are the same as other ports. Refer to the GPIO section of the STR750 Reference Manual for the register description and reset values.

- P0.11 and P0.00 are sampled by the boot logic after reset, prior to fetching the first word of user code at address 0000 0000h.

- When booting from SMI (and only in this case), the reset state of the following GPIOs is "SMI alternate function output enabled":

- P0.07 (SMI\_DOUT)

- P0.05 (SMI\_CLK)

- P0.04 (SMI\_CS0)

- P0.06 (SMI\_DIN)

Note that the other SMI pins: SMI\_CS1,2,3 (P0.12, P0.11, P0.10) are not affected.

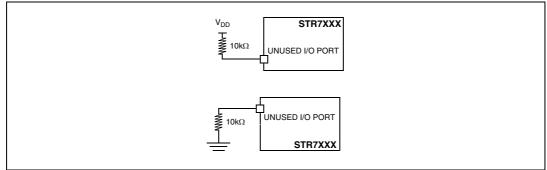

To avoid excess power consumption, unused I/O ports must be tied to ground.

|                        | Pin                     | n°                    |                        |                                  |      |                | In       | put   |                   | C          | utpu      | ıt | yc                |                                                  |                                                        |                        |

|------------------------|-------------------------|-----------------------|------------------------|----------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------------------|--------------------------------------------------------|------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                         | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)             | Alternate                                              | e function             |

| 1                      | B1                      | 1                     | B1                     | P1.12 /<br>ADC_IN13              | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT12             | O8         | х         | х  |                   | Port 1.12                                        | ADC: Analog<br>input 13                                |                        |

| 2                      | B2                      | 2                     | C2                     | P0.02 /<br>TIM2_OC1 /<br>ADC_IN0 | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT0              | O8         | x         | х  |                   | Port 0.02                                        | TIM2: Output<br>Compare 1 <sup>(4)</sup>               | ADC: Analog<br>input 0 |

| 3                      | B3                      | 3                     | C1                     | P0.01 / TIM0_TI1<br>/ MCO        | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O8         | x         | x  |                   | Port 0.01                                        | TIM0: Input<br>Capture / trigger<br>/ external clock 1 | Main Clock<br>Output   |

| 4                      | C2                      | 4                     | СЗ                     | P0.00 /<br>TIM0_OC1 /<br>BOOT0   | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O8         | x         | x  |                   | Port 0.00 /<br>Boot mode<br>selection<br>input 0 | TIM0: Output Compare 1                                 |                        |

| 5                      | C1                      |                       |                        | P0.31 / TIM1_TI2                 | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.31                                        | TIM1: Input Capture / trigger /<br>external clock 2    |                        |

| 6                      | D2                      |                       |                        | P0.30 /<br>TIM1_OC2              | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.30                                        | TIM1: Output Compare 2                                 |                        |

| Table 6. | STR750F pin | description |

|----------|-------------|-------------|

|----------|-------------|-------------|

|                        | Pin                     | n°                    |                        |                               |      |                | In       | put   |                   | C          | )utpu     | ıt | y                 |                                                       |                                                                                                                                                             |                        |  |

|------------------------|-------------------------|-----------------------|------------------------|-------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                      | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)                  | Alternate function                                                                                                                                          |                        |  |

| 91                     | A4                      | 59                    | A3                     | P1.04 / PWM3N /<br>ADC_IN9    | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | х         | х  |                   | Port 1.04                                             | PWM: PWM3<br>complementary<br>output <sup>(4)</sup>                                                                                                         | ADC: analog<br>input 9 |  |

| 92                     | A3                      |                       |                        | P1.14 /<br>ADC_IN15           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O8         | х         | х  |                   | Port 1.14                                             | ADC: analog inpu                                                                                                                                            | t 15                   |  |

| 93                     | A2                      |                       |                        | P1.13 /<br>ADC_IN14           | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT13             | O8         | х         | х  |                   | Port 1.13                                             | ADC: analog inpu                                                                                                                                            | t 14                   |  |

| 94                     | D5                      |                       |                        | P1.01 / TIM0_TI2              | I/O  | TT             | x        | х     |                   | 02         | x         | x  |                   | Port 1.01                                             | TIM0: Input Captu<br>external clock 2 (r<br>P0.05) <sup>(8)</sup>                                                                                           |                        |  |

| 95                     | E6                      |                       |                        | P1.00 /<br>TIM0_OC2           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 1.00                                             | TIM0: Output com<br>(remappable to Po                                                                                                                       |                        |  |

| 96                     | C4                      | 60                    | C4                     | V18                           | S    |                |          |       |                   |            |           |    |                   | external capa<br>See <i>Figure 4.</i><br>To be connec | for main voltage regulator. Requires<br>icitors 33nF between V18 and VSS18.<br>.2.<br>ted to the 1.8V external power supply<br>ded regulators are not used. |                        |  |

| 97                     | D4                      | 61                    | C5                     | VSS18                         | S    |                |          |       |                   |            |           |    |                   | Ground Volta                                          | ge for the main voltage regulator.                                                                                                                          |                        |  |

| 98                     | D3                      | 62                    | A2                     | VSS_IO                        | S    |                |          |       |                   |            |           |    |                   | Ground Volta                                          | ge for digital I/Os                                                                                                                                         |                        |  |

| 99                     | C3                      | 63                    | B2                     | VDD_IO                        | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                                         | e for digital I/Os                                                                                                                                          |                        |  |

| 100                    | A1                      | 64                    | A1                     | P0.03 / TIM2_TI1<br>/ ADC_IN1 | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | 02         | x         | x  |                   | Port 0.03                                             | TIM2: Input<br>Capture / trigger<br>/ external clock 1                                                                                                      | ADC: analog<br>input 1 |  |

Table 6. STR750F pin description (continued)

1. For STR755FVx part numbers, the USB pins must be left unconnected.

2. The non available pins on LQPFP64 and LFBGA64 packages are internally tied to low level.

3. None of the I/Os are True Open Drain: when configured as Open Drain, there is always a protection diode between the I/O pin and VDD\_IO.

4. In the 100-pin package, this Alternate Function is duplicated on two ports. You can configure one port to use this AF, the other port is then free for general purpose I/O (GPIO), external interrupt/wake-up lines, or analog input (ADC\_IN) where these functions are listed in the table.

5. It is mandatory that the NJTRST pin is reset to ground during the power-up phase. It is recommended to connect this pin to NRSTOUT pin (if available) or NRSTIN.

After reset, these pins are enabled as JTAG alternate function see (*Port reset state on page 16*). To use these ports as general purpose I/O (GPIO), the DBGOFF control bit in the GPIO\_REMAPOR register must be set by software (in this case, debugging these I/Os via JTAG is not possible).

7. There are two different TQFP and BGA 64-pin packages: in the first one, pins 41 and 42 are mapped to USB DN/DP while for the second one, they are mapped to P0.15/CAN\_TX and P0.14/CAN\_RX.

8. For details on remapping these alternate functions, refer to the GPIO\_REMAPOR register description.

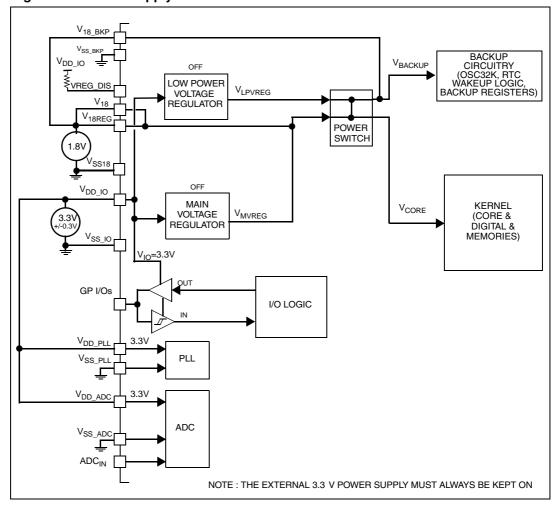

## Figure 9. Power supply scheme 2

Power supply scheme 2: Dual external 1.8V and 3.3V supply

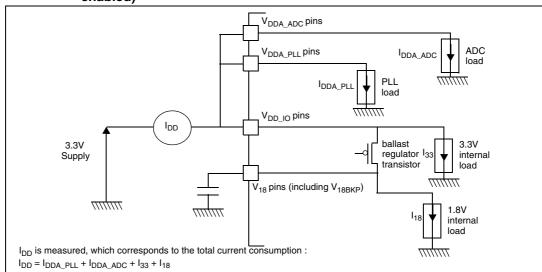

# Figure 12. Power consumption measurements in power scheme 1 (regulators enabled)

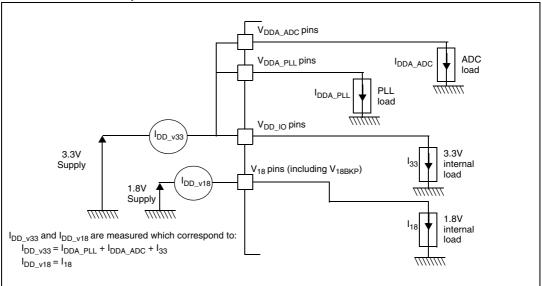

Figure 13. Power consumption measurements in power scheme 2 (regulators disabled)

# 6.3.4 Supply current characteristics

The current consumption is measured as described in *Figure 12 on page 30* and *Figure 13 on page 30*.

Subject to general operating conditions for  $V_{\text{DD}\ \text{IO}}$  , and  $T_{\text{A}}$

## Maximum power consumption

For the measurements in *Table 13* and *Table 14*, the MCU is placed under the following conditions:

- All I/O pins are configured in output push-pull 0

- All peripherals are disabled except if explicitly mentioned.

- Embedded Regulators are used to provide 1.8 V (except if explicitly mentioned).

| Symbol          | Parameter                     | Conditions <sup>(1)</sup>                                                                                                                                                                                                                               |                         | Тур <sup>(2)</sup> | Max <sup>(3)</sup> | Unit |

|-----------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|--------------------|------|

| I <sub>DD</sub> | Supply current in<br>RUN mode | External Clock with PLL<br>multiplication, code running from<br>RAM, all peripherals enabled in the<br>MRCC_PLCKEN register: f <sub>HCLK</sub> =60<br>MHz, f <sub>PCLK</sub> =30 MHz<br>Single supply scheme see <i>Figure 12</i><br>/ <i>Figure 14</i> | 3.3V<br>and 5V<br>range | 80                 | 90                 | mA   |

|                 | Supply current in<br>WFI mode | External Clock, code running from<br>RAM: f <sub>HCLK</sub> =60 MHz, f <sub>PCLK</sub> =30 MHz<br>Single supply scheme see<br><i>Figure 12./ Figure 14</i><br>Parameter setting BURST=1,<br>WFI_FLASHEN=1                                               | 3.3V<br>and 5V<br>range | 62                 | 67                 | mA   |

1. The conditions for these consumption measurements are described at the beginning of Section 6.3.4.

2. Typical data are based on  $T_A=25^\circ C,\,V_{DD\_IO}=3.3V$  or 5.0V and  $V_{18}=1.8V$  unless otherwise specified.

3. Data based on product characterisation, tested in production at  $V_{DD_{-}IO}$  max and  $V_{18}$  max (1.95V in dual supply mode or regulator output value in single supply mode) and  $T_A$  max.

### Typical power consumption

The following measurement conditions apply to Table 15, Table 16 and Table 17.

In RUN mode:

- Program is executed from Flash (except if especially mentioned). The program consists

of an infinite loop. When f<sub>HCLK</sub> > 32 MHz, burst mode is activated.

- A standard 4 MHz crystal source is used.

- In all cases the PLL is used to multiply the frequency.

- All measurements are done in the single supply scheme with internal regulators used (see *Figure 12*)

In WFI Mode:

- In WFI Mode the measurement conditions are similar to RUN mode (OSC4M and PLL enabled). In addition, the Flash can be disabled depending on burst mode activation:

- For AHB frequencies greater than 32 MHz, burst mode is activated and the Flash is kept enabled by setting the WFI\_FLASH\_EN bit (this bit cannot be reset when burst mode is activated).

- For AHB frequencies less than or equal to 32 MHz, burst mode is deactivated, WFI\_FLASH\_EN is reset and the LP\_PARAM14 bit is set (Flash is disabled in WFI mode).

In SLOW mode:

The same program as in RUN mode is executed from Flash. The CPU is clocked by the FREEOSC, OSC4M, LPOSC or OSC32K. Only EXTIT peripheral is enabled in the MRCC\_PCLKEN register.

In SLOW-WFI mode:

In SLOW-WFI, the measurement conditions are similar to SLOW mode (CPU clocked by a low frequency clock). In addition, the LP\_PARAM14 bit is set (FLASH is OFF). The WFI routine itself is executed from SRAM (it is not allowed to execute a WFI from the internal FLASH)

In STOP mode:

• Several measurements are given: in the single supply scheme with internal regulators used (see *Figure 12*): and in the dual supply scheme (see *Figure 13*).

In STANDBY mode:

- Three measurements are given:

- The RTC is disabled, only the consumption of the LPVREG and RSM remain (almost no leakage currents)

- The RTC is running, clocked by a standard 32.768 kHz crystal.

- The RTC is running, clocked by the internal Low Power RC oscillator (LPOSC)

- STANDBY mode is only supported in the single supply scheme (see Figure 12)

# Table 16.Dual supply supply typical power consumption in Run, WFI, Slow and<br/>Slow-WFI modes

To calculate the power consumption in Dual supply mode, refer to the values given in *Table 15*. and consider that this consumption is split as follows:  $I_{DD}(single supply) \sim I_{DD}(dual supply) = I_{DD} \vee 18 + I_{DD}(VDD_{IO})$

For 3.3V range:  $I_{DD(VDD_IO)} \sim 1$  to 2 mA For 5V range:  $I_{DD(VDD_IO)} \sim 2$  to 3 mA Therefore most of the consumption is sunk on the V<sub>18</sub> power supply This formula does not apply in STOP and STANDBY modes, refer to *Table 17*.

Subject to general operating conditions for  $V_{\text{DD\_IO}}\text{,}$  and  $T_{\text{A}}$

Table 17. Typical power consumption in STOP and STANDBY modes

| Symbol                         | Parameter                         | Conditions                                                   |                                            | 3.3V<br>Typ <sup>(1)</sup> | 5V<br>Typ <sup>(2)</sup> | Unit |

|--------------------------------|-----------------------------------|--------------------------------------------------------------|--------------------------------------------|----------------------------|--------------------------|------|

|                                |                                   | LP_PARAM bits: ALL OFF <sup>(5)</sup>                        |                                            | 12                         | 15                       |      |

|                                | Supply current                    | LP_PARAM bits : MVREG ON, OSC4M OFF, F<br>OFF <sup>(6)</sup> | LASH                                       | 130                        | 135                      |      |

|                                | in STOP<br>mode <sup>(4)</sup>    | LP_PARAM bits: MVREG ON, OSC4M ON , FI                       | _ASH                                       | 1950                       | 1930                     | μA   |

|                                |                                   | LP_PARAM bits: MVREG ON, OSC4M OFF, FL                       | _ASH ON <sup>(6)</sup>                     | 630                        | 635                      |      |

|                                |                                   | LP_PARAM bits: MVREG ON, OSC4M ON, FL                        | 2435                                       | 2425                       |                          |      |

| I <sub>DD</sub> <sup>(3)</sup> |                                   | LPPARAM bits: ALL OFF, with V <sub>18</sub> =1.8 V           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 5<br><1                    | 5<br><1                  |      |

|                                | Supply current                    | LP_PARAM bits: OSC4M ON, FLASH OFF                           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 410<br>1475                | 410<br>1435              | μA   |

|                                | mode <sup>(7)</sup>               | LP_PARAM bits: OSC4M OFF, FLASH ON                           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 550<br><1                  | 550<br>1                 | μΛ   |

|                                |                                   | LP_PARAM bits: OSC4M ON, FLASH ON                            | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 910<br>1475                | 910<br>1445              |      |

|                                | Supply current                    | RTC OFF                                                      |                                            | 11                         | 14                       |      |

|                                | in STANDBY<br>mode <sup>(4)</sup> | RTC ON clocked by OSC32K                                     |                                            | 14                         | 18                       | μA   |

1. Typical data are based on  $T_A=25^{\circ}$ C,  $V_{DD IO}=3.3$  V and  $V_{18}=1.8$  V unless otherwise indicated in the table.

2. Typical data are based on  $T_A=25^{\circ}C$ ,  $V_{DD\_IO}=5.0$  V and  $V_{18}=1.8$  V unless otherwise indicated in the table.

3. The conditions for these consumption measurements are described at the beginning of Section 6.3.4 on page 36.

4. Single supply scheme see *Figure 12*.

5. In this mode, the whole digital circuitry is powered internally by the LPVREG at approximately 1.4 V, which significantly reduces the leakage currents.

6. In this mode, the whole digital circuitry is powered internally by the MVREG at 1.8 V.

7. Dual supply scheme see Figure 13.

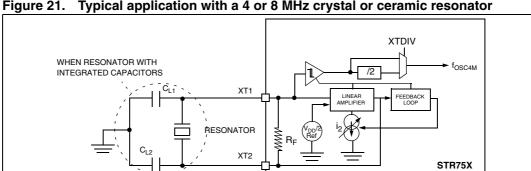

## 4/8 MHz crystal / ceramic resonator oscillator (XT1/XT2)

The STR750 system clock or the input of the PLL can be supplied by a OSC4M which is a 4 MHz clock generated from a 4 MHz or 8 MHz crystal or ceramic resonator. If using an 8 MHz oscillator, software set the XTDIV bit to enable a divider by 2 and generate a 4 MHz OSC4M clock. All the information given in this paragraph are based on product characterisation with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                                            | Parameter                                                                                                                   | Conditions                                                                                                                                     | Min | Тур | Max | Unit |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC4M</sub>                                | Oscillator frequency                                                                                                        | 4 MHz Crystal/Resonator Oscillator<br>connected on XT1/XT2 XTDIV=0<br>or<br>8 MHz Crystal/Resonator Oscillator<br>connected on XT1/XT2 XTDIV=1 |     | 4   |     | MHz  |

| R <sub>F</sub>                                    | Feedback resistor                                                                                                           |                                                                                                                                                | 200 | 240 | 270 | kΩ   |

| C <sub>L1</sub> <sup>(2)</sup><br>C <sub>L2</sub> | Recommended load<br>capacitance versus equivalent<br>serial resistance of the crystal or<br>ceramic resonator $(R_S)^{(3)}$ | R <sub>S</sub> =200Ω                                                                                                                           |     |     | 60  | pF   |

| i <sub>2</sub>                                    | XT2 driving current                                                                                                         | V <sub>DD_IO</sub> =3.3 V or 5.0 V                                                                                                             |     | 425 |     | μA   |

| t <sub>SU(OSC4M)</sub> <sup>(4)</sup>             | Startup time at V <sub>DD_IO</sub> power-up                                                                                 |                                                                                                                                                |     | 1   |     | ms   |

| Table 22. | 4/8 MHz crystal | / ceramic resonator oscillato | or (XT1/XT2) <sup>(1)</sup> |

|-----------|-----------------|-------------------------------|-----------------------------|

|-----------|-----------------|-------------------------------|-----------------------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5-pF to 25-pF range (typ.) designed for high-frequency applications and selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the 2. same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included when sizing  $C_{L1}$  and  $C_{L2}$  (10 pF can be used as a rough estimate of the combined pin and board capacitance).

- 3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- $t_{SU(OSC4M)}$  is the typical start-up time measured from the moment  $V_{DD \ IO}$  is powered (with a quick  $V_{DD \ IO}$  ramp-up from 0 to 3.3V (<50µs) to a stabilized 4MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal/ceramic resonator manufacturer.

Figure 21. Typical application with a 4 or 8 MHz crystal or ceramic resonator

# 6.3.7 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

## Functional EMS (electro magnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                                    | Level/<br>Class | l |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|---|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | $V_{DD\_IO}{=}3.3$ V or 5 V, $T_{A}{=}{+}25^{\circ}$ C, $f_{CK\_SYS}{=}32$ MHz conforms to IEC 1000-4-2       | Class A         |   |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD_IO}$ =3.3 V or 5 V,<br>T <sub>A</sub> =+25° C, f <sub>CK_SYS</sub> =32 MHz<br>conforms to IEC 1000-4-4 | Class A         | ] |

### Figure 25. Connecting unused I/O pins

### Output driving current

The GP I/Os have different drive capabilities:

- O2 outputs can sink or source up to +/-2 mA.

- O4 outputs can sink or source up to +/-4 mA.

- outputs can sink or source up to +/-8 mA or can sink +20 mA (with a relaxed V<sub>OL</sub>).

In the application, the user must limit the number of I/O pins which can drive current to respect the absolute maximum rating specified in *Section 6.2.2*:

- The sum of the current sourced by all the I/Os on V<sub>DD\_IO</sub>, plus the maximum RUN consumption of the MCU sourced on V<sub>DD\_IO</sub>, can not exceed the absolute maximum rating IV<sub>DD\_IO</sub>.

- The sum of the current sunk by all the I/Os on V<sub>SS\_IO</sub> plus the maximum RUN consumption of the MCU sunk on V<sub>SS\_IO</sub> can not exceed the absolute maximum rating IV<sub>SS\_IO</sub>.

Subject to general operating conditions for  $V_{\text{DD}\ \text{IO}}$  and  $T_{\text{A}}$  unless otherwise specified.

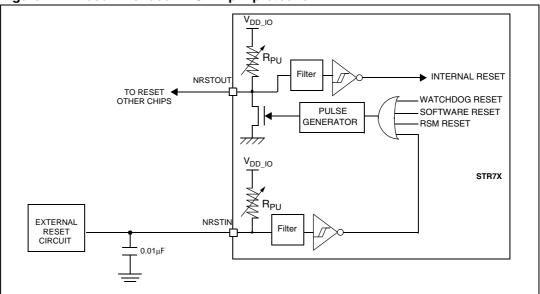

Figure 27. Recommended NRSTIN pin protection

1. The user must ensure that the level on the NRSTIN pin can go below the V<sub>IL(NRSTIN)</sub> max. level specified in NRSTIN and NRSTOUT pins on page 58. Otherwise the reset will not be taken into account internally.

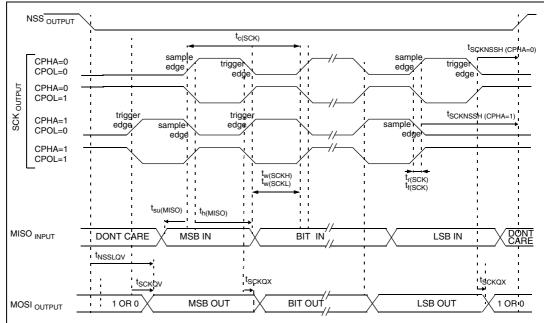

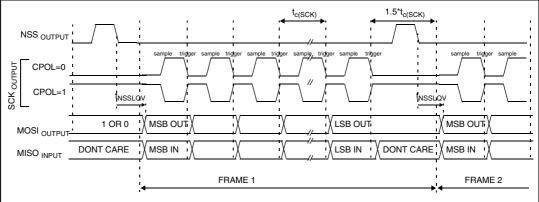

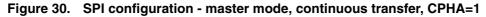

Figure 28. SPI configuration - master mode, single transfer

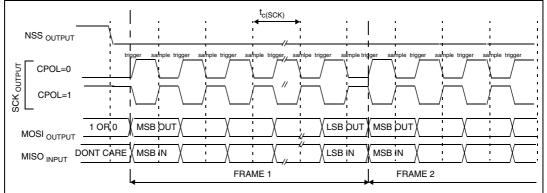

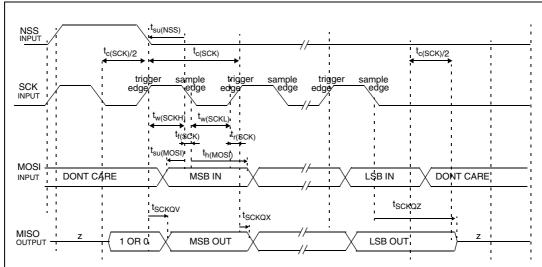

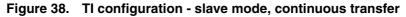

# SSP synchronous serial peripheral in slave mode (SPI or TI mode)

Subject to general operating conditions with  $C_L\approx 45~\text{pF}$

| Table 39.             | SSP Slave mode charac      | teristic | 63.7    |                           |                                                                                                                                                               |      |

|-----------------------|----------------------------|----------|---------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Symbol                | Parameter                  | Con      | ditions | Min                       | Max                                                                                                                                                           | Unit |

| f                     | SPI clock frequency        |          | SSP0    |                           | 2.66 MHz                                                                                                                                                      | MHz  |

| f <sub>SCK</sub>      | SPI clock frequency        |          | SSP1    |                           | (f <sub>PLCK</sub> /12)                                                                                                                                       |      |

| +                     | NSS input setup time w.r.t |          | SSP0    | 0                         |                                                                                                                                                               |      |

| t <sub>su(NSS)</sub>  | SCK first edge             |          | SSP1    | 0                         |                                                                                                                                                               |      |

| +                     | NSS input hold time w.r.t  |          | SSP0    | t <sub>PCLK</sub> +15ns   |                                                                                                                                                               |      |

| t <sub>h(NSS)</sub>   | SCK last edge              |          | SSP1    | t <sub>PCLK</sub> +15ns   |                                                                                                                                                               |      |

| +                     | NSS low to Data Output     |          | SSP0    | 2t <sub>PCLK</sub>        | 3t <sub>PCLK</sub> +30 ns                                                                                                                                     |      |

| t <sub>NSSLQV</sub>   | MISO valid time            |          | SSP1    | 2t <sub>PCLK</sub>        | 3t <sub>PCLK</sub> +30 ns                                                                                                                                     |      |

| +                     | NSS low to Data Output     |          | SSP0    | 2t <sub>PCLK</sub>        | 3t <sub>PCLK</sub> +15 ns                                                                                                                                     |      |

| t <sub>NSSLQZ</sub>   | MISO invalid time          |          | SSP1    | 2t <sub>PCLK</sub>        | 3t <sub>PCLK</sub> +15 ns                                                                                                                                     | ns   |

| t                     | SCK trigger edge to data   |          | SSP0    |                           | 15                                                                                                                                                            | 115  |

| t <sub>SCKQV</sub>    | output MISO valid time     |          | SSP1    |                           | 30                                                                                                                                                            |      |

| t                     | SCK trigger edge to data   |          | SSP0    | 2t <sub>PCLK</sub>        |                                                                                                                                                               |      |

| t <sub>SCKQX</sub>    | output MISO invalid time   |          | SSP1    | 2t <sub>PCLK</sub>        |                                                                                                                                                               |      |

| t areas               | MOSI setup time w.r.t SCK  |          | SSP0    | 0                         |                                                                                                                                                               |      |

| t <sub>su(MOSI)</sub> | sampling edge              |          | SSP1    | 0                         |                                                                                                                                                               |      |

| tu u com              | MOSI hold time w.r.t SCK   |          | SSP0    | 3t <sub>PCLK</sub> +15 ns |                                                                                                                                                               |      |

| t <sub>h(MOSI)</sub>  | sampling edge              |          | SSP1    | 3t <sub>PCLK</sub> +15 ns | 2.66 MHz<br>(f <sub>PLCK</sub> /12)<br>3t <sub>PCLK</sub> +30 ns<br>3t <sub>PCLK</sub> +30 ns<br>3t <sub>PCLK</sub> +15 ns<br>3t <sub>PCLK</sub> +15 ns<br>15 |      |

Table 39.

SSP slave mode characteristics<sup>(1)</sup>

1. Data based on characterisation results, not tested in production.

Figure 33. SPI configuration, slave mode with CPHA=0, single transfer

Figure 37. TI configuration - slave mode, single transfer

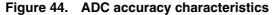

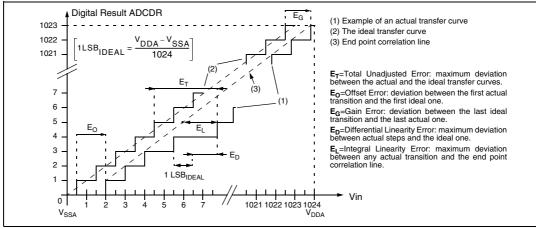

| ADC accuracy with $f_{CK_SYS}$ = 20 MHz, $f_{ADC}$ =8 MHz, $R_{AIN}$ < 10 k $\Omega$<br>This assumes that the ADC is calibrated <sup>(1)</sup> |                                                 |                             |      |      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------|------|------|------|

| Symbol                                                                                                                                         | Parameter                                       | Conditions                  | Тур  | Max  | Unit |

| IE <sub>T</sub> I                                                                                                                              | Total unadjusted error <sup>(2) (3)</sup>       | V <sub>DDA_ADC</sub> =3.3 V | 1    | 1.2  | -    |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | 1    | 1.2  |      |

| IE <sub>O</sub> I                                                                                                                              | Offset error <sup>(2) (3)</sup>                 | V <sub>DDA_ADC</sub> =3.3 V | 0.15 | 0.5  |      |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | 0.15 | 0.5  |      |

| E <sub>G</sub>                                                                                                                                 | Gain Error <sup>(2) (3)</sup>                   | V <sub>DDA_ADC</sub> =3.3 V | -0.8 | -0.2 | LSB  |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | -0.8 | -0.2 | LOD  |

| IE <sub>D</sub> I                                                                                                                              | Differential linearity error <sup>(2) (3)</sup> | V <sub>DDA_ADC</sub> =3.3 V | 0.7  | 0.9  |      |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | 0.7  | 0.9  |      |

| ΙΕ <sub>L</sub> Ι                                                                                                                              | Integral linearity error <sup>(2) (3)</sup>     | V <sub>DDA_ADC</sub> =3.3 V | 0.6  | 0.8  |      |

|                                                                                                                                                |                                                 | V <sub>DDA_ADC</sub> =5.0 V | 0.6  | 0.8  |      |

### Table 47.ADC accuracy

1. Calibration is needed once after each power-up.

2. Refer to ADC accuracy vs. negative injection current on page 73

3. ADC Accuracy vs. MCO (Main Clock Output): the ADC accuracy can be significantly degraded when activating the MCO on pin P0.01 while converting an analog channel (especially those which are close to the MCO pin). To avoid this, when an ADC conversion is launched, it is strongly recommended to disable the MCO.

75/84

# 7.2 Thermal characteristics

The maximum chip junction temperature (T<sub>Jmax</sub>) must never exceed the values given in *Table 10: General operating conditions on page 34*.

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

Where:

- T<sub>Amax</sub> is the maximum Ambient Temperature in °C,

- $\Theta_{JA}$  is the Package Junction-to-Ambient Thermal Resistance, in ° C/W,

- $P_{Dmax}$  is the sum of  $P_{INTmax}$  and  $P_{I/Omax} (P_{Dmax} = P_{INTmax} + P_{I/Omax})$ ,

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum Power Dissipation on Output Pins. Where:

$\mathsf{P}_{\mathsf{I}/\mathsf{Omax}} = \Sigma (\mathsf{V}_{\mathsf{OL}}^* \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}}^* \mathsf{V}_{\mathsf{OH}})^* \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

Table 48.Thermal characteristics<sup>(1)</sup>

| Symbol        | Parameter                                                                   | Value | Unit |

|---------------|-----------------------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LQFP 100 - 14 x 14 mm / 0.5 mm pitch | 46    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LQFP 64 - 10 x 10 mm / 0.5 mm pitch  | 45    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LFBGA 64 - 8 x 8 x 1.7mm             | 58    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LFBGA 100 - 10 x 10 x 1.7mm          | 41    | °C/W |

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

# 7.2.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

# 8 Order codes

| Table 49. | Order codes |  |  |

|-----------|-------------|--|--|

|           |             |  |  |

| Order code  | Flash Prog.<br>Memory<br>(Bank 0)<br>Kbytes | Package        | CAN<br>Periph | USB<br>Periph | Nominal<br>Temp. Range<br>(T <sub>A</sub> ) |  |

|-------------|---------------------------------------------|----------------|---------------|---------------|---------------------------------------------|--|

| STR750FV0T6 | 64                                          |                | Vez           | Yes           |                                             |  |

| STR750FV1T6 | 128                                         | LQFP100 14x14  |               |               | -40 to +85°C                                |  |

| STR750FV2T6 | 256                                         |                |               |               |                                             |  |

| STR750FV0H6 | 64                                          |                | Yes           |               |                                             |  |

| STR750FV1H6 | 128                                         | LFBGA100 10x10 |               |               |                                             |  |

| STR750FV2H6 | 256                                         |                |               |               |                                             |  |

| STR751FR0T6 | 64                                          |                |               | Yes           | -40 to +85°C                                |  |

| STR751FR1T6 | 128                                         | LQFP64 10x10   |               |               |                                             |  |

| STR751FR2T6 | 256                                         |                |               |               |                                             |  |

| STR751FR0H6 | 64                                          |                | -             |               |                                             |  |

| STR751FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |  |

| STR751FR2H6 | 256                                         |                |               |               |                                             |  |

| STR752FR0T6 | 64                                          |                | Yes           | -             | -40 to +85°C                                |  |

| STR752FR1T6 | 128                                         | LQFP64 10x10   |               |               |                                             |  |

| STR752FR2T6 | 256                                         |                |               |               |                                             |  |

| STR752FR0H6 | 64                                          |                |               |               |                                             |  |

| STR752FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |  |

| STR752FR2H6 | 256                                         |                |               |               |                                             |  |

| STR752FR0T7 | 64                                          |                |               | -             |                                             |  |

| STR752FR1T7 | 128                                         | LQFP64 10x10   | Yes           |               | -40 to +105°C                               |  |

| STR752FR2T7 | 256                                         |                |               |               |                                             |  |

| STR752FR0H7 | 64                                          |                |               |               |                                             |  |

| STR752FR1H7 | 128                                         | LFBGA64 8x8    |               |               |                                             |  |

| STR752FR2H7 | 256                                         |                |               |               |                                             |  |

| STR755FR0T6 | 64                                          |                | -             |               | -40 to +85°C                                |  |

| STR755FR1T6 | 128                                         | LQFP64 10x10   |               | -             |                                             |  |

| STR755FR2T6 | 256                                         |                |               |               |                                             |  |

| STR755FR0H6 | 64                                          |                |               |               | -40 10 +00 0                                |  |

| STR755FR1H6 | 128                                         | LFBGA64 8x8    |               |               |                                             |  |

| STR755FR2H6 | 256                                         |                |               |               |                                             |  |