Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                            |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 60MHz                                                               |

| Connectivity               | I <sup>2</sup> C, SPI, SSI, SSP, UART/USART                         |

| Peripherals                | DMA, PWM, WDT                                                       |

| Number of I/O              | 38                                                                  |

| Program Memory Size        | 64KB (64K x 8)                                                      |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | A/D 11x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-LQFP                                                             |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str755fr0t6 |

|                            |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Serial memory interface (SMI)

The Serial Memory interface is directly able to access up to 4 serial FLASH devices. It can be used to access data, execute code directly or boot the application from external memory. The memory is addressed as 4 banks of up to 16 Mbytes each.

#### **Clocks and start-up**

After RESET or when exiting from Low Power Mode, the CPU is clocked immediately by an internal RC oscillator (FREEOSC) at a frequency centered around 5 MHz, so the application code can start executing without delay. In parallel, the 4/8 MHz Oscillator is enabled and its stabilization time is monitored using a dedicated counter.

An oscillator failure detection is implemented: when the clock disappears on the XT1 pin, the circuit automatically switches to the FREEOSC oscillator and an interrupt is generated.

In Run mode, the AHB and APB clock speeds can be set at a large number of different frequencies thanks to the PLL and various prescalers: up to 60 MHz for AHB and up to 32 MHz for APB when fetching from Flash (64 MHz and 32 MHz when fetching from SRAM).

In SLOW mode, the AHB clock can be significantly decreased to reduce power consumption.

The built-in Clock Controller also provides the 48 MHz USB clock directly without any extra oscillators or PLL. For instance, starting from the 4 MHz crystal source, it is possible to obtain in parallel 60 MHz for the AHB clock, 48 MHz for the USB clock and 30 MHz for the APB peripherals.

#### **Boot modes**

At start-up, boot pins are used to select one of five boot options:

- Boot from internal flash

- Boot from external serial Flash memory

- Boot from internal boot loader

- Boot from internal SRAM

Booting from SMI memory allows booting from a serial flash. This way, a specific boot monitor can be implemented. Alternatively, the STR750F can boot from the internal boot loader that implements a boot from UART.

#### **Power supply schemes**

You can connect the device in any of the following ways depending on your application.

- Power Scheme 1: Single external 3.3V power source. In this configuration the V<sub>CORE</sub> supply required for the internal logic is generated internally by the main voltage regulator and the V<sub>BACKUP</sub> supply is generated internally by the low power voltage regulator. This scheme has the advantage of requiring only one 3.3V power source.

- Power Scheme 2: Dual external 3.3V and 1.8V power sources. In this configuration, the internal voltage regulators are switched off by forcing the VREG\_DIS pin to high level. V<sub>CORE</sub> is provided externally through the V<sub>18</sub> and V<sub>18REG</sub> power pins and V<sub>BACKUP</sub> through the V<sub>18\_BKP</sub> pin. This scheme is intended to save power consumption for applications which already provide an 1.8V power supply.

- Power Scheme 3: Single external 5.0V power source. In this configuration the V<sub>CORE</sub> supply required for the internal logic is generated internally by the main voltage

regulator and the  $V_{BACKUP}$  supply is generated internally by the low power voltage regulator. This scheme has the advantage of requiring only one 5.0V power source.

- Power Scheme 4: Dual external 5.0V and 1.8V power sources. In this configuration, the internal voltage regulators are switched off, by forcing the VREG\_DIS pin to high level. V<sub>CORE</sub> is provided externally through the V<sub>18</sub> and V<sub>18REG</sub> power pins and V<sub>BACKUP</sub> through the V<sub>18\_BKP</sub> pin. This scheme is intended to provide 5V I/O capability.

- **Caution:** When powered by 5.0V, the USB peripheral cannot operate.

#### Low power modes

The STR750F supports 5 low power modes, SLOW, PCG, WFI, STOP and STANDBY.

- SLOW MODE: the system clock speed is reduced. Alternatively, the PLL and the main oscillator can be stopped and the device is driven by a low power clock (f<sub>RTC</sub>). The clock is either an external 32.768 kHz oscillator or the internal low power RC oscillator.

- PCG MODE (Peripheral Clock Gating MODE): When the peripherals are not used, their APB clocks are gated to optimize the power consumption.

- WFI MODE (Wait For Interrupts): only the CPU clock is stopped, all peripherals continue to work and can wake-up the CPU when IRQs occur.

- STOP MODE: all clocks/peripherals are disabled. It is also possible to disable the oscillators and the Main Voltage Regulator (In this case the V<sub>CORE</sub> is entirely powered by V<sub>18\_BKP</sub>). This mode is intended to achieve the lowest power consumption with SRAM and registers contents retained. The system can be woken up by any of the external interrupts / wake-up lines or by the RTC timer which can optionally be kept running. The RTC can be clocked either by the 32.768 kHz Crystal or the Low Power RC Oscillator.

Alternatively, STOP mode gives flexibility to keep the either main oscillator, or the Flash or the Main Voltage Regulator enabled when a fast start after wake-up is preferred (at the cost of some extra power consumption).

- STANDBY MODE: This mode (only available in single supply power schemes) is intended to achieve the lowest power consumption even when the temperature is increasing. The digital power supply (V<sub>CORE</sub>) is completely removed (no leakage even at high ambient temperature). SRAM and all register contents are lost. Only the RTC remains powered by V<sub>18\_BKP</sub> The STR750F can be switched back from STANDBY to RUN mode by a trigger event on the WKP\_STDBY pin or an alarm timeout on the RTC counter.

- **Caution:** It is important to bear in mind that it is forbidden to remove power from the V<sub>DD\_IO</sub> power supply in any of the Low Power Modes (even in STANDBY MODE).

#### DMA

The flexible 4-channel general-purpose DMA is able to manage memory to memory, peripheral to memory and memory to peripheral transfers. The DMA controller supports circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

The DMA can be used with the main peripherals: UART0, SSP0, Motor control PWM timer (PWM), standard timer TIM0 and ADC.

#### RTC (real-time clock)

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a

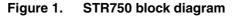

## 3.2 Block diagram

## 4.1 Pin description table

### Legend / abbreviations for Table 6:

| Туре:                              | I = input, O = output, S = supply,                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input levels:                      | All Inputs are LVTTL at $V_{DD_IO} = 3.3V+/-0.3V$ or TTL at $V_{DD_IO} = 5V\pm 0.5V$ . In both cases, $T_T$ means $V_{ILmax} = 0.8V V_{IHmin} = 2.0V$                                                                                                                                                                                                                                 |

| Inputs:                            | All inputs can be configured as floating or with internal weak pull-up or pull down (pu/pd)                                                                                                                                                                                                                                                                                           |

| Outputs:                           | <ul> <li>All Outputs can be configured as Open Drain (OD) or<br/>Push-Pull (PP) (see also note 6 below <i>Table 6</i>).</li> <li>There are 3 different types of Output with different<br/>drives and speed characteristics:</li> <li>- O8: f<sub>max</sub> = 40 MHz on C<sub>L</sub>=50pF and 8 mA static<br/>drive capability for V<sub>OL</sub>=0.4V and up to 20 mA for</li> </ul> |

|                                    | <ul> <li>V<sub>OL</sub>=1.3V (see<i>Output driving current on page 55</i>)</li> <li>O4: f<sub>max</sub> = 20 MHz on C<sub>L</sub>=50pF and 4 mA static drive capability for V<sub>OL</sub>=0.4V (see<i>Output driving</i>)</li> </ul>                                                                                                                                                 |

|                                    | <i>current on page 55</i> )<br>- O2: $f_{max} = 10 \text{ MHz on } C_L=50 \text{pF}$ and 2 mA static                                                                                                                                                                                                                                                                                  |

|                                    | drive capability of for V <sub>OL</sub> =0.4V (see <i>Output driving current on page 55</i> )                                                                                                                                                                                                                                                                                         |

| External interrupts/wake-up lines: | EITx                                                                                                                                                                                                                                                                                                                                                                                  |

#### Port reset state

The reset state of the I/O ports is GPIO input floating. Exceptions are P1[19:16] and P0.13 which are configured as JTAG alternate functions:

- The JTAG inputs (JTDI, JTMS and JTDI) are configured as input floating and are ready to accept JTAG sequences.

- The JTAG output JTDO is configured as floating when idle (no JTAG operation) and is configured in output push-pull only when serial JTAG data must be output.

- The JTAG output RTCK is always configured as output push-pull. It outputs '0' level during the reset phase and then outputs the JTCK input signal resynchronized 3 times by the internal AHB clock.

- The GPIO\_PCx registers do not control JTAG AF selection, so the reset values of GPIO\_PCx for P1[19:16] and P0. 13 are the same as other ports. Refer to the GPIO section of the STR750 Reference Manual for the register description and reset values.

- P0.11 and P0.00 are sampled by the boot logic after reset, prior to fetching the first word of user code at address 0000 0000h.

- When booting from SMI (and only in this case), the reset state of the following GPIOs is "SMI alternate function output enabled":

- P0.07 (SMI\_DOUT)

- P0.05 (SMI\_CLK)

- P0.04 (SMI\_CS0)

- P0.06 (SMI\_DIN)

Note that the other SMI pins: SMI\_CS1,2,3 (P0.12, P0.11, P0.10) are not affected.

To avoid excess power consumption, unused I/O ports must be tied to ground.

|                        | Pin                     | n°                    |                        |                                  |      |                | In       | put   |                   | C          | utpu      | ıt | yc                |                                                  |                                                        |                        |

|------------------------|-------------------------|-----------------------|------------------------|----------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------------------|--------------------------------------------------------|------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                         | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)             | Alternate                                              | e function             |

| 1                      | B1                      | 1                     | B1                     | P1.12 /<br>ADC_IN13              | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT12             | O8         | х         | х  |                   | Port 1.12                                        | ADC: Analog<br>input 13                                |                        |

| 2                      | B2                      | 2                     | C2                     | P0.02 /<br>TIM2_OC1 /<br>ADC_IN0 | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT0              | O8         | x         | х  |                   | Port 0.02                                        | TIM2: Output<br>Compare 1 <sup>(4)</sup>               | ADC: Analog<br>input 0 |

| 3                      | B3                      | 3                     | C1                     | P0.01 / TIM0_TI1<br>/ MCO        | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O8         | x         | х  |                   | Port 0.01                                        | TIM0: Input<br>Capture / trigger<br>/ external clock 1 | Main Clock<br>Output   |

| 4                      | C2                      | 4                     | СЗ                     | P0.00 /<br>TIM0_OC1 /<br>BOOT0   | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O8         | x         | x  |                   | Port 0.00 /<br>Boot mode<br>selection<br>input 0 | TIM0: Output Compare 1                                 |                        |

| 5                      | C1                      |                       |                        | P0.31 / TIM1_TI2                 | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.31                                        | TIM1: Input Capture / trigger /<br>external clock 2    |                        |

| 6                      | D2                      |                       |                        | P0.30 /<br>TIM1_OC2              | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.30                                        | TIM1: Output Con                                       | npare 2                |

| Table 6. | STR750F pin | description |

|----------|-------------|-------------|

|----------|-------------|-------------|

|                        | Pin                     | n°                    |                        |                                    |      |                | In       | put   |                   | C          | )utpu     | ıt | Š                 |                                      |                                                     |                                                    |

|------------------------|-------------------------|-----------------------|------------------------|------------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------|-----------------------------------------------------|----------------------------------------------------|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                           | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset) | Alternate                                           | e function                                         |

| 68                     | A10                     |                       |                        | P1.02 /<br>TIM2_OC2                | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 1.02                            | TIM2: Output con<br>(remappable to P                | npare 2<br>0.06) <sup>(8)</sup>                    |

| 69                     | D7                      | 44                    | C6                     | VDD_IO                             | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                        | e for digital I/Os                                  |                                                    |

| 70                     | D8                      | 45                    | D6                     | VDDA_ADC                           | S    |                |          |       |                   |            |           |    |                   | Supply Voltag                        | e for A/D converte                                  | r                                                  |

| 71                     | C9                      |                       |                        | P2.11                              | I/O  | TT             | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.11                            |                                                     |                                                    |

| 72                     | B10                     |                       |                        | P2.10                              | I/O  | TT             | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.10                            |                                                     |                                                    |

| 73                     | C8                      | 46                    | D7                     | VSSA_ADC                           | S    |                |          |       |                   |            |           |    |                   | Ground Volta                         | ge for A/D converte                                 | er                                                 |

| 74                     | C7                      | 47                    | C7                     | VSS_IO                             | S    |                |          |       |                   |            |           |    |                   | Ground Volta                         | ge for digital I/Os                                 |                                                    |

| 75                     | E8                      | 48                    | D5                     | VREG_DIS                           | I    | TT             |          |       |                   |            |           |    |                   | Voltage Regu                         | lator Disable input                                 |                                                    |

| 76                     | A9                      | 49                    | A8                     | P0.07 /<br>SMI_DOUT /<br>SSP0_MOSI | I/O  | TT             | x        | x     | EIT2              | O4         | x         | x  |                   | Port 0.07                            | Serial Memory<br>Interface: data<br>output          | SSP0: Master out<br>Slave in data                  |

| 77                     | A8                      | 50                    | A7                     | P0.06 / SMI_DIN<br>/ SSP0_MISO     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O4         | х         | х  |                   | Port 0.06                            | Serial Memory<br>Interface: data<br>input           | SSP0: Master in Slave out data                     |

| 78                     | A7                      | 51                    | A6                     | P0.05 /<br>SSP0_SCLK /<br>SMI_CK   | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT1              | 04         | x         | x  |                   | Port 0.05                            | SSP0: Serial<br>clock                               | Serial Memory<br>Interface: Serial<br>clock output |

| 79                     | B7                      | 52                    | B6                     | P0.04 / SMI_CS0<br>/ SSP0_NSS      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O4         | x         | x  |                   | Port 0.04                            | Serial Memory<br>Interface: chip<br>select output 0 | SSP0: Slave select input                           |

| 80                     | C5                      | 53                    | B7                     | P1.10<br>PWM_EMERGE<br>NCY         | I/O  | Τ <sub>Τ</sub> | x        | х     | EIT10             | O2         | x         | x  |                   | Port 1.10                            | PWM: Emergency                                      | y input                                            |

| 81                     | B6                      | 54                    | B5                     | P1.09 / PWM1                       | I/O  | TT             | х        | х     | EIT9              | 04         | Х         | Х  |                   | Port 1.09                            | PWM: PWM1 out                                       | put                                                |

| 82                     | C6                      |                       |                        | P2.09 / PWM1N                      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 2.09                            | PWM: PWM1 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 83                     | G7                      |                       |                        | P2.08 / PWM2                       | I/O  | TT             | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.08                            | PWM: PWM2 out                                       | put <sup>(4)</sup>                                 |

| 84                     | G6                      |                       |                        | P2.07 / PWM2N                      | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 2.07                            | PWM: PWM2 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 85                     | F7                      |                       |                        | P2.06 / PWM3                       | I/O  | TT             | х        | х     |                   | 02         | х         | х  |                   | Port 2.06                            | PWM: PWM3 output <sup>(4)</sup>                     |                                                    |

| 86                     | F6                      |                       |                        | P2.05 / PWM3N                      | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 2.05                            | PWM: PWM3 cor<br>output <sup>(4)</sup>              | nplementary                                        |

| 87                     | A6                      | 55                    | A5                     | P1.08 / PWM1N /<br>ADC_IN11        | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | х         | х  |                   | Port 1.08                            | PWM: PWM1<br>complementary<br>output <sup>(8)</sup> | ADC: analog<br>input 11                            |

| 88                     | B5                      | 56                    | B4                     | P1.07 / PWM2                       | I/O  | TT             | х        | х     | EIT8              | 04         | х         | Х  |                   | Port 1.07                            | PWM: PWM2 out                                       | put <sup>(4)</sup>                                 |

| 89                     | A5                      | 57                    | A4                     | P1.06 / PWM2N /<br>ADC_IN10        | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 04         | x         | х  |                   | Port 1.06                            | PWM: PWM2<br>complementary<br>output <sup>(4)</sup> | ADC: analog<br>input 10                            |

| 90                     | B4                      | 58                    | B3                     | P1.05 / PWM3                       | I/O  | TT             | х        | х     | EIT7              | O4         | х         | Х  |                   | Port 1.05                            | PWM: PWM3 out                                       | put <sup>(4)</sup>                                 |

### Table 6. STR750F pin description (continued)

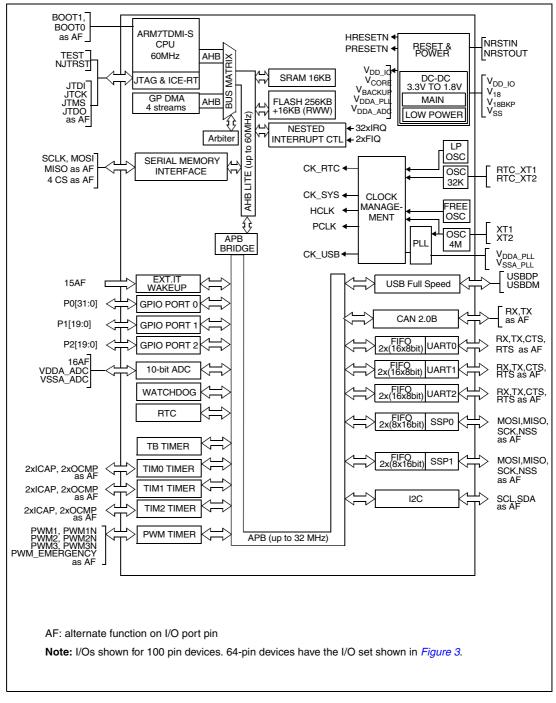

## 5 Memory map

| Figure 5. | Memory map |

|-----------|------------|

|-----------|------------|

## 6.3 Operating conditions

#### 6.3.1 General operating conditions

Subject to general operating conditions for  $V_{\text{DD}\ \text{IO}}$  , and  $T_{\text{A}}$  unless otherwise specified.

| Table 10. General | operating conditions |

|-------------------|----------------------|

|-------------------|----------------------|

| Symbol             | Parameter                                                  | Conditions                                                | Min  | Max  | Unit |  |  |  |

|--------------------|------------------------------------------------------------|-----------------------------------------------------------|------|------|------|--|--|--|

|                    |                                                            | Accessing SRAM with 0 wait states                         | 0    | 64   |      |  |  |  |

|                    |                                                            | Accessing Flash in burst<br>mode, T <sub>A</sub> ≤85° C   | 0    | 60   |      |  |  |  |

| f <sub>HCLK</sub>  | Internal AHB Clock frequency                               | Accessing Flash in burst<br>mode<br>T <sub>A</sub> >85° C |      | 56   | MHz  |  |  |  |

|                    |                                                            | Accessing Flash with 0 wait states                        | 0    | 32   |      |  |  |  |

|                    |                                                            | Write access to Flash registers <sup>(1)</sup>            | 0    | 30   |      |  |  |  |

|                    |                                                            | Accessing Flash in RWW mode                               | 0    | 16   |      |  |  |  |

| f <sub>PCLK</sub>  | Internal APB Clock frequency                               |                                                           | 0    | 32   | MHz  |  |  |  |

|                    | Standard Operating Voltage<br>Power Scheme 1 & 2           |                                                           | 3.0  | 3.6  |      |  |  |  |

| V <sub>DD_IO</sub> | Standard Operating Voltage<br>Power Scheme 3 & 4           |                                                           | 4.5  | 5.5  | V    |  |  |  |

| V <sub>18</sub>    | Standard Operating Voltage<br>Power Scheme 2 & 4           |                                                           | 1.65 | 1.95 |      |  |  |  |

|                    |                                                            | LQFP100                                                   |      | 434  |      |  |  |  |

| Р                  | Power dissipation at $T_A = 85^{\circ} C$                  | LQFP64                                                    |      | 444  |      |  |  |  |

| PD                 | for suffix 6 or $T_A$ = 105° C for suffix 7 <sup>(2)</sup> | LFBGA100                                                  |      | 487  | mW   |  |  |  |

|                    |                                                            | LFBGA64                                                   |      | 344  |      |  |  |  |

|                    | Ambient temperature for 6 suffix                           | Maximum power dissipation                                 | -40  | 85   | °C   |  |  |  |

| T <sub>A</sub>     | version                                                    | Low power dissipation <sup>(3)</sup>                      | -40  | 105  | °C   |  |  |  |

| 'A                 | Ambient temperature for 7 suffix                           | Maximum power dissipation                                 | -40  | 105  | °C   |  |  |  |

|                    | version                                                    | Low power dissipation <sup>(3)</sup>                      | -40  | 125  | °C   |  |  |  |

| ТJ                 | Junction temperature range                                 | 6 Suffix Version                                          | -40  | 105  | °C   |  |  |  |

| ۰J                 |                                                            | 7 Suffix Version                                          | -40  | 125  | °C   |  |  |  |

1. Write access to Flash registers is either a program, erase, set protection or un-set protection operation.

2. If  $T_A$  is lower, higher PD values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.2: Thermal characteristics on page 79).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.2: Thermal characteristics on page 79).

# Table 16.Dual supply supply typical power consumption in Run, WFI, Slow and<br/>Slow-WFI modes

To calculate the power consumption in Dual supply mode, refer to the values given in *Table 15*. and consider that this consumption is split as follows:  $I_{DD}(single supply) \sim I_{DD}(dual supply) = I_{DD} \vee 18 + I_{DD}(VDD_{IO})$

For 3.3V range:  $I_{DD(VDD_IO)} \sim 1$  to 2 mA For 5V range:  $I_{DD(VDD_IO)} \sim 2$  to 3 mA Therefore most of the consumption is sunk on the V<sub>18</sub> power supply This formula does not apply in STOP and STANDBY modes, refer to *Table 17*.

Subject to general operating conditions for  $V_{\text{DD\_IO}}\text{,}$  and  $T_{\text{A}}$

Table 17. Typical power consumption in STOP and STANDBY modes

| Symbol                         | Parameter                         | Conditions                                                   |                                            | 3.3V<br>Typ <sup>(1)</sup> | 5V<br>Typ <sup>(2)</sup> | Unit |

|--------------------------------|-----------------------------------|--------------------------------------------------------------|--------------------------------------------|----------------------------|--------------------------|------|

|                                |                                   | LP_PARAM bits: ALL OFF <sup>(5)</sup>                        |                                            | 12                         | 15                       |      |

|                                | Supply current                    | LP_PARAM bits : MVREG ON, OSC4M OFF, F<br>OFF <sup>(6)</sup> | LASH                                       | 130                        | 135                      |      |

|                                | in STOP<br>mode <sup>(4)</sup>    | LP_PARAM bits: MVREG ON, OSC4M ON , FI                       | _ASH                                       | 1950                       | 1930                     | μA   |

|                                |                                   | LP_PARAM bits: MVREG ON, OSC4M OFF, FL                       | 630                                        | 635                        |                          |      |

|                                |                                   | LP_PARAM bits: MVREG ON, OSC4M ON, FL                        | 2435                                       | 2425                       |                          |      |

| I <sub>DD</sub> <sup>(3)</sup> | ا <sub>חח</sub> <sup>(3)</sup>    | LPPARAM bits: ALL OFF, with V <sub>18</sub> =1.8 V           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 5<br><1                    | 5<br><1                  |      |

|                                | Supply current                    | LP_PARAM bits: OSC4M ON, FLASH OFF                           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 410<br>1475                | 410<br>1435              | μA   |

|                                | in STOP<br>mode <sup>(7)</sup>    | LP_PARAM bits: OSC4M OFF, FLASH ON                           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 550<br><1                  | 550<br>1                 | μΛ   |

|                                |                                   | LP_PARAM bits: OSC4M ON, FLASH ON                            | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 910<br>1475                | 910<br>1445              |      |

|                                | Supply current                    | RTC OFF                                                      |                                            | 11                         | 14                       |      |

|                                | in STANDBY<br>mode <sup>(4)</sup> | RTC ON clocked by OSC32K                                     |                                            | 14                         | 18                       | μA   |

1. Typical data are based on  $T_A=25^{\circ}$ C,  $V_{DD IO}=3.3$  V and  $V_{18}=1.8$  V unless otherwise indicated in the table.

2. Typical data are based on  $T_A=25^{\circ}C$ ,  $V_{DD\_IO}=5.0$  V and  $V_{18}=1.8$  V unless otherwise indicated in the table.

3. The conditions for these consumption measurements are described at the beginning of Section 6.3.4 on page 36.

4. Single supply scheme see *Figure 12*.

5. In this mode, the whole digital circuitry is powered internally by the LPVREG at approximately 1.4 V, which significantly reduces the leakage currents.

6. In this mode, the whole digital circuitry is powered internally by the MVREG at 1.8 V.

7. Dual supply scheme see Figure 13.

## Supply and clock manager power consumption

| Table 18. | Supply and clock manager power consumption |

|-----------|--------------------------------------------|

|-----------|--------------------------------------------|

| Symbol                  | Parameter                                                                                     | Conditions <sup>(1)</sup>                                                                                   | 3.3V<br>Typ | 5V<br>Typ | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------|-----------|------|

| I <sub>DD(OSC4M)</sub>  | Supply current of resonator oscillator<br>in STOP or WFI mode (LP_PARAM<br>bit: OSC4M ON)     | External components specified in:<br>4/8 MHz crystal / ceramic resonator<br>oscillator (XT1/XT2) on page 46 | 1815        | 1795      |      |

| I <sub>DD(FLASH)</sub>  | FLASH static current consumption in<br>STOP or WFI mode (LP_PARAM bit<br>FLASH ON)            |                                                                                                             | 515         | 515       |      |

| I <sub>DD(MVREG)</sub>  | Main Voltage Regulator static current<br>consumption in STOP mode<br>(LP_PARAM bit: MVREG ON) |                                                                                                             | 130         | 135       | μA   |

|                         |                                                                                               | STOP mode includes leakage where $\rm V_{18}$ is internally set to 1.4 V                                    | 12          | 15        |      |

| I <sub>DD(LPVREG)</sub> | Low Power Voltage Regulator + RSM<br>current static current consumption                       | STANDBY mode where $V_{18BKP}$ and $V_{18}$ are internally set to 1.4 V and 0 V respectively                | 11          | 14        |      |

1. Measurements performed in 3.3V single supply mode see *Figure 12*

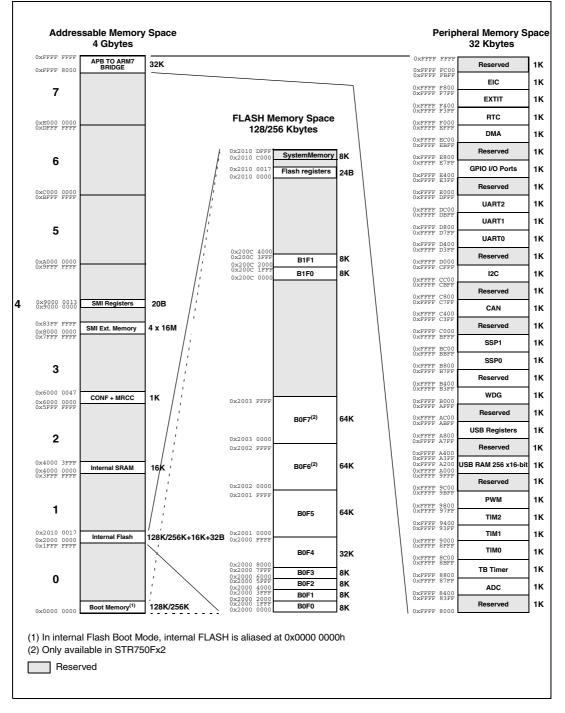

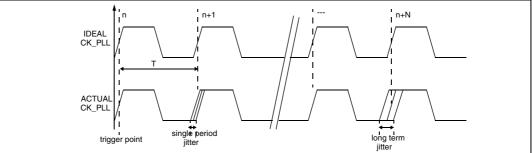

difference between N+1 consecutive clock rising edges and  $T_{min}$  is the minimum time difference between N+1 consecutive clock rising edges.

N should be kept sufficiently large to have a long term jitter (ex: thousands).

For N=1, this becomes the single period jitter.

See Figure 23

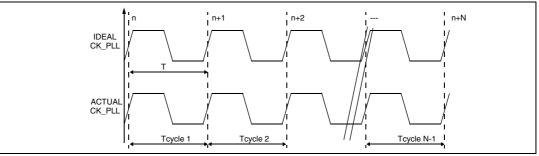

• Cycle-to-cycle jitter (N period jitter)

This corresponds to the time variation between adjacent cycles over a random sample of adjacent clock cycles pairs. Jitter(cycle-to-cycle) = Max(Tcycle n- Tcycle n-1) for n=1 to N.

See Figure 24

#### Figure 24. Cycle-to-cycle jitter

#### **PLL characteristics**

Subject to general operating conditions for  $V_{DD \ IO}$ , and  $T_A$ .

| Table 24. PLL characteristics | Table 24. | PLL | characteristics |

|-------------------------------|-----------|-----|-----------------|

|-------------------------------|-----------|-----|-----------------|

| Symbol                                  | Parameter Test Condit                              |                                                                     |     | Value |                    |      |

|-----------------------------------------|----------------------------------------------------|---------------------------------------------------------------------|-----|-------|--------------------|------|

| Symbol                                  | Falameter                                          | Test Conditions                                                     | Min | Тур   | Max <sup>(1)</sup> | Unit |

| f                                       | PLL input clock                                    |                                                                     |     | 4.0   |                    | MHz  |

| f <sub>PLL_IN</sub>                     | PLL input clock duty cycle                         |                                                                     | 40  |       | 60                 | %    |

| f <sub>PLL_OUT</sub>                    | PLL multiplier output clock                        | f <sub>PLL_IN</sub> x 24                                            |     |       | 165                | MHz  |

| f <sub>VCO</sub>                        | VCO frequency range                                | When PLL<br>operates (locked)                                       | 336 |       | 960                | MHz  |

| t <sub>LOCK</sub>                       | PLL lock time                                      |                                                                     |     |       | 300                | μs   |

| ∆t <sub>JITTER1</sub> <sup>(2)(3)</sup> | Single period jitter (+/-3 $\Sigma$ peak to peak)  | $f_{PLL_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable  |     |       | +/-250             | ps   |

| ∆t <sub>JITTER2</sub> <sup>(2)(3)</sup> | Long term jitter (+/- $3\Sigma$ peak to peak)      | $f_{PLL_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable  |     |       | +/-2.5             | ns   |

| ∆t <sub>JITTER3</sub> <sup>(2)(3)</sup> | Cycle to cycle jitter (+/- $3\Sigma$ peak to peak) | $f_{PLL\_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable |     |       | +/-500             | ps   |

1. Data based on product characterisation, not tested in production.

2. Refer to jitter terminology in : PLL characteristics on page 47 for details on how jitter is specified.

The jitter specification holds true only up to 50mV (peak-to-peak) noise on V<sub>DDA\_PLL</sub> and V<sub>18</sub> supplies. Jitter will increase if the noise is more than 50mV. In addition, it assumes that the input clock has no jitter.

4. The PLL parameters (MX1, MX0, PRESC1, PRESC2) must respect the constraints described in: PLL characteristics on page 47.

#### Internal RC oscillators (FREEOSC & LPOSC)

Subject to general operating conditions for  $V_{DD}$  IO, and  $T_A$ .

#### Table 25. Internal RC oscillators (FREEOSC & LPOSC)

| Symbol                  | Parameter                    | Conditions | Min | Тур | Max | Unit |

|-------------------------|------------------------------|------------|-----|-----|-----|------|

| f <sub>CK_FREEOSC</sub> | FREEOSC Oscillator Frequency |            | 3   | 5   | 8   | MHz  |

| f <sub>CK_LPOSC</sub>   | LPOSC Oscillator Frequency   |            | 150 | 300 | 500 | kHz  |

#### Electro magnetic interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Symbo            | Parameter  | Conditions                                                                                                                 | Monitored                                       | Max vs. [f <sub>O</sub> | sc4m/f <sub>HCLK</sub> ] | Unit |           |

|------------------|------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------|--------------------------|------|-----------|

| I                |            |                                                                                                                            | Frequency Band                                  | 4/32MHz                 | 4/60MHz                  | Onit |           |

|                  |            | evel $V_{DD_{-}IO}=3.3 \text{ V or } 5 \text{ V}, T_{A}=+25^{\circ} \text{ C}, LQFP64 \text{ package conforming to SAE J}$ | 0.1 MHz to 30 MHz                               | 22                      | 26                       |      |           |

|                  |            |                                                                                                                            | V <sub>DD_IO</sub> =3.3 V or 5 V,<br>T₄=+25° C. | 30 MHz to 130 MHz       | 31                       | 26   | $dB\mu V$ |

| S <sub>EMI</sub> | Peak level |                                                                                                                            | 130 MHz to 1 GHz                                | 19                      | 23                       |      |           |

|                  |            |                                                                                                                            | SAE EMI Level                                   | >4                      | >4                       | -    |           |

Table 29. EMI characteristics

#### Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electro-Static discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

| Table 30. Absolute maximum ra | ratings |

|-------------------------------|---------|

|-------------------------------|---------|

| Symbol                | Ratings                                                   | Conditions             | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-----------------------------------------------------------|------------------------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model)    |                        | 2000                            |      |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage<br>(Machine Model)       | T <sub>A</sub> =+25° C | 200                             | V    |

| V <sub>ESD(CDM)</sub> | Electro-static discharge voltage<br>(Charge Device Model) |                        | 750                             |      |

1. Data based on product characterisation, not tested in production.

| Symbol                               | Parameter                               | Conditions                                            | Min                 | Тур               | Мах             | Unit                |

|--------------------------------------|-----------------------------------------|-------------------------------------------------------|---------------------|-------------------|-----------------|---------------------|

|                                      |                                         | $f_{CK_TIM(MAX)} = f_{CK_SYS}$                        | 1                   |                   |                 | $t_{\rm CK_TIM}$    |

| t <sub>res(PWM)</sub> PWM resolution | PWM resolution time                     | f <sub>CK_TIM</sub> = f <sub>CK_SYS</sub> =<br>60 MHz | 16.6 <sup>(1)</sup> |                   |                 | ns                  |

| Res <sub>PWM</sub>                   | PWM resolution                          |                                                       |                     |                   | 16              | bit                 |

| V <sub>OS</sub> <sup>(1)</sup>       | PWM/DAC output step                     | V <sub>DD_IO</sub> =3.3 V, Res=16-bits                |                     | 50 <sup>(1)</sup> |                 | μV                  |

| voltage                              | voltage                                 | V <sub>DD_IO</sub> =5.0 V, Res=16-bits                |                     | 76 <sup>(1)</sup> |                 | μV                  |

|                                      | Timer clock period                      |                                                       | 1                   |                   | 65536           | t <sub>CK_TIM</sub> |

| <sup>t</sup> COUNTER                 | COUNTER when internal clock is selected | f <sub>CK_TIM</sub> =60 MHz                           | 0.0166              |                   | 1087            | μs                  |

| t                                    | Maximum Possible                        |                                                       |                     |                   | 65536x<br>65536 | t <sub>CK_TIM</sub> |

| <sup>t</sup> MAX_COUNT               | Count                                   | $f_{CK_{TIM}} = f_{CK_{SYS}} =$<br>60 MHz             |                     |                   | 71.58           | s                   |

Table 37. PWM Timer (PWM)

1. Take into account the frequency limitation due to the I/O speed capability when outputting the PWM to an I/O pin, as described in : *Output speed on page 57*.

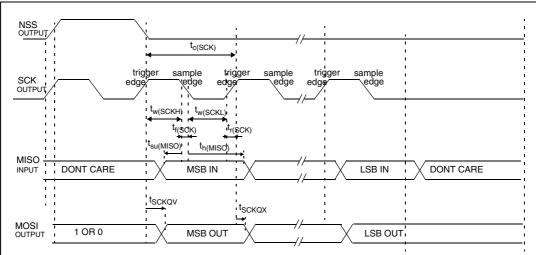

Figure 31. TI configuration - master mode, single transfer

| t <sub>c(S0</sub>           | СК)                              | t <sub>c(SCK)</sub>           |                               |          |

|-----------------------------|----------------------------------|-------------------------------|-------------------------------|----------|

| NSS OUTPUT                  | //                               |                               |                               | 1<br>1   |

| SCK OUTPUT                  | e trigger, sample trigger sample | trigger sample trigger sample | trigger sample trigger sample |          |

|                             | XXX                              |                               |                               | OUT      |

| MISO INPUT DONT CARE MSB IN | X/X                              |                               | N X // LSB                    |          |

|                             | FRAME 1                          | <b>.</b>                      | FRAME 2                       | <b>→</b> |

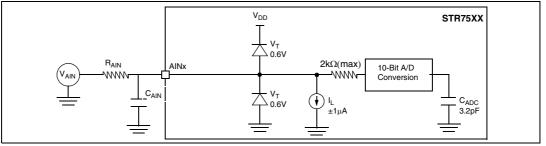

#### ADC accuracy vs. negative injection current

Injecting negative current on specific pins listed in *Table 46* (generally adjacent to the analog input pin being converted) should be avoided as this significantly reduces the accuracy of the conversion being performed. It is recommended to add a Schottky diode (pin to ground) to pins which may potentially inject negative current.

| Table 46. List of adjacent pi | ns |

|-------------------------------|----|

|-------------------------------|----|

| Analog input | Related adjacent pins |

|--------------|-----------------------|

| a            | None                  |

| AIN1/P0.03   | None                  |

| AIN2/P0.12   | P0.11                 |

| AIN3/P0.17   | P0.18 and P0.16       |

| AIN4/P0.19   | P0.24                 |

| AIN5/P0.22   | None                  |

| AIN6/P0.23   | P2.04                 |

| AIN7/P0.27   | P1.11 and P0.26       |

| AIN8/P0.29   | P0.30 and P0.28       |

| AIN9/P1.04   | None                  |

| AIN10/P1.06  | P1.05                 |

| AIN11/P1.08  | P1.04 and P1.13       |

| AIN12/P1.11  | P2.17 and P0.27       |

| AIN13/P1.12  | None                  |

| AIN14/P1.13  | P1.14 and P1.01       |

| AIN15/P1.14  | None                  |

#### Figure 42. Typical application with ADC

#### Analog power supply and reference pins

The  $V_{DDA\_ADC}$  and  $V_{SSA\_ADC}$  pins are the analog power supply of the A/D converter cell.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see : *General PCB design guidelines on page 74*).

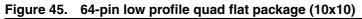

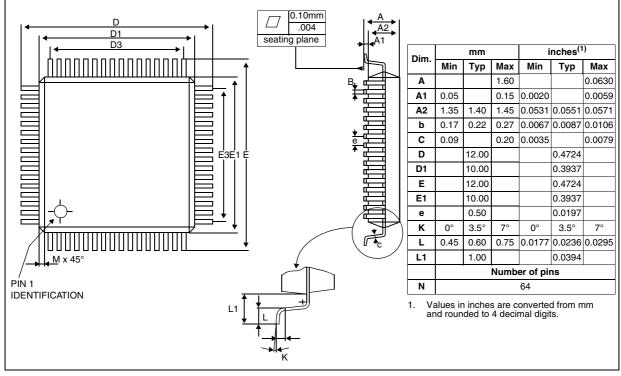

## 7 Package characteristics

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

## 7.1 Package mechanical data

#### Figure 46. 100-pin low profile flat package (14x14)

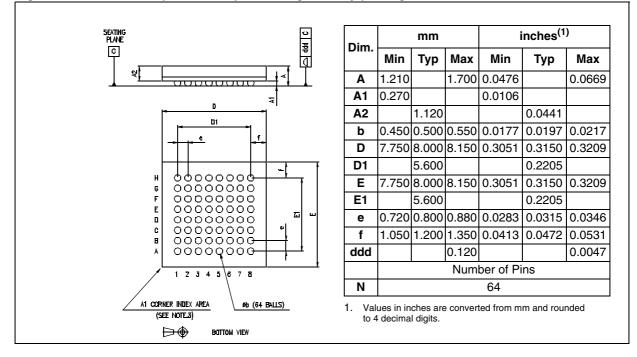

#### Figure 47. 64-ball low profile fine pitch ball grid array package

### 7.2 Thermal characteristics

The maximum chip junction temperature (T<sub>Jmax</sub>) must never exceed the values given in *Table 10: General operating conditions on page 34*.

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

Where:

- T<sub>Amax</sub> is the maximum Ambient Temperature in °C,

- $\Theta_{JA}$  is the Package Junction-to-Ambient Thermal Resistance, in ° C/W,

- $P_{Dmax}$  is the sum of  $P_{INTmax}$  and  $P_{I/Omax} (P_{Dmax} = P_{INTmax} + P_{I/Omax})$ ,

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum Power Dissipation on Output Pins. Where:

$\mathsf{P}_{\mathsf{I}/\mathsf{Omax}} = \Sigma (\mathsf{V}_{\mathsf{OL}}^* \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}}^* \mathsf{V}_{\mathsf{OH}})^* \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

Table 48.Thermal characteristics<sup>(1)</sup>

| Symbol        | Parameter                                                                   | Value | Unit |

|---------------|-----------------------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LQFP 100 - 14 x 14 mm / 0.5 mm pitch | 46    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LQFP 64 - 10 x 10 mm / 0.5 mm pitch  | 45    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LFBGA 64 - 8 x 8 x 1.7mm             | 58    | °C/W |

| $\Theta_{JA}$ | Thermal Resistance Junction-Ambient<br>LFBGA 100 - 10 x 10 x 1.7mm          | 41    | °C/W |

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

#### 7.2.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

# 9 Revision history

| Table 50. | Document revision history |

|-----------|---------------------------|

|-----------|---------------------------|

| Date        | Revision | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25-Sep-2006 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 30-Oct-2006 | 2        | Added power consumption data for 5V operation in Section 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 04-Jul-2007 | 3        | Changed datasheet title from STR750F to STR750FXX STR751Fxx<br>STR752Fxx STR755xx.<br>Added <i>Table 1: Device summary on page 1</i><br>Added note 1 to <i>Table 6</i><br>Added STOP mode IDD max. values in <i>Table 14</i><br>Updated XT2 driving current in <i>Table 23</i> .<br>Updated RPD in <i>Table 32</i><br>Updated <i>Table 21: XRTC1 external clock source on page 45</i><br>Updated <i>Table 34: Output speed on page 57</i><br>Added characteristics for <i>SSP synchronous serial peripheral in master</i><br><i>mode (SPI or TI mode) on page 62</i> and <i>SSP synchronous serial</i><br><i>peripheral in slave mode (SPI or TI mode) on page 65</i><br>Added characteristics for <i>SMI - serial memory interface on page 68</i><br>Added <i>Table 42: USB startup time on page 70</i> |

| 23-Oct-2007 | 4        | Updated Section 6.2.3: Thermal characteristics on page 33<br>Updated P <sub>D</sub> , T <sub>J</sub> and T <sub>A</sub> in Section 6.3: Operating conditions on page 34<br>Updated Table 20: XT1 external clock source on page 44<br>Updated Table 21: XRTC1 external clock source on page 45<br>Updated Section 7: Package characteristics on page 76 (inches rounded<br>to 4 decimal digits instead of 3)<br>Updated Ordering information Section 8: Order codes on page 81                                                                                                                                                                                                                                                                                                                            |

| 17-Feb-2009 | 5        | Modified note 3 below <i>Table 8: Current characteristics on page 33</i><br>Added AHB clock frequency for write access to Flash registers in<br><i>Table 10: General operating conditions on page 34</i><br>Modified note 3 below <i>Table 41: SDA and SCL characteristics on</i><br><i>page 69</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |