Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                            |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 60MHz                                                               |

| Connectivity               | I <sup>2</sup> C, SPI, SSI, SSP, UART/USART                         |

| Peripherals                | DMA, PWM, WDT                                                       |

| Number of I/O              | 72                                                                  |

| Program Memory Size        | 256KB (256K x 8)                                                    |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 100-LFBGA                                                           |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str755fv2h6 |

|                            |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Serial memory interface (SMI)

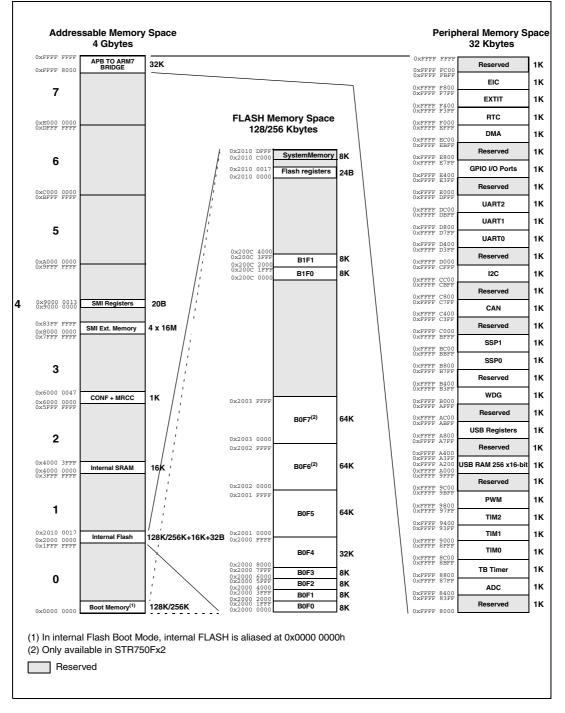

The Serial Memory interface is directly able to access up to 4 serial FLASH devices. It can be used to access data, execute code directly or boot the application from external memory. The memory is addressed as 4 banks of up to 16 Mbytes each.

# **Clocks and start-up**

After RESET or when exiting from Low Power Mode, the CPU is clocked immediately by an internal RC oscillator (FREEOSC) at a frequency centered around 5 MHz, so the application code can start executing without delay. In parallel, the 4/8 MHz Oscillator is enabled and its stabilization time is monitored using a dedicated counter.

An oscillator failure detection is implemented: when the clock disappears on the XT1 pin, the circuit automatically switches to the FREEOSC oscillator and an interrupt is generated.

In Run mode, the AHB and APB clock speeds can be set at a large number of different frequencies thanks to the PLL and various prescalers: up to 60 MHz for AHB and up to 32 MHz for APB when fetching from Flash (64 MHz and 32 MHz when fetching from SRAM).

In SLOW mode, the AHB clock can be significantly decreased to reduce power consumption.

The built-in Clock Controller also provides the 48 MHz USB clock directly without any extra oscillators or PLL. For instance, starting from the 4 MHz crystal source, it is possible to obtain in parallel 60 MHz for the AHB clock, 48 MHz for the USB clock and 30 MHz for the APB peripherals.

### **Boot modes**

At start-up, boot pins are used to select one of five boot options:

- Boot from internal flash

- Boot from external serial Flash memory

- Boot from internal boot loader

- Boot from internal SRAM

Booting from SMI memory allows booting from a serial flash. This way, a specific boot monitor can be implemented. Alternatively, the STR750F can boot from the internal boot loader that implements a boot from UART.

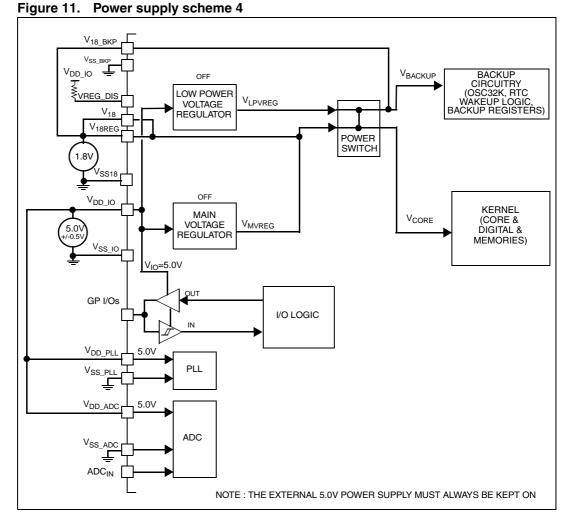

### **Power supply schemes**

You can connect the device in any of the following ways depending on your application.

- Power Scheme 1: Single external 3.3V power source. In this configuration the V<sub>CORE</sub> supply required for the internal logic is generated internally by the main voltage regulator and the V<sub>BACKUP</sub> supply is generated internally by the low power voltage regulator. This scheme has the advantage of requiring only one 3.3V power source.

- Power Scheme 2: Dual external 3.3V and 1.8V power sources. In this configuration, the internal voltage regulators are switched off by forcing the VREG\_DIS pin to high level. V<sub>CORE</sub> is provided externally through the V<sub>18</sub> and V<sub>18REG</sub> power pins and V<sub>BACKUP</sub> through the V<sub>18\_BKP</sub> pin. This scheme is intended to save power consumption for applications which already provide an 1.8V power supply.

- Power Scheme 3: Single external 5.0V power source. In this configuration the V<sub>CORE</sub> supply required for the internal logic is generated internally by the main voltage

|                        | Pin                     | n°                    |                        |                                         |      |                | In       | put   |                   | C          | )utpu     | ıt | y                 |                                                  |                                                  |                                                                     |  |

|------------------------|-------------------------|-----------------------|------------------------|-----------------------------------------|------|----------------|----------|-------|-------------------|------------|-----------|----|-------------------|--------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------|--|

| LQFP100 <sup>(1)</sup> | LFBGA100 <sup>(1)</sup> | LQFP64 <sup>(2)</sup> | LFBGA64 <sup>(2)</sup> | Pin name                                | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD<br>(3) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)             | Alternate function                               |                                                                     |  |

| 7                      | D1                      | 5                     | D1                     | P0.29 / TIM1_TI1<br>/ ADC_IN8           | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.29                                        | TIM1: Input<br>Capture 1                         | ADC: Analog<br>input 8                                              |  |

| 8                      | E1                      | 6                     | D2                     | P0.28 /<br>TIM1_OC1                     | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | Port 0.28                                        | TIM1: Output Cor                                 | npare 1                                                             |  |

| 9                      | E5                      | 7                     | D3                     | TEST                                    | Ι    |                |          |       |                   |            |           |    |                   | Reserved, mu                                     | ist be tied to groun                             | d                                                                   |  |

| 10                     | E4                      | 8                     | D4                     | VSS_IO                                  | S    |                |          |       |                   |            |           |    |                   | Ground Voltag                                    | ge for digital I/Os                              |                                                                     |  |

| 11                     | E2                      |                       |                        | P0.23 /<br>UART1_RTS /<br>ADC_IN6       | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O2         | x         | x  |                   | Port 0.23                                        | UART1: Ready<br>To Send<br>output <sup>(4)</sup> | ADC analog input<br>6                                               |  |

| 12                     | F5                      |                       |                        | P2.04 /<br>TIM2_OC1                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 2.04                                        | TIM2: Output<br>Compare 1 <sup>(4)</sup>         |                                                                     |  |

| 13                     | F1                      |                       |                        | P2.03 /<br>UART1_RTS                    | I/O  | т <sub>т</sub> | x        | x     |                   | 02         | x         | x  |                   | Port 2.03                                        | UART1: Ready<br>To Send<br>output <sup>(4)</sup> |                                                                     |  |

| 14                     | F4                      |                       |                        | P2.02                                   | I/O  | Τ <sub>T</sub> | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.02                                        |                                                  |                                                                     |  |

| 15                     | E3                      |                       |                        | P0.22 /<br>UART1_CTS /<br>ADC_IN5       | I/O  | Τ <sub>Τ</sub> | x        | x     |                   | O2         | x         | x  |                   | Port 0.22                                        | UART1: Clear To<br>Send input                    | ADC: Analog<br>input 5                                              |  |

| 16                     | F2                      | 9                     | E4                     | P0.21 /<br>UART1_TX                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | 02         | х         | х  |                   | Port 0.21                                        | UART1: Transmit<br>(remappable to P              | data output<br>0.15) <sup>(4)</sup>                                 |  |

| 17                     | F3                      | 10                    | E3                     | P0.20 /<br>UART1_RX                     | I/O  | Τ <sub>Τ</sub> | x        | х     |                   | O2         | х         | х  |                   | Port 0.20                                        | UART1: Receive (remappable to P                  | data input<br>0.14) <sup>(4)</sup>                                  |  |

| 18                     | G3                      | 11                    | E2                     | P1.19 / JTMS                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | O2         | х         | х  |                   | JTAG mode<br>selection<br>input <sup>(6)</sup>   | Port 1.19                                        |                                                                     |  |

| 19                     | G2                      | 12                    | E1                     | P1.18 / JTCK                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | JTAG clock<br>input <sup>(6)</sup>               | Port 1.18                                        |                                                                     |  |

| 20                     | H3                      | 13                    | F4                     | P1.17 / JTDO                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | O8         | х         | х  |                   | JTAG data<br>output <sup>(6)</sup>               | Port 1.17                                        |                                                                     |  |

| 21                     | H2                      | 14                    | F3                     | P1.16 / JTDI                            | I/O  | Τ <sub>Τ</sub> | х        | х     |                   | 02         | х         | х  |                   | JTAG data<br>input <sup>(6)</sup>                | Port 1.16                                        |                                                                     |  |

| 22                     | G1                      | 15                    | F2                     | NJTRST                                  | Ι    | TT             |          |       |                   |            |           |    |                   | JTAG reset in                                    | put <sup>(5)</sup>                               |                                                                     |  |

| 23                     | G4                      |                       |                        | P2.01                                   | I/O  | $T_T$          | х        | х     |                   | 02         | Х         | Х  |                   | Port 2.01                                        |                                                  |                                                                     |  |

| 24                     | G5                      |                       |                        | P2.00                                   | I/O  | TT             | X        | х     |                   | O2         | х         | х  |                   | Port 2.00                                        |                                                  |                                                                     |  |

|                        |                         |                       |                        |                                         |      |                |          |       |                   |            |           |    |                   | ITAC                                             | Port 0.13                                        |                                                                     |  |

| 25                     | H1                      | 16                    | F1                     | P0.13 / RTCK /<br>UART0_RTS<br>UART2_TX | I/O  | Τ <sub>Τ</sub> | х        | x     |                   | O8         | х         | х  |                   | JTAG<br>return<br>clock<br>output <sup>(6)</sup> | UART0: Ready<br>To Send<br>output <sup>(4)</sup> | UART2: Transmit<br>Data output<br>(when<br>remapped) <sup>(8)</sup> |  |

# Table 6. STR750F pin description (continued)

# 5 Memory map

| Figure 5. | Memory map |

|-----------|------------|

|-----------|------------|

Power supply scheme 4: Dual external 1.8 V and 5.0 V supply

# 6.1.7 I/O characteristics versus the various power schemes (3.3V or 5.0V)

Unless otherwise mentioned, all the I/O characteristics are valid for both

- V<sub>DD IO</sub>=3.0 V to 3.6 V with bit EN33=1

- V<sub>DD IO</sub>=4.5 V to 5.5 V with bit EN33=0

When  $V_{DD \ IO}$ =3.0 V to 3.6 V, I/Os are not 5V tolerant.

# 6.1.8 Current consumption measurements

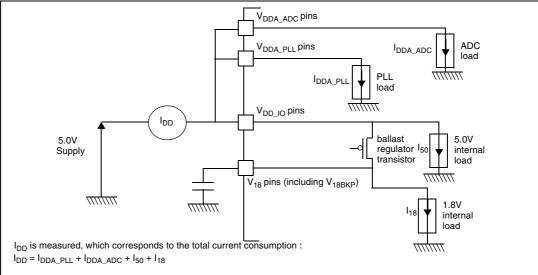

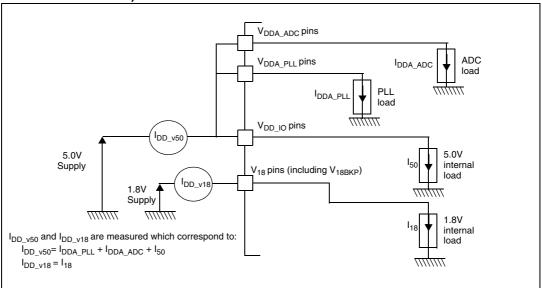

All the current consumption measurements mentioned below refer to Power scheme 1 and 2 as described in *Figure 12* and *Figure 13*

57

Figure 15. Power consumption measurements in power scheme 4 (regulators disabled)

# 6.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 6.2.1 Voltage characteristics

| Symbol                                | Ratings                                                                                                  | Min                                                  | Max                                                  | Unit |

|---------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------|

| $V_{DD_x} - V_{SS_x}^{(1)}$           | Including $V_{DDA\_ADC}$ and $V_{DDA\_PLL}$                                                              | -0.3                                                 | 6.5                                                  | V    |

| V <sub>18</sub> - V <sub>SS18</sub>   | Digital 1.8 V Supply voltage on all V <sub>18</sub><br>power pins (when 1.8 V is provided<br>externally) | -0.3                                                 | 2.0                                                  |      |

| V <sub>IN</sub>                       | Input voltage on any pin <sup>(2)</sup>                                                                  | V <sub>SS</sub> -0.3 to<br>V <sub>DD_IO</sub> +0.3   | V <sub>SS</sub> -0.3 to<br>V <sub>DD_IO</sub> +0.3   |      |

| ا∆V <sub>DDx</sub> I                  | Variations between different 3.3 V or 5.0 V power pins                                                   |                                                      | 50                                                   |      |

| l∆V <sub>18x</sub> l                  | Variations between different 1.8 V power pins <sup>(3)</sup>                                             |                                                      | 25                                                   | mV   |

| IV <sub>SSX</sub> - V <sub>SS</sub> I | Variations between all the different ground pins                                                         |                                                      | 50                                                   |      |

| V <sub>ESD(HBM)</sub>                 | Electro-static discharge voltage (Human<br>Body Model)                                                   | see : Absolute<br>maximum                            | see : Absolute<br>maximum                            |      |

| V <sub>ESD(MM)</sub>                  | Electro-static discharge voltage (Machine Model)                                                         | ratings<br>(electrical<br>sensitivity) on<br>page 52 | ratings<br>(electrical<br>sensitivity) on<br>page 52 |      |

# Table 7. Voltage characteristics

All 3.3 V or 5.0 V power (V<sub>DD\_IO</sub>, V<sub>DDA\_ADC</sub>, V<sub>DDA\_PLL</sub>) and ground (V<sub>SS\_IO</sub>, V<sub>SSA\_ADC</sub>, V<sub>DDA\_ADC</sub>) pins must always be connected to the external 3.3V or 5.0V supply. When powered by 3.3V, I/Os are not 5V tolerant.

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

Only when using external 1.8 V power supply. All the power (V<sub>18</sub>, V<sub>18REG</sub>, V<sub>18BKP</sub>) and ground (V<sub>SS18</sub>, V<sub>SSBKP</sub>) pins must always be connected to the external 1.8 V supply.

# 6.2.2 Current characteristics

### Table 8.Current characteristics

| Symbol                                     | Ratings                                                                 | Maximum<br>value | Unit |  |  |  |

|--------------------------------------------|-------------------------------------------------------------------------|------------------|------|--|--|--|

| I <sub>VDD_IO</sub> <sup>(1)</sup>         | Total current into $V_{DD_{IO}}$ power lines (source) <sup>(2)</sup>    | 150              |      |  |  |  |

| I <sub>VSS_IO</sub> <sup>(1)</sup>         |                                                                         |                  |      |  |  |  |

|                                            | Output current sunk by any I/O and control pin                          | 25               |      |  |  |  |

| IIO                                        | Output current source by any I/Os and control pin                       | - 25             | mA   |  |  |  |

|                                            | Injected current on NRSTIN pin                                          | ± 5              | ША   |  |  |  |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> & (4) | Injected current on XT1 and XT2 pins                                    | ± 5              |      |  |  |  |

|                                            | Injected current on any other pin <sup>(5)</sup>                        | ± 5              |      |  |  |  |

| $\Sigma I_{\rm INJ(PIN)}^{(3)}$            | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ± 25             |      |  |  |  |

1. The user can use GPIOs to source or sink high current (up to 20 mA for O8 type High Sink I/Os). In this case, the user must ensure that these absolute max. values are not exceeded (taking into account the RUN power consumption) and must follow the rules described in *Section 6.3.8: I/O port pin characteristics on page 54*.

- 2. All 3.3 V or 5.0 V power ( $V_{DD\_IO}$ ,  $V_{DDA\_ADC}$ ,  $V_{DDA\_PLL}$ ) and ground ( $V_{SS\_IO}$ ,  $V_{SSA\_ADC}$ ,  $V_{DDA\_ADC}$ ) pins must always be connected to the external 3.3V or 5.0V supply.

- 3. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. Data based on T<sub>A</sub>=25°C.

- 4. Negative injection disturbs the analog performance of the device. See note in *Section 6.3.12: 10-bit ADC characteristics on page 72.*

- 5. When several inputs are submitted to a current injection, the maximum Σl<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with Σl<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

# 6.2.3 Thermal characteristics

### Table 9. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

# 6.3.4 Supply current characteristics

The current consumption is measured as described in *Figure 12 on page 30* and *Figure 13 on page 30*.

Subject to general operating conditions for  $V_{\text{DD}\ \text{IO}}$  , and  $T_{\text{A}}$

# Maximum power consumption

For the measurements in *Table 13* and *Table 14*, the MCU is placed under the following conditions:

- All I/O pins are configured in output push-pull 0

- All peripherals are disabled except if explicitly mentioned.

- Embedded Regulators are used to provide 1.8 V (except if explicitly mentioned).

| Symbol          | Parameter                     | Conditions <sup>(1)</sup>                                                                                                                                                                                                                               |                         | Тур <sup>(2)</sup> | Max <sup>(3)</sup> | Unit |

|-----------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|--------------------|------|

| I <sub>DD</sub> | Supply current in<br>RUN mode | External Clock with PLL<br>multiplication, code running from<br>RAM, all peripherals enabled in the<br>MRCC_PLCKEN register: f <sub>HCLK</sub> =60<br>MHz, f <sub>PCLK</sub> =30 MHz<br>Single supply scheme see <i>Figure 12</i><br>/ <i>Figure 14</i> | 3.3V<br>and 5V<br>range | 80                 | 90                 | mA   |

|                 | Supply current in<br>WFI mode | External Clock, code running from<br>RAM: f <sub>HCLK</sub> =60 MHz, f <sub>PCLK</sub> =30 MHz<br>Single supply scheme see<br><i>Figure 12./ Figure 14</i><br>Parameter setting BURST=1,<br>WFI_FLASHEN=1                                               | 3.3V<br>and 5V<br>range | 62                 | 67                 | mA   |

1. The conditions for these consumption measurements are described at the beginning of Section 6.3.4.

2. Typical data are based on  $T_A=25^\circ C,\,V_{DD\_IO}=3.3V$  or 5.0V and  $V_{18}=1.8V$  unless otherwise specified.

3. Data based on product characterisation, tested in production at  $V_{DD_{-}IO}$  max and  $V_{18}$  max (1.95V in dual supply mode or regulator output value in single supply mode) and  $T_A$  max.

300

250

200

150 100

50

0

-40

25

IStop (uA)

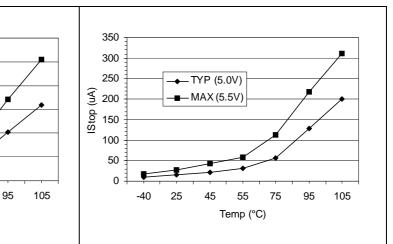

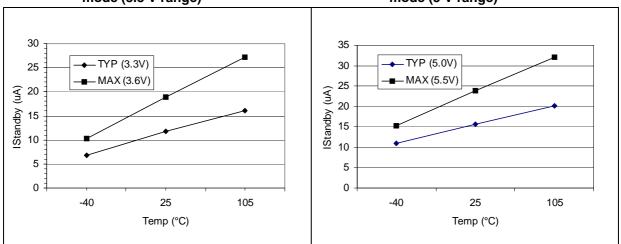

Figure 16. Power consumption in STOP mode Figure 17. Pow in Single supply scheme (3.3 V Sing range)

Figure 18. Power consumption in STANDBY mode (3.3 V range)

-TYP (3.3V)

MAX (3.6V)

45

55

Temp (°C)

75

57

7. Power consumption in STOP mode Single supply scheme (5 V range)

# Table 16.Dual supply supply typical power consumption in Run, WFI, Slow and<br/>Slow-WFI modes

To calculate the power consumption in Dual supply mode, refer to the values given in *Table 15*. and consider that this consumption is split as follows:  $I_{DD}(single supply) \sim I_{DD}(dual supply) = I_{DD} \vee 18 + I_{DD}(VDD_{IO})$

For 3.3V range:  $I_{DD(VDD_IO)} \sim 1$  to 2 mA For 5V range:  $I_{DD(VDD_IO)} \sim 2$  to 3 mA Therefore most of the consumption is sunk on the V<sub>18</sub> power supply This formula does not apply in STOP and STANDBY modes, refer to *Table 17*.

Subject to general operating conditions for  $V_{\text{DD\_IO}}\text{,}$  and  $T_{\text{A}}$

Table 17. Typical power consumption in STOP and STANDBY modes

| Symbol                         | Parameter                                        | Conditions                                                   |                                            | 3.3V<br>Typ <sup>(1)</sup> | 5V<br>Typ <sup>(2)</sup> | Unit |  |

|--------------------------------|--------------------------------------------------|--------------------------------------------------------------|--------------------------------------------|----------------------------|--------------------------|------|--|

|                                |                                                  | LP_PARAM bits: ALL OFF <sup>(5)</sup>                        |                                            | 12                         | 15                       |      |  |

|                                | Supply current                                   | LP_PARAM bits : MVREG ON, OSC4M OFF, F<br>OFF <sup>(6)</sup> | LASH                                       | 130                        | 135                      |      |  |

|                                | in STOP<br>mode <sup>(4)</sup>                   | LP_PARAM bits: MVREG ON, OSC4M ON , FI                       | _ASH                                       | 1950                       | 1930                     | μA   |  |

|                                |                                                  | LP_PARAM bits: MVREG ON, OSC4M OFF, FL                       | _ASH ON <sup>(6)</sup>                     | 630                        | 635                      |      |  |

|                                |                                                  | LP_PARAM bits: MVREG ON, OSC4M ON, FL                        | 2435                                       | 2425                       |                          |      |  |

| I <sub>DD</sub> <sup>(3)</sup> | Supply current<br>in STOP<br>mode <sup>(7)</sup> | LPPARAM bits: ALL OFF, with V <sub>18</sub> =1.8 V           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 5<br><1                    | 5<br><1                  |      |  |

|                                |                                                  | LP_PARAM bits: OSC4M ON, FLASH OFF                           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 410<br>1475                | 410<br>1435              |      |  |

|                                |                                                  | LP_PARAM bits: OSC4M OFF, FLASH ON                           | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 550<br><1                  | 550<br>1                 | μA   |  |

|                                |                                                  | LP_PARAM bits: OSC4M ON, FLASH ON                            | I <sub>DD_V18</sub><br>I <sub>DD_V33</sub> | 910<br>1475                | 910<br>1445              |      |  |

|                                | Supply current                                   | RTC OFF                                                      |                                            | 11                         | 14                       |      |  |

|                                | in STANDBY<br>mode <sup>(4)</sup>                | RTC ON clocked by OSC32K                                     |                                            |                            | 18                       | μA   |  |

1. Typical data are based on  $T_A=25^{\circ}$ C,  $V_{DD IO}=3.3$  V and  $V_{18}=1.8$  V unless otherwise indicated in the table.

2. Typical data are based on  $T_A=25^{\circ}C$ ,  $V_{DD\_IO}=5.0$  V and  $V_{18}=1.8$  V unless otherwise indicated in the table.

3. The conditions for these consumption measurements are described at the beginning of Section 6.3.4 on page 36.

4. Single supply scheme see Figure 12.

5. In this mode, the whole digital circuitry is powered internally by the LPVREG at approximately 1.4 V, which significantly reduces the leakage currents.

6. In this mode, the whole digital circuitry is powered internally by the MVREG at 1.8 V.

7. Dual supply scheme see Figure 13.

# Supply and clock manager power consumption

| Table 18. | Supply and clock manager power consumption |

|-----------|--------------------------------------------|

|-----------|--------------------------------------------|

| Symbol                  | Parameter                                                                                     | Conditions <sup>(1)</sup>                                                                                   | 3.3V<br>Typ | 5V<br>Typ | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------|-----------|------|

| I <sub>DD(OSC4M)</sub>  | Supply current of resonator oscillator<br>in STOP or WFI mode (LP_PARAM<br>bit: OSC4M ON)     | External components specified in:<br>4/8 MHz crystal / ceramic resonator<br>oscillator (XT1/XT2) on page 46 | 1815        | 1795      |      |

| I <sub>DD(FLASH)</sub>  | FLASH static current consumption in<br>STOP or WFI mode (LP_PARAM bit<br>FLASH ON)            |                                                                                                             | 515         | 515       |      |

| I <sub>DD(MVREG)</sub>  | Main Voltage Regulator static current<br>consumption in STOP mode<br>(LP_PARAM bit: MVREG ON) |                                                                                                             | 130         | 135       | μA   |

|                         | Low Power Voltage Regulator + RSM                                                             | STOP mode includes leakage where $\rm V_{18}$ is internally set to 1.4 V                                    | 12          | 15        |      |

| I <sub>DD(LPVREG)</sub> | current static current consumption                                                            | STANDBY mode where $V_{18BKP}$ and $V_{18}$ are internally set to 1.4 V and 0 V respectively                | 11          | 14        |      |

1. Measurements performed in 3.3V single supply mode see *Figure 12*

# XRTC1 external clock source

Subject to general operating conditions for  $V_{\text{DD}\_\text{IO}}\text{,}$  and  $T_{\text{A}}\text{.}$

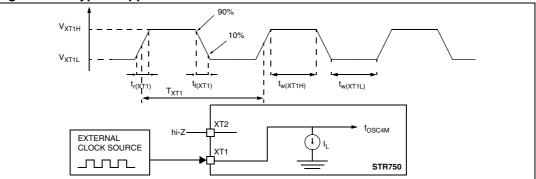

Table 21. XRTC1 external clock source

| Symbol                                           | Parameter                                 | Conditions <sup>(1)</sup>                                | Min                    | Тур    | Max                    | Unit |

|--------------------------------------------------|-------------------------------------------|----------------------------------------------------------|------------------------|--------|------------------------|------|

| f <sub>XRTC1</sub>                               | External clock source<br>frequency        |                                                          |                        | 32.768 | 500                    | kHz  |

| V <sub>XRTC1H</sub>                              | XRTC1 input pin high<br>level voltage     |                                                          | 0.7xV <sub>DD_IO</sub> |        | V <sub>DD_IO</sub>     | V    |

| V <sub>XRTC1L</sub>                              | XRTC1 input pin low<br>level voltage      | see Figure 20                                            | V <sub>SS</sub>        |        | 0.3xV <sub>DD_IO</sub> | v    |

| t <sub>w(XRTC1H)</sub><br>t <sub>w(XRTC1L)</sub> | XRTC1 high or low<br>time <sup>(2)</sup>  |                                                          | 900                    |        |                        | ns   |

| t <sub>r(XRTC1)</sub><br>t <sub>f(XRTC1)</sub>   | XRTC1 rise or fall time <sup>(2)</sup>    |                                                          |                        |        | 50                     | 115  |

| ΙL                                               | XRTCx Input leakage<br>current            | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD_I</sub><br>o |                        |        | ±1                     | μA   |

| C <sub>IN(RTC1)</sub>                            | XRTC1 input<br>capacitance <sup>(2)</sup> |                                                          |                        | 5      |                        | pF   |

| DuCy <sub>(RTC1)</sub>                           | Duty cycle                                |                                                          | 30                     |        | 70                     | %    |

1. Data based on typical application software.

2. Data based on design simulation and/or technology characteristics, not tested in production.

### Figure 20. Typical application with an external clock source

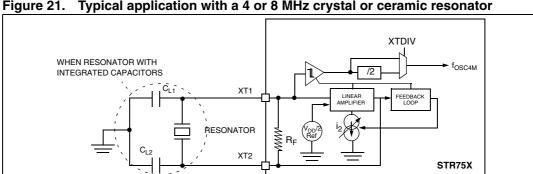

# 4/8 MHz crystal / ceramic resonator oscillator (XT1/XT2)

The STR750 system clock or the input of the PLL can be supplied by a OSC4M which is a 4 MHz clock generated from a 4 MHz or 8 MHz crystal or ceramic resonator. If using an 8 MHz oscillator, software set the XTDIV bit to enable a divider by 2 and generate a 4 MHz OSC4M clock. All the information given in this paragraph are based on product characterisation with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                                            | Parameter                                                                                                                   | Conditions                                                                                                                                     | Min | Тур | Max | Unit |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC4M</sub>                                | Oscillator frequency                                                                                                        | 4 MHz Crystal/Resonator Oscillator<br>connected on XT1/XT2 XTDIV=0<br>or<br>8 MHz Crystal/Resonator Oscillator<br>connected on XT1/XT2 XTDIV=1 |     | 4   |     | MHz  |

| R <sub>F</sub>                                    | Feedback resistor                                                                                                           |                                                                                                                                                | 200 | 240 | 270 | kΩ   |

| C <sub>L1</sub> <sup>(2)</sup><br>C <sub>L2</sub> | Recommended load<br>capacitance versus equivalent<br>serial resistance of the crystal or<br>ceramic resonator $(R_S)^{(3)}$ | R <sub>S</sub> =200Ω                                                                                                                           |     |     | 60  | pF   |

| i <sub>2</sub>                                    | XT2 driving current                                                                                                         | V <sub>DD_IO</sub> =3.3 V or 5.0 V                                                                                                             |     | 425 |     | μA   |

| t <sub>SU(OSC4M)</sub> <sup>(4)</sup>             | Startup time at V <sub>DD_IO</sub> power-up                                                                                 |                                                                                                                                                |     | 1   |     | ms   |

| Table 22. | 4/8 MHz cry | stal / ceramic resonator | oscillator | (XT1/XT2) <sup>(1)</sup> | ) |

|-----------|-------------|--------------------------|------------|--------------------------|---|

|-----------|-------------|--------------------------|------------|--------------------------|---|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5-pF to 25-pF range (typ.) designed for high-frequency applications and selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the 2. same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included when sizing  $C_{L1}$  and  $C_{L2}$  (10 pF can be used as a rough estimate of the combined pin and board capacitance).

- 3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- $t_{SU(OSC4M)}$  is the typical start-up time measured from the moment  $V_{DD \ IO}$  is powered (with a quick  $V_{DD \ IO}$  ramp-up from 0 to 3.3V (<50µs) to a stabilized 4MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal/ceramic resonator manufacturer.

57

Figure 21. Typical application with a 4 or 8 MHz crystal or ceramic resonator

# **PLL characteristics**

Subject to general operating conditions for  $V_{DD \ IO}$ , and  $T_A$ .

| Table 24. PLL characteristics | Table 24. | PLL | characteristics |

|-------------------------------|-----------|-----|-----------------|

|-------------------------------|-----------|-----|-----------------|

| Symbol                                  | Parameter                                          | Test Conditions                                                     |     | Unit |                    |      |

|-----------------------------------------|----------------------------------------------------|---------------------------------------------------------------------|-----|------|--------------------|------|

| Symbol                                  | Falameter                                          | Test Conditions                                                     | Min | Тур  | Max <sup>(1)</sup> | Unit |

| f                                       | PLL input clock                                    |                                                                     |     | 4.0  |                    | MHz  |

| f <sub>PLL_IN</sub>                     | PLL input clock duty cycle                         |                                                                     | 40  |      | 60                 | %    |

| f <sub>PLL_OUT</sub>                    | PLL multiplier output clock                        | f <sub>PLL_IN</sub> x 24                                            |     |      | 165                | MHz  |

| f <sub>VCO</sub>                        | VCO frequency range                                | When PLL<br>operates (locked)                                       | 336 |      | 960                | MHz  |

| t <sub>LOCK</sub>                       | PLL lock time                                      |                                                                     |     |      | 300                | μs   |

| ∆t <sub>JITTER1</sub> <sup>(2)(3)</sup> | Single period jitter (+/-3 $\Sigma$ peak to peak)  | $f_{PLL_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable  |     |      | +/-250             | ps   |

| ∆t <sub>JITTER2</sub> <sup>(2)(3)</sup> | Long term jitter (+/- $3\Sigma$ peak to peak)      | $f_{PLL_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable  |     |      | +/-2.5             | ns   |

| ∆t <sub>JITTER3</sub> <sup>(2)(3)</sup> | Cycle to cycle jitter (+/- $3\Sigma$ peak to peak) | $f_{PLL\_IN} = 4 \text{ MHz}^{(4)}$<br>V <sub>DD_IO</sub> is stable |     |      | +/-500             | ps   |

1. Data based on product characterisation, not tested in production.

2. Refer to jitter terminology in : PLL characteristics on page 47 for details on how jitter is specified.

The jitter specification holds true only up to 50mV (peak-to-peak) noise on V<sub>DDA\_PLL</sub> and V<sub>18</sub> supplies. Jitter will increase if the noise is more than 50mV. In addition, it assumes that the input clock has no jitter.

4. The PLL parameters (MX1, MX0, PRESC1, PRESC2) must respect the constraints described in: PLL characteristics on page 47.

# Internal RC oscillators (FREEOSC & LPOSC)

Subject to general operating conditions for  $V_{DD}$  IO, and  $T_A$ .

# Table 25. Internal RC oscillators (FREEOSC & LPOSC)

| Symbol                  | Parameter                    | Conditions | Min | Тур | Max | Unit |

|-------------------------|------------------------------|------------|-----|-----|-----|------|

| f <sub>CK_FREEOSC</sub> | FREEOSC Oscillator Frequency |            | 3   | 5   | 8   | MHz  |

| f <sub>CK_LPOSC</sub>   | LPOSC Oscillator Frequency   |            | 150 | 300 | 500 | kHz  |

# 6.3.6 Memory characteristics

# **Flash memory**

Subject to general operating conditions for  $V_{DD\_IO}$  and  $V_{18},\,T_A$  = -40 to 105  $^\circ C$  unless otherwise specified.

| Symbol           | Demonster               | Test Condition-                                    | Va            | Unit                                       |      |

|------------------|-------------------------|----------------------------------------------------|---------------|--------------------------------------------|------|

|                  | Parameter               | Test Conditions                                    | Тур           | Max <sup>(1)</sup>                         | Unit |

| t <sub>PW</sub>  | Word Program            |                                                    | 35            |                                            | μs   |

| t <sub>PDW</sub> | Double Word Program     |                                                    | 60            |                                            | μS   |

| t <sub>PB0</sub> | Bank 0 Program (256K)   | Single Word programming of a checker-board pattern | 2             | 4.9 <sup>(2)</sup>                         | S    |

| t <sub>PB1</sub> | Bank 1 Program (16K)    | Single Word programming of a checker-board pattern | 125           | 224 <sup>(2)</sup>                         | ms   |

| t <sub>ES</sub>  | Sector Erase (64K)      | Not preprogrammed (all 1)<br>Preprogrammed (all 0) | 1.54<br>1.176 | 2.94 <sup>(2)</sup><br>2.38 <sup>(2)</sup> | S    |

| t <sub>ES</sub>  | Sector Erase (8K)       | Not preprogrammed (all 1)<br>Preprogrammed (all 0) | 392<br>343    | 560 <sup>(2)</sup><br>532 <sup>(2)</sup>   | ms   |

| t <sub>ES</sub>  | Bank 0 Erase (256K)     | Not preprogrammed (all 1)<br>Preprogrammed (all 0) | 8.0<br>6.6    | 13.7<br>11.2                               | s    |

| t <sub>ES</sub>  | Bank 1 Erase (16K)      | Not preprogrammed (all 1)<br>Preprogrammed (all 0) | 0.9<br>0.8    | 1.5<br>1.3                                 | S    |

| t <sub>RPD</sub> | Recovery when disabled  |                                                    |               | 20                                         | μs   |

| t <sub>PSL</sub> | Program Suspend Latency |                                                    |               | 10                                         | μS   |

| t <sub>ESL</sub> | Erase Suspend Latency   |                                                    |               | 300                                        | μs   |

Table 26.

Flash memory characteristics

1. Data based on characterisation not tested in production

2. 10K program/erase cycles.

Table 27.

Flash memory endurance and data retention

| Symbol              | Parameter                  | Conditions                                             |                    | Unit |     |         |

|---------------------|----------------------------|--------------------------------------------------------|--------------------|------|-----|---------|

|                     |                            |                                                        | Min <sup>(1)</sup> | Тур  | Max | Unit    |

| N <sub>END_B0</sub> | Endurance (Bank 0 sectors) |                                                        | 10                 |      |     | kcycles |

| N <sub>END_B1</sub> | Endurance (Bank 1 sectors) |                                                        | 100                |      |     | kcycles |

| Y <sub>RET</sub>    | Data Retention             | T <sub>A</sub> =85° C                                  | 20                 |      |     | Years   |

| t <sub>ESR</sub>    | Erase Suspend Rate         | Min time from Erase<br>Resume to next Erase<br>Suspend | 20                 |      |     | ms      |

1. Data based on characterisation not tested in production.

# 6.3.8 I/O port pin characteristics

# **General characteristics**

Subject to general operating conditions for  $V_{DD_{-}IO}$  and  $T_A$  unless otherwise specified.

### Table 32.General characteristics

| I/O static characteristics              |                                                            |                                     |                           |     |     |      |                      |  |

|-----------------------------------------|------------------------------------------------------------|-------------------------------------|---------------------------|-----|-----|------|----------------------|--|

| Symbol                                  | Parameter                                                  | Con                                 | ditions                   | Min | Тур | Мах  | Unit                 |  |

| V <sub>IL</sub>                         | Input low level voltage                                    |                                     |                           |     |     | 0.8  | v                    |  |

| V <sub>IH</sub>                         | Input high level voltage                                   | TTL ports                           |                           | 2   |     |      | v                    |  |

| V <sub>hys</sub>                        | Schmitt trigger voltage<br>hysteresis <sup>(1)</sup>       |                                     |                           |     | 400 |      | mV                   |  |

| I <sub>INJ(PIN)</sub>                   | Injected Current on any I/O pin                            |                                     |                           |     |     | ± 4  |                      |  |

| ΣI <sub>INJ(PIN</sub><br>(2)            | Total injected current (sum of all I/O and control pins)   |                                     |                           |     |     | ± 25 | mA                   |  |

| I <sub>lkg</sub>                        | Input leakage current on robust pins                       | See Section 6.3.12 on page 72       |                           |     |     |      |                      |  |

| , i i i i i i i i i i i i i i i i i i i | Input leakage current <sup>(3)</sup>                       | $V_{SS} \leq V_{IN} \leq V_{DI}$    |                           |     | ±1  |      |                      |  |

| ۱ <sub>S</sub>                          | Static current consumption <sup>(4)</sup>                  | Floating inpu                       | t mode                    |     | 200 |      | μA                   |  |

| Б                                       | Weak pull-up equivalent                                    | V V                                 | V <sub>DD_IO</sub> =3.3 V | 50  | 95  | 200  | kΩ                   |  |

| R <sub>PU</sub>                         | resistor <sup>(5)</sup>                                    | V <sub>IN</sub> =V <sub>SS</sub>    | V <sub>DD_IO</sub> =5 V   | 20  | 58  | 150  | kΩ                   |  |

| Б                                       | Weak pull-down equivalent                                  | V V                                 | V <sub>DD_IO</sub> =3.3 V | 25  | 80  | 180  | kΩ                   |  |

| R <sub>PD</sub>                         | resistor <sup>(5)</sup>                                    | V <sub>IN</sub> =V <sub>DD_IO</sub> | V <sub>DD_IO</sub> =5 V   | 20  | 50  | 120  | kΩ                   |  |

| C <sub>IO</sub>                         | I/O pin capacitance                                        |                                     |                           |     | 5   |      | pF                   |  |

| t <sub>w(IT)in</sub>                    | External interrupt/wake-up lines pulse time <sup>(6)</sup> |                                     |                           | 2   |     |      | Т <sub>АР</sub><br>в |  |

1. Hysteresis voltage between Schmitt trigger switching levels.

When the current limitation is not possible, the V<sub>IN</sub> absolute maximum rating must be respected, otherwise refer to I<sub>INJ(PIN)</sub> specification. A positive injection is induced by V<sub>IN</sub>>V<sub>DD\_IO</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. Refer to *Section 6.2 on page 32* for more details.

3. Leakage could be higher than max. if negative current is injected on adjacent pins.

Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor (see *Figure 25*). Data based on design simulation and/or technology characteristics, not tested in production.

5. The R<sub>PU</sub> pull-up and R<sub>PD</sub> pull-down equivalent resistor are based on a resistive transistor.

6. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

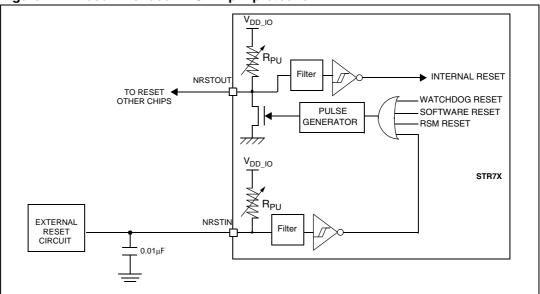

### **NRSTIN and NRSTOUT pins**

NRSTIN Pin Input Driver is TTL/LVTTL as for all GP I/Os. A permanent pull-up is present which is the same as R<sub>PU</sub> (see : *General characteristics on page 54*)

NRSTOUT Pin Output Driver is equivalent to the O2 type driver except that it works only as an open-drain (the P-MOS is de-activated). A permanent pull-up is present which is the same as  $R_{PLI}$  (see : *General characteristics on page 54*)

Subject to general operating conditions for V<sub>DD IO</sub> and T<sub>A</sub> unless otherwise specified.

| Symbol                   | Parameter                                                                    | Co                                                                                  | nditions                  | Min | <b>Typ</b> <sup>1)</sup> | Max | Unit |

|--------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------|-----|--------------------------|-----|------|

| V <sub>IL(NRSTIN)</sub>  | NRSTIN Input low level voltage <sup>(1)</sup>                                |                                                                                     |                           |     |                          | 0.8 | V    |

| V <sub>IH(NRSTIN)</sub>  | NRSTIN Input high level voltage <sup>(1)</sup>                               |                                                                                     |                           | 2   |                          |     | v    |

| V <sub>hys(NRSTIN)</sub> | NRSTIN Schmitt trigger voltage hysteresis <sup>(2)</sup>                     |                                                                                     |                           |     | 400                      |     | mV   |

| V <sub>OL(NRSTIN)</sub>  | NRSTOUT Output low level voltage <sup>(3)</sup>                              | I <sub>IO</sub> =+2 mA                                                              |                           |     |                          | 0.4 | ۷    |

| P                        | NRSTIN Weak pull-up                                                          | V                                                                                   | V <sub>DD_IO</sub> =3.3 V | 25  | 50                       | 100 | kΩ   |

| R <sub>PU(NRSTIN)</sub>  | equivalent resistor <sup>(4)</sup>                                           | V <sub>IN</sub> =V <sub>SS</sub>                                                    | V <sub>DD_IO</sub> =5 V   | 20  | 31                       | 100 | kΩ   |

| t <sub>w(RSTL)out</sub>  | Generated reset pulse<br>duration (visible at NRSTOUT<br>pin) <sup>(5)</sup> | Internal reset source                                                               |                           | 15  | 20                       |     | μs   |

|                          | External react pulse hold time                                               | At V <sub>DD_IO</sub>                                                               | power-up <sup>(5)</sup>   | 20  |                          |     | μS   |

| t <sub>h(RSTL)in</sub>   | External reset pulse hold time at NRSTIN pin <sup>(6)</sup>                  | When V <sub>DD_IO</sub> is established <sup>(5)</sup>                               |                           | 1   |                          |     | μs   |

| t <sub>g(RSTL)in</sub>   | maximum negative spike<br>duration filtered at NRSTIN<br>pin <sup>(7)</sup>  | The time between two<br>spikes must be higher<br>than 1/2 of the spike<br>duration. |                           |     | 150                      |     | ns   |

# Table 35. NRSTIN and NRSTOUT pins

1. Data based on product characterisation, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels.

- 3. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 6.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

- 4. The R<sub>PU</sub> pull-up equivalent resistor are based on a resistive transistor

- 5. To guarantee the reset of the device, a minimum pulse of 15 µs has to be applied to the internal reset. At V<sub>DD\_IO</sub> power-up, the built-in reset stretcher may not generate the 15 µs pulse duration while once V<sub>DD\_IO</sub> is established, an external reset pulse will be internally stretched up to 15 µs thanks to the reset pulse stretcher.

- 6. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

- 7. In fact the filter is made to ignore all incoming pulses with short duration:

all negative spikes with a duration less than 150 ns are filtered

all trains of negative spikes with a ratio of 1/2 are filtered. This means that all spikes with a maximum duration of 150 ns with minimum interval between spikes of 75 ns are filtered.

Data guaranteed by design, not tested in production.

Figure 27. Recommended NRSTIN pin protection

1. The user must ensure that the level on the NRSTIN pin can go below the V<sub>IL(NRSTIN)</sub> max. level specified in NRSTIN and NRSTOUT pins on page 58. Otherwise the reset will not be taken into account internally.

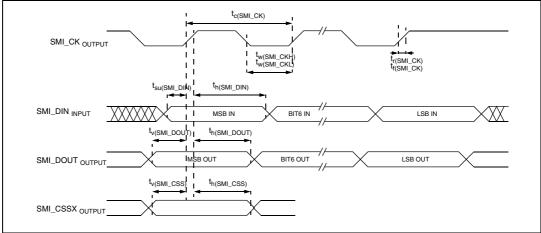

# SMI - serial memory interface

Subject to general operating conditions with  $C_L\approx 30$  pF.

| Table 40. | SMI characteristics <sup>(1)</sup> | ) |

|-----------|------------------------------------|---|

|-----------|------------------------------------|---|

| Symbol                   | Parameter              | Min | Max                  | Unit   |

|--------------------------|------------------------|-----|----------------------|--------|

| 4                        | SMI clock frequency    |     | 32 <sup>(2)(3)</sup> | MHz    |

| f <sub>SMI_CK</sub>      |                        |     | 48 <sup>(4)</sup>    | INILIZ |

| t <sub>r(SMI_CK)</sub>   | SMI clock rise time    |     | 10                   | nc     |

| t <sub>f(SMI_CK)</sub>   | SMI clock fall time    |     | 8                    | ns     |

| t <sub>v(SMI_DOUT)</sub> | Data output valid time |     | 10                   |        |

| t <sub>h(SMI_DOUT)</sub> | Data output hold time  |     | 0                    |        |

| t <sub>v(SMI_CSSx)</sub> | CSS output valid time  |     | 10                   |        |

| t <sub>h(SMI_CSSx)</sub> | CSS output hold time   |     | 0                    |        |

| t <sub>su(SMI_DIN)</sub> | Data input setup time  | 0   |                      |        |

| t <sub>h(SMI_DIN)</sub>  | Data input hold time   | 5   |                      |        |

1. Data based on characterisation results, not tested in production.

2. Max. frequency =  $f_{PCLK}/2 = 64/2 = 32$  MHz.

3. Valid for all temperature ranges: -40 to 105  $^{\circ}\text{C},$  with 30 pF load capacitance.

4. Valid up to 60 °C, with 10 pF load capacitance.

### Figure 39. SMI timing diagram

# I<sup>2</sup>C - Inter IC control interface

Subject to general operating conditions for  $V_{DD_{-}IO}$ ,  $f_{PCLK}$ , and  $T_A$  unless otherwise specified.

The  $I^2C$  interface meets the requirements of the Standard  $I^2C$  communication protocol described in the following table with the restriction mentioned below:

**Restriction:** The I/O pins which SDA and SCL are mapped to are not "True" Open-Drain: when configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD\_IO}$  is disabled, but it is still present. Also, there is a protection diode between the I/O pin and  $V_{DD\_IO}$  is disabled, but it is still present. Also, there is a protection diode between the I/O pin and  $V_{DD\_IO}$ . Consequently, when using this I<sup>2</sup>C in a multi-master network, it is

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com