Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                |

| Core Processor             | CIP-51 8051                                                             |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 50MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 21                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2.25K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                             |

| Data Converters            | A/D 13x10/12b SAR; D/A 2x12b                                            |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 24-SSOP (0.154", 3.90mm Width)                                          |

| Supplier Device Package    | 24-QSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8bb31f16g-a-qsop24 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

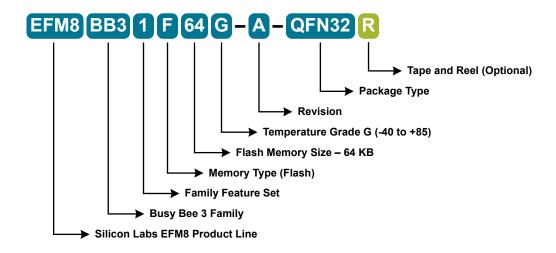

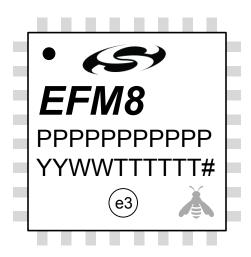

### 2. Ordering Information

Figure 2.1. EFM8BB3 Part Numbering

All EFM8BB3 family members have the following features:

- · CIP-51 Core running up to 49 MHz

- Three Internal Oscillators (49 MHz, 24.5 MHz and 80 kHz)

- SMBus

- I2C Slave

- SPI

- · 2 UARTs

- 6-Channel Programmable Counter Array (PWM, Clock Generation, Capture/Compare)

- · Six 16-bit Timers

- · Four Configurable Logic Units

- 12-bit Analog-to-Digital Converter with integrated multiplexer, voltage reference, temperature sensor, channel sequencer, and directto-XRAM data transfer

- Two Voltage Digital-to-Analog Converters (DACs)

- · Two Analog Comparators

- · 16-bit CRC Unit

- · AEC-Q100 qualified (pending)

In addition to these features, each part number in the EFM8BB3 family has a set of features that vary across the product line. The product selection guide shows the features available on each family member.

**Table 2.1. Product Selection Guide**

| Ordering Part Number | Flash Memory (kB) | RAM (Bytes) | Digital Port I/Os (Total) | Number of DACs | ADC0 Channels | Comparator 0 Inputs | Comparator 1 Inputs | Pb-free (RoHS Compliant) | Temperature Range | Package |

|----------------------|-------------------|-------------|---------------------------|----------------|---------------|---------------------|---------------------|--------------------------|-------------------|---------|

| EFM8BB31F64G-A-QFN32 | 64                | 4352        | 29                        | 4              | 20            | 10                  | 9                   | Yes                      | -40 to +85 °C     | QFN32   |

| EFM8BB31F64G-A-QFP32 | 64                | 4352        | 28                        | 4              | 20            | 10                  | 9                   | Yes                      | -40 to +85 °C     | QFP32   |

| EFM8BB31F64G-A-QFN24 | 64                | 4352        | 20                        | 4              | 12            | 6                   | 6                   | Yes                      | -40 to +85 °C     | QFN24   |

#### Universal Asynchronous Receiver/Transmitter (UART1)

UART1 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates. A received data FIFO allows UART1 to receive multiple bytes before data is lost and an overflow occurs.

UART1 provides the following features:

- Asynchronous transmissions and receptions

- Dedicated baud rate generator supports baud rates up to SYSCLK/2 (transmit) or SYSCLK/8 (receive)

- 5, 6, 7, 8, or 9 bit data

- · Automatic start and stop generation

- · Automatic parity generation and checking

- · Single-byte buffer on transmit and receive

- · Auto-baud detection

- · LIN break and sync field detection

- · CTS / RTS hardware flow control

#### Serial Peripheral Interface (SPI0)

The serial peripheral interface (SPI) module provides access to a flexible, full-duplex synchronous serial bus. The SPI can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select the SPI in slave mode, or to disable master mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a firmware-controlled chip-select output in master mode, or disabled to reduce the number of pins required. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

- Supports 3- or 4-wire master or slave modes

- · Supports external clock frequencies up to 12 Mbps in master or slave mode

- · Support for all clock phase and polarity modes

- 8-bit programmable clock rate (master)

- Programmable receive timeout (slave)

- · Two byte FIFO on transmit and receive

- Can operate in suspend or snooze modes and wake the CPU on reception of a byte

- Support for multiple masters on the same data lines

### System Management Bus / I2C (SMB0)

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus.

The SMBus module includes the following features:

- · Standard (up to 100 kbps) and Fast (400 kbps) transfer speeds

- · Support for master, slave, and multi-master modes

- · Hardware synchronization and arbitration for multi-master mode

- · Clock low extending (clock stretching) to interface with faster masters

- Hardware support for 7-bit slave and general call address recognition

- · Firmware support for 10-bit slave address decoding

- · Ability to inhibit all slave states

- · Programmable data setup/hold times

- Transmit and receive buffers to help increase throughput in faster applications

#### 3.7 Analog

#### 12/10-Bit Analog-to-Digital Converter (ADC0)

The ADC is a successive-approximation-register (SAR) ADC with 12- and 10-bit modes, integrated track-and hold and a programmable window detector. The ADC is fully configurable under software control via several registers. The ADC may be configured to measure different signals using the analog multiplexer. The voltage reference for the ADC is selectable between internal and external reference sources.

- · Up to 20 external inputs

- Single-ended 12-bit and 10-bit modes

- Supports an output update rate of up to 400 ksps in 12-bit mode

- Channel sequencer logic with direct-to-XDATA output transfers

- · Operation in a low power mode at lower conversion speeds

- Asynchronous hardware conversion trigger, selectable between software, external I/O and internal timer and configurable logic sources

- · Output data window comparator allows automatic range checking

- · Support for output data accumulation

- Conversion complete and window compare interrupts supported

- Flexible output data formatting

- Includes a fully-internal fast-settling 1.65 V reference and an on-chip precision 2.4 / 1.2 V reference, with support for using the supply as the reference, an external reference and signal ground

- · Integrated temperature sensor

### 12-Bit Digital-to-Analog Converters (DAC0, DAC1, DAC2, DAC3)

The DAC modules are 12-bit Digital-to-Analog Converters with the capability to synchronize multiple outputs together. The DACs are fully configurable under software control. The voltage reference for the DACs is selectable between internal and external reference sources.

- · Voltage output with 12-bit performance

- Supports an update rate of 200 ksps

- · Hardware conversion trigger, selectable between software, external I/O and internal timer and configurable logic sources

- · Outputs may be configured to persist through reset and maintain output state to avoid system disruption

- · Multiple DAC outputs can be synchronized together

- DAC pairs (DAC0 and 1 or DAC2 and 3) support complementary output waveform generation

- Outputs may be switched between two levels according to state of configurable logic / PWM input trigger

- · Flexible input data formatting

- Supports references from internal supply, on-chip precision reference, or external VREF pin

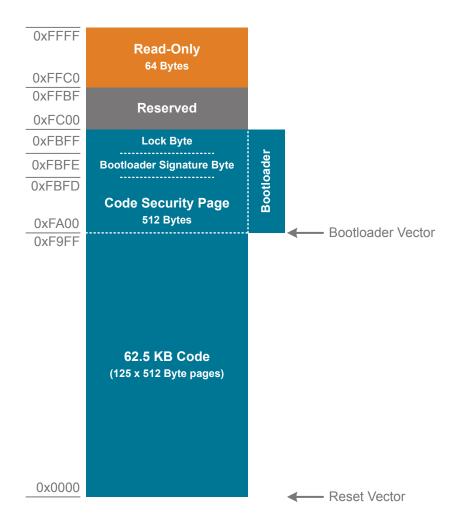

#### 3.10 Bootloader

All devices come pre-programmed with a UART0 bootloader. This bootloader resides in the code security page, which is the last page of code flash; it can be erased if it is not needed.

The byte before the Lock Byte is the Bootloader Signature Byte. Setting this byte to a value of 0xA5 indicates the presence of the bootloader in the system. Any other value in this location indicates that the bootloader is not present in flash.

When a bootloader is present, the device will jump to the bootloader vector after any reset, allowing the bootloader to run. The bootloader then determines if the device should stay in bootload mode or jump to the reset vector located at 0x0000. When the bootloader is not present, the device will jump to the reset vector of 0x0000 after any reset.

Figure 3.2. Flash Memory Map with Bootloader — 62.5 KB Devices

| Parameter                        | Symbol            | Test Condition                        | Min         | Тур   | Max | Unit   |

|----------------------------------|-------------------|---------------------------------------|-------------|-------|-----|--------|

| Offset Temperature Coefficient   | TC <sub>OFF</sub> |                                       | _           | TBD   | _   | LSB/°C |

| Slope Error                      | E <sub>M</sub>    | 12 Bit Mode                           | _           | TBD   | TBD | %      |

|                                  |                   | 10 Bit Mode                           | _           | TBD   | _   | %      |

| Dynamic Performance 10 kHz Sine  | Wave Input        | 1 dB below full scale, Max throughput | , using AGN | D pin |     |        |

| Signal-to-Noise                  | SNR               | 12 Bit Mode                           | _           | TBD   | _   | dB     |

|                                  |                   | 10 Bit Mode                           | _           | TBD   | _   | dB     |

| Signal-to-Noise Plus Distortion  | SNDR              | 12 Bit Mode                           | TBD         | TBD   | _   | dB     |

|                                  |                   | 10 Bit Mode                           | _           | TBD   | _   | dB     |

| Total Harmonic Distortion (Up to | THD               | 12 Bit Mode                           | _           | TBD   | _   | dB     |

| 5th Harmonic)                    |                   | 10 Bit Mode                           | _           | TBD   | _   | dB     |

| Spurious-Free Dynamic Range      | SFDR              | 12 Bit Mode                           | _           | TBD   | _   | dB     |

|                                  |                   | 10 Bit Mode                           | _           | TBD   | _   | dB     |

### Note:

1. Conversion Time does not include Tracking Time. Total Conversion Time is:

Total Conversion Time = [RPT × (ADTK + NUMBITS + 1) × T(SARCLK)] + (T(ADCCLK) × 4)

where RPT is the number of conversions represented by the ADRPT field and ADCCLK is the clock selected for the ADC.

2. Absolute input pin voltage is limited by the  $V_{\mbox{\scriptsize IO}}$  supply.

## 4.1.15 Port I/O

Table 4.15. Port I/O

| Parameter                                  | Symbol          | Test Condition                                              | Min                   | Тур | Max                   | Unit |

|--------------------------------------------|-----------------|-------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| Output High Voltage (High Drive)           | V <sub>OH</sub> | $I_{OH}$ = -7 mA, $V_{IO} \ge 3.0 \text{ V}$                | V <sub>IO</sub> - 0.7 | _   | _                     | V    |

|                                            |                 | $I_{OH}$ = -3.3 mA, 2.2 V $\leq$ V <sub>IO</sub> $<$ 3.0 V  | V <sub>IO</sub> x 0.8 | _   | _                     | V    |

|                                            |                 | $I_{OH}$ = -1.8 mA, 1.71 V $\leq$ V <sub>IO</sub> $<$ 2.2 V |                       |     |                       |      |

| Output Low Voltage (High Drive)            | V <sub>OL</sub> | I <sub>OL</sub> = 13.5 mA, V <sub>IO</sub> ≥ 3.0 V          | _                     | _   | 0.6                   | V    |

|                                            |                 | $I_{OL}$ = 7 mA, 2.2 V $\leq$ V <sub>IO</sub> $<$ 3.0 V     | _                     | _   | V <sub>IO</sub> x 0.2 | V    |

|                                            |                 | $I_{OL}$ = 3.6 mA, 1.71 V $\leq$ V <sub>IO</sub> $<$ 2.2 V  |                       |     |                       |      |

| Output High Voltage (Low Drive)            | V <sub>OH</sub> | $I_{OH}$ = -4.75 mA, $V_{IO} \ge 3.0 \text{ V}$             | V <sub>IO</sub> - 0.7 | _   | _                     | V    |

|                                            |                 | $I_{OH}$ = -2.25 mA, 2.2 V $\leq$ V <sub>IO</sub> $<$ 3.0 V | V <sub>IO</sub> x 0.8 | _   | _                     | V    |

|                                            |                 | $I_{OH}$ = -1.2 mA, 1.71 V $\leq$ V <sub>IO</sub> $<$ 2.2 V |                       |     |                       |      |

| Output Low Voltage (Low Drive)             | V <sub>OL</sub> | $I_{OL}$ = 6.5 mA, $V_{IO} \ge 3.0 \text{ V}$               | _                     | _   | 0.6                   | V    |

|                                            |                 | $I_{OL}$ = 3.5 mA, 2.2 V ≤ $V_{IO}$ < 3.0 V                 | _                     | _   | V <sub>IO</sub> x 0.2 | V    |

|                                            |                 | $I_{OL}$ = 1.8 mA, 1.71 V $\leq$ V <sub>IO</sub> $<$ 2.2 V  |                       |     |                       |      |

| Input High Voltage                         | V <sub>IH</sub> |                                                             | 0.7 x                 | _   | _                     | V    |

|                                            |                 |                                                             | V <sub>IO</sub>       |     |                       |      |

| Input Low Voltage                          | V <sub>IL</sub> |                                                             | _                     | _   | 0.3 x                 | V    |

|                                            |                 |                                                             |                       |     | V <sub>IO</sub>       |      |

| Pin Capacitance                            | C <sub>IO</sub> |                                                             | _                     | 7   | _                     | pF   |

| Weak Pull-Up Current                       | I <sub>PU</sub> | V <sub>DD</sub> = 3.6                                       | -30                   | -20 | -10                   | μΑ   |

| (V <sub>IN</sub> = 0 V)                    |                 |                                                             |                       |     |                       |      |

| Input Leakage (Pullups off or Analog)      | I <sub>LK</sub> | GND < V <sub>IN</sub> < V <sub>IO</sub>                     | TBD                   | _   | TBD                   | μΑ   |

| Input Leakage Current with V <sub>IN</sub> | I <sub>LK</sub> | V <sub>IO</sub> < V <sub>IN</sub> < V <sub>IO</sub> +2.5 V  | 0                     | 5   | 150                   | μΑ   |

| above V <sub>IO</sub>                      |                 | Any pin except P3.0, P3.1, P3.2, or P3.3                    |                       |     |                       | _    |

#### 4.2 Thermal Conditions

**Table 4.16. Thermal Conditions**

| Parameter          | Symbol        | Test Condition  | Min | Тур | Max | Unit |

|--------------------|---------------|-----------------|-----|-----|-----|------|

| Thermal Resistance | $\theta_{JA}$ | QFN24 Packages  | _   | TBD | _   | °C/W |

|                    |               | QFN32 Packages  | _   | TBD | _   | °C/W |

|                    |               | QFP32 Packages  | _   | 80  | _   | °C/W |

|                    |               | QSOP24 Packages | _   | 65  | _   | °C/W |

#### Note:

### 4.3 Absolute Maximum Ratings

Stresses above those listed in Table 4.17 Absolute Maximum Ratings on page 27 may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

Table 4.17. Absolute Maximum Ratings

| Parameter                                                              | Symbol            | Test Condition          | Min     | Max                  | Unit |

|------------------------------------------------------------------------|-------------------|-------------------------|---------|----------------------|------|

| Ambient Temperature Under Bias                                         | T <sub>BIAS</sub> |                         | -55     | 125                  | °C   |

| Storage Temperature                                                    | T <sub>STG</sub>  |                         | -65     | 150                  | °C   |

| Voltage on VDD                                                         | V <sub>DD</sub>   |                         | GND-0.3 | 4.2                  | V    |

| Voltage on VIO <sup>2</sup>                                            | V <sub>IO</sub>   |                         | GND-0.3 | V <sub>DD</sub> +0.3 | V    |

| Voltage on I/O pins or RSTb, excluding                                 |                   | V <sub>IO</sub> > TBD V | GND-0.3 | TBD                  | V    |

| P2.0-P2.3 (QFN24 and QSOP24) or P3.0-P3.3 (QFN32 and QFP32)            |                   | V <sub>IO</sub> < TBD V | GND-0.3 | TBD                  | V    |

| Voltage on P2.0-P2.3 (QFN24 and QSOP24) or P3.0-P3.3 (QFN32 and QFP32) | V <sub>IN</sub>   |                         | GND-0.3 | V <sub>DD</sub> +0.3 | V    |

| Total Current Sunk into Supply Pin                                     | I <sub>VDD</sub>  |                         | _       | 400                  | mA   |

| Total Current Sourced out of Ground Pin                                | I <sub>GND</sub>  |                         | 400     | _                    | mA   |

| Current Sourced or Sunk by any I/O<br>Pin or RSTb                      | I <sub>IO</sub>   |                         | -100    | 100                  | mA   |

- 1. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2. In certain package configurations, the VIO and VDD supplies are bonded to the same pin.

<sup>1.</sup> Thermal resistance assumes a multi-layer PCB with any exposed pad soldered to a PCB pad.

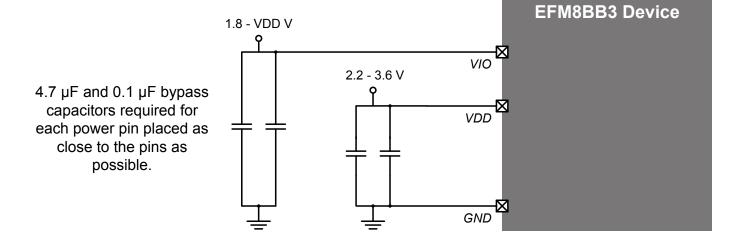

# 5. Typical Connection Diagrams

### 5.1 Power

Figure 5.1 Power Connection Diagram on page 28 shows a typical connection diagram for the power pins of the device.

Figure 5.1. Power Connection Diagram

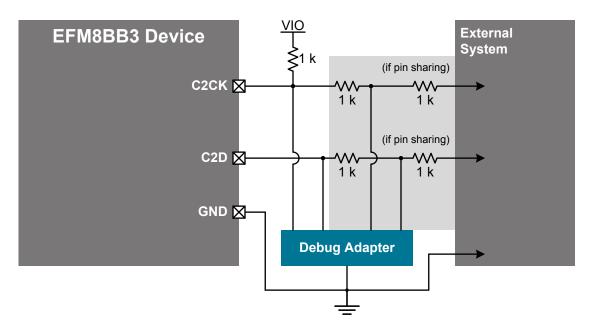

### 5.2 Debug

The diagram below shows a typical connection diagram for the debug connections pins. The pin sharing resistors are only required if the functionality on the C2D (a GPIO pin) and the C2CK (RSTb) is routed to external circuitry. For example, if the RSTb pin is connected to an external switch with debouncing filter or if the GPIO sharing with the C2D pin is connected to an external circuit, the pin sharing resistors and connections to the debug adapter must be placed on the hardware. Otherwise, these components and connections can be omitted.

For more information on debug connections, see the example schematics and information available in AN127: "Pin Sharing Techniques for the C2 Interface." Application notes can be found on the Silicon Labs website (http://www.silabs.com/8bit-appnotes) or in Simplicity Studio.

Figure 5.2. Debug Connection Diagram

#### 5.3 Other Connections

Other components or connections may be required to meet the system-level requirements. Application Note AN203: "8-bit MCU Printed Circuit Board Design Notes" contains detailed information on these connections. Application Notes can be accessed on the Silicon Labs website (www.silabs.com/8bit-appnotes).

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 15            | P2.2     | Multifunction I/O | Yes                 | P2MAT.2                         | ADC0.15          |

|               |          |                   |                     | CLU2OUT                         | CMP1P.4          |

|               |          |                   |                     | CLU1A.15                        | CMP1N.4          |

|               |          |                   |                     | CLU2B.14                        |                  |

|               |          |                   |                     | CLU3A.14                        |                  |

| 16            | P2.1     | Multifunction I/O | Yes                 | P2MAT.1                         | ADC0.14          |

|               |          |                   |                     | I2C0_SCL                        | CMP1P.3          |

|               |          |                   |                     | CLU1B.14                        | CMP1N.3          |

|               |          |                   |                     | CLU2A.15                        |                  |

|               |          |                   |                     | CLU3B.15                        |                  |

| 17            | P2.0     | Multifunction I/O | Yes                 | P2MAT.0                         | CMP1P.2          |

|               |          |                   |                     | I2C0_SDA                        | CMP1N.2          |

|               |          |                   |                     | CLU1A.14                        |                  |

|               |          |                   |                     | CLU2A.14                        |                  |

|               |          |                   |                     | CLU3B.14                        |                  |

| 18            | P1.7     | Multifunction I/O | Yes                 | P1MAT.7                         | ADC0.13          |

|               |          |                   |                     | CLU0B.15                        | CMP0P.9          |

|               |          |                   |                     | CLU1B.13                        | CMP0N.9          |

|               |          |                   |                     | CLU2A.13                        |                  |

| 19            | P1.6     | Multifunction I/O | Yes                 | P1MAT.6                         | ADC0.12          |

|               |          |                   |                     | CLU0A.15                        |                  |

|               |          |                   |                     | CLU1B.12                        |                  |

|               |          |                   |                     | CLU2A.12                        |                  |

| 20            | P1.5     | Multifunction I/O | Yes                 | P1MAT.5                         | ADC0.11          |

|               |          |                   |                     | CLU0B.14                        |                  |

|               |          |                   |                     | CLU1A.13                        |                  |

|               |          |                   |                     | CLU2B.13                        |                  |

|               |          |                   |                     | CLU3B.11                        |                  |

| 21            | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                         | ADC0.10          |

|               |          |                   |                     | CLU0A.14                        |                  |

|               |          |                   |                     | CLU1A.12                        |                  |

|               |          |                   |                     | CLU2B.12                        |                  |

|               |          |                   |                     | CLU3B.10                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 22            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                         | ADC0.9           |

|               |          |                   |                     | CLU0B.13                        |                  |

|               |          |                   |                     | CLU1B.11                        |                  |

|               |          |                   |                     | CLU2B.11                        |                  |

|               |          |                   |                     | CLU3A.13                        |                  |

| 23            | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                         | ADC0.8           |

|               |          |                   |                     | CLU0A.13                        | CMP0P.8          |

|               |          |                   |                     | CLU1A.11                        | CMP0N.8          |

|               |          |                   |                     | CLU2B.10                        |                  |

|               |          |                   |                     | CLU3A.12                        |                  |

|               |          |                   |                     | CLU3B.13                        |                  |

| 24            | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                         | ADC0.7           |

|               |          |                   |                     | CLU0B.12                        | CMP0P.7          |

|               |          |                   |                     | CLU1B.10                        | CMP0N.7          |

|               |          |                   |                     | CLU2A.11                        |                  |

|               |          |                   |                     | CLU3B.12                        |                  |

| 25            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                         | ADC0.6           |

|               |          |                   |                     | CLU10UT                         | CMP0P.6          |

|               |          |                   |                     | CLU0A.12                        | CMP0N.6          |

|               |          |                   |                     | CLU1A.10                        | CMP1P.1          |

|               |          |                   |                     | CLU2A.10                        | CMP1N.1          |

| 26            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                         | ADC0.5           |

|               |          |                   |                     | INT0.7                          | CMP0P.5          |

|               |          |                   |                     | INT1.7                          | CMP0N.5          |

|               |          |                   |                     | CLU0B.11                        | CMP1P.0          |

|               |          |                   |                     | CLU1B.9                         | CMP1N.0          |

|               |          |                   |                     | CLU3A.11                        |                  |

| 27            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                         | ADC0.4           |

|               |          |                   |                     | CNVSTR                          | CMP0P.4          |

|               |          |                   |                     | INT0.6                          | CMP0N.4          |

|               |          |                   |                     | INT1.6                          |                  |

|               |          |                   |                     | CLU0A.11                        |                  |

|               |          |                   |                     | CLU1B.8                         |                  |

|               |          |                   |                     | CLU3A.10                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 18            | P1.7     | Multifunction I/O | Yes                 | P1MAT.7                      | ADC0.13          |

|               |          |                   |                     | CLU0B.15                     | CMP0P.9          |

|               |          |                   |                     | CLU1B.13                     | CMP0N.9          |

|               |          |                   |                     | CLU2A.13                     |                  |

| 19            | P1.6     | Multifunction I/O | Yes                 | P1MAT.6                      | ADC0.12          |

|               |          |                   |                     | CLU0A.15                     |                  |

|               |          |                   |                     | CLU1B.12                     |                  |

|               |          |                   |                     | CLU2A.12                     |                  |

| 20            | P1.5     | Multifunction I/O | Yes                 | P1MAT.5                      | ADC0.11          |

|               |          |                   |                     | CLU0B.14                     |                  |

|               |          |                   |                     | CLU1A.13                     |                  |

|               |          |                   |                     | CLU2B.13                     |                  |

|               |          |                   |                     | CLU3B.11                     |                  |

| 21            | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                      | ADC0.10          |

|               |          |                   |                     | CLU0A.14                     |                  |

|               |          |                   |                     | CLU1A.12                     |                  |

|               |          |                   |                     | CLU2B.12                     |                  |

|               |          |                   |                     | CLU3B.10                     |                  |

| 22            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                      | ADC0.9           |

|               |          |                   |                     | CLU0B.13                     |                  |

|               |          |                   |                     | CLU1B.11                     |                  |

|               |          |                   |                     | CLU2B.11                     |                  |

|               |          |                   |                     | CLU3A.13                     |                  |

| 23            | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                      | ADC0.8           |

|               |          |                   |                     | CLU0A.13                     | CMP0P.8          |

|               |          |                   |                     | CLU1A.11                     | CMP0N.8          |

|               |          |                   |                     | CLU2B.10                     |                  |

|               |          |                   |                     | CLU3A.12                     |                  |

|               |          |                   |                     | CLU3B.13                     |                  |

| 24            | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                      | ADC0.7           |

|               |          |                   |                     | CLU0B.12                     | CMP0P.7          |

|               |          |                   |                     | CLU1B.10                     | CMP0N.7          |

|               |          |                   |                     | CLU2A.11                     |                  |

|               |          |                   |                     | CLU3B.12                     |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 30            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                      | XTAL2            |

|               |          |                   |                     | EXTCLK                       |                  |

|               |          |                   |                     | INT0.3                       |                  |

|               |          |                   |                     | INT1.3                       |                  |

|               |          |                   |                     | CLU0B.9                      |                  |

|               |          |                   |                     | CLU2B.10                     |                  |

|               |          |                   |                     | CLU3A.9                      |                  |

| 31            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                      | XTAL1            |

|               |          |                   |                     | INT0.2                       | ADC0.1           |

|               |          |                   |                     | INT1.2                       | CMP0P.1          |

|               |          |                   |                     | CLU0OUT                      | CMP0N.1          |

|               |          |                   |                     | CLU0A.9                      |                  |

|               |          |                   |                     | CLU2B.8                      |                  |

|               |          |                   |                     | CLU3A.8                      |                  |

| 32            | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                      | ADC0.0           |

|               |          |                   |                     | INT0.1                       | CMP0P.0          |

|               |          |                   |                     | INT1.1                       | CMP0N.0          |

|               |          |                   |                     | CLU0B.8                      | AGND             |

|               |          |                   |                     | CLU2A.9                      |                  |

|               |          |                   |                     | CLU3B.9                      |                  |

| Pin<br>Number | Pin Name  | Description         | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|-----------|---------------------|---------------------|------------------------------|------------------|

| 2             | P0.0      | Multifunction I/O   | Yes                 | P0MAT.0                      | VREF             |

|               |           |                     |                     | INT0.0                       |                  |

|               |           |                     |                     | INT1.0                       |                  |

|               |           |                     |                     | CLU0A.8                      |                  |

|               |           |                     |                     | CLU2A.8                      |                  |

|               |           |                     |                     | CLU3B.8                      |                  |

| 3             | GND       | Ground              |                     |                              |                  |

| 4             | VDD / VIO | Supply Power Input  |                     |                              |                  |

| 5             | RSTb /    | Active-low Reset /  |                     |                              |                  |

|               | C2CK      | C2 Debug Clock      |                     |                              |                  |

| 6             | P3.0 /    | Multifunction I/O / |                     |                              |                  |

|               | C2D       | C2 Debug Data       |                     |                              |                  |

| 7             | P2.3      | Multifunction I/O   | Yes                 | P2MAT.3                      | DAC3             |

|               |           |                     |                     | CLU1B.15                     |                  |

|               |           |                     |                     | CLU2B.15                     |                  |

|               |           |                     |                     | CLU3A.15                     |                  |

| 8             | P2.2      | Multifunction I/O   | Yes                 | P2MAT.2                      | DAC2             |

|               |           |                     |                     | CLU1A.15                     |                  |

|               |           |                     |                     | CLU2B.14                     |                  |

|               |           |                     |                     | CLU3A.14                     |                  |

| 9             | P2.1      | Multifunction I/O   | Yes                 | P2MAT.1                      | DAC1             |

|               |           |                     |                     | CLU1B.14                     |                  |

|               |           |                     |                     | CLU2A.15                     |                  |

|               |           |                     |                     | CLU3B.15                     |                  |

| 10            | P2.0      | Multifunction I/O   | Yes                 | P2MAT.0                      | DAC0             |

|               |           |                     |                     | CLU1A.14                     |                  |

|               |           |                     |                     | CLU2A.14                     |                  |

|               |           |                     |                     | CLU3B.14                     |                  |

| 11            | P1.6      | Multifunction I/O   | Yes                 | P1MAT.6                      | ADC0.11          |

|               |           |                     |                     | CLU3OUT                      | CMP1P.5          |

|               |           |                     |                     | CLU0A.15                     | CMP1N.5          |

|               |           |                     |                     | CLU1B.12                     |                  |

|               |           |                     |                     | CLU2A.12                     |                  |

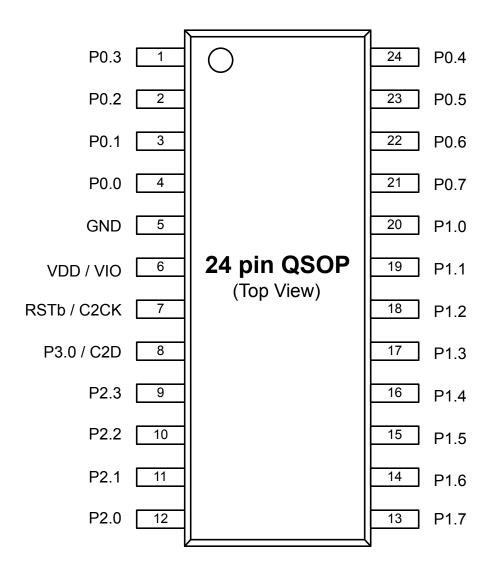

### 6.4 EFM8BB3x-QSOP24 Pin Definitions

Figure 6.4. EFM8BB3x-QSOP24 Pinout

Table 6.4. Pin Definitions for EFM8BB3x-QSOP24

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 1             | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                      | XTAL2            |

|               |          |                   |                     | EXTCLK                       |                  |

|               |          |                   |                     | INT0.3                       |                  |

|               |          |                   |                     | INT1.3                       |                  |

|               |          |                   |                     | CLU0B.9                      |                  |

|               |          |                   |                     | CLU2B.10                     |                  |

|               |          |                   |                     | CLU3A.9                      |                  |

| Pin<br>Number | Pin Name  | Description         | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|-----------|---------------------|---------------------|---------------------------------|------------------|

| 2             | P0.2      | Multifunction I/O   | Yes                 | P0MAT.2                         | XTAL1            |

|               |           |                     |                     | INT0.2                          | ADC0.1           |

|               |           |                     |                     | INT1.2                          | CMP0P.1          |

|               |           |                     |                     | CLU0OUT                         | CMP0N.1          |

|               |           |                     |                     | CLU0A.9                         |                  |

|               |           |                     |                     | CLU2B.8                         |                  |

|               |           |                     |                     | CLU3A.8                         |                  |

| 3             | P0.1      | Multifunction I/O   | Yes                 | P0MAT.1                         | ADC0.0           |

|               |           |                     |                     | INT0.1                          | CMP0P.0          |

|               |           |                     |                     | INT1.1                          | CMP0N.0          |

|               |           |                     |                     | CLU0B.8                         | AGND             |

|               |           |                     |                     | CLU2A.9                         |                  |

|               |           |                     |                     | CLU3B.9                         |                  |

| 4             | P0.0      | Multifunction I/O   | Yes                 | P0MAT.0                         | VREF             |

|               |           |                     |                     | INT0.0                          |                  |

|               |           |                     |                     | INT1.0                          |                  |

|               |           |                     |                     | CLU0A.8                         |                  |

|               |           |                     |                     | CLU2A.8                         |                  |

|               |           |                     |                     | CLU3B.8                         |                  |

| 5             | GND       | Ground              |                     |                                 |                  |

| 6             | VDD / VIO | Supply Power Input  |                     |                                 |                  |

| 7             | RSTb /    | Active-low Reset /  |                     |                                 |                  |

|               | C2CK      | C2 Debug Clock      |                     |                                 |                  |

| 8             | P3.0 /    | Multifunction I/O / |                     |                                 |                  |

|               | C2D       | C2 Debug Data       |                     |                                 |                  |

| 9             | P2.3      | Multifunction I/O   | Yes                 | P2MAT.3                         | DAC3             |

|               |           |                     |                     | CLU1B.15                        |                  |

|               |           |                     |                     | CLU2B.15                        |                  |

|               |           |                     |                     | CLU3A.15                        |                  |

| 10            | P2.2      | Multifunction I/O   | Yes                 | P2MAT.2                         | DAC2             |

|               |           |                     |                     | CLU1A.15                        |                  |

|               |           |                     |                     | CLU2B.14                        |                  |

|               |           |                     |                     | CLU3A.14                        |                  |

Dimension Min Typ Max

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC Solid State Outline MO-220.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

| Dimension | Min  | Тур  | Max |

|-----------|------|------|-----|

| aaa       |      | 0.20 |     |

| bbb       |      | 0.20 |     |

| ccc       | 0.10 |      |     |

| ddd       | 0.20 |      |     |

| theta     | 0°   | 3.5° | 7°  |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS-026.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 8.3 QFP32 Package Marking

Figure 8.3. QFP32 Package Marking

The package marking consists of:

- PPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

- # The device revision (A, B, etc.).

| Dimension | Min | Тур  | Max |

|-----------|-----|------|-----|

| aaa       |     | 0.20 |     |

| bbb       |     | 0.18 |     |

| ccc       |     | 0.10 |     |

| ddd       |     | 0.10 |     |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.