#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                         |

|----------------------------|------------------------------------------------------------------|

| Flouuci Status             |                                                                  |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 33MHz                                                            |

| Connectivity               | EBI/EMI, SIO, UART/USART                                         |

| Peripherals                | Power-Fail Reset, WDT                                            |

| Number of I/O              | 32                                                               |

| Program Memory Size        | 16KB (16K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 1K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                      |

| Data Converters            | -                                                                |

| Oscillator Type            | External                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Through Hole                                                     |

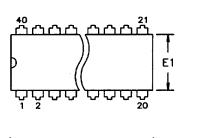

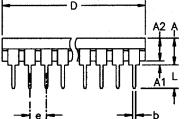

| Package / Case             | 40-DIP (0.600", 15.24mm)                                         |

| Supplier Device Package    | 40-PDIP                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/ds89c420-mnl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Note 1: Specifications to -40°C are guaranteed by design and not production tested.

- Note 2: All voltages are referenced to ground.

- Note 3: Active current is measured with a 25MHz/33MHz clock source driving XTAL1, V<sub>cc</sub> = RST = 5.5V. All other pins disconnected.

- **Note 4:** Idle mode current measured with a 25MHz/33MHz clock source driving XTAL1,  $V_{CC}$  = 5.5V, RST at ground. All other pins disconnected. **Note 5:** Stop mode measured with XTAL and RST grounded,  $V_{CC}$  = 5.5V. All other pins disconnected.

- Note 6: When addressing external memory.

- Note 7: RST = 5.5V. This condition mimics the operation of pins in I/O mode.

- Note 8: During a 0-to-1 transition, a one-shot drives the ports hard for two clock cycles. This measurement reflects a port pin in transition mode.

- Note 9: Ports 1, 2, and 3 source transition current when being pulled down externally. The current reaches its maximum at approximately 2V.

- Note 10: This port is a weak address holding latch in bus mode. Peak current occurs near the input transition point of the holding latch at approximately 2V.

- Note 11: RST = 5.5V. Port 0 floating during reset and when in the logic-high state during I/O mode.

- Note 12: While the specifications for V<sub>PFW</sub> and V<sub>RST</sub> overlap, the design of the hardware makes it such that this is not possible. Within the ranges given, there is a guaranteed separation between these two voltages.

- Note 13: The user should note that this part is tested and guaranteed to operate down to 4.5V (10%) and that V<sub>RST</sub> (min) is specified below that point. This indicates that there is a range of voltages [V<sub>MIN</sub> to V<sub>RST</sub> (min)] where the processor's operation is not guaranteed, but the reset trip point has not been reached. This should not be an issue in most applications, but should be considered when proper operation must be maintained at all times. For these applications, it may be desirable to use a more accurate external reset.

- Note 14: Guaranteed by design.

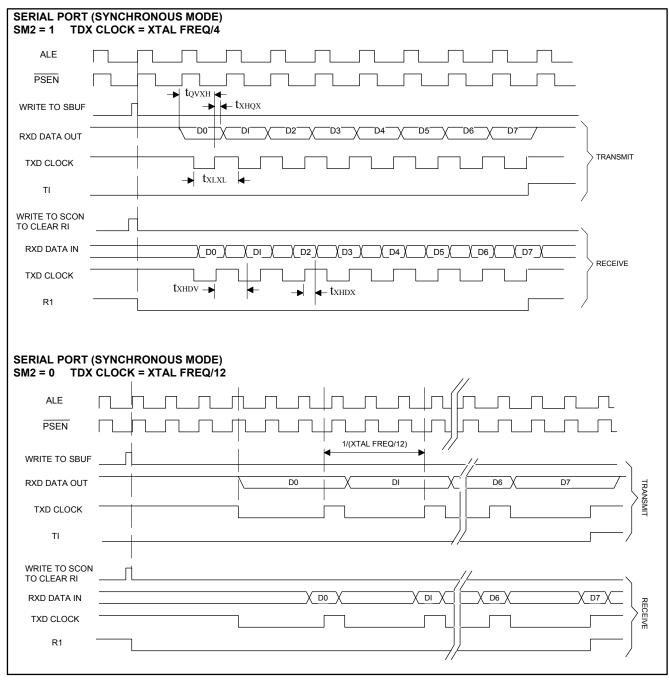

#### Figure 4. Serial Port Timing

# **PIN DESCRIPTION**

| DIP | PIN<br>PLCC   | TQFP              | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|---------------|-------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40  | 12, 44        | 6, 38             | V <sub>cc</sub> | V <sub>CC</sub> - +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20  | 1, 22, 23, 34 | 16, 17, 28,<br>39 | GND             | Logic Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9   | 10            | 4                 | RST             | External Reset. The RST input pin is bidirectional and contains a Schmitt trigger to recognize external active-high reset inputs. The pin also employs an internal pulldown resistor to allow for a combination of wire-ORed external reset sources. An RC is not required for power-up, since the device provides this function internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19  | 21            | 15                | XTAL1           | XTAL1, XTAL2. The crystal oscillator pins XTAL1 and XTAL2 provide support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18  | 20            | 14                | XTAL2           | for fundamental mode parallel resonant, AT cut crystals. XTAL1 also acts as<br>an input if there is an external clock source in place of a crystal. XTAL2<br>serves as the output of the crystal amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 29  | 32            | 26                | PSEN            | Program Store Enable. This signal is commonly connected to optional external program memory as a chip enable. PSEN provides an active-low pulse and is driven high when external program memory is not being accessed. In 1-cycle page mode 1, PSEN remains low for consecutive page hits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 30  | 33            | 27                | ALE/PROG        | Address Latch Enable. Functions as a clock to latch the external address LSB from the multiplexed address/data bus on Port 0. This signal is commonly connected to the latch enable of an external 373 family transparent latch. In default mode, ALE has a pulse width of 1.5 XTAL1 cycles and a period of four XTAL1 cycles. In page mode, the ALE pulse width is altered according to the page mode selection. In traditional 8051 mode, ALE is high when using the EMI reduction mode and during a reset condition. ALE can be enabled by writing ALEON = 1 (PMR.2). Note that ALE operates independently of ALEON during external memory accesses. As an alternate mode, this pin (PROG) is used to execute the parallel program function.                                                                                                                                                                        |

| 39  | 43            | 37                | P0.0 (AD0)      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 38  | 42            | 36                | P0.1 (AD1)      | Port 0 (AD0–7), I/O. Port 0 is an open-drain 8-bit, bidirectional I/O port. As an alternate function, Port 0 can function as the multiplexed address/data bus to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 37  | 41            | 35                | P0.2 (AD2)      | access off-chip memory. During the time when ALE is high, the LSB of a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 36  | 40            | 34                | P0.3 (AD3)      | memory address is presented. When ALE falls to a logic 0, the port transitions to a bidirectional data bus. This bus is used to read external                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 35  | 39            | 33                | P0.4 (AD4)      | program memory and read/write external RAM or peripherals. When used as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 34  | 38            | 32                | P0.5 (AD5)      | a memory bus, the port provides weak pullups for logic 1 outputs. The reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 33  | 37            | 31                | P0.6 (AD6)      | condition of Port 0 is three-state. Pullup resistors are required when using Port 0 as an I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 32  | 36            | 30                | P0.7 (AD7)      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1–8 | 2–9           | 40–44, 1–<br>3    | P1.0-P1.7       | Port 1, I/O. Port 1 functions as both an 8-bit, bidirectional I/O port and an<br>alternate functional interface for timer 2 I/O, new external interrupts, and new<br>serial port 1. The reset condition of port 1 is with all bits at logic 1. In this<br>state, a weak pullup holds the port high. This condition also serves as an<br>input state, since any external circuit that writes to the port overcomes the<br>weak pullup. When software writes a 0 to any port pin, the DS89C420<br>activates a strong pulldown that remains on until either a 1 is written or a<br>reset occurs. Writing a 1 after the port has been at 0 causes a strong<br>transition driver to turn on, followed by a weaker sustaining pullup. Once the<br>momentary strong driver turns off, the port again becomes the output high<br>(and input) state. The alternate functions of Port 1 are outlined below.PORTALTERNATEFUNCTION |

| 1   | 2             | 40                |                 | P1.0 T2 External I/O for Timer/Counter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2   | 3             | 41                |                 | P1.1 T2EX Timer 2 Capture/Reload Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3   | 4             | 42                |                 | P1.2         RXD1         Serial Port 1 Receive           P1.3         TXD1         Serial Port 1 Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4 5 | 5             | 43<br>44          |                 | P1.3         TXD1         Serial Port 1 Transmit           P1.4         INT2         External Interrupt 2 (Positive Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6   | 7             | 1                 |                 | P1.5 INT3 External Interrupt 3 (Negative Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7   | 8             | 2                 |                 | P1.6 INT4 External Interrupt 4 (Positive Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8   | 9             | 3                 |                 | P1.7 INT5 External Interrupt 5 (Negative Edge Detect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# PIN DESCRIPTION (continued)

|       | PIN       |         | NAME       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        | FUNCTION                                                                                   |  |  |  |

|-------|-----------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| DIP   | PLCC      | PDIP    |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |                                                                                            |  |  |  |

| 21    | 24        | 18      | P2.0 (A8)  | Port 2 (A8–15), I/O. Port 2 is an 8-bit, bidirectional I/O port. The reset condition of port 2 is logic high. In this state, a weak pullup holds the port high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |                                                                                            |  |  |  |

| 22    | 25        | 19      | P2.1 (A9)  | This conditio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | n also serves as an i  | nput mode, since any external circuit that                                                 |  |  |  |

| 23    | 26        | 20      | P2.2 (A10) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        | weak pullup. When software writes a 0 to any<br>a strong pulldown that remains on until    |  |  |  |

| 24    | 27        | 21      | P2.3 (A11) | either a 1 is v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | written or a reset occ | curs. Writing a 1 after the port has been at 0                                             |  |  |  |

| 25    | 28        | 22      | P2.4 (A12) | pullup. Once                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | the momentary strong   | to turn on, followed by a weaker sustaining<br>ng driver turns off, the port again becomes |  |  |  |

| 26    | 29        | 23      | P2.5 (A13) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        | ate. As an alternate function, port 2 can<br>al address bus when reading external          |  |  |  |

| 27    | 30        | 24      | P2.6 (A14) | program mer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nory and read/write    | external RAM or peripherals. In page mode                                                  |  |  |  |

| 28    | 31        | 25      | P2.7 (A15) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | vides both the MSB and | and LSB of the external address bus; in page data.                                         |  |  |  |

| 10–17 | 11, 13–19 | 5, 7–13 | P3.0–P3.7  | Port 3, I/O. Port 3 functions as both an 8-bit, bidirectional I/O port and an alternate functional interface for external interrupts, serial port 0, timer 0 and 1 inputs, and $\overline{RD}$ and $\overline{WR}$ strobes. The reset condition of port 3 is with all bits at logic 1. In this state, a weak pullup holds the port high. This condition also serves as an input mode, since any external circuit that writes to the port overcomes the weak pullup. When software writes a 0 to any port pin, the DS89C420 activates a strong pulldown that remains on until either a 1 is written or a reset occurs. Writing a 1 after the port has been at 0 causes a strong transition driver to turn on, followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port 3 are outlined below. |                        |                                                                                            |  |  |  |

|       |           |         |            | PORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ALTERNATE              | FUNCTION                                                                                   |  |  |  |

| 10    | 11        | 5       | P3.0       | P3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RXD0                   | Serial Port 0 Receive                                                                      |  |  |  |

| 11    | 13        | 7       | P3.1       | P3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TXD0                   | Serial Port 0 Transmit                                                                     |  |  |  |

| 12    | 14        | 8       | P3.2       | P3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INTO                   | External Interrupt 0                                                                       |  |  |  |

| 13    | 15        | 9       | P3.3       | P3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ĪNT1                   | External Interrupt 1                                                                       |  |  |  |

| 14    | 16        | 10      | P3.4       | P3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Т0                     | Timer 0 External Input                                                                     |  |  |  |

| 15    | 17        | 11      | P3.5       | P3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | T1                     | Timer 1 External Input                                                                     |  |  |  |

| 16    | 18        | 12      | P3.6       | P3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | WR                     | External Data Memory Write Strobe                                                          |  |  |  |

| 17    | 19        | 13      | P3.7       | P3.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RD                     | External Data Memory Read Strobe                                                           |  |  |  |

| 31    | 35        | 29      | ĒĀ         | External Access. Allows selection of internal or external program memory.<br>Connect to ground to force the DS89C420 to use an external memory-<br>program memory. The internal RAM is still accessible as determined by<br>register settings. Connect to $V_{cc}$ to use internal flash memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                                                                                            |  |  |  |

# Table 1. Special Function Registers

|          | -          | I unction |           |           | -         |                    |           |           | -         |

|----------|------------|-----------|-----------|-----------|-----------|--------------------|-----------|-----------|-----------|

| REGISTER | ADDR       | BIT 7     | BIT 6     | BIT 5     | BIT 4     | BIT 3              | BIT 2     | BIT 1     | BIT 0     |

| P0       | 80h        | P0.7      | P0.6      | P0.5      | P0.4      | P0.3               | P0.2      | P0.1      | P0.0      |

| SP       | 81h        | _         | —         | _         | —         | —                  | —         | —         | —         |

| DPL      | 82h        |           | _         |           | _         | _                  | _         | _         | _         |

| DPH      | 83h        | _         | _         | _         | _         | _                  | _         | _         | _         |

| DPL1     | 84h        | _         | —         | _         | _         | _                  | _         | _         | —         |

| DPH1     | 85h        | _         | —         | _         | _         |                    |           |           | —         |

| DPS      | 86h        | ID1       | ID0       | TSL       | AID       | _                  | _         | _         | SEL       |

| PCON     | 87h        | SMOD_0    | SMOD0     | OFDF      | OFDE      | GF1                | GF0       | STOP      | IDLE      |

| TCON     | 88h        | TF1       | TR1       | TF0       | TR0       | IE1                | IT1       | IE0       | IT0       |

| TMOD     | 89h        | GATE      | C/T       | M1        | MO        | GATE               | C/T       | M1        | MO        |

| TLO      | 8Ah        |           | —         |           |           | _                  |           |           |           |

| TL1      | 8Bh        |           | _         |           | _         | _                  | _         |           | _         |

| THO      | 8Ch        |           | _         |           | _         | _                  | _         | _         | _         |

| TH1      | 8Dh        |           |           |           |           |                    |           |           |           |

| CKCON    | 8Eh        | WD1       | WD0       | T2M       | T1M       | ТОМ                | MD2       | MD1       | MD0       |

| P1       | 90h        | P1.7/INT5 | P1.6/INT4 | P1.5/INT3 | P1.4/INT2 | P1.3/TXD1          | P1.2/RXD1 | P1.1/T2EX | P1.0/T2   |

| EXIF     | 91h        | IE5       | IE4       | IE3       | IE2       | CKRY               | RGMD      | RGSL      | BGS       |

| CKMOD    | 96h        | IL5       |           | T2MH      | T1MH      | TOMH               | KGIVID    | ROSL      | 663       |

|          |            |           |           |           |           |                    |           |           |           |

| SCON0    | 98h        | SM0/FE_0  | SM1_0     | SM2_0     | REN_0     | TB8_0              | RB8_0     | TI_0      | RI_0      |

| SBUF0    | 99h        |           |           |           | —         | —                  | —         | —         | _         |

| ACON     | 9Dh        | PAGEE     | PAGES1    | PAGES0    | —         | —                  | —         | —         | —         |

| P2       | A0h        | P2.7      | P2.6      | P2.5      | P2.4      | P2.3               | P2.2      | P2.1      | P2.0      |

| IE       | A8h        | EA        | ES1       | ET2       | ES0       | ET1                | EX1       | ET0       | EX0       |

| SADDR0   | A9h        |           | —         | _         | —         | —                  | —         | —         | —         |

| SADDR1   | AAh        |           | _         | _         | —         | _                  | _         | —         | —         |

| P3       | B0h        | P3.7/RD   | P3.6/WR   | P3.5/T1   | P3.4/T0   | P3.3/INT1          | P3.2/INT0 | P3.1/TXD0 | P3.0/RXD0 |

| IP1      | B1h        | _         | MPS1      | MPT2      | MPS0      | MPT1               | MPX1      | MPT0      | MPX0      |

| IP0      | B8h        | _         | LPS1      | LPT2      | LPS0      | LPT1               | LPX1      | LPT0      | LPX0      |

| SADEN0   | B9h        |           | —         | _         | _         |                    |           |           | _         |

| SADEN1   | BAh        | _         | —         | _         | —         | —                  | —         | —         | —         |

| SCON1    | C0h        | SM0/FE_1  | SM1_1     | SM2_1     | REN_1     | TB8_1              | RB8_1     | TI_1      | RI_1      |

| SBUF1    | C1h        | _         | —         | -         | —         | —                  | —         | —         | —         |

| ROMSIZE  | C2h        | _         | —         | _         | _         | PRAME              | RMS2      | RMS1      | RMS0      |

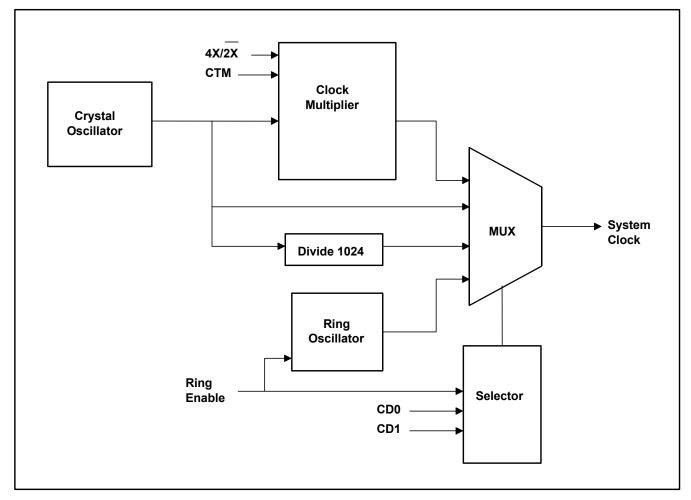

| PMR      | C4h        | CD1       | CD0       | SWB       | CTM       | $4X/\overline{2X}$ | ALEON     | DME1      | DME0      |

| STATUS   | C5h        | PIS2      | PIS1      | PIS0      | —         | SPTA1              | SPRA1     | SPTA0     | SPRA0     |

| TA       | C7h        | _         | —         | _         | —         | —                  | —         | —         | —         |

| T2CON    | C8h        | TF2       | EXF2      | RCLK      | TCLK      | EXEN2              | TR2       | C/T2      | CP/RL2    |

| T2MOD    | C9h        | —         | —         | _         | —         | —                  | —         | T2OE      | DCEN      |

| RCAP2L   | CAh        |           |           | —         | —         |                    |           |           | —         |

| RCAP2H   | CBh        | _         | —         | -         | _         | —                  | —         | —         | _         |

| TL2      | CCh        | _         | _         | _         | _         | _                  | _         | _         | _         |

| TH2      | CDh        |           |           | _         | _         | _                  | _         | _         | _         |

| PSW      | D0h        | CY        | AC        | F0        | RS1       | RS0                | OV        | F1        | Р         |

| FCNTL    | D5h        | FBUSY     | FERR      |           |           | FC3                | FC2       | FC1       | FC0       |

| FDATA    | D6h        | _         | _         | _         | —         |                    |           |           | _         |

| WDCON    | D8h        | SMOD_1    | POR       | EPFI      | PFI       | WDIF               | WTRF      | EWT       | RWT       |

| ACC      | E0h        |           | _         | —         | —         |                    | —         |           | _         |

| EIE      | E8h        | _         | _         | _         | EWDI      | EX5                | EX4       | EX3       | EX2       |

|          |            |           | 1         |           | 1         | 1                  |           |           | İ         |

| B        | F0h        | —         | —         | —         |           | —                  |           |           | —         |

|          | F0h<br>F1h |           | —         |           | <br>MPWDI | MPX5               | MPX4      | MPX3      | MPX2      |

#### Table 2. SFR Reset Value

| REGISTER | ADDR | BIT 7 | BIT 6   | BIT 5   | BIT 4   | BIT 3   | BIT 2   | BIT 1   | BIT ( |

|----------|------|-------|---------|---------|---------|---------|---------|---------|-------|

| P0       | 80h  | 1     | 1       | 1       | 1       | 1       | 1       | 1       | 1     |

| SP       | 81h  | 0     | 0       | 0       | 0       | 0       | 1       | 1       | 1     |

| DPL      | 82h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| DPH      | 83h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| DPL1     | 84h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| DPH1     | 85h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| DPS      | 86h  | 0     | 0       | 0       | 0       | 0       | 1       | 0       | 0     |

| PCON     | 87h  | 0     | 0       | Special | Special | 0       | 0       | 0       | 0     |

| TCON     | 88h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| TMOD     | 89h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| TL0      | 8Ah  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| TL1      | 8Bh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| TH0      | 8Ch  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| TH1      | 8Dh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| CKCON    | 8Eh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 1     |

| P1       | 90h  | 1     | 1       | 1       | 1       | 1       | 1       | 1       | 1     |

| EXIF     | 91h  | 0     | 0       | 0       | 0       | Special | Special | Special | 0     |

| CKMOD    | 96h  | 1     | 1       | 0       | 0       | 0       | 1       | 1       | 1     |

| SCON0    | 98h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| SBUF0    | 99h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| ACON     | 9Dh  | 0     | 0       | 0       | 1       | 1       | 1       | 1       | 1     |

| P2       | A0h  | 1     | 1       | 1       | 1       | 1       | 1       | 1       | 1     |

| IE       | All  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| SADDR0   | A9h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

|          |      | -     | -       | -       | -       | -       | -       | -       |       |

| SADDR1   | AAh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| P3       | B0h  | 1     | 1       | 1       | 1       | 1       | 1       | 1       | 1     |

| IP1      | B1h  | 1     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| IP0      | B8h  | 1     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| SADEN0   | B9h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| SADEN1   | BAh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| SCON1    | C0h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| SBUF1    | C1h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| ROMSIZE  | C2h  | 1     | 1       | 1       | 1       | 0       | 1       | 0       | 1     |

| PMR      | C4h  | 1     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| STATUS   | C5h  | 0     | 0       | 0       | 1       | 0       | 0       | 0       | 0     |

| TA       | C7h  | 1     | 1       | 1       | 1       | 1       | 1       | 1       | 1     |

| T2CON    | C8h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| T2MOD    | C9h  | 1     | 1       | 1       | 1       | 1       | 1       | 0       | 0     |

| RCAP2L   | CAh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| RCAP2H   | CBh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| TL2      | CCh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| TH2      | CDh  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| PSW      | D0h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| FCNTL    | D5h  | 1     | 0       | 1       | 1       | 0       | 0       | 0       | 0     |

| FDATA    | D6h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| WDCON    | D8h  | 0     | Special | 0       | Special | 0       | Special | Special | 0     |

| ACC      | E0h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| EIE      | E8h  | 1     | 1       | 1       | 0       | 0       | 0       | 0       | 0     |

| В        | F0h  | 0     | 0       | 0       | 0       | 0       | 0       | 0       | 0     |

| EIP1     | F1h  | 1     | 1       | 1       | 0       | 0       | 0       | 0       | 0     |

| EIP0     | F8h  | 1     | 1       | 1       | 0       | 0       | 0       | 0       | 0     |

#### MEMORY ORGANIZATION

There are three distinct memory areas in the DS89C420: scratchpad registers, program memory, and data memory. All registers are located on-chip but the program and data memory spaces can either be on-chip, off-chip, or both. There are 16kB of on-chip program memory implemented in flash memory and 1kB of on-chip data memory space that can be configured as program space using the PRAME bit in the ROMSIZE feature. The DS89C420 uses a memory-addressing scheme that separates program memory from data memory. The program and data segments can be overlapped since they are accessed in different ways. If the maximum address of on-chip program or data memory is exceeded, the DS89C420 performs an external memory access using the expanded memory bus. The  $\overrightarrow{PSEN}$  signal goes active-low to serve as a chip enable or output enable when performing a code fetch from external program memory. MOVX instructions activate the  $\overrightarrow{RD}$  or  $\overrightarrow{WR}$  signal for

external MOVX data memory access. The lower 128 bytes of on-chip flash memory store reset and interrupt vectors. The program memory ROMSIZE feature allows software to dynamically configure the maximum address of on-chip program memory. This allows the DS89C420 to act as a bootloader for an external flash or NV SRAM. It also enables the use of the overlapping external program spaces. 256 bytes of on-chip RAM serve as a register area and program stack, which are separated from the data memory.

## **REGISTER SPACE**

Registers are located in the 256 bytes of on-chip RAM, which can be divided into two subareas of 128 bytes each as illustrated in <u>Figure 6</u>. Separate classes of instructions are used to access the registers and the program/data memory. The upper 128 bytes are overlapped with the 128 bytes of SFRs in the memory map. Indirect addressing accesses the upper 128 bytes of scratchpad RAM, and direct addressing accesses the SFR area. Direct or indirect addressing can access the lower 128 bytes.

There are four banks of eight individual working registers in the lower 128 bytes of scratchpad RAM. The working registers are general-purpose RAM locations that can be addressed within the selected bank by any instructions that use R0–R7. The register bank selection is controlled through the program status register in the SFR area. The contents of the working registers can be used for indirectly addressing the upper 128 bytes of scratchpad RAM.

To support the Boolean operations, there are individually addressable bits in both the RAM and SFR areas. In the scratchpad RAM area, registers 20h–2Fh are bit-addressable by software using Boolean operation instructions.

Another use of the scratchpad RAM area is for the stack. The stack pointer in the SFRs is used to select storage locations for program variables and for return addresses of control operations.

### MEMORY CONFIGURATION

As illustrated in <u>Figure 6</u>, the DS89C420 incorporates two 8kB flash memories for on-chip program memory and 1kB of SRAM for on-chip data memory or a particular range (400–7FF) of "alternate" program memory space. The DS89C420 uses an address scheme that separates program memory from data memory, such that the 16-bit address bus can address each memory area up to 64kB.

#### PROGRAM MEMORY ACCESS

On-chip program memory begins at address 0000h and is contiguous through 3FFFh (16kB). Exceeding the maximum address of on-chip program memory causes the device to access off-chip memory. However, the maximum on-chip decoded address is selectable by software using the ROMSIZE feature. Software can cause the DS89C420 to behave like a device with less on-chip memory. This is beneficial when overlapping external memory is used. The maximum memory size is dynamically variable. Thus, a portion of memory can be removed from the memory map to access off-chip memory, then be restored to access on-chip memory. In fact, all of the on-chip memory can be removed from the memory map allowing the full 64kB memory space to be addressed from off-chip memory. Program memory addresses that are larger than the selected maximum are automatically fetched from outside the part through ports 0 and 2 (Figure 6).

The ROMSIZE register is used to select the maximum on-chip decoded address for program memory. Bits RMS2, RMS1, RMS0 have the following effect:

| RMS2 | RMS1 | RMS0<br>ADDRESS | MAXIMUM ON-CHIP<br>PROGRAM MEMORY |

|------|------|-----------------|-----------------------------------|

| 0    | 0    | 0               | 0k                                |

| 0    | 0    | 1               | 1k/03FFh                          |

| 0    | 1    | 0               | 2k/07FFh                          |

| 0    | 1    | 1               | 4k/0FFFh                          |

| 1    | 0    | 0               | 8k/1FFFh                          |

| 1    | 0    | 1               | 16k (default)/3FFFh               |

| 1    | 1    | 0               | Invalid–Reserved                  |

| 1    | 1    | 1               | Invalid–Reserved                  |

| LEVEL | LB1 | LB2 | LB3 | PROTECTION                                                                                                                                                                        |

|-------|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 1   | 1   | 1   | No program lock. Encrypted verify if encryption array is programmed.                                                                                                              |

| 2     | 0   | 1   | 1   | Prevent MOVC in external memory from reading program code in internal memory. EA is sampled and latched on reset. Allow no further parallel or program memory loader programming. |

| 3     | x   | 0   | 1   | Level 2 plus no verify operation. Also prevent MOVX in external memory<br>from reading internal SRAM.                                                                             |

| 4     | Х   | Х   | 0   | Level 3 plus no external execution.                                                                                                                                               |

#### Table 3. Flash Memory Lock Bits

The DS89C420 provides user-selectable options that must be set before beginning software execution. The option control register uses flash bits rather than SFRs, and is individually erasable and programmable as a byte-wide register. Bit 3 of this register is defined as the watchdog POR default. Setting this bit to 1 disables the watchdog-reset function on power-up, and clearing this bit to 0 enables the watchdog-reset function automatically. Other bits of this register are undefined and are at logic 1 when read. The value of this register can be read at address FCh in parallel programming mode or when executing a verify-option control-register instruction in ROM loader mode.

The signature bytes can be read in ROM loader mode or in parallel programming mode. Reading data from addresses 30h, 31h, and 60h provides signature information about manufacturer, part, and extension as follows:

| ADDRESS VALUE | FUNCTION           |

|---------------|--------------------|

| 30h DAh       | Manufacturer ID    |

| 31h 42h       | DS89C420 Device ID |

| 60h 01h       | Device Extension   |

#### **ROM LOADER**

The full 16kB of on-chip flash program-memory space, security flash block, and external SRAM can be programmed in-system from an external source through serial port 0 under the control of a built-in ROM loader. The ROM loader also has an auto-baud feature that determines which baud rate frequencies are being used for communication and sets up the baud rate generator for communication at that frequency.

When the DS89C420 is powered up and has entered its user operating mode, the ROM loader mode can be invoked at any time by forcing RST = 1,  $\overline{EA}$  = 0, and  $\overline{PSEN}$  = 0. It remains in effect until power-down or when the condition (RST = 1 and  $\overline{PSEN}$  =  $\overline{EA}$  = 0) is removed. Entering the ROM loader mode forces the processor to start fetching from the 2kB internal ROM for program memory initialization and other loader functions.

The read/write accessibility is determined by the state of the lock bits, which can be verified directly by the ROM loader. In the ROM loader mode, a mass-erase operation also erases the memory bank select and sets it to the default state. Otherwise, the memory bank select cannot be altered in the ROM loader mode.

Flash programming is executed by a series of internal flash commands that are derived (by the built-in ROM loader) from data transmitted over the serial interface from a host PC. PC-based software tools that configure and load the microcontrollers are available at <u>www.maxim-ic.com/micros/ftpinfo.html</u>.

Full details of the ROM loader software and its implementation are given in the Ultra-High-Speed Flash Microcontroller User's Guide.

| INSTRUCTION                      | P2.5:0,<br>P1.7:0 | P0.7:0     | PROG              | P2.6 | P2.7 | P3.6 | P3.7 | OPERATION                                                                                                                                                                       |

|----------------------------------|-------------------|------------|-------------------|------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mass Erase                       | Don't care        | Don't care | PL <sup>(1)</sup> | Н    | L    | L    | L    | Mass erase the 16k x 8 program<br>memory, the security block and the bank<br>select. The contents of every memory<br>location is returned to FFh.                               |

| Write Program<br>Memory          | ADDR              | DIN        | PL <sup>(3)</sup> | L    | Н    | Н    | н    | Program the 16k program memory.                                                                                                                                                 |

| Read Program<br>Memory           | ADDR              | DOUT       | H <sup>(4)</sup>  | L    | L    | Н    | Н    | Verify the 16k program memory.                                                                                                                                                  |

| Write Encryption<br>Array        | ADDR              | DIN        | PL <sup>(3)</sup> | L    | Н    | L    | Н    | Program the 64 byte encryption array.                                                                                                                                           |

| Write LB1                        | Don't care        | Don't care | PL <sup>(3)</sup> | Н    | Н    | Н    | Н    | Program LB1 to logic 0.                                                                                                                                                         |

| Write LB2                        | Don't care        | Don't care | PL <sup>(3)</sup> | Н    | Н    | L    | L    | Program LB2 and LB1 to 00b.                                                                                                                                                     |

| Write LB3                        | Don't care        | Don't care | PL <sup>(3)</sup> | Н    | L    | Н    | L    | Program LB3, LB2, and LB1 to 000b.                                                                                                                                              |

| Read Lock Bits                   | Don't care        | DOUT       | H <sup>(4)</sup>  | L    | L    | L    | н    | Verify the lock bits. The lock bits are at<br>address 40h and the three LSBs of the<br>DOUT are the logic value of the lock bits<br>LB3, LB2, and LB1, respectively.            |

| Write Option<br>Control Register | Don't care        | DIN        | PL <sup>(3)</sup> | L    | Н    | L    | L    | Program the option control register. Bit 3<br>of the DIN represents the watchdog<br>POR default setting.                                                                        |

| Erase Option<br>Control Register | Don't care        | Don't care | PL <sup>(2)</sup> | Н    | L    | L    | Н    | Erase the option control register. This operation disables the watch-dog reset function on power-up.                                                                            |

| Read Address 30,<br>31, 60, FC   | ADDR              | DOUT       | H <sup>(4)</sup>  | L    | L    | L    | L    | 30h = Manufacturer ID<br>31h = Device ID<br>60h = Device extension<br>FCh = Verify the option control register.<br>Bit 3 of the DOUT is the logic value of<br>the watchdog POR. |

| <b>Table 4. Parallel Programming</b> | Instruction Set |

|--------------------------------------|-----------------|

|--------------------------------------|-----------------|

<sup>1)</sup> Mass erase requires an active-low  $\overline{PROG}$  pulse width of 828ms.

<sup>2)</sup> Erase option control register requires an active-low PROG pulse width of 828ms.

<sup>3)</sup> Byte program requires an active-low  $\overline{PROG}$  pulse width of 100 $\mu$ s max.

<sup>4)</sup> *PROG* is weakly pulled to a high internally.

**Note 1:** P3.2 is pulled low during programming to indicate Busy. P3.2 is pulled high again when programming is completed to indicate Ready. **Note 2:** P3.0 is pulled high during programming to indicate an error.

# DATA POINTER INCREMENT/DECREMENT AND OPTIONS

The DS89C420 incorporates a hardware feature to assist applications that require data pointer increment/decrement. Data pointer increment/decrement bits ID0 and ID1 (DPS.6 and DPS.7) define how the INC DPTR instruction functions in relation to the active DPTR (selected by the SEL bit). Setting ID0 = 1 and SEL = 0 enables the decrement operation for DPTR, and execution of the INC DPTR instruction decrements the DPTR contents by 1. Similarly, setting ID1 = 1 and SEL = 1 enables the decrement operation for DPTR1, and execution of the INC DPTR instruction decrements the DPTR1 contents by 1. With this feature, the user can configure the data pointers to operate in four ways for the INC DPTR instruction:

| ID1 | ID0 | SEL = 0        | SEL = 1         |

|-----|-----|----------------|-----------------|

| 0   | 0   | Increment DPTR | Increment DPTR1 |

| 0   | 1   | Decrement DPTR | Increment DPTR1 |

| 1   | 0   | Increment DPTR | Decrement DPTR1 |

| 1   | 1   | Decrement DPTR | Decrement DPTR1 |

The SEL (DPS.0) bit always selects the active data pointer. The DS89C420 offers a programmable option that allows any instructions related to data pointer to toggle the SEL bit automatically. This option is enabled by setting the toggle-select-enable bit (TSL-DPS.5) to logic 1. Once enabled, the SEL bit is automatically toggled after the execution of one of the following five DPTR-related instructions:

INC DPTR MOV DPTR #data16 MOVC A, @A+DPTR MOVX A, @DPTR MOVX @DPTR, A

The DS89C420 also offers a programmable option that automatically increases (or decreases) the contents of the selected data pointer by 1 after the execution of a DPTR-related instruction. The actual function (increment or decrement) is dependent upon the setting of the ID1 and ID0 bits. This option is enabled by setting the automatic increment/decrement enable (AID-DPS.4) to a logic 1 and is affected by one of the following three instructions:

MOVC A, @A+DPTR MOVX A, @DPTR MOVX @DPTR, A

### EXTERNAL MEMORY