Welcome to E-XFL.COM

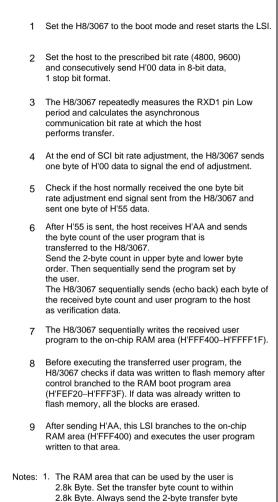

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI, SmartCard                                                               |

| Peripherals                | DMA, PWM, WDT                                                                |

| Number of I/O              | 70                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-BFQFP                                                                    |

| Supplier Device Package    | 100-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3067rf20v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.6 Instruction Set

### 2.6.1 Instruction Set Overview

The H8/300H CPU has 62 types of instructions, which are classified in table 2.1.

| Table 2.1 | Instruction | Classification |

|-----------|-------------|----------------|

|-----------|-------------|----------------|

| Function              | Instruction                                                                                            | Types |

|-----------------------|--------------------------------------------------------------------------------------------------------|-------|

| Data transfer         | MOV, PUSH <sup>*1</sup> , POP <sup>*1</sup> , MOVTPE <sup>*2</sup> , MOVFPE <sup>*2</sup>              | 3     |

| Arithmetic operations | ADD, SUB, ADDX, SUBX, INC, DEC, ADDS, SUBS, DAA, DAS, MULXU, MULXS, DIVXU, DIVXS, CMP, NEG, EXTS, EXTU | 18    |

| Logic operations      | AND, OR, XOR, NOT                                                                                      | 4     |

| Shift operations      | SHAL, SHAR, SHLL, SHLR, ROTL, ROTR, ROTXL, ROTXR                                                       | 8     |

| Bit manipulation      | BSET, BCLR, BNOT, BTST, BAND, BIAND, BOR, BIOR, BXOR, BIXOR, BLD, BILD, BST, BIST                      | 14    |

| Branch                | Bcc*3, JMP, BSR, JSR, RTS                                                                              | 5     |

| System control        | TRAPA, RTE, SLEEP, LDC, STC, ANDC, ORC, XORC, NOP                                                      | 9     |

| Block data transfer   | EEPMOV                                                                                                 | 1     |

Total 62 types

- Notes: 1. POP.W Rn is identical to MOV.W @SP+, Rn. PUSH.W Rn is identical to MOV.W Rn, @-SP. POP.L ERn is identical to MOV.L @SP+, Rn. PUSH.L ERn is identical to MOV.L Rn, @-SP.

- 2. Not available in the H8/3067 Group.

- 3. Bcc is a generic branching instruction.

| Instruction  | Size*       | Function                                                                                                                                   |

|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| MOV          | B/W/L       | $(EAs) \rightarrow Rd, Rs \rightarrow (EAd)$                                                                                               |

|              |             | Moves data between two general registers or between a general register and memory, or moves immediate data to a general register.          |

| MOVFPE       | В           | $(EAs) \rightarrow Rd$                                                                                                                     |

|              |             | Cannot be used in this LSI.                                                                                                                |

| MOVTPE       | В           | $Rs \rightarrow (EAs)$                                                                                                                     |

|              |             | Cannot be used in this LSI.                                                                                                                |

| POP          | W/L         | $@SP+ \rightarrow Rn$                                                                                                                      |

|              |             | Pops a general register from the stack. POP.W Rn is identical to MOV.W<br>@SP+, Rn. Similarly, POP.L ERn is identical to MOV.L @SP+, ERn.  |

| PUSH         | W/L         | $Rn \rightarrow @-SP$                                                                                                                      |

|              |             | Pushes a general register onto the stack. PUSH.W Rn is identical to MOV.W Rn, @-SP. Similarly, PUSH.L ERn is identical to MOV.L ERn, @-SP. |

| Note: * Size | e refers to | o the operand size.                                                                                                                        |

| B:           | Byte        |                                                                                                                                            |

Table 2.3

Data Transfer Instructions

W: Word

L: Longword

### Table 2.4 Arithmetic Operation Instructions

| Instruction | Size* | Function                                                                                                                                                                                                                             |  |  |  |  |  |  |

|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| ADD,SUB     | B/W/L | $Rd \pm Rs \to Rd,  Rd \pm \#IMM \to Rd$                                                                                                                                                                                             |  |  |  |  |  |  |

|             |       | Performs addition or subtraction on data in two general registers, or on immediate data and data in a general register. (Immediate byte data cannot be subtracted from data in a general register. Use the SUBX or ADD instruction.) |  |  |  |  |  |  |

| ADDX,       | В     | $Rd \pm Rs \pm C \to Rd,  Rd \pm \#IMM \pm C \to Rd$                                                                                                                                                                                 |  |  |  |  |  |  |

| SUBX        |       | Performs addition or subtraction with carry or borrow on data in two general registers, or on immediate data and data in a general register.                                                                                         |  |  |  |  |  |  |

| INC,        | B/W/L | $Rd \pm 1 \rightarrow Rd, Rd \pm 2 \rightarrow Rd$                                                                                                                                                                                   |  |  |  |  |  |  |

| DEC         |       | Increments or decrements a general register by 1 or 2. (Byte operands can be incremented or decremented by 1 only.)                                                                                                                  |  |  |  |  |  |  |

| ADDS,       | L     | $Rd \pm 1 \to Rd,  Rd \pm 2 \to Rd,  Rd \pm 4 \to Rd$                                                                                                                                                                                |  |  |  |  |  |  |

| SUBS        |       | Adds or subtracts the value 1, 2, or 4 to or from data in a 32-bit register.                                                                                                                                                         |  |  |  |  |  |  |

| DAA, B      |       | Rd decimal adjust $\rightarrow$ Rd                                                                                                                                                                                                   |  |  |  |  |  |  |

| DAS         |       | Decimal-adjusts an addition or subtraction result in a general register by referring to CCR to produce 4-bit BCD data.                                                                                                               |  |  |  |  |  |  |

| MULXU B/W   |       | $Rd \times Rs \rightarrow Rd$                                                                                                                                                                                                        |  |  |  |  |  |  |

|             |       | Performs unsigned multiplication on data in two general registers:<br>either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$ 16 bits $\rightarrow$ 32 bits.                                                         |  |  |  |  |  |  |

| MULXS       | B/W   | $Rd \times Rs \to Rd$                                                                                                                                                                                                                |  |  |  |  |  |  |

|             |       | Performs signed multiplication on data in two general registers:<br>either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$ 16 bits $\rightarrow$ 32 bits.                                                           |  |  |  |  |  |  |

| DIVXU       | B/W   | $Rd \div Rs \to Rd$                                                                                                                                                                                                                  |  |  |  |  |  |  |

|             |       | Performs unsigned division on data in two general registers: either 16 bits $\div$ 8 bits $\rightarrow$ 8-bit quotient and 8-bit remainder or 32 bits $\div$ 16 bits $\rightarrow$ 16-bit quotient and 16-bit remainder              |  |  |  |  |  |  |

| DIVXS       | B/W   | $Rd \div Rs \to Rd$                                                                                                                                                                                                                  |  |  |  |  |  |  |

|             |       | Performs signed division on data in two general registers: either 16 bits $\div$ 8 bits $\rightarrow$ 8-bit quotient and 8-bit remainder, or 32 bits $\div$ 16 bits $\rightarrow$ 16-bit quotient and 16-bit remainder               |  |  |  |  |  |  |

| CMP         | B/W/L | Rd – Rs, Rd – #IMM                                                                                                                                                                                                                   |  |  |  |  |  |  |

|             |       | Compares data in a general register with data in another general register or with immediate data, and sets CCR according to the result.                                                                                              |  |  |  |  |  |  |

| NEG         | B/W/L | $0 - Rd \rightarrow Rd$                                                                                                                                                                                                              |  |  |  |  |  |  |

|             |       | Takes the two's complement (arithmetic complement) of data in a general register.                                                                                                                                                    |  |  |  |  |  |  |

### 4.6 Notes on Stack Usage

When accessing word data or longword data, the H8/3067 Group regards the lowest address bit as 0. The stack should always be accessed by word access or longword access, and the value of the stack pointer (SP, ER7) should always be kept even.

Use the following instructions to save registers:

PUSH.W Rn (or MOV.W Rn, @–SP) PUSH.L ERn (or MOV.L ERn, @–SP) Use the following instructions to restore registers:

> POP.W Rn (or MOV.W @SP+, Rn) POP.L ERn (or MOV.L @SP+, ERn)

Setting SP to an odd value may lead to a malfunction. Figure 4.7 shows an example of what happens when the SP value is odd.

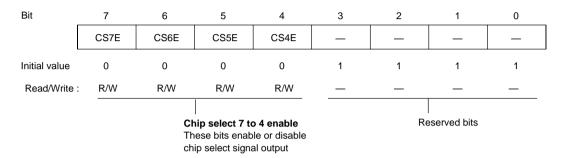

### 6.2.6 Chip Select Control Register (CSCR)

CSCR is an 8-bit readable/writable register that enables or disables output of chip select signals  $(\overline{CS}_7 \text{ to } \overline{CS}_4)$ .

If output of a chip select signal is enabled by a setting in this register, the corresponding pin functions as a chip select signal  $(\overline{CS}_7 \text{ to } \overline{CS}_4)$  output regardless of any other settings. CSCR cannot be modified in single-chip mode.

CSCR is initialized to H'0F by a reset and in hardware standby mode. It is not initialized in software standby mode.

Bits 7 to 4—Chip Select 7 to 4 Enable (CS7E to CS4E): These bits enable or disable output of the corresponding chip select signal.

| Bit n<br>CSnE               | Description                                  |                 |

|-----------------------------|----------------------------------------------|-----------------|

| 0                           | Output of chip select signal CSn is disabled | (Initial value) |

| 1                           | Output of chip select signal CSn is enabled  |                 |

| Note: $n = 7 \text{ to } 4$ |                                              |                 |

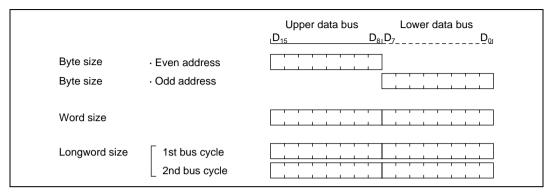

In byte access, whether the upper or lower data bus is used is determined by whether the address is even or odd. The upper data bus is used for an even address, and the lower data bus for an odd address.

Figure 6.8 Access Sizes and Data Alignment Control (16-Bit Access Area)

#### 6.4.3 Valid Strobes

Table 6.4 shows the data buses used, and the valid strobes, for the access spaces.

In a read, the  $\overline{RD}$  signal is valid for both the upper and the lower half of the data bus.

In a write, the  $\overline{HWR}$  signal is valid for the upper half of the data bus, and the  $\overline{LWR}$  signal for the lower half.

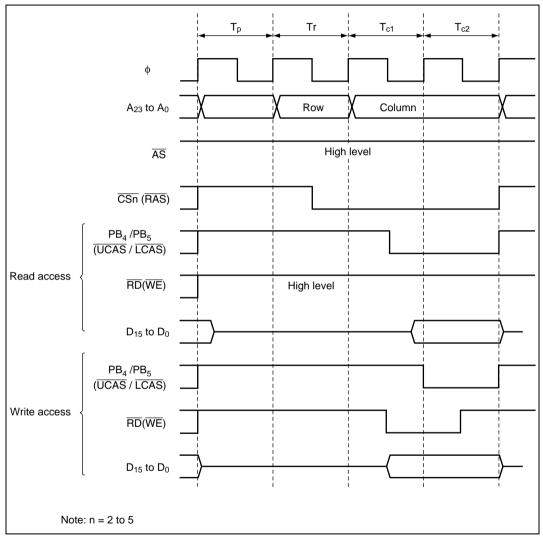

### Renesas

If a DRAM read/write cycle is followed by an access cycle for an external area other than DRAM space when  $\overline{HWR}$  and  $\overline{LWR}$  are selected as the  $\overline{UCAS}$  and  $\overline{LCAS}$  output pins, an idle cycle (Ti) is inserted unconditionally immediately after the DRAM access cycle. See section 6.9, Idle Cycle, for details.

Figure 6.18 Basic Access Timing (CSEL = 0 in DRCRB)

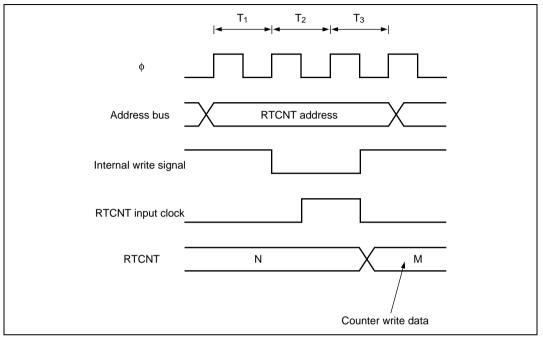

**Contention between RTCNT Write and Increment:** If an increment pulse occurs in the  $T_3$  state of an RTCNT write cycle, writing takes priority and RTCNT is not incremented. See Figure 6.40.

Figure 6.40 Contention between RTCNT Write and Increment

| No. | CKS2 to CKS0<br>Write Timing                          | RTCNT Operation    |

|-----|-------------------------------------------------------|--------------------|

| 3   | "High" <del>→</del> "Low"<br>switchover* <sup>3</sup> | Old clock source   |

|     |                                                       | New clock source   |

|     |                                                       |                    |

|     |                                                       | RTCNT N N+1 N+2    |

|     |                                                       | CKS bits rewritten |

| 4   | "High" <b>→</b> "High"<br>switchover <sup>∗4</sup>    | Old clock source   |

|     |                                                       | New clock source   |

|     |                                                       |                    |

|     |                                                       | RTCNT N N+1 N+2    |

|     |                                                       | CKS bits rewritten |

#### Table 6.10 Internal Clock Switchover and RTCNT Operation (2)

Notes: 3. Including switchover from a high clock source to the halted state.

4. The switchover is regarded as a falling edge, causing RTCNT to increment.

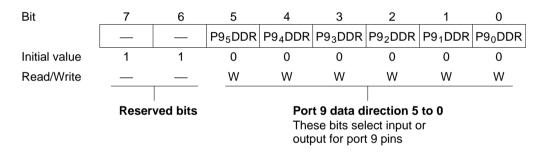

### 8.10.2 Register Descriptions

Table 8.16 summarizes the registers of port 9.

#### Table 8.16 Port 9 Registers

| Address* | Name                           | Abbreviation | R/W | Initial Value |

|----------|--------------------------------|--------------|-----|---------------|

| H'EE008  | Port 9 data direction register | P9DDR        | W   | H'C0          |

| H'FFFD8  | Port 9 data register           | P9DR         | R/W | H'C0          |

|          |                                |              |     |               |

Note: \* Lower 20 bits of the address in advanced mode.

**Port 9 Data Direction Register (P9DDR):** P9DDR is an 8-bit write-only register that can select input or output for each pin in port 9.

Bits 7 and 6 are reserved. They are fixed at 1, and cannot be modified.

When port 9 functions as an input/output port, a pin in port 9 becomes an output port if the corresponding P9DDR bit is set to 1, and an input port if this bit is cleared to 0. For the method of selecting the pin functions, see table 8.17.

P9DDR is a write-only register. Its value cannot be read. All bits return 1 when read.

P9DDR is initialized to H'C0 by a reset and in hardware standby mode. In software standby mode it retains its previous setting. Therefore, if a transition is made to software standby mode while port 9 is functioning as an input/output port and a P9DDR bit is set to 1, the corresponding pin maintains its output state.

| Channel | Address <sup>*1</sup> | Name                         | Abbre-<br>viation | R/W | Initial<br>Value |

|---------|-----------------------|------------------------------|-------------------|-----|------------------|

| 2       | H'FFF78               | Timer control register 2     | TCR2              | R/W | H'80             |

|         | H'FFF79               | Timer I/O control register 2 | TIOR2             | R/W | H'88             |

|         | H'FFF7A               | Timer counter 2H             | TCNT2H            | R/W | H'00             |

|         | H'FFF7B               | Timer counter 2L             | TCNT2L            | R/W | H'00             |

|         | H'FFF7C               | General register A2H         | GRA2H             | R/W | H'FF             |

|         | H'FFF7D               | General register A2L         | GRA2L             | R/W | H'FF             |

|         | H'FFF7E               | General register B2H         | GRB2H             | R/W | H'FF             |

|         | H'FFF7F               | General register B2L         | GRB2L             | R/W | H'FF             |

Notes: 1. The lower 20 bits of the address in advanced mode are indicated.

2. Only 0 can be written in bits 3 to 0, to clear the flags.

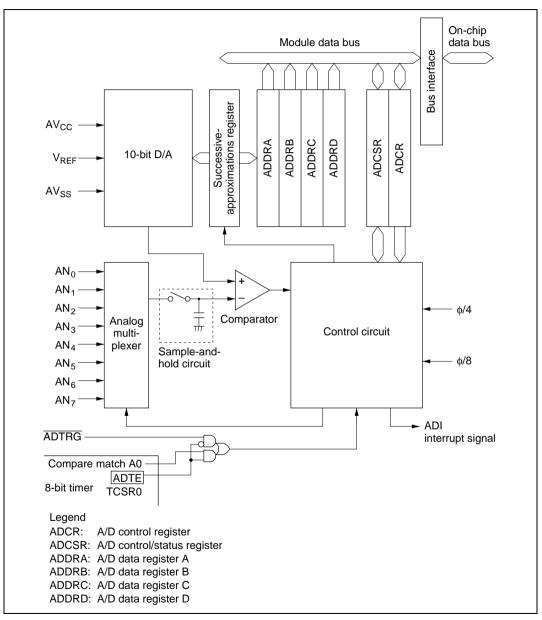

#### 15.1.2 Block Diagram

Figure 15.1 shows a block diagram of the A/D converter.

Figure 15.1 A/D Converter Block Diagram

Rev. 4.00 Jan 26, 2006 page 570 of 938 REJ09B0276-0400

# Section 17 RAM

## 17.1 Overview

The H8/3067 and H8/3066 have 4 kbytes of high-speed static RAM on-chip. The H8/3065 has 2 kbytes. The RAM is connected to the CPU by a 16-bit data bus. The CPU accesses both byte data and word data in two states, making the RAM useful for rapid data transfer.

The on-chip RAM of the H8/3067 and H8/3066 is assigned to addresses H'FEF20 to H'FFF1F in modes 1, 2, and 7, and to addresses H'FFEF20 to H'FFF1F in modes 3, 4, and 5, and to addresses H'EF20 to H'FF1F in mode 6. The on-chip RAM of the H8/3065 are assigned to addresses H'FF720 to H'FFF1F in modes 1, 2, and 7, and to addresses H'FF720 to H'FFF1F in modes 3, 4, and 5, and to addresses H'F720 to H'FFF1F in mode 6. The RAM enable bit (RAME) in the system control register (SYSCR) can enable or disable the on-chip RAM.

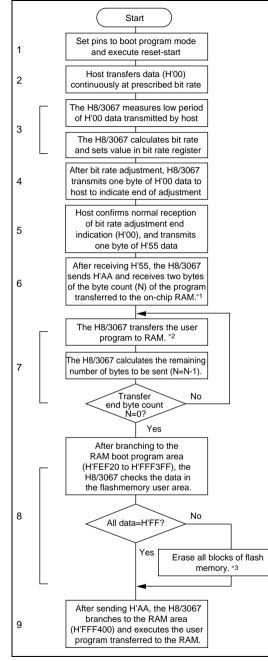

count in upper byte and lower byte order. Transfer byte count example: For 256 bytes (H'0100),

2. Set the part that controls the user program flash

memory at the program according to the flash memory programming/erase algorithms described later.

3. When a memory cell malfunctions and cannot be

erased, the H8/3067 sends one H'FF byte as an erase

error and stops the erase operation and subsequent

upper byte H'01, lower byte H'00.

operations.

#### Figure 18.6 Boot Mode Execution Procedure

### Renesas

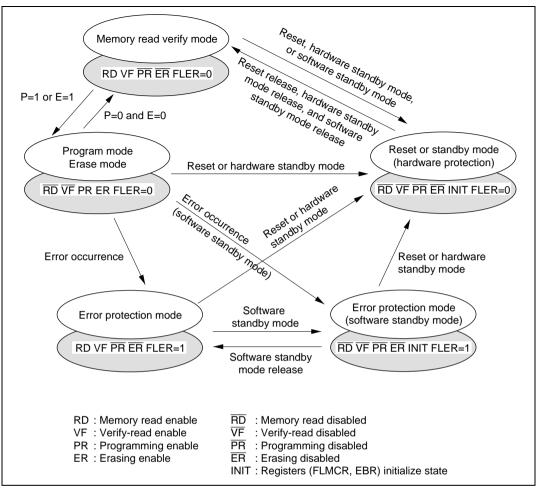

### Figure 18.13 Flash Memory State Transitions (When High level apply to FWE pin in modes 5 and 7 (on-chip ROM enabled))

The error protection function is disabled for errors other than the FLER bit set conditions. If considerable time elapses up to transit to this protection state, the flash memory may already be damaged. As a result, this function cannot completely protect the flash memory against damage.

Therefore, to prevent such erroneous operation, operation must be carried out correctly in according with the program/erase algorithms in the state that flash write enable (FWE) is set. In addition, the operation must be always carried out correctly by supervising microcomputer errors inside and outside the chip with the watchdog timer, etc. At transition to this protection mode, the flash memory may be erroneously programmed or erased, or its abort may result in incomplete

# Renesas

#### 21.2.2 DC Characteristics

Tables 21.11 lists the DC characteristics. Table 21.12 lists the permissible output currents.

#### Table 21.11 DC Characteristics (1)

Conditions:  $V_{cc} = 5.0 V \pm 10\%$ ,  $AV_{cc} = 5.0 V \pm 10\%$ ,  $V_{REF} = 4.5 V$  to  $AV_{cc}^{*1}$ ,  $V_{ss} = AV_{ss} = 0 V^{*1}$ ,  $T_a = -20^{\circ}$ C to  $+75^{\circ}$ C (regular specifications),  $T_a = -40^{\circ}$ C to  $+85^{\circ}$ C (wide-range specifications) [Programming/erasing conditions:  $T_a = 0^{\circ}$ C to  $+75^{\circ}$ C (regular specifications),  $T_a = 0^{\circ}$ C to  $+85^{\circ}$ C (wide-range specifications)]

| ltem                  |                                                                                                                                            | Symbol                      | Min                   | Тур | Max                   | Unit | Test Conditions                                         |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------|-----|-----------------------|------|---------------------------------------------------------|

| Schmitt trigger       |                                                                                                                                            | V <sub>T</sub> <sup>-</sup> | 1.0                   | _   | _                     | V    |                                                         |

| input voltages        | $P8_0$ to $P8_2$                                                                                                                           | $V_{T}^{+}$                 | —                     | —   | $V_{cc} 	imes 0.7$    | V    |                                                         |

|                       |                                                                                                                                            | $V_T^+ - V_T^-$             | 0.4                   | _   | _                     | V    | _                                                       |

| Input high<br>voltage | $\frac{\text{RES}}{\text{NMI}}, \frac{\text{STBY}}{\text{MD}_2} \text{ to} \\ \text{MD}_0, \text{FWE}$                                     | V <sub>IH</sub>             | V <sub>cc</sub> – 0.7 |     | V <sub>cc</sub> + 0.3 | V    |                                                         |

|                       | EXTAL                                                                                                                                      | -                           | $V_{cc} \times 0.7$   | _   | V <sub>cc</sub> + 0.3 | V    | -                                                       |

|                       | Port 7                                                                                                                                     | -                           | 2.0                   | —   | $AV_{cc} + 0.3$       | V    | =                                                       |

|                       | Ports 1 to 6,<br>P8 <sub>3</sub> , P8 <sub>4</sub> , P9 <sub>0</sub> to<br>P9 <sub>5</sub> , port B                                        | -                           | 2.0                   | _   | V <sub>cc</sub> + 0.3 | V    | -                                                       |

| Input low<br>voltage  | $\frac{\overline{\text{RES}}, \overline{\text{STBY}},}{\overline{\text{FWE}}, \overline{\text{MD}}_2 \text{ to}}$ $\overline{\text{MD}}_0$ | V <sub>IL</sub>             | -0.3                  |     | 0.5                   | V    |                                                         |

|                       | NMI, EXTAL,<br>ports 1 to 7,<br>$P8_3$ , $P8_4$ , $P9_0$ to<br>$P9_5$ , port B                                                             | -                           | -0.3                  | _   | 0.8                   | V    | -                                                       |

| Output high           | All output pins                                                                                                                            | V <sub>OH</sub>             | $V_{cc} - 0.5$        | _   | _                     | V    | I <sub>oH</sub> = -200 μA                               |

| voltage               |                                                                                                                                            |                             | 3.5                   |     | —                     | V    | I <sub>он</sub> = —1 mA                                 |

| Output low            | All output pins                                                                                                                            | V <sub>ol</sub>             | _                     |     | 0.4                   | V    | I <sub>oL</sub> = 1.6 mA                                |

| voltage               | Ports 1, 2,<br>and 5                                                                                                                       | -                           | _                     | _   | 1.0                   | V    | I <sub>oL</sub> = 10 mA                                 |

| Input leakage current | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                      | I <sub>in</sub>             | _                     | _   | 1.0                   | μA   | $V_{in}$ = 0.5 V to<br>$V_{cc}$ – 0.5 V                 |

|                       | Port 7                                                                                                                                     | -                           |                       | —   | 1.0                   | μA   | $V_{in} = 0.5 \text{ V to}$<br>AV <sub>cc</sub> - 0.5 V |

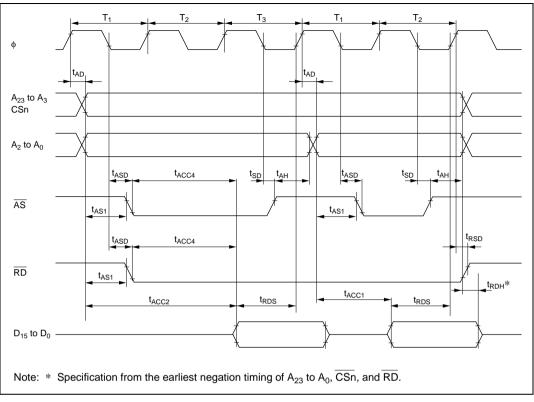

Figure 21.14 Burst ROM Access Timing: Two-State Access

|                                                  | nput Pull | -Up Con      | trol Regi   | ster                                            |                                                                              | H'EE03                                                                               | E                                                                     | Port                                |

|--------------------------------------------------|-----------|--------------|-------------|-------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------|

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

| Bit                                              | 7         | 6            | 5           | 4                                               | 3                                                                            | 2                                                                                    | 1                                                                     | 0                                   |

|                                                  | P47PCR    | P46PCR       | P45PCR      | P44PCR                                          | P43PCR                                                                       | P42PCR                                                                               | P41PCR                                                                | P40PCR                              |

| Initial value                                    | 0         | 0            | 0           | 0                                               | 0                                                                            | 0                                                                                    | 0                                                                     | 0                                   |

| Read/Write                                       | R/W       | R/W          | R/W         | R/W                                             | R/W                                                                          | R/W                                                                                  | R/W                                                                   | R/W                                 |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

| Port 4 input pull-up control 7 to 0              |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

| 0 Input pull-up transistor is off                |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

|                                                  |           | 1            | I Input p   | oull-up tran                                    | sistor is o                                                                  | n                                                                                    |                                                                       |                                     |

|                                                  |           | Not          | te: Valid w | hen the co                                      | orrespondi                                                                   | ing P4DDF                                                                            | R bit is clea                                                         | ared to 0                           |

|                                                  |           |              | (doolgi     | nating gene                                     | ono mput).                                                                   |                                                                                      |                                                                       |                                     |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

| R—Port 5 I                                       | nput Pull | -Up Con      | trol Regi   | ster                                            |                                                                              | H'EE03                                                                               | F                                                                     | Port                                |

|                                                  |           |              |             |                                                 |                                                                              |                                                                                      |                                                                       |                                     |

| R—Port 5 I                                       | nput Pull | -Up Con<br>6 | trol Regi   | ster<br>4                                       | 3                                                                            | 2                                                                                    | 1                                                                     | 0                                   |

|                                                  |           |              |             |                                                 | 3<br>P53PCR                                                                  |                                                                                      | 1                                                                     |                                     |

| Bit<br>Initial value                             |           |              |             |                                                 | P53PCR<br>0                                                                  | 2<br>P52PCR<br>0                                                                     | 1<br>P51PCR<br>0                                                      | 0<br>P50PCR<br>0                    |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4                                               | P53PCR                                                                       | 2<br>P52PCR                                                                          | 1<br>P51PCR                                                           | 0<br>P50PCR                         |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br><br>1<br>                                  | P53PCR<br>0<br>R/W                                                           | 2<br>P52PCR<br>0<br>R/W                                                              | 1<br>P51PCR<br>0<br>R/W                                               | 0<br>P50PCR<br>0                    |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br>1<br><br>Port 5 ii                         | P53PCR<br>0<br>R/W                                                           | 2<br>P52PCR<br>0<br>R/W                                                              | 1<br>P51PCR<br>0<br>R/W                                               | 0<br>P50PCR<br>0                    |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br><br>Port 5 ii<br>0 Ir                      | P53PCR<br>0<br>R/W<br>nput pull-u                                            | 2<br>P52PCR<br>0<br>R/W<br>up control 3<br>p transisto                               | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off                         | 0<br>P50PCR<br>0                    |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br><br>Port 5 ii<br>0 Ir                      | P53PCR<br>0<br>R/W<br>nput pull-u                                            | 2<br>P52PCR<br>0<br>R/W                                                              | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off                         | 0<br>P50PCR<br>0                    |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br><br>Port 5 in<br>0 Ir<br>1 Ir              | P53PCR<br>0<br>R/W<br>nput pull-u<br>nput pull-u<br>nput pull-u              | 2<br>P52PCR<br>0<br>R/W<br>up control 3<br>p transisto<br>p transisto                | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off<br>r is on              | 0<br>P50PCR<br>0<br>R/W             |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br>1<br>Port 5 ii<br>0 Ir<br>1 Ir<br>Note: Va | P53PCR<br>0<br>R/W<br>nput pull-u<br>nput pull-u<br>nput pull-u<br>alid when | 2<br>P52PCR<br>0<br>R/W<br>up control 3<br>p transisto<br>p transisto<br>p transisto | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off<br>r is on<br>ponding P | 0<br>P50PCR<br>0<br>R/W<br>5DDR bit |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br>1<br>Port 5 ii<br>0 Ir<br>1 Ir<br>Note: Va | P53PCR<br>0<br>R/W<br>nput pull-u<br>nput pull-u<br>nput pull-u<br>alid when | 2<br>P52PCR<br>0<br>R/W<br>up control 3<br>p transisto<br>p transisto                | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off<br>r is on<br>ponding P | 0<br>P50PCR<br>0<br>R/W<br>5DDR bit |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br>1<br>Port 5 ii<br>0 Ir<br>1 Ir<br>Note: Va | P53PCR<br>0<br>R/W<br>nput pull-u<br>nput pull-u<br>nput pull-u<br>alid when | 2<br>P52PCR<br>0<br>R/W<br>up control 3<br>p transisto<br>p transisto<br>p transisto | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off<br>r is on<br>ponding P | 0<br>P50PCR<br>0<br>R/W<br>5DDR bit |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br>1<br>Port 5 ii<br>0 Ir<br>1 Ir<br>Note: Va | P53PCR<br>0<br>R/W<br>nput pull-u<br>nput pull-u<br>nput pull-u<br>alid when | 2<br>P52PCR<br>0<br>R/W<br>up control 3<br>p transisto<br>p transisto<br>p transisto | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off<br>r is on<br>ponding P | 0<br>P50PCR<br>0<br>R/W<br>5DDR bit |

| Bit<br>Initial value                             | 7         | 6            | 5           | 4<br>1<br>Port 5 ii<br>0 Ir<br>1 Ir<br>Note: Va | P53PCR<br>0<br>R/W<br>nput pull-u<br>nput pull-u<br>nput pull-u<br>alid when | 2<br>P52PCR<br>0<br>R/W<br>up control 3<br>p transisto<br>p transisto<br>p transisto | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off<br>r is on<br>ponding P | 0<br>P50PCR<br>0<br>R/W<br>5DDR bit |

| R—Port 5 I<br>Bit<br>Initial value<br>Read/Write | 7         | 6            | 5           | 4<br>1<br>Port 5 ii<br>0 Ir<br>1 Ir<br>Note: Va | P53PCR<br>0<br>R/W<br>nput pull-u<br>nput pull-u<br>nput pull-u<br>alid when | 2<br>P52PCR<br>0<br>R/W<br>up control 3<br>p transisto<br>p transisto<br>p transisto | 1<br>P51PCR<br>0<br>R/W<br>3 to 0<br>r is off<br>r is on<br>ponding P | 0<br>P50PCR<br>0<br>R/W<br>5DDR bit |

| Pin<br>Name | Mode   | Reset | Hardware<br>Standby<br>Mode | Software Standby<br>Mode                                                                                                                                                                                                                                                                | Bus-Released<br>Mode                                                                                                                                                    | Program Execution<br>Mode                                                                                                                                                                                                   |

|-------------|--------|-------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P80         | 1 to 5 | Т     | Т                           | When DRAM space<br>is not selected <sup>*1</sup><br>(RFSHE=0)<br>Keep<br>(RFSHE=1)<br>Illegal setting<br>When DRAM space<br>is selected <sup>*2</sup><br>(RFSHE=0)<br>Keep<br>(RFSHE=1,<br>SRFMD=0, SSOE=0)<br>T<br>(RFSHE=1,<br>SRFMD=0, SSOE=1)<br>H<br>(RFSHE=1,<br>SRFMD=1)<br>RFSH |                                                                                                                                                                         | (RFSHE=0)<br>I/O port<br>(RFSHE=1)<br>RFSH                                                                                                                                                                                  |

|             | 6, 7   | Т     | Т                           | Кеер                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                       | I/O port                                                                                                                                                                                                                    |

| P81         | 1 to 5 | Τ     | Τ                           | When DRAM space<br>is selected <sup>*3</sup><br>(SSOE=0)<br>T<br>(SSOE=1)<br>H<br>When DRAM space<br>is selected <sup>*4</sup><br>Keep<br>Otherwise <sup>*5 *1</sup><br>(DDR=0)<br>T<br>(DDR=1, SSOE=0)<br>T<br>(DDR=1, SSOE=1)<br>H                                                    | When DRAM space<br>is selected <sup>*3</sup><br>T<br>When DRAM space<br>is selected <sup>*4</sup><br>Keep<br>Otherwise <sup>*1</sup><br>(DDR=0)<br>Keep<br>(DDR=1)<br>T | When DRAM space<br>is selected and RAS3<br>is output<br>$\overline{RAS}_3$<br>When DRAM space<br>is selected and RAS3<br>is<br>not output<br>I/O port<br>Otherwise<br>(DDR=0)<br>Input port<br>(DDR=1)<br>$\overline{CS}_3$ |

|             | 6, 7   | Т     | Т                           | Keep                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                       | I/O port                                                                                                                                                                                                                    |