Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | Н8/300Н                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20MHz                                                                          |

| Connectivity               | SCI, SmartCard                                                                 |

| Peripherals                | DMA, PWM, WDT                                                                  |

| Number of I/O              | 70                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-BFQFP                                                                      |

| Supplier Device Package    | 100-QFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3067rf20vtr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section 5 Interrupt Controller

# 5.1 Overview

### 5.1.1 Features

The interrupt controller has the following features:

- Interrupt priority registers (IPRs) for setting interrupt priorities Interrupts other than NMI can be assigned to two priority levels on a module-by-module basis in interrupt priority registers A and B (IPRA and IPRB).

- Three-level masking by the I and UI bits in the CPU condition code register (CCR)

- Seven external interrupt pins

NMI has the highest priority and is always accepted<sup>\*</sup>; either the rising or falling edge can be selected. For each of  $IRQ_0$  to  $IRQ_5$ , sensing of the falling edge or level sensing can be selected independently.

Note: \* In the flash memory and flash memory R versions, NMI input is sometimes disabled. For details see 18.6.4, NMI Input Disable Conditions.

Bit 2—Priority Level B2 (IPRB2): Selects the priority level of SCI channel 1 interrupt requests.

| Bit 2<br>IPRB2 | Description                                                         |                          |

|----------------|---------------------------------------------------------------------|--------------------------|

| 0              | SCI1 interrupt requests have priority level 0 (low priority)        | (Initial value)          |

| 1              | SCI1 interrupt requests have priority level 1 (high priority)       |                          |

| Bit 1—F        | Priority Level B1 (IPRB1): Selects the priority level of SCI channe | el 2 interrupt requests. |

| Bit 1<br>IPRB1 | Description                                                            |                 |

|----------------|------------------------------------------------------------------------|-----------------|

| 0              | SCI channel 2 interrupt requests have priority level 0 (low priority)  | (Initial value) |

| 1              | SCI channel 2 interrupt requests have priority level 1 (high priority) |                 |

Bit 0-Reserved: This bit can be written and read, but it does not affect interrupt priority.

Bits 3 and 2—Area 5 Wait Control 1 and 0 (W51, W50): These bits select the number of program wait states when area 5 in external space is accessed while the AST5 bit in ASTCR is set to 1.

| Bit 3 | Bit 2 |                                                                                       |

|-------|-------|---------------------------------------------------------------------------------------|

| W51   | W50   | Description                                                                           |

| 0     | 0     | Program wait not inserted when external space area 5 is accessed                      |

|       | 1     | 1 program wait state inserted when external space area 5 is accessed                  |

| 1     | 0     | 2 program wait states inserted when external space area 5 is accessed                 |

|       | 1     | 3 program wait states inserted when external space area 5 is accessed (Initial value) |

Bits 1 and 0—Area 4 Wait Control 1 and 0 (W41, W40): These bits select the number of program wait states when area 4 in external space is accessed while the AST4 bit in ASTCR is set to 1.

| Bit 1<br>W41 | Bit 0<br>W40 | Description                                                                           |

|--------------|--------------|---------------------------------------------------------------------------------------|

| 0            | 0            | Program wait not inserted when external space area 4 is accessed                      |

|              | 1            | 1 program wait state inserted when external space area 4 is accessed                  |

| 1            | 0            | 2 program wait states inserted when external space area 4 is accessed                 |

|              | 1            | 3 program wait states inserted when external space area 4 is accessed (Initial value) |

**Bit 4—Burst Cycle Select 1 (BRSTS1):** Selects the number of burst cycle states for the burst ROM interface.

| Bit 4<br>BRSTS1 | Description                           |                 |  |  |  |

|-----------------|---------------------------------------|-----------------|--|--|--|

| 0               | Burst access cycle comprises 2 states | (Initial value) |  |  |  |

| 1               | Burst access cycle comprises 3 states |                 |  |  |  |

**Bit 3—Burst Cycle Select 0 (BRSTS0):** Selects the number of words that can be accessed in a burst ROM interface burst access.

# Bit 3 BRSTS0 Description 0 Max. 4 words in burst access (burst access on match of address bits above A3)( 1 Max. 8 words in burst access (burst access on match of address bits above A4)

Bit 2—Reserved: Read-only bit, always read as 1.

**Bit 1—Area Division Unit Select (RDEA):** Selects the memory map area division units. This bit is valid in modes 3, 4, and 5, and is invalid in modes 1, 2, 6, and 7.

#### Bit 1 RDEA Description 0 Area divisions are as follows: Area 0: 2 MB Area 4: 1.93 MB Area 1: 2 MB Area 5: 4 kB Area 2: 8 MB Area 6: 23.75 kB Area 3: 2 MB Area 7: 22 B 1 Areas 0 to 7 are the same size (2 MB) (Initial value)

**Bit 0—WAIT Pin Enable (WAITE):** Enables or disables wait insertion by means of the  $\overline{WAIT}$  pin.

| Bit 0<br>WAITE | Description                                                                                                               |                          |

|----------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 0              | $\overline{\text{WAIT}}$ pin wait input is disabled, and the $\overline{\text{WAIT}}$ pin can be used a input/output port | as an<br>(Initial value) |

| 1              | WAIT pin wait input is enabled                                                                                            |                          |

#### Section 6 Bus Controller

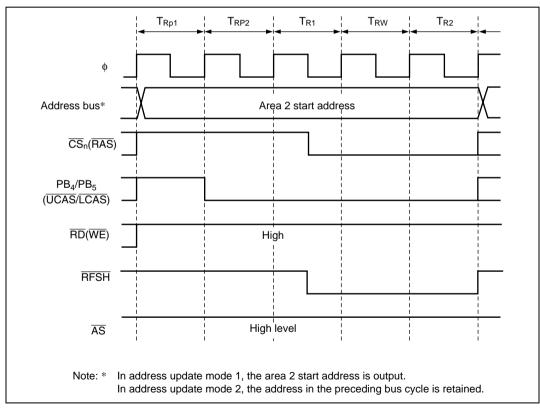

The basic CBS refresh cycle timing comprises three states: one RAS precharge cycle  $(T_{RP})$  state, and two RAS output cycle  $(T_{R1}, T_{R2})$  states. Either one or two states can be selected for the RAS precharge cycle. When the TPC bit is set to 1 in DRCRB, RAS signal output is delayed by one cycle. This does not affect the timing of UCAS and LCAS output.

Use the RLW bit in DRCRB to adjust the  $\overline{RAS}$  signal width. A single refresh wait state ( $T_{RW}$ ) can be inserted between the  $T_{R1}$  state and  $T_{R2}$  state by setting the RLW bit to 1.

The RLW bit setting is valid only for CBR refresh cycles, and does not affect DRAM read/write cycles. The number of states in the CBR refresh cycle is not affected by the settings in ASTCR, WCRH, or WCRL, or by the state of the  $\overline{WAIT}$  pin.

Figure 6.29 shows the timing when the TPC bit and RLW bit are both set to 1.

Figure 6.29 CBR Refresh Timing (CSEL = 0, TPC = 1, RLW = 1)

Rev. 4.00 Jan 26, 2006 page 182 of 938 REJ09B0276-0400

# RENESAS

**Bits 2 to 0—Data Transfer Select 2B to 0B (DTS2B, DTS1B, DTS0B):** These bits select the data transfer activation source. The selectable activation sources differ between normal mode and block transfer mode.

Normal mode

| Bit 2<br>DTS2B | Bit 1<br>DTS1B | Bit 0<br>DTS0B | Description                     |                 |

|----------------|----------------|----------------|---------------------------------|-----------------|

| 0              | 0              | 0              | Auto-request (burst mode)       | (Initial value) |

|                |                | 1              | Cannot be used                  |                 |

|                | 1              | 0              | Auto-request (cycle-steal mode) |                 |

|                |                | 1              | Cannot be used                  |                 |

| 1              | 0              | 0              | Cannot be used                  |                 |

|                |                | 1              | Cannot be used                  |                 |

|                | 1              | 0              | Falling edge of DREQ            |                 |

|                |                | 1              | Low level input at DREQ         |                 |

Block transfer mode

| Bit 2<br>DTS2B | Bit 1<br>DTS1B | Bit 0<br>DTS0B | Description                                                                            |

|----------------|----------------|----------------|----------------------------------------------------------------------------------------|

| 0              | 0              | 0              | Compare match/input capture A interrupt from 16-bit timer channel 0<br>(Initial value) |

|                |                | 1              | Compare match/input capture A interrupt from 16-bit timer channel 1                    |

|                | 1              | 0              | Compare match/input capture A interrupt from 16-bit timer channel 2                    |

|                |                | 1              | Conversion-end interrupt from A/D converter                                            |

| 1              | 0              | 0              | Cannot be used                                                                         |

|                |                | 1              | Cannot be used                                                                         |

|                | 1              | 0              | Falling edge of DREQ                                                                   |

|                |                | 1              | Cannot be used                                                                         |

The same internal interrupt can be selected to activate two or more channels. The channels are activated in a priority order, highest priority first. For the priority order, see section 7.4.9, Multiple-Channel Operation.

# RENESAS

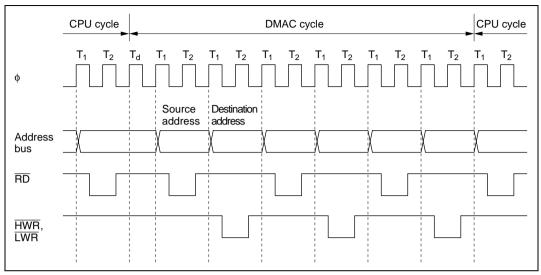

Figure 7.15 shows an auto-requested burst-mode transfer. This example shows a transfer of three words from a 16-bit two-state access area to another 16-bit two-state access area.

Figure 7.15 Burst DMA Bus Timing

When the DMAC is activated from a  $\overline{\text{DREQ}}$  pin there is a minimum interval of four states from when the transfer is requested until the DMAC starts operating. The  $\overline{\text{DREQ}}$  pin is not sampled during the time between the transfer request and the start of the transfer. In short address mode and normal mode, the pin is next sampled at the end of the read cycle. In block transfer mode, the pin is next sampled at the end of the read cycle.

# 8.2 Port 1

### 8.2.1 Overview

Port 1 is an 8-bit input/output port also used for address output, with the pin configuration shown in figure 8.1. The pin functions differ between the expanded modes with on-chip ROM disabled, expanded modes with on-chip ROM enabled, and single-chip mode. In modes 1 to 4 (expanded modes with on-chip ROM disabled), they are address bus output pins ( $A_7$  to  $A_0$ ).

In modes 5 (expanded modes with on-chip ROM enabled), settings in the port 1 data direction register (P1DDR) can designate pins for address bus output ( $A_7$  to  $A_0$ ) or generic input. In mode 6 and 7 (single-chip mode), port 1 is a generic input/output port.

When DRAM is connected to area 2, 3, 4, 5,  $A_7$  to  $A_0$  output row and column addresses in read and write cycles. For details see section 6.5, DRAM Interface.

Pins in port 1 can drive one TTL load and a 90-pF capacitive load. They can also drive an LED or a darlington transistor pair.

|        | Port 1 pins                                                                                                  | Modes 1 to 4                                                                  | Modes 5                                                                                                                                                                                                  | Mode 6 and 7                                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|        | $\begin{array}{c} \bullet  P1_7/A_7 \\ \bullet  \bullet  P1_6/A_6 \\ \bullet  \bullet  P1_5/A_5 \end{array}$ | A <sub>7</sub> (output)<br>A <sub>6</sub> (output)<br>A <sub>5</sub> (output) | P1 <sub>7</sub> (input)/A <sub>7</sub> (output)<br>P1 <sub>6</sub> (input)/A <sub>6</sub> (output)<br>P1 <sub>5</sub> (input)/A <sub>5</sub> (output)                                                    | P1 <sub>7</sub> (input/output)<br>P1 <sub>6</sub> (input/output)<br>P1 <sub>5</sub> (input/output)                                   |

| Port 1 | $P1_4/A_4$ $P1_3/A_3$ $P1_2/A_2$ $P1_1/A_1$                                                                  | $A_4$ (output)<br>$A_3$ (output)<br>$A_2$ (output)<br>$A_1$ (output)          | P1 <sub>4</sub> (input)/A <sub>4</sub> (output)<br>P1 <sub>3</sub> (input)/A <sub>3</sub> (output)<br>P1 <sub>2</sub> (input)/A <sub>2</sub> (output)<br>P1 <sub>1</sub> (input)/A <sub>1</sub> (output) | P1 <sub>4</sub> (input/output)<br>P1 <sub>3</sub> (input/output)<br>P1 <sub>2</sub> (input/output)<br>P1 <sub>1</sub> (input/output) |

|        | ← P1 <sub>0</sub> /A <sub>0</sub>                                                                            | A <sub>0</sub> (output)                                                       | P1 <sub>0</sub> (input)/A <sub>0</sub> (output)                                                                                                                                                          | P1 <sub>0</sub> (input/output)                                                                                                       |

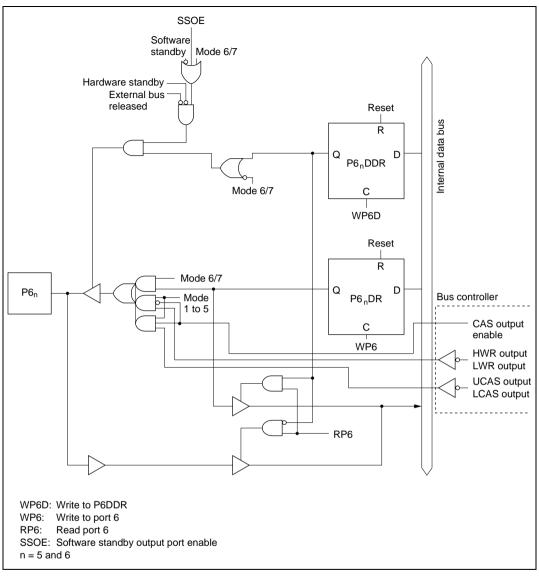

becomes an output port if the corresponding bit of P6<sub>6</sub>DDR to P6<sub>0</sub>DDR is set to 1, and an input port if this pin is cleared to 0.

P6DDR is a write-only register. Its value cannot be read. All bits return 1 when read.

P6DDR is initialized to H'80 by a reset and in hardware standby mode. In software standby mode it retains its previous setting. Therefore, if a transition is made to software standby mode while port 6 is functioning as an input/output port and a P6DDR bit is set to 1, the corresponding pin maintains its output state.

**Port 6 Data Register (P6DR):** P6DR is an 8-bit readable/writable register that stores output data for port 6. When port 6 functions as an output port, the value of this register is output. For bit 7, a value of 1 is returned if the bit is read while the PSTOP bit in MSTCRH is cleared to 0, and the P67 pin logic level is returned if the bit is read while the PSTOP bit is set to 1. Bit 7 cannot be modified. For bits 6 to 0, the pin logic level is returned if the bit is returned if the bit is read while the corresponding bit in P6DDR is cleared to 0, and the P6DR value is returned if the bit is read while the corresponding bit in P6DDR is set to 1.

| Bit                                                                | 7   | 6               | 5               | 4   | 3   | 2               | 1               | 0               |

|--------------------------------------------------------------------|-----|-----------------|-----------------|-----|-----|-----------------|-----------------|-----------------|

|                                                                    | P67 | P6 <sub>6</sub> | P6 <sub>5</sub> | P64 | P63 | P6 <sub>2</sub> | P6 <sub>1</sub> | P6 <sub>0</sub> |

| Initial value                                                      | 1   | 0               | 0               | 0   | 0   | 0               | 0               | 0               |

| Read/Write                                                         | R   | R/W             | R/W             | R/W | R/W | R/W             | R/W             | R/W             |

| <b>Port 6 data 7 to 0</b><br>These bits store data for port 6 pins |     |                 |                 |     |     |                 |                 |                 |

P6DR is initialized to H'80 by a reset and in hardware standby mode. In software standby mode it retains its previous setting.

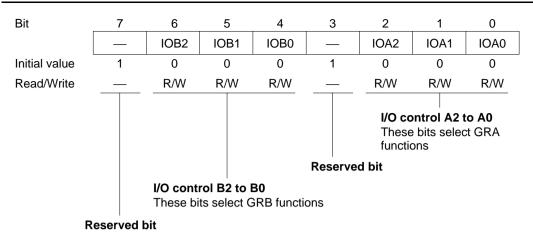

Each TIOR is an 8-bit readable/writable register that selects the output compare or input capture function for GRA and GRB, and specifies the functions of the TIORA and TIORC pins. If the output compare function is selected, TIOR also selects the type of output. If input capture is selected, TIOR also selects the edge or edges of the input capture signal.

TIOR is initialized to H'88 by a reset and in standby mode.

Bit 7—Reserved: This bit cannot be modified and is always read as 1.

Bits 6 to 4—I/O Control B2 to B0 (IOB2 to IOB0): These bits select the GRB function.

| Bit 6<br>IOB2 | Bit 5<br>IOB1 | Bit 4<br>IOB0      | Function             |                                                                 |        |  |  |  |

|---------------|---------------|--------------------|----------------------|-----------------------------------------------------------------|--------|--|--|--|

| 0             | 0             | 0                  | GRB is an output     | No output at compare match (Initial                             | value) |  |  |  |

|               |               | 1                  | compare register<br> | 0 output at GRB compare match*1                                 |        |  |  |  |

|               | 1             | 0                  |                      | 1 output at GRB compare match*1                                 |        |  |  |  |

|               |               | 1                  |                      | Output toggles at GRB compare match (1 output in channel 2)*1*2 |        |  |  |  |

| 1             | 0             | 0                  | GRB is an input      | GRB captures rising edge of input                               |        |  |  |  |

|               |               | 1 compare register |                      | GRB captures falling edge of input                              |        |  |  |  |

|               | 1 0           |                    |                      | GRB captures both edges of input                                |        |  |  |  |

|               |               | 1                  |                      |                                                                 |        |  |  |  |

Notes: 1. After a reset, the output conforms to the TOLR setting until the first compare match.

2. Channel 2 output cannot be toggled by compare match. This setting selects 1 output

instead.

**Bits 7 and 6—Group 3 Compare Match Select 1 and 0 (G3CMS1, G3CMS0):** These bits select the compare match event that triggers TPC output group 3 ( $TP_{15}$  to  $TP_{12}$ ).

| Bit 7<br>G3CMS1 | Bit 6<br>G3CMS0 | Description                                                                                                                        |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| 0               | 0               | TPC output group 3 (TP $_{\rm 15}$ to TP $_{\rm 12}$ ) is triggered by compare match in 16-bit timer channel 0                     |

|                 | 1               | TPC output group 3 (TP $_{15}$ to TP $_{12}$ ) is triggered by compare match in 16-bit timer channel 1                             |

| 1               | 0               | TPC output group 3 (TP $_{15}$ to TP $_{12}$ ) is triggered by compare match in 16-bit timer channel 2                             |

|                 | 1               | TPC output group 3 (TP <sub>15</sub> to TP <sub>12</sub> ) is triggered by (Initial value) compare match in 16-bit timer channel 2 |

Bits 5 and 4—Group 2 Compare Match Select 1 and 0 (G2CMS1, G2CMS0): These bits

| select the compare match event t | hat triggers TPC output | t group 2 ( $TP_{11}$ to $TP_8$ ). |

|----------------------------------|-------------------------|------------------------------------|

|----------------------------------|-------------------------|------------------------------------|

| Bit 5<br>G2CMS1 | Bit 4<br>G2CMS0 | Description                                                                                                  |         |

|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------|---------|

| 0               | 0               | TPC output group 2 (TP <sub>11</sub> to TP <sub>8</sub> ) is triggered by compare match in 1 timer channel 0 | 16-bit  |

|                 | 1               | TPC output group 2 (TP <sub>11</sub> to TP <sub>8</sub> ) is triggered by compare match in 1 timer channel 1 | 16-bit  |

| 1               | 0               | TPC output group 2 (TP <sub>11</sub> to TP <sub>8</sub> ) is triggered by compare match in 1 timer channel 2 | l 6-bit |

|                 | 1               | TPC output group 2 (TP11 to TP3) is triggered by(Initialcompare match in 16-bit timer channel 2              | value)  |

# 12.4 Interrupts

During interval timer operation, an overflow generates an interval timer interrupt (WOVI). The interval timer interrupt is requested whenever the OVF bit is set to 1 in TCSR.

## 12.5 Usage Notes

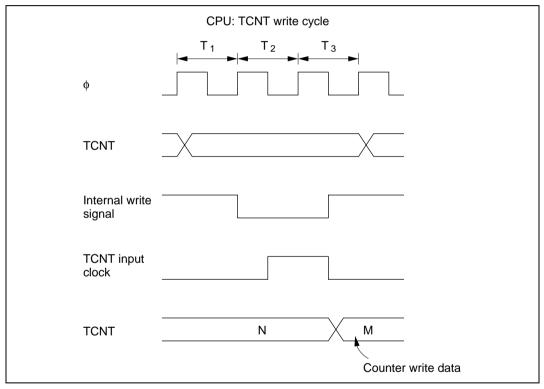

**Contention between TCNT Write and Increment:** If a timer counter clock pulse is generated during the  $T_3$  state of a write cycle to TCNT, the write takes priority and the timer count is not incremented. See figure 12.8.

Figure 12.8 Contention between TCNT Write and Count up

**Changing CKS2 to CKS0 Bit:** Halt TCNT by clearing the TME bit to 0 in TCSR before changing the values of bits CKS2 to CKS0.

**Bit 2—Smart Card Data Invert (SINV):** Specifies inversion of the data logic level. This function is used in combination with the SDIR bit to communicate with inverse-convention cards.<sup>\*2</sup> The SINV bit does not affect the logic level of the parity bit. For parity settings, see section 14.3.4, Register Settings.

| Bit 2<br>SINV | Description                                    |                 |

|---------------|------------------------------------------------|-----------------|

| 0             | Unmodified TDR contents are transmitted        | (Initial value) |

|               | Receive data is stored unmodified in RDR       |                 |

| 1             | Inverted TDR contents are transmitted          |                 |

|               | Receive data is inverted before storage in RDR |                 |

Bit 1—Reserved: Read-only bit, always read as 1.

Bit 0—Smart Card Interface Mode Select (SMIF): Enables the smart card interface function.

| Bit 0 |                                           |                 |

|-------|-------------------------------------------|-----------------|

| SMIF  | Description                               |                 |

| 0     | Smart card interface function is disabled | (Initial value) |

| 1     | Smart card interface function is enabled  |                 |

- Notes: 1. The function for switching between LSB-first and MSB-first mode can also be used with the normal serial communication interface. Note that when the communication format data length is set to 7 bits and MSB-first mode is selected for the serial data to be transferred, bit 0 of TDR is not transmitted, and only bits 7 to 1 of the received data are valid.

- 2. The data logic level inversion function can also be used with the normal serial communication interface. Note that, when inverting the serial data to be transferred, parity transmission and parity checking is based on the number of high-level periods at the serial data I/O pin, and not on the register value.

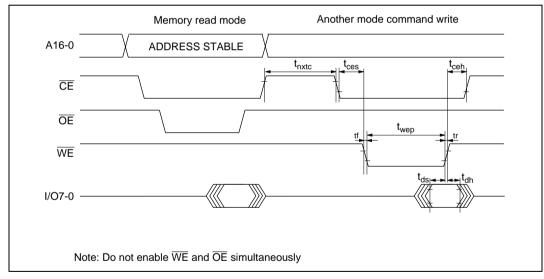

# Table 18.15 AC Characteristics in Transition from Memory Read Mode to Another Mode

| Item                | Symbol            | Min | Max | Unit | Notes |

|---------------------|-------------------|-----|-----|------|-------|

| Command write cycle | t <sub>nxtc</sub> | 20  | _   | μs   |       |

| CE hold time        | t <sub>ceh</sub>  | 0   | _   | ns   |       |

| CE setup time       | t <sub>ces</sub>  | 0   | _   | ns   |       |

| Data hold time      | t <sub>dh</sub>   | 50  | _   | ns   |       |

| Data setup time     | t <sub>ds</sub>   | 50  | _   | ns   |       |

| Write pulse width   | t <sub>wep</sub>  | 70  | _   | ns   |       |

| WE rise time        | t,                | _   | 30  | ns   |       |

| WE fall time        | t <sub>r</sub>    | _   | 30  | ns   |       |

(Conditions:  $V_{cc} = 5.0 \text{ V} \pm 10\%$ ,  $V_{ss} = 0 \text{ V}$ ,  $T_a = 25^{\circ}\text{C} \pm 5^{\circ}\text{C}$ )

Figure 18.19 Transition From Memory Read Mode to Another Mode

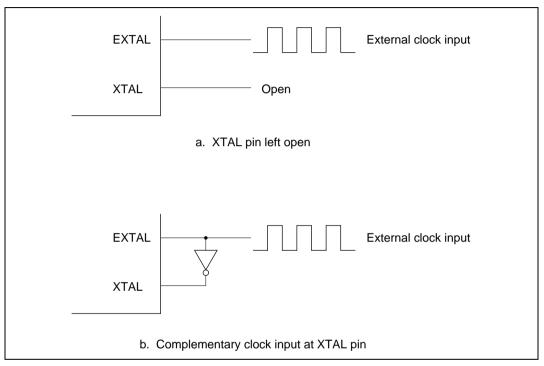

#### 19.2.2 External Clock Input

**Circuit Configuration:** An external clock signal can be input as shown in the examples in figure 19.5. If the XTAL pin is left open, the stray capacitance should not exceed 10 pF. If the stray capacitance at the XTAL pin exceeds 10 pF in configuration a, use configuration b instead and hold the clock high in standby mode.

Figure 19.5 External Clock Input (Examples)

#### Table 21.2 DC Characteristics (3)

Conditions:  $V_{cc} = 3.0$  to 5.5 V,  $AV_{cc} = 3.0$  to 5.5 V,  $V_{REF} = 3.0$  V to  $AV_{cc}^{*1}$ ,  $V_{ss} = AV_{ss} = 0$  V<sup>\*1</sup>,  $T_a = -20^{\circ}$ C to +75°C (regular specifications),  $T_a = -40^{\circ}$ C to +85°C (wide-range specifications)

| Item                                 |                                                                                                       | Symbol                                          | Min                                             | Тур | Мах                   | Unit        | Test Conditions                                                                                                              |

|--------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-----|-----------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| Schmitt<br>trigger input<br>voltages | Port A,<br>P8 <sub>0</sub> to P8 <sub>2</sub>                                                         | $V_{T}^{-}$ $V_{T}^{+}$ $V_{T}^{+} - V_{T}^{-}$ | $V_{cc} \times 0.2$<br><br>$V_{cc} \times 0.07$ |     | $V_{cc} \times 0.7$   | V<br>V<br>V |                                                                                                                              |

| Input high voltage                   | $\frac{\text{RES}}{\text{NMI}}, \frac{\text{STBY}}{\text{MD}_2} \text{ to}$ $\text{MD}_0$             | V <sub>IH</sub>                                 | $V_{cc} \times 0.9$                             |     | V <sub>cc</sub> + 0.3 | V           |                                                                                                                              |

|                                      | EXTAL                                                                                                 |                                                 | $V_{cc} 	imes 0.7$                              |     | V <sub>cc</sub> + 0.3 | V           | _                                                                                                                            |

|                                      | Port 7                                                                                                | -                                               | $V_{cc} 	imes 0.7$                              |     | $AV_{cc}$ + 0.3       | V           | _                                                                                                                            |

|                                      | Ports 1 to 6<br>P8 <sub>3</sub> , P8 <sub>4</sub> , P9 <sub>0</sub> to<br>P9 <sub>5</sub> , port B    | -                                               | $V_{cc} \times 0.7$                             |     | V <sub>cc</sub> + 0.3 | V           | _                                                                                                                            |

| Input low<br>voltage                 | $\overline{\text{RES}}, \overline{\text{STBY}}, \\ \text{MD}_2 \text{ to } \text{MD}_0$               | V                                               | -0.3                                            | —   | $V_{cc} 	imes 0.1$    | V           |                                                                                                                              |

|                                      | NMI, EXTAL,                                                                                           |                                                 | -0.3                                            | —   | $V_{cc} \times 0.2$   | V           | $V_{cc}$ < 4.0 V                                                                                                             |

|                                      | ports 1 to 7<br>P8 <sub>3</sub> , P8 <sub>4</sub> , P9 <sub>0</sub> to<br>P9 <sub>5</sub> , port B    |                                                 |                                                 |     | 0.8                   | V           | $V_{cc}$ = 4.0 to 5.5 V                                                                                                      |

| Output high                          | All output pins                                                                                       | V <sub>OH</sub>                                 | $V_{cc} - 0.5$                                  | —   | —                     | V           | I <sub>oH</sub> = -200 μA                                                                                                    |

| voltage                              | (except RESO)                                                                                         |                                                 | $V_{cc} - 1.0$                                  |     | _                     | V           | I <sub>он</sub> = —1 mA                                                                                                      |

| Output low voltage                   | All output pins (except RESO)                                                                         | V <sub>ol</sub>                                 | _                                               | —   | 0.4                   | V           | I <sub>oL</sub> = 1.6 mA                                                                                                     |

|                                      | Ports 1, 2,<br>and 5                                                                                  |                                                 | _                                               | _   | 1.0                   | V           | $I_{oL} = 5 \text{ mA}$<br>( $V_{cc} < 4.0 \text{ V}$ )<br>$I_{oL} = 10 \text{ mA}$<br>( $V_{cc} = 4.0 \text{ to}$<br>5.5 V) |

|                                      | RESO                                                                                                  |                                                 | _                                               | _   | 0.4                   | V           | I <sub>oL</sub> = 1.6 mA                                                                                                     |

| Input<br>leakage<br>current          | $\overline{\text{STBY}}, \overline{\text{RES}}, \\ \text{NMI}, \text{MD}_2 \text{ to} \\ \text{MD}_0$ | <sub>in</sub>                                   | _                                               | _   | 1.0                   | μA          | $V_{in} = 0.5 V$ to<br>$V_{cc} - 0.5 V$                                                                                      |

|                                      | Port 7                                                                                                |                                                 | —                                               | —   | 1.0                   | μA          | $V_{in} = 0.5 \text{ V to}$<br>AV <sub>cc</sub> - 0.5 V                                                                      |

## RENESAS

#### **Condition Code Notation**

| Symbol     | Description                                        |

|------------|----------------------------------------------------|

| $\uparrow$ | Changed according to execution result              |

| *          | Undetermined (no guaranteed value)                 |

| 0          | Cleared to 0                                       |

| 1          | Set to 1                                           |

| _          | Not affected by execution of the instruction       |

| Δ          | Varies depending on conditions, described in notes |

| DRCRB—DRAM Contr | ol Regi | ister B |         |                          |                        |                         | H'EE         | 027                                          | DRAM interface |

|------------------|---------|---------|---------|--------------------------|------------------------|-------------------------|--------------|----------------------------------------------|----------------|

| Bit              | 7       | 6       | 5       | 4                        | 3                      | 2                       | 1            | 0                                            |                |

|                  | MXC1    | MXC0    | CSEL    | RCYCE                    |                        | TPC                     | RCW          | RLW                                          |                |

| Initial value    | 0       | 0       | 0       | 0                        | 1                      | 0                       | 0            | 0                                            |                |

| Read/Write       | R/W     | R/W     | R/W     | R/W                      | —                      | R/W                     | R/W          | R/W                                          |                |

|                  | Тг      |         |         |                          |                        | T                       |              |                                              |                |

|                  |         |         |         |                          |                        |                         |              |                                              |                |

|                  |         |         |         |                          |                        |                         |              |                                              |                |

|                  |         |         |         |                          |                        |                         |              |                                              |                |

|                  |         |         | -       | Refresh cy               |                        |                         |              |                                              | 7              |

|                  |         |         |         |                          |                        |                         | rtion is dis | sabled                                       | _              |

|                  |         |         |         | 1 1 wa                   | it state               | (T <sub>RW</sub> ) is i | nserted      |                                              |                |

|                  |         |         | RA      | S-CAS wa                 | it                     |                         |              |                                              |                |

|                  |         |         | 0       | Wait sta                 | ate (T <sub>rw</sub> ) | insertior               | n is disabl  | ed                                           |                |

|                  |         |         | 1       | 1 wait s                 | tate (T                | ,) is inse              | rted         |                                              |                |

|                  |         | TF      | o cycle | control                  |                        |                         |              |                                              |                |

|                  |         |         | -       | ate precha               | irge cyc               | le is inse              | rted         |                                              |                |

|                  |         |         |         | ate precha               |                        |                         |              |                                              |                |

|                  |         | Refree  |         | enable                   | 0 ,                    |                         |              |                                              |                |

|                  |         |         | -       | cycles are               | disable                | əd                      |              |                                              |                |

|                  |         |         |         | efresh cyc               |                        |                         |              |                                              |                |

|                  |         |         |         |                          |                        |                         |              |                                              |                |

|                  |         |         | -       | 5 selected               |                        | E and I                 |              | ut pipo                                      |                |

|                  |         |         |         | VR selected              |                        |                         |              |                                              |                |

|                  |         |         |         | In selecte               |                        | AS anu                  |              |                                              |                |

|                  |         |         | and 0   |                          |                        | Deceri                  | tion         |                                              |                |

|                  | MXC1    | MXC0    | 0.1     |                          | 0.1.1.                 | Descrip                 | Juon         |                                              |                |

|                  | 0       | 0       |         | nn address<br>ared addre |                        |                         |              |                                              |                |

|                  |         |         |         | es 1, 2                  |                        | t access                | space        | A <sub>19</sub> to                           | A。             |

|                  |         |         |         |                          |                        | bit acces               |              | A <sub>19</sub> to                           |                |

|                  |         |         | Mod     | es 3, 4, 5               | 8-bi                   | t access                | space        | A <sub>23</sub> to                           | A <sub>8</sub> |

|                  |         |         |         |                          | 16-l                   | oit acces               | s space      | A <sub>23</sub> to                           | A <sub>9</sub> |

|                  |         | 1       |         | nn address               |                        |                         |              |                                              |                |

|                  |         |         |         | ared addre               |                        | taccocc                 | 60202        | A to                                         | ٨              |

|                  |         |         |         | es 1, 2                  |                        | t access<br>bit access  | •            | A <sub>19</sub> to A                         |                |

|                  |         |         | Mod     | es 3, 4, 5               |                        | t access                |              | A <sub>23</sub> to .                         |                |

|                  |         |         |         |                          |                        | oit acces               |              | A <sub>23</sub> to .                         |                |

|                  | 1       | 0       | Colum   | nn address               | : 10 bits              | 6                       |              |                                              |                |

|                  |         |         |         | ared addre               |                        |                         |              |                                              |                |

|                  |         |         | Mod     | es 1, 2                  |                        | t access                |              | A <sub>19</sub> to                           |                |

|                  |         |         | Mod     | es 3, 4, 5               |                        | bit access<br>t access  | •            | A <sub>19</sub> to .<br>A <sub>23</sub> to . |                |

|                  |         |         |         | , ., 0                   |                        | bit acces               |              | A <sub>23</sub> to .                         |                |

|                  |         | 1       | Illegal | setting                  |                        |                         |              | 20                                           |                |

|                  | L       |         |         | 0                        |                        |                         |              |                                              |                |

Figure C.6 (f) Port 6 Block Diagram (Pins P6<sub>5</sub> and P6<sub>6</sub>)