Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 13MHz                                                                          |

| Connectivity               | SCI, SmartCard                                                                 |

| Peripherals                | DMA, PWM, WDT                                                                  |

| Number of I/O              | 70                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-BFQFP                                                                      |

| Supplier Device Package    | 100-QFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3067rvfi13v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

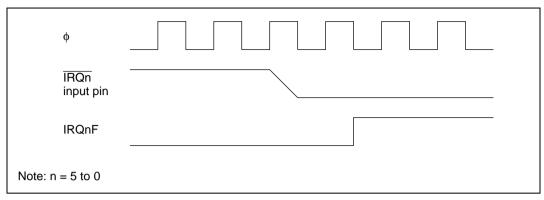

Figure 5.3 shows the timing of the setting of the interrupt flags (IRQnF).

Figure 5.3 Timing of Setting of IRQnF

Interrupts  $IRQ_0$  to  $IRQ_5$  have vector numbers 12 to 17. These interrupts are detected regardless of whether the corresponding pin is set for input or output. When using a pin for external interrupt input, clear its DDR bit to 0 and do not use the pin for chip select output, refresh output, SCI input/output, or A/D external trigger input.

### 5.3.2 Internal Interrupts

Thirty-Six internal interrupts are requested from the on-chip supporting modules.

- Each on-chip supporting module has status flags for indicating interrupt status, and enable bits for enabling or disabling interrupts.

- Interrupt priority levels can be assigned in IPRA and IPRB.

- 16-bit timer, SCI, and A/D converter interrupt requests can activate the DMAC, in which case no interrupt request is sent to the interrupt controller, and the I and UI bits are disregarded.

### 5.3.3 Interrupt Vector Table

Table 5.3 lists the interrupt sources, their vector addresses, and their default priority order. In the default priority order, smaller vector numbers have higher priority. The priority of interrupts other than NMI can be changed in IPRA and IPRB. The priority order after a reset is the default order shown in table 5.3.

# 5.5 Usage Notes

### 5.5.1 Contention between Interrupt and Interrupt-Disabling Instruction

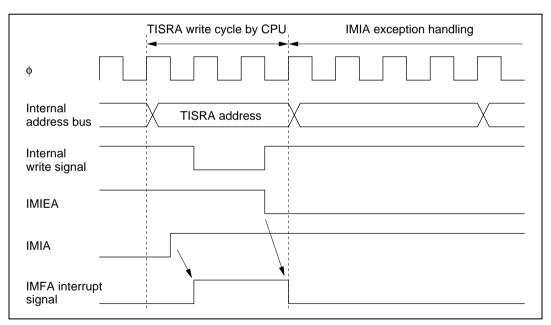

When an instruction clears an interrupt enable bit to 0 to disable the interrupt, the interrupt is not disabled until after execution of the instruction is completed. If an interrupt occurs while a BCLR, MOV, or other instruction is being executed to clear its interrupt enable bit to 0, at the instant when execution of the instruction ends the interrupt is still enabled, so its interrupt exception handling is carried out. If a higher-priority interrupt is also requested, however, interrupt exception handling for the higher-priority interrupt is carried out, and the lower-priority interrupt is ignored. This also applies to the clearing of an interrupt flag to 0.

Figure 5.8 shows an example in which an IMIEA bit is cleared to 0 in the 16-bit timer's TISRA register.

Figure 5.8 Contention between Interrupt and Interrupt-Disabling Instruction

This type of contention will not occur if the interrupt is masked when the interrupt enable bit or flag is cleared to 0.

### 6.2.9 Refresh Timer Control/Status Register (RTMCSR)

| Bit           | 7     | 6    | 5    | 4    | 3    | 2 | 1 | 0 |

|---------------|-------|------|------|------|------|---|---|---|

|               | CMF   | CMIE | CKS2 | CKS1 | CKS0 | — | — | _ |

| Initial value | 0     | 0    | 0    | 0    | 0    | 1 | 1 | 1 |

| Read/Write    | R(W)* | R/W  | R/W  | R/W  | R/W  | _ | _ | _ |

RTMCSR is an 8-bit readable/writable register that selects the refresh timer counter clock. When the refresh timer is used as an interval timer, RTMCSR also enables or disables interrupt requests. Bits 7 and 6 of RTMCSR are initialized to 0 by a reset and in the standby modes. Bits 5 to 3 are initialized to 0 by a reset and in hardware standby mode; they are not initialized in software standby mode.

Note: Only 0 can be written to clear the flag.

**Bit 7—Compare Match Flag (CMF):** Status flag that indicates a match between the values of RTCNT and RTCOR.

| Bit 7<br>CMF | Description                                                                                                     |                 |

|--------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| 0            | Clearing conditions<br>When the chip is reset and in standby mode<br>Read CMF when CMF = 1, then write 0 in CMF | (Initial value) |

| 1            | Setting condition<br>When RTCNT = RTCOR                                                                         |                 |

**Bit 6—Compare Match Interrupt Enable (CMIE):** Enables or disables the CMI interrupt requested when the CMF flag is set to 1 in RTMCSR. The CMIE bit is always cleared to 0 when any of areas 2 to 5 is designated as DRAM space.

| Bit 6<br>CMIE | Description                                    |                 |

|---------------|------------------------------------------------|-----------------|

| 0             | The CMI interrupt requested by CMF is disabled | (Initial value) |

| 1             | The CMI interrupt requested by CMF is enabled  |                 |

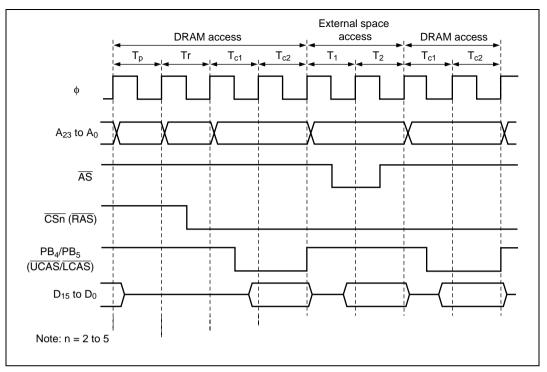

Figure 6.23 Example of Operation Timing in RAS Down Mode (CSEL = 0)

When RAS down mode is selected, the conditions for an asserted  $\overline{RAS}n$  signal to return to the high level are as shown below. The timing in these cases is shown in figure 6.24.

- When DRAM space with a different row address is accessed

- Immediately before a CAS-before-RAS refresh cycle

- When the BE bit or RDM bit is cleared to 0 in DRCRA

- Immediately before release of the external bus

### 6.6 Interval Timer

### 6.6.1 Operation

When DRAM is not connected to the H8/3067 Group chip, the refresh timer can be used as an interval timer by clearing bits DRAS2 to DRAS0 in DRCRA to 0. After setting RTCOR, selection a clock source with bits CKS2 to CKS0 in RTMCSR, and set the CMIE bit to 1.

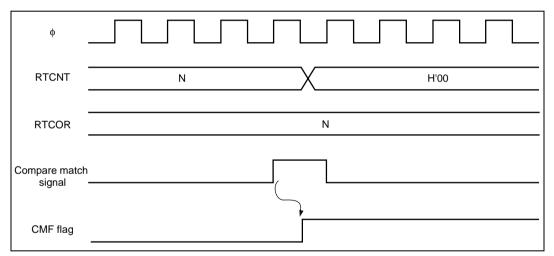

**Timing of Setting of Compare Match Flag and Clearing by Compare Match:** The CMF flag in RTMCSR is set to 1 by a compare match output when the RTCOR and RTCNT values match. The compare match signal is generated in the last state in which the values match (when RTCNT is updated from the matching value to a new value). Accordingly, when RTCNT and RTCOR match, the compare match signal is not generated until the next counter clock pulse. Figure 6.38 shows the timing.

Figure 6.38 Timing of CMF Flag Setting

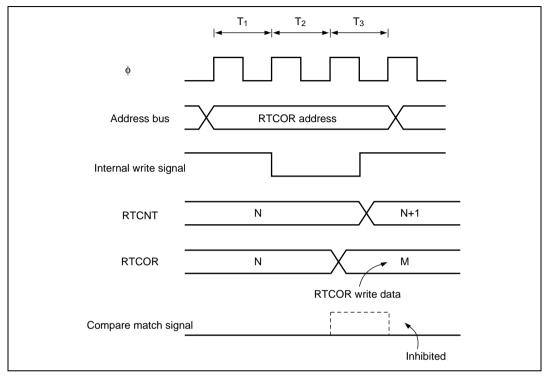

**Contention between RTCOR Write and Compare Match:** If a compare match occurs in the  $T_3$  state of an RTCOR write cycle, writing takes priority and the compare match signal is inhibited. See Figure 6.41.

Figure 6.41 Contention between RTCOR Write and Compare Match

**RTCNT Operation at Internal Clock Source Switchover:** Switching internal clock sources may cause RTCNT to increment, depending on the switchover timing. Table 6.10 shows the relation between the time of the switchover (by writing to bits CKS2 to CKS0) and the operation of RTCNT.

The RTCNT input clock is generated from the internal clock source by detecting the falling edge of the internal clock. If a switchover is made from a high clock source to a low clock source, as in case No. 3 in table 6.10, the switchover will be regarded as a falling edge, an RTCNT clock pulse will be generated, and RTCNT will be incremented.

**DMAC:** When the DMAC receives an activation request, it requests the bus right from the bus arbiter. If the DMAC is bus master and the DRAM interface or an external bus master requests the bus, the bus arbiter transfers the bus right from the DMAC to the bus master that requested the bus. The bus right is transferred at the following times.

The bus right is transferred when the DMAC finishes transferring one byte or one word. A DMAC transfer cycle consists of a read cycle and a write cycle. The bus right is not transferred between the read cycle and the write cycle.

There is a priority order among the DMAC channels. For details see section 7.4.9, Multiple-Channel Operation.

**DRAM Interface:** The DRAM interface requests the bus right from the bus arbiter when a refresh cycle request is issued, and releases the bus at the end of the refresh cycle. For details see section 6.5, DRAM Interface.

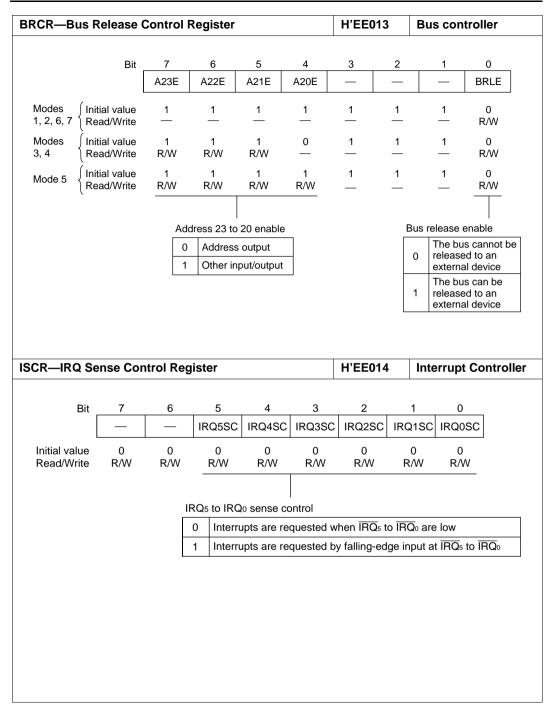

**External Bus Master:** When the BRLE bit is set to 1 in BRCR, the bus can be released to an external bus master. The external bus master has highest priority, and requests the bus right from the bus arbiter y driving the  $\overline{BREQ}$  signal low. Once the external bus master acquires the bus, it keeps the bus until the  $\overline{BREQ}$  signal goes high. While the bus is released to an external bus master, the H8/3067 Group chip holds the address bus, data bus, bus control signals ( $\overline{AS}$ ,  $\overline{RD}$ ,  $\overline{HWR}$ , and  $\overline{LWR}$ ), and chip select signals ( $\overline{CSn}$ : n = 7 to 0) in the high-impedance state, and holds the  $\overline{BACK}$  pin in the low output state.

The bus arbiter samples the  $\overline{BREQ}$  pin at the rise of the system clock ( $\phi$ ). If  $\overline{BREQ}$  is low, the bus is released to the external bus master at the appropriate opportunity. The  $\overline{BREQ}$  signal should be held low until the  $\overline{BACK}$  signal goes low.

When the  $\overline{BREQ}$  pin is high in two consecutive samples, the  $\overline{BACK}$  pin is driven high to end the bus-release cycle.

Figure 6.48 shows the timing when the bus right is requested by an external bus master during a read cycle in a two-state access area. There is a minimum interval of three states from when the BREQ signal goes low until the bus is released.

### 7.1.3 Functional Overview

Table 7.1 gives an overview of the DMAC functions.

### Table 7.1DMAC Functional Overview

|                          |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                | Address Reg. Length |             |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|--|

| Transfer                 | Mode                                                                                                                                                                                                                                                                                                                                                                                 | Activation                                                                                                                                                                                     | Source              | Destination |  |

| Short<br>address<br>mode | <ul> <li>I/O mode</li> <li>Transfers one byte or one word<br/>per request</li> <li>Increments or decrements the memory<br/>address by 1 or 2</li> <li>Executes 1 to 65,536 transfers</li> </ul>                                                                                                                                                                                      | <ul> <li>Compare match/input<br/>capture A interrupts from<br/>16-bit timer channels 0 to<br/>2</li> <li>Transmit-data-empty<br/>interrupt from SCI channel<br/>0</li> </ul>                   | 24                  | 8           |  |

|                          | <ul> <li>Idle mode</li> <li>Transfers one byte or one word per request</li> <li>Holds the memory address fixed</li> </ul>                                                                                                                                                                                                                                                            | <ul> <li>Conversion-end interrupt<br/>from A/D converter</li> <li>Receive-data-full interrupt<br/>from SCI channel 0</li> </ul>                                                                | 8                   | 24          |  |

|                          | <ul> <li>Executes 1 to 65,536 transfers<br/>Repeat mode</li> <li>Transfers one byte or one word per<br/>request</li> <li>Increments or decrements the memory<br/>address by 1 or 2</li> <li>Executes a specified number (1 to 255)<br/>of transfers, then returns to the initial<br/>state and continues</li> </ul>                                                                  | External request                                                                                                                                                                               | 24                  | 8           |  |

| Full<br>address<br>mode  | <ul> <li>Normal mode</li> <li>Auto-request <ul> <li>Retains the transfer request internally</li> <li>Executes a specified number(1 to 65,536) of transfers continuously</li> <li>Selection of burst mode or cyclesteal mode</li> </ul> </li> <li>External request <ul> <li>Transfers one byte or one word per request</li> <li>Executes 1 to 65,536 transfers</li> </ul> </li> </ul> | <ul> <li>Auto-request</li> <li>External request</li> </ul>                                                                                                                                     | 24                  | 24          |  |

|                          | <ul> <li>Block transfer</li> <li>Transfers one block of a specified size per request</li> <li>Executes 1 to 65,536 transfers</li> <li>Allows either the source or destination to be a fixed block area</li> <li>Block size can be 1 to 255 bytes or words</li> </ul>                                                                                                                 | <ul> <li>Compare match/ input<br/>capture A interrupts from<br/>16-bit timer channels 0 to<br/>2</li> <li>External request</li> <li>Conversion-end interrupt<br/>from A/D converter</li> </ul> | 24                  | 24          |  |

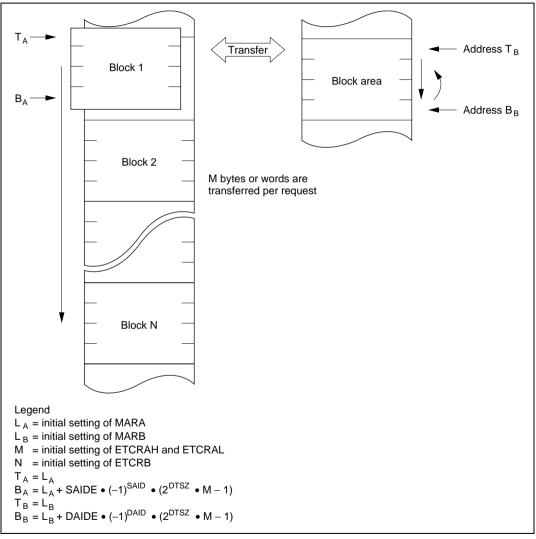

If M (1 to 255) is the size of the block transferred at each request and N (1 to 65,536) is the number of blocks to be transferred, then ETCRAH and ETCRAL should initially be set to M and ETCRB should initially be set to N.

Figure 7.10 illustrates how block transfer mode operates. In this figure, bit TMS is cleared to 0, meaning the block area is the destination.

#### Figure 7.10 Operation in Block Transfer Mode

Rev. 4.00 Jan 26, 2006 page 244 of 938 REJ09B0276-0400

executed. If level sensing is selected, the transfer continues while  $\overline{\text{DREQ}}$  is low, until the transfer is completed. The bus is released temporarily after each byte or word has been transferred, however. If the  $\overline{\text{DREQ}}$  input goes high during a transfer, the transfer is suspended after the current byte or word has been transferred. When  $\overline{\text{DREQ}}$  goes low, the request is held internally until one byte or word has been transferred. The TEND signal goes low during the last write cycle.

In block transfer mode, an external request operates as follows. Only edge-sensitive transfer requests are possible in block transfer mode. Each time a high-to-low transition of the  $\overline{DREQ}$  input is detected, a block of the specified size is transferred. The  $\overline{TEND}$  signal goes low during the last write cycle in each block.

Activation by Auto-Request: The transfer starts as soon as enabled by register setup, and continues until completed. Cycle-steal mode or burst mode can be selected.

In cycle-steal mode the DMAC releases the bus temporarily after transferring each byte or word. Normally, DMAC cycles alternate with CPU cycles.

In burst mode the DMAC keeps the bus until the transfer is completed, unless there is a higherpriority bus request. If there is a higher-priority bus request, the bus is released after the current byte or word has been transferred.

### 13.1.3 Input/Output Pins

The SCI has serial pins for each channel as listed in table 13.1.

### Table 13.1 SCI Pins

| Channel | Name              | Abbreviation     | I/O          | Function                              |

|---------|-------------------|------------------|--------------|---------------------------------------|

| 0       | Serial clock pin  | SCK              | Input/output | SCI <sub>0</sub> clock input/output   |

|         | Receive data pin  | RxD <sub>0</sub> | Input        | SCI <sub>0</sub> receive data input   |

|         | Transmit data pin | TxD <sub>0</sub> | Output       | SCI <sub>0</sub> transmit data output |

| 1       | Serial clock pin  | SCK              | Input/output | SCI <sub>1</sub> clock input/output   |

|         | Receive data pin  | RxD <sub>1</sub> | Input        | SCI, receive data input               |

|         | Transmit data pin | TxD <sub>1</sub> | Output       | SCI, transmit data output             |

| 2       | Serial clock pin  | SCK <sub>2</sub> | Input/output | SCI <sub>2</sub> clock input/output   |

|         | Receive data pin  | RxD <sub>2</sub> | Input        | SCI <sub>2</sub> receive data input   |

|         | Transmit data pin | TxD <sub>2</sub> | Output       | SCI <sub>2</sub> transmit data output |

#### **Transmitting and Receiving Data:**

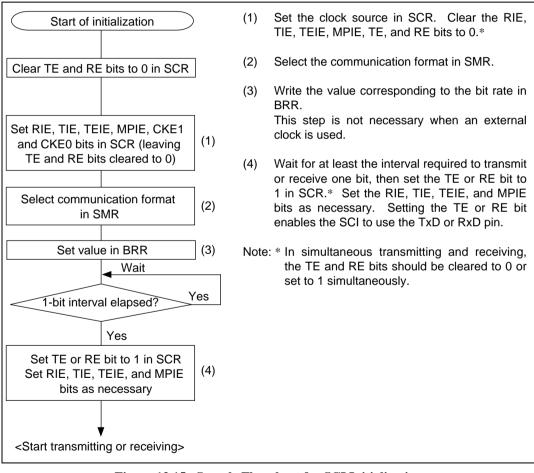

• SCI Initialization (Synchronous Mode): Before transmitting or receiving data, clear the TE and RE bits to 0 in SCR, then initialize the SCI as follows.

When changing the communication mode or format, always clear the TE and RE bits to 0 before following the procedure given below. Clearing TE to 0 sets the TDRE flag to 1 and initializes TSR. Note that clearing RE to 0, however, does not initialize the RDRF, PER, and ORE flags, or RDR, which retain their previous contents.

Figure 13.15 shows a sample flowchart for initializing the SCI.

Figure 13.15 Sample Flowchart for SCI Initialization

the receiving device places the signal line in the high-impedance state again. The signal line is pulled high again by a pull-up resistor.

5. If the transmitting device does not receive an error signal, it proceeds to transmit the next data frame. If it receives an error signal, however, it returns to step 2 and transmits the same data again.

#### 14.3.4 Register Settings

Table 14.3 shows a bit map of the registers used in the smart card interface. Bits indicated as 0 or 1 must be set to the value shown. The setting of other bits is described in this section.

|          |           | Bit   |       |       |       |       |       |        |       |

|----------|-----------|-------|-------|-------|-------|-------|-------|--------|-------|

| Register | Address*1 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

| SMR      | H'FFFB0   | GM    | 0     | 1     | O/E   | 1     | 0     | CKS1   | CKS0  |

| BRR      | H'FFFB1   | BRR7  | BRR6  | BRR5  | BRR4  | BRR3  | BRR2  | BRR1   | BRR0  |

| SCR      | H'FFFB2   | TIE   | RIE   | TE    | RE    | 0     | 0     | CKE1*2 | CKE0  |

| TDR      | H'FFFB3   | TDR7  | TDR6  | TDR5  | TDR4  | TDR3  | TDR2  | TDR1   | TDR0  |

| SSR      | H'FFFB4   | TDRE  | RDRF  | ORER  | ERS   | PER   | TEND  | 0      | 0     |

| RDR      | H'FFFB5   | RDR7  | RDR6  | RDR5  | RDR4  | RDR3  | RDR2  | RDR1   | RDR0  |

| SCMR     | H'FFFB6   | _     | _     | _     | _     | SDIR  | SINV  | _      | SMIF  |

Table 14.3

Smart Card Interface Register Settings

Notes: — Unused bit.

1. Lower 20 bits of the address in advanced mode.

2. When GM is cleared to 0 in SMR, the CKE1 bit must also be cleared to 0.

Serial Mode Register (SMR) Settings: Clear the GM bit to 0 when using the normal smart card interface mode, or set to 1 when using GSM mode. Clear the  $O/\overline{E}$  bit to 0 if the smart card is of the direct convention type, or set to 1 if of the inverse convention type.

Bits CKS1 and CKS0 select the clock source of the built-in baud rate generator. See section 14.3.5, Clock.

**Bit Rate Register (BRR) Settings:** BRR is used to set the bit rate. See section 14.3.5, Clock, for the method of calculating the value to be set.

**Serial Control Register (SCR) Settings:** The TIE, RIE, TE, and RE bits have their normal serial communication functions. See section 13, Serial Communication Interface, for details. The CKE1 and CKE0 bits specify clock output. To disable clock output, clear these bits to 00; to enable clock

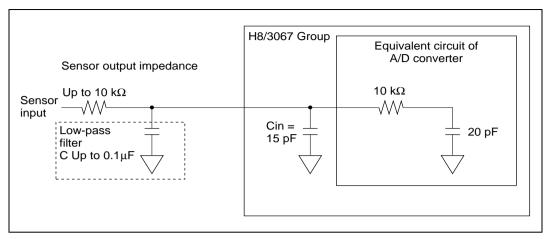

If a filter circuit is used, be careful of interference with digital signals on the same board, and make sure the circuit does not act as an antenna.

Figure 15.11 Analog Input Circuit (Example)

### Notes on use of the RAM emulation function

(1) Notes on flash write enable (FWE) high/low

Care is necessary to prevent erroneous programming/erasing at FWE=high/low, the same as in the on-board programming mode. To prevent erroneous programming and erasing due to program runaway, etc., during FWE application, in particular, the watchdog timer should be set when the PSU, P, ESU, or E bit is set to 1 in FLMCR, even while the emulation function is being used. For more information, see section 18.9, Notes on Flash Memory Programming/Erasing.

(2) NMI input disable conditions

When the P and E bits in FLMCR are set, NMI input is disabled, the same as normal program/erase even when using the emulation function.

NMI input is cleared when the P and E bits are reset (including watchdog timer reset), in the standby mode, when a high level is not applied to FWE, and when the SWE bit in FLMCR is 0 in state in which a high level is input to FWE.

### 20.4.6 Cautions on Clearing the Software Standby Mode of F-ZTAT Version

(1) Operation phenomena

When using operating mode 5, 6, or 7\* (on-chip flash memory enabled), the first read of onchip flash memory after exiting software standby mode may not be carried out correctly. Software standby mode is exited by means of an external interrupt (via the NMI,  $\overline{IRQ}_0$ ,  $\overline{IRQ}_1$ , or  $\overline{IRQ}_2$  pin), the  $\overline{RES}$  pin, or the  $\overline{STBY}$  pin. In the case of an external interrupt via the NMI,  $\overline{IRQ}_0$ ,  $\overline{IRQ}_1$ , or  $\overline{IRQ}_2$  pin, the first read after exiting software standby mode is a read of the vector corresponding to the respective exception handling interrupt source. This vector may not be read correctly, resulting in program runaway.

Note: \* Mode 5: expanded 16-Mbyte mode with on-chip ROM enabled

Mode 6: single-chip normal mode

Mode 7: single-chip advanced mode

(2) Exemplary procedures to avoid program runaway

This operation phenomenon can be avoided by writing or amending program code in accordance with the following procedures.

- (a) When using mode 5 or mode 7, assign addresses in the 64-kbyte space from H'00000 to H'0FFFF as the vector addresses for the external interrupts that clear software standby mode.

- (b) When using mode 6, change the mode to mode 7 in the program, and use change (a) above. Note that it is necessary to change vector address assignments and to extend addresses as follows.

- Addresses H'DFFF and below (on-chip ROM area): H'xxxx  $\rightarrow$  H'0xxxx

- Addresses H'E000 to H'E0FF (internal I/O registers-1): H'yyyy  $\rightarrow$  H'Eyyyy

- Addresses H'EF20 and above (on-chip RAM area and internal I/O registers-2): H'zzzz  $\rightarrow$  H'Fzzzz

(Where x, y and z are any hexadecimal numbers)

With the production lots prior to the week code "9K1" of the HD64F3067 and HD64F3067R, avoid program runaway according to the procedures designated above. Meanwhile, as for the production lots of the week code "9K1" and after, the special constraint according to of the aforementioned Section (2) is not applicable.

| FLMSR-Fla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FLMSR-Flash Memory Status Register |          |           |         |        |                                                                    |         | Flas | Flash Memory                |     |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|-----------|---------|--------|--------------------------------------------------------------------|---------|------|-----------------------------|-----|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |          |           |         |        |                                                                    |         |      |                             |     |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                  |          | 6         | 5       | 4      | 3                                                                  | 2       | 1    | 0                           |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FL                                 | ER       |           |         |        |                                                                    | —       |      | —                           |     |  |

| Initial value<br>R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C<br>F                             |          | 1         | 1       | 1      | 1                                                                  | 1       | 1    | 1                           |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |          |           |         | R      | eserved l                                                          | bits    |      |                             |     |  |

| F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RAM se                             | elect, R | AM2, RA   | M1      |        |                                                                    |         |      |                             |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit 7                              |          |           |         | -<br>- |                                                                    |         |      |                             |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FLER                               |          |           |         | L      | escription                                                         |         |      |                             |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                  | [Clea    | ring conc | lition] | •      | ction (error                                                       | . ,     |      | d (Initial value)           | )   |  |

| <ol> <li>An error has occurred during flash memory programming/erasing, and err<br/>tection*1 is enabled<br/>[Setting conditions]</li> <li>Flash memory was read*2 while being programmed or erased (includin<br/>or instruction fetch, but not including reading of a RAM area overlappe<br/>flash memory).</li> <li>A hardware exception-handling sequence (other than a reset, invalid in<br/>trap instruction, or zero-divide exception) was executed just before pro<br/>or erasing.*3</li> <li>The SLEEP instruction (including software standby mode) was execut<br/>programming or erasing.</li> </ol> |                                    |          |           |         |        | cluding vector<br>lapped onto<br>alid instruction<br>re programmin | i,<br>g |      |                             |     |  |

| Notes 1. See 18.6.3, Error Protection, for details.<br>2. The read value in this case is undefined.<br>3. Before stack and vector read by exception handling.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |          |           |         |        |                                                                    |         |      |                             |     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    | onding   |           |         |        |                                                                    |         |      | Reading the es to this addr | ess |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |          |           |         |        |                                                                    |         |      |                             |     |  |

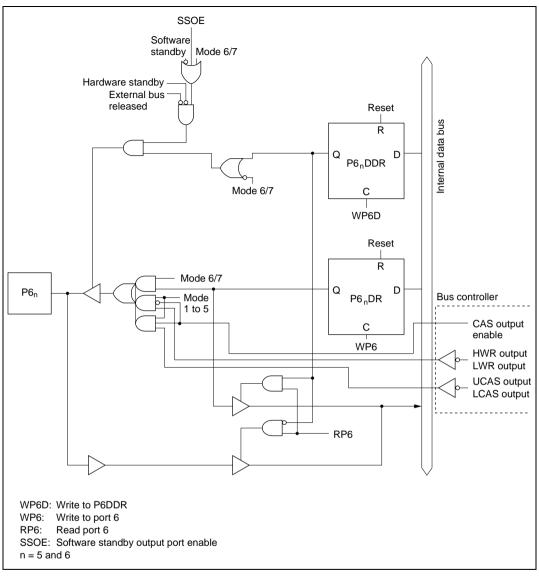

Figure C.6 (f) Port 6 Block Diagram (Pins P6<sub>5</sub> and P6<sub>6</sub>)

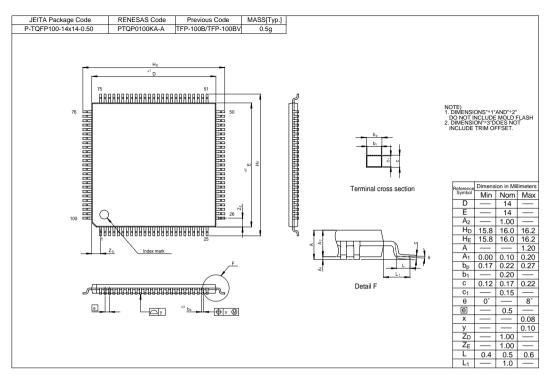

Figure G.2 Package Dimensions (PTQP0100KA-A)