#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 13MHz                                                                         |

| Connectivity               | SCI, SmartCard                                                                |

| Peripherals                | DMA, PWM, WDT                                                                 |

| Number of I/O              | 70                                                                            |

| Program Memory Size        | 128KB (128K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-QFP                                                                       |

| Supplier Device Package    | -                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3067rvx13v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Secti | on 1    | Overview                                      | 1    |

|-------|---------|-----------------------------------------------|------|

| 1.1   | Overvi  | ew                                            | 1    |

| 1.2   | Block   | Diagram                                       | 7    |

| 1.3   | Pin De  | scription                                     | 8    |

|       | 1.3.1   | Pin Arrangement                               | 8    |

|       | 1.3.2   | Pin Functions                                 | 10   |

|       | 1.3.3   | Pin Assignments in Each Mode                  | 16   |

| 1.4   | Notes   | on Flash Memory R Version Model               | 21   |

|       | 1.4.1   | Pin Arrangement                               | 21   |

|       | 1.4.2   | Differences in Flash Memory R Version         | 21   |

| Secti | on 2    | CPU                                           | 23   |

| 2.1   |         | ew                                            | 23   |

|       | 2.1.1   | Features                                      | 23   |

|       | 2.1.2   | Differences from H8/300 CPU                   | 24   |

| 2.2   | CPU C   | perating Modes                                | 25   |

| 2.3   |         | ss Space                                      | 26   |

| 2.4   |         | er Configuration                              | 27   |

|       | 2.4.1   | Overview                                      | 27   |

|       | 2.4.2   | General Registers                             | 28   |

|       | 2.4.3   | Control Registers                             | 29   |

|       | 2.4.4   | Initial CPU Register Values                   | 30   |

| 2.5   | Data F  | ormats                                        | 31   |

|       | 2.5.1   | General Register Data Formats                 | 31   |

|       | 2.5.2   | Memory Data Formats                           | 32   |

| 2.6   | Instruc | tion Set                                      | 34   |

|       | 2.6.1   | Instruction Set Overview                      | 34   |

|       | 2.6.2   | Instructions and Addressing Modes             | 35   |

|       | 2.6.3   | Tables of Instructions Classified by Function | 36   |

|       | 2.6.4   | Basic Instruction Formats                     | 45   |

|       | 2.6.5   | Notes on Use of Bit Manipulation Instructions | 46   |

| 2.7   | Addres  | ssing Modes and Effective Address Calculation | 48   |

|       | 2.7.1   | Addressing Modes                              | 48   |

|       | 2.7.2   | Effective Address Calculation                 | 50   |

| 2.8   | Proces  | sing States                                   | 54   |

|       | 2.8.1   | Overview                                      | 54   |

|       | 2.8.2   | Program Execution State                       | 55   |

|       | 2.8.3   | Exception-Handling State                      | 55   |

|       |         | Rev. 4.00 Jan 26, 2006 page vii of            | xxii |

16 bits.  $A_{23}$  to  $A_{21}$  are valid when 0 is written in bits 7 to 5 of the bus release control register (BRCR). (In this mode  $A_{20}$  is always used for address output.)

### 3.4.4 Mode 4

Ports 1, 2, and 5 and part of port A function as address pins  $A_{23}$  to  $A_0$ , permitting access to a maximum 16-Mbyte address space. The initial bus mode after a reset is 16 bits, with 16-bit access to all areas. If all areas are designated for 8-bit access in ABWCR, the bus mode switches to 8 bits.  $A_{23}$  to  $A_{21}$  are valid when 0 is written in bits 7 to 5 of BRCR. (In this mode  $A_{20}$  is always used for address output.)

### 3.4.5 Mode 5

Ports 1, 2, and 5 and part of port A can function as address pins  $A_{23}$  to  $A_0$ , permitting access to a maximum 16-Mbyte address space, but following a reset they are input ports. To use ports 1, 2, and 5 as an address bus, the corresponding bits in their data direction registers (P1DDR, P2DDR, and P5DDR) must be set to 1. For  $A_{23}$  to  $A_{20}$  output, write 0 in bits 7 to 4 of BRCR. The initial bus mode after a reset is 8 bits, with 8-bit access to all areas. If at least one area is designated for 16-bit access in ABWCR, the bus mode switches to 16 bits.

#### 3.4.6 Mode 6

This mode operates using the on-chip ROM, RAM, and registers. All I/O ports are available. Mode 6 supports a maximum address space of 64 kbytes.

#### 3.4.7 Mode 7

This mode operates using the on-chip ROM, RAM, and registers. All I/O ports are available. Mode 7 supports a 1-Mbyte address space.

#### 5.1.3 **Pin Configuration**

Table 5.1 lists the interrupt pins.

#### Table 5.1Interrupt Pins

| Name                              | Abbreviation                                   | I/O   | Function                                                       |

|-----------------------------------|------------------------------------------------|-------|----------------------------------------------------------------|

| Nonmaskable interrupt             | NMI                                            | Input | Nonmaskable interrupt*, rising edge or falling edge selectable |

| External interrupt request 5 to 0 | $\overline{IRQ}_{_5}$ to $\overline{IRQ}_{_0}$ | Input | Maskable interrupts, falling edge or level sensing selectable  |

Note: \* In the flash memory and flash memory R versions, NMI input is sometimes disabled. For details see 18.6.4, NMI Input Disable Conditions.

#### 5.1.4 Register Configuration

Table 5.2 lists the registers of the interrupt controller.

#### Table 5.2 Interrupt Controller Registers

| Address <sup>*1</sup> | Name                          | Abbreviation | R/W     | Initial Value |

|-----------------------|-------------------------------|--------------|---------|---------------|

| H'EE012               | System control register       | SYSCR        | R/W     | H'09          |

| H'EE014               | IRQ sense control register    | ISCR         | R/W     | H'00          |

| H'EE015               | IRQ enable register           | IER          | R/W     | H'00          |

| H'EE016               | IRQ status register           | ISR          | R/(W)*2 | H'00          |

| H'EE018               | Interrupt priority register A | IPRA         | R/W     | H'00          |

| H'EE019               | Interrupt priority register B | IPRB         | R/W     | H'00          |

Notes: 1. Lower 20 bits of the address in advanced mode.

2. Only 0 can be written, to clear flags.

If a DRAM read/write cycle is followed by an access cycle for an external area other than DRAM space when  $\overline{HWR}$  and  $\overline{LWR}$  are selected as the  $\overline{UCAS}$  and  $\overline{LCAS}$  output pins, an idle cycle (Ti) is inserted unconditionally immediately after the DRAM access cycle. See section 6.9, Idle Cycle, for details.

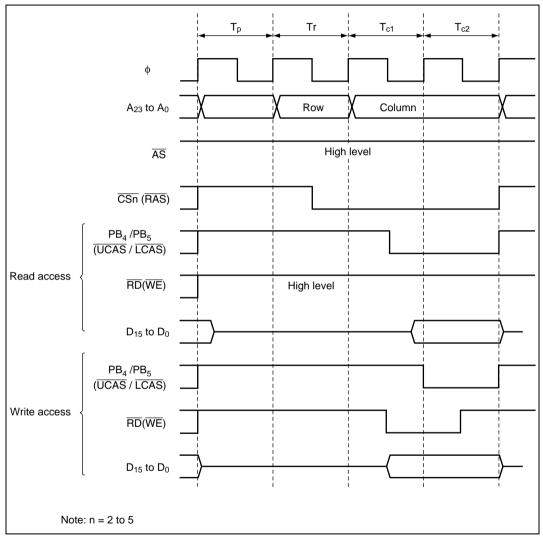

Figure 6.18 Basic Access Timing (CSEL = 0 in DRCRB)

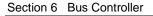

Figure 6.20 Example of Wait State Insertion Timing (CSEL = 0)

### 6.5.9 Byte Access Control and CAS Output Pin

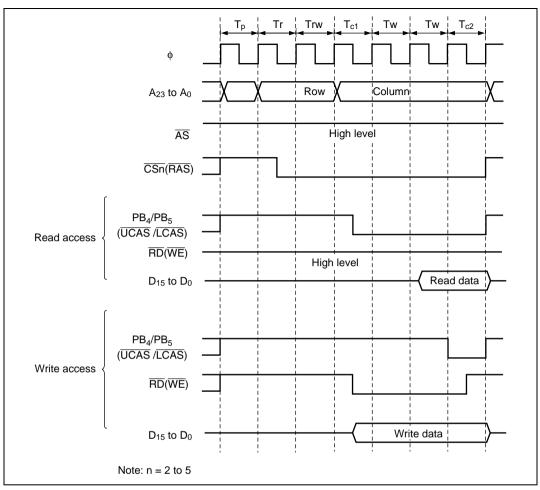

When an access is made to DRAM space designated as a 16-bit-access area in ABWCR, column address strobes ( $\overline{\text{UCAS}}$  and  $\overline{\text{LCAS}}$ ) corresponding to the upper and lower halves of the external data bus are output. In the case of × 16-bit organization DRAM, the 2-CAS type can be connected.

Either PB4 and PB5, or  $\overline{HWR}$  and  $\overline{LWR}$ , can be used as the  $\overline{UCAS}$  and  $\overline{LCAS}$  output pins, the selection being made with the CSEL bit in DRCRB. Table 6.8 shows the CSEL bit settings and corresponding output pin selections.

Figure 6.31 Interconnections and Address Map for 2-CAS 16-Mbit DRAMs with × 16-Bit Organization

### 7.4.6 Block Transfer Mode

In block transfer mode the A and B channels are combined. One block of a specified size is transferred per request. A designated number of block transfers are executed. Addresses are specified in MARA and MARB. The block area address can be either held fixed or cycled.

Table 7.10 indicates the register functions in block transfer mode.

| <b>Table 7.10</b> | <b>Register Functions in Block Transfer</b> | Mode |

|-------------------|---------------------------------------------|------|

|-------------------|---------------------------------------------|------|

| Register    | Function                          | Initial Setting              | Operation                                                                                  |

|-------------|-----------------------------------|------------------------------|--------------------------------------------------------------------------------------------|

| 23<br>MARA  | 0 Source address<br>register      | Source start<br>address      | Incremented or<br>decremented once per<br>transfer, or held fixed                          |

| 23<br>MARB  | 0 Destination<br>address register | Destination start address    | Incremented or<br>decremented once per<br>transfer, or held fixed                          |

| 7<br>ETCRA  | 0 Block size counter              | Block size                   | Decremented once per<br>transfer until H'00 is<br>reached, then reloaded<br>from ETCRL     |

| 7<br>ETCRA  | 0 Initial block size              | Block size                   | Held fixed                                                                                 |

| 15<br>ETCRB | 0 Block transfer<br>counter       | Number of block<br>transfers | Decremented once per<br>block transfer until H'0000<br>is reached and the<br>transfer ends |

Legend

MARA: Memory address register A

MARB: Memory address register B

ETCRA: Execute transfer count register A

ETCRB: Execute transfer count register B

The source and destination addresses are both 24-bit addresses. MARA specifies the source address. MARB specifies the destination address. MARA and MARB can be independently incremented, decremented, or held fixed as data is transferred. One of these registers operates as a block area register: even if it is incremented or decremented, it is restored to its initial value at the end of each block transfer. The TMS bit in DTCRB selects whether the block area is the source or destination.

|      | 1-Mbyte Mode                               | 16-Mbyte Mode                                  |  |

|------|--------------------------------------------|------------------------------------------------|--|

| MAR  | H'00000 to H'FFFFF<br>(0 to 1048575)       | H'000000 to H'FFFFFF<br>(0 to 16777215)        |  |

| IOAR | H'FFF00 to H'FFFFF<br>(1048320 to 1048575) | H'FFFF00 to H'FFFFFF<br>(16776960 to 16777215) |  |

#### Table 7.14 Address Ranges Specifiable in MAR and IOAR

MAR bits 23 to 20 are ignored in 1-Mbyte mode.

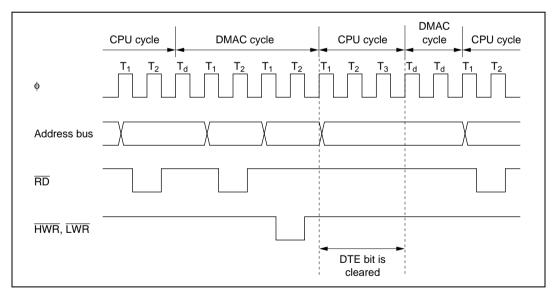

#### 7.6.8 Bus Cycle when Transfer is Aborted

When a transfer is aborted by clearing the DTE bit or suspended by an NMI that clears the DTME bit, if this halts a channel for which the DMAC has a transfer request pending internally, a dead cycle may occur. This dead cycle does not update the halted channel's address register or counter value. Figure 7.27 shows an example in which an auto-requested transfer in cycle-steal mode on channel 0 is aborted by clearing the DTE bit in channel 0.

Figure 7.27 Bus Timing at Abort of DMA Transfer in Cycle-Steal Mode

ABWCR and P4DDR are not initialized in software standby mode. Therefore, if a transition is made to software standby mode while port 4 is functioning as an input/output port and a P4DDR bit is set to 1, the corresponding pin maintains its output state.

**Port 4 Data Register (P4DR):** P4DR is an 8-bit readable/writable register that stores output data for port 4. When port 4 functions as an output port, the value of this register is output. When a bit in P4DDR is set to 1, if port 4 is read the value of the corresponding P4DR bit is returned. When a bit in P4DDR is cleared to 0, if port 4 is read the corresponding pin logic level is read.

| Bit           | 7   | 6               | 5               | 4   | 3   | 2   | 1               | 0               |

|---------------|-----|-----------------|-----------------|-----|-----|-----|-----------------|-----------------|

|               | P47 | P4 <sub>6</sub> | P4 <sub>5</sub> | P44 | P43 | P42 | P4 <sub>1</sub> | P4 <sub>0</sub> |

| Initial value | 0   | 0               | 0               | 0   | 0   | 0   | 0               | 0               |

| Read/Write    | R/W | R/W             | R/W             | R/W | R/W | R/W | R/W             | R/W             |

|               |     |                 |                 |     |     |     |                 |                 |

Port 4 data 7 to 0 These bits store data for port 4 pins

P4DR is initialized to H'00 by a reset and in hardware standby mode. In software standby mode it retains its previous setting.

**Port 4 Input Pull-Up MOS Control Register (P4PCR):** P4PCR is an 8-bit readable/writable register that controls the MOS input pull-up transistors in port 4.

| Bit           | 7      | 6                   | 5         | 4                   | 3                   | 2                   | 1      | 0      |

|---------------|--------|---------------------|-----------|---------------------|---------------------|---------------------|--------|--------|

|               | P47PCR | P4 <sub>6</sub> PCR | $P4_5PCR$ | P4 <sub>4</sub> PCR | P4 <sub>3</sub> PCR | P4 <sub>2</sub> PCR | P41PCR | P40PCR |

| Initial value | 0      | 0                   | 0         | 0                   | 0                   | 0                   | 0      | 0      |

| Read/Write    | R/W    | R/W                 | R/W       | R/W                 | R/W                 | R/W                 | R/W    | R/W    |

|               |        |                     | Port 4 i  | nput pull           | -up contro          | ol 7 to 0           |        |        |

These bits control input pull-up transistors built into port 4

In mode 6 and 7 (single-chip mode), and in 8-bit bus mode in modes 1 to 5 (expanded modes), when a P4DDR bit is cleared to 0 (selecting generic input), if the corresponding P4PCR bit is set to 1, the input pull-up transistor is turned on.

P4PCR is initialized to H'00 by a reset and in hardware standby mode. In software standby mode it retains its previous setting.

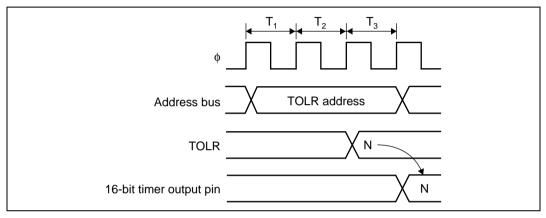

#### 9.4.6 Setting Initial Value of 16-Bit Timer Output

Any desired value can be specified for the initial 16-bit timer output value when a timer count operation is started by making a setting in TOLR.

Figure 9.32 shows the timing for setting the initial output value with TOLR.

Only write to TOLR when the corresponding bit in TSTR is cleared to 0.

Figure 9.32 Example of Timing for Setting Initial Value of 16-Bit Timer Output by Writing to TOLR

| ¢                    |   |

|----------------------|---|

| TCNT                 | N |

| TCORB                | N |

| Input capture signal |   |

| CMFB                 |   |

Figure 10.15 CMFB Flag Setting Timing when Input Capture Occurs

**Timing of Overflow Flag (OVF) Setting:** The OVF flag in TCSR is set to 1 by the overflow signal generated when TCNT overflows (from H'FF to H'00). Figure 10.16 shows the timing in this case.

| φ               |             |

|-----------------|-------------|

| TCNT            | H'FF X H'00 |

| Overflow signal |             |

| OVF             |             |

Figure 10.16 Timing of OVF Setting

### 10.4.5 Operation with Cascaded Connection

If bits CKS2 to CKS0 are set to B'100 in either TCR0 or TCR1, the 8-bit timers of channels 0 and 1 are cascaded. With this configuration, the two timers can be used as a single 16-bit timer (16-bit count mode), or channel 0 8-bit timer compare matches can be counted in channel 1 (compare match count mode). In this case, the timer operates as below. Similarly, if bits CKS2 to CKS0 are set to B'100 in either TCR2 or TCR3, the 8-bit timers of channels 0 and 1 are cascaded. With this configuration, the two timers can be used as a single 16-bit timer (16-bit count mode), or channel 2 8-bit timer compare matches can be counted in channel 3 (compare match count mode). Timer operation in these cases is described below.

### 11.2.8 Next Data Enable Register B (NDERB)

NDERB is an 8-bit readable/writable register that enables or disables TPC output groups 3 and 2 ( $TP_{15}$  to  $TP_8$ ) on a bit-by-bit basis.

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|---------------|--------|--------|--------|--------|--------|--------|-------|-------|

|               | NDER15 | NDER14 | NDER13 | NDER12 | NDER11 | NDER10 | NDER9 | NDER8 |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W   | R/W   |

|               |        |        |        |        |        |        |       |       |

Next data enable 15 to 8 These bits enable or disable TPC output groups 3 and 2

If a bit is enabled for TPC output by NDERB, then when the 16-bit timer compare match event selected in the TPC output control register (TPCR) occurs, the NDRB value is automatically transferred to the corresponding PBDR bit, updating the output value. If TPC output is disabled, the bit value is not transferred from NDRB to PBDR and the output value does not change.

NDERB is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in software standby mode.

**Bits 7 to 0—Next Data Enable 15 to 8 (NDER15 to NDER8):** These bits enable or disable TPC output groups 3 and 2 ( $TP_{15}$  to  $TP_{8}$ ) on a bit-by-bit basis.

| Bits 7 to 0<br>NDER15 to NDER8 | Description                                                                                              |                 |

|--------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|

| 0                              | TPC outputs $TP_{15}$ to $TP_8$ are disabled<br>(NDR15 to NDR8 are not transferred to $PB_7$ to $PB_0$ ) | (Initial value) |

| 1                              | TPC outputs $TP_{15}$ to $TP_8$ are enabled<br>(NDR15 to NDR8 are transferred to $PB_7$ to $PB_0$ )      |                 |

### 14.2 Register Descriptions

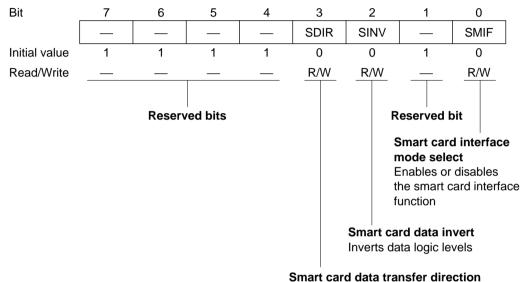

This section describes the new or modified registers and bit functions in the smart card interface.

#### 14.2.1 Smart Card Mode Register (SCMR)

SCMR is an 8-bit readable/writable register that selects smart card interface functions.

Selects the serial/parallel conversion format

SCMR is initialized to H'F2 by a reset and in standby mode.

Bits 7 to 4—Reserved: Read-only bits, always read as 1.

**Bit 3—Smart Card Data Transfer Direction (SDIR):** Selects the serial/parallel conversion format.<sup>\*1</sup>

| Bit 3<br>SDIR | Description                             |                 |

|---------------|-----------------------------------------|-----------------|

| 0             | TDR contents are transmitted LSB-first  | (Initial value) |

|               | Receive data is stored LSB-first in RDR |                 |

| 1             | TDR contents are transmitted MSB-first  |                 |

|               | Receive data is stored MSB-first in RDR |                 |

The following equation calculates the bit rate register (BRR) setting from the operating frequency and bit rate. N is an integer from 0 to 255, specifying the value with the smaller error.

$$N = \frac{\varphi}{1488 \times 2^{2n-1} \times B} \times 10^6 - 1$$

#### Table 14.6 BRR Settings for Typical Bit Rates (bits/s) (When n = 0)

|       | φ (MHz)                                        |       |   |       |   |       |   |       |   |       |      |       |   |       |

|-------|------------------------------------------------|-------|---|-------|---|-------|---|-------|---|-------|------|-------|---|-------|

|       | 7.1424 10.00 10.7136 13.00 14.2848 16.00 18.00 |       |   |       |   |       |   |       |   |       | 8.00 |       |   |       |

| bit/s | Ν                                              | Error | Ν | Error | Ν | Error | Ν | Error | Ν | Error | Ν    | Error | Ν | Error |

| 9600  | 0                                              | 0.00  | 1 | 30    | 1 | 25    | 1 | 8.99  | 1 | 0.00  | 1    | 12.01 | 2 | 15.99 |

Table 14.7

Maximum Bit Rates for Various Frequencies (Smart Card Interface Mode)

| φ (MHz) | Maximum Bit Rate (bits/s) | Ν | n |  |

|---------|---------------------------|---|---|--|

| 7.1424  | 9600                      | 0 | 0 |  |

| 10.00   | 13441                     | 0 | 0 |  |

| 10.7136 | 14400                     | 0 | 0 |  |

| 13.00   | 17473                     | 0 | 0 |  |

| 14.2848 | 19200                     | 0 | 0 |  |

| 16.00   | 21505                     | 0 | 0 |  |

| 18.00   | 24194                     | 0 | 0 |  |

The bit rate error is given by the following equation:

Error (%) =

$$\left(\frac{\phi}{1488 \times 2^{2n-1} \times B \times (N+1)} \times 10^6 - 1\right) \times 100$$

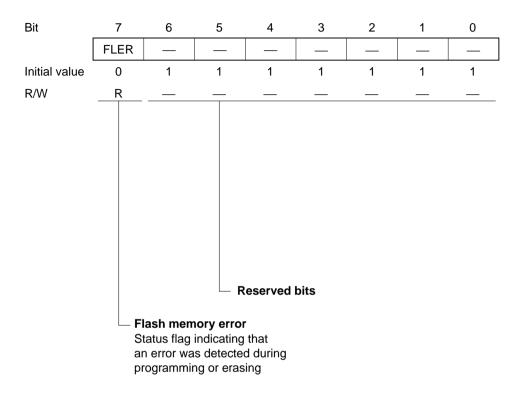

#### 18.3.4 Flash Memory Status Register

The flash memory status register (FLMSR) detects flash memory errors.

### Section 21 Electrical Characteristics

|                                     |                    |                                          | Con                          |                              |                                          |      |                                |

|-------------------------------------|--------------------|------------------------------------------|------------------------------|------------------------------|------------------------------------------|------|--------------------------------|

|                                     |                    |                                          | Α                            |                              | В                                        | _    | Test                           |

| Item                                | Symbol             | Min                                      | Max                          | Min                          | Max                                      | Unit | Conditions                     |

| Read data access time 1             | t <sub>ACC1</sub>  | _                                        | 2.0 t <sub>cyc</sub><br>- 80 | _                            | 2.0 t <sub>cyc</sub><br>- 45             | ns   | Figure 21.11, figure 21.12,    |

| Read data access time 2             | t <sub>ACC2</sub>  | —                                        | 3.0 t <sub>cyc</sub><br>- 80 | —                            | 3.0 t <sub><sub>cyc</sub><br/>– 45</sub> | ns   | figure 21.14,<br>figure 21.15, |

| Read data access time 3             | t <sub>ACC3</sub>  | —                                        | 1.5 t <sub>cyc</sub><br>– 80 |                              | 1.5 t <sub>cyc</sub><br>– 45             | ns   | <sup>–</sup> figure 21.17      |

| Read data access time 4             | t <sub>ACC4</sub>  | —                                        | 2.5 t <sub>cyc</sub><br>- 80 |                              | 2.5 t <sub>cyc</sub><br>– 45             | ns   | _                              |

| Precharge time 1                    | t <sub>PCH1</sub>  | 1.0 t <sub>cyc</sub><br>– 30             | —                            | 1.0 t <sub>cyc</sub><br>– 20 | —                                        | ns   |                                |

| Precharge time 2                    | t <sub>PCH2</sub>  | 0.5 t <sub>cyc</sub><br>– 30             | _                            | 0.5 t <sub>cyc</sub><br>– 20 | _                                        | ns   |                                |

| Wait setup time                     | t <sub>wrs</sub>   | 40                                       | _                            | 25                           | _                                        | ns   | Figure 21.13                   |

| Wait hold time                      | t <sub>wth</sub>   | 5                                        | —                            | 5                            | _                                        | ns   |                                |

| Bus request setup time              | t <sub>BRQS</sub>  | 40                                       | —                            | 25                           |                                          | ns   | Figure 21.16                   |

| Bus acknowledge delay time 1        | t <sub>BACD1</sub> | _                                        | 50                           | _                            | 30                                       | ns   |                                |

| Bus acknowledge delay time 2        | t <sub>BACD2</sub> | —                                        | 50                           | —                            | 30                                       | ns   |                                |

| Bus-floating time                   | t <sub>BZD</sub>   | —                                        | 50                           | —                            | 30                                       | ns   |                                |

| RAS precharge time                  | t <sub>RP</sub>    | 1.5 t <sub><sub>cyc</sub><br/>– 40</sub> | —                            | 1.5 t <sub>cyc</sub><br>– 25 | —                                        | ns   | Figure 21.17<br>to             |

| CAS precharge time                  | t <sub>cP</sub>    | 0.5 t <sub><sub>cyc</sub><br/>– 25</sub> | _                            | 0.5 t <sub>cyc</sub><br>– 15 | —                                        | ns   | figure 21.19                   |

| Low address hold time               | t <sub>RAH</sub>   | 0.5 t <sub>cyc</sub><br>– 25             | _                            | 0.5 t <sub>cyc</sub> –<br>15 | —                                        | ns   |                                |

| RAS delay time 1                    | t <sub>RAD1</sub>  | —                                        | 50                           | —                            | 25                                       | ns   |                                |

| RAS delay time 2                    | t <sub>RAD2</sub>  | _                                        | 50                           | _                            | 30                                       | ns   | _                              |

| CAS delay time 1                    | t <sub>CASD1</sub> | _                                        | 50                           | —                            | 25                                       | ns   |                                |

| CAS delay time 2 t <sub>CASD2</sub> |                    | _                                        | 50                           | _                            | 25                                       | ns   | _                              |

| WE delay time                       | t <sub>wcD</sub>   |                                          | 50                           |                              | 25                                       | ns   | _                              |

| CAS pulse width 1                   | t <sub>CAS1</sub>  | 1.5 t <sub><sub>cyc</sub><br/>– 40</sub> | _                            | 1.5 t <sub>cyc</sub><br>– 20 | _                                        | ns   |                                |

| CAS pulse width 2                   | t <sub>CAS2</sub>  | 1.0 t <sub>cyc</sub><br>- 40             | _                            | 1.0 t <sub>cyc</sub><br>– 20 | _                                        | ns   |                                |

| CAS pulse width 3                   | t <sub>CAS3</sub>  | 1.0 t <sub>cyc</sub><br>- 40             |                              | 1.0 t <sub>cyc</sub><br>– 20 | _                                        | ns   |                                |

| IOAR0B—I/     | O Address | s Register | H'FFF2E      |              | DMAC0       |              |     |     |

|---------------|-----------|------------|--------------|--------------|-------------|--------------|-----|-----|

|               |           |            |              |              |             |              |     |     |

| Bit           | 7         | 6          | 5            | 4            | 3           | 2            | 1   | 0   |

|               |           |            |              |              |             |              |     |     |

| Initial value |           |            |              | Undete       | rmined      | 1            |     |     |

| Read/Write    | R/W       | R/W        | R/W          | R/W          | R/W         | R/W          | R/W | R/W |

|               |           |            |              |              |             |              |     |     |

|               |           | Shor       | t address mo | ode : source | or destinat | tion address |     |     |

|               |           | Full a     | address mod  | le : not use | d           |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

|               |           |            |              |              |             |              |     |     |

| L             |           |            |              |              |             |              |     |     |

| SRA—Timer Int | terrupt St     | atus Register A                                              | H'FFF64                   | 16-bit timer (all channels)           |

|---------------|----------------|--------------------------------------------------------------|---------------------------|---------------------------------------|

| F             | Bit:           | 7 6 5                                                        | 4 3 2                     | 1 0                                   |

|               |                | IMIEA2 IMIEA1 IM                                             | IEA0 — IMFA2 IM           | FA1 IMFA0                             |

| I             | Initial value: | 1 0 0                                                        | 0 1 0                     | 0 0                                   |

| F             | Read/Write:    |                                                              | <u>2/W — R/(W)* R/(</u>   | <u>(W)*</u> <u>R/(W)*</u>             |

|               |                |                                                              |                           |                                       |

|               |                |                                                              |                           |                                       |

|               |                | Input capture/compare mat                                    | ch flag A0                |                                       |

|               |                | [Clearing conditions]                                        |                           | (Initial value)                       |

|               |                |                                                              | MFA0=1, then write 0 in I | MFA0                                  |

|               |                | DMAC activated by                                            | IMIAU Interrupt.          |                                       |

|               |                | [Setting conditions]                                         |                           |                                       |

|               |                | 1 TCNT0=GRA0 when                                            | GRA0 functions as an o    | output compare register.              |

|               |                | I CN I 0 Value is tran                                       |                           | put capture signal when GRA0          |

|               |                | functions as an inpu                                         | t capture register.       |                                       |

|               | Inpu           | t capture/compare match fla                                  | ag A1                     |                                       |

|               |                | [Clearing conditions]                                        |                           | (Initial value)                       |

|               | 0              | Read IMFA1 when IMFA                                         | 1=1, then write 0 in IMFA | 1                                     |

|               |                | DMAC activated by IMIA                                       | 1 interrupt.              |                                       |

|               |                | [Setting conditions]                                         |                           |                                       |

|               |                | TCNT1=GRA1 when GR                                           | A1 functions as an outpu  | t compare register.                   |

|               | 1              |                                                              |                           | apture signal when GRA1               |

|               |                | functions as an input cap                                    | ture register.            |                                       |

|               |                | ure/compare match flag A2                                    |                           |                                       |

|               |                | earing conditions]                                           |                           | (Initial value)                       |

|               | -              | ad IMFA2 when IMFA2=1, t                                     | nen write 0 in IMFA2      |                                       |

|               |                | IAC activated by IMIA2 inter                                 |                           |                                       |

|               |                |                                                              | ·                         |                                       |

|               |                | tting conditions]                                            |                           |                                       |

|               | 1 1            | NT2=GRA2 when GRA2 fur<br>NT2 value is transferred to (      |                           | • •                                   |

|               |                | ctions as an input capture re                                |                           |                                       |

|               |                |                                                              |                           |                                       |

|               |                | mpare match interrupt enabl                                  |                           | <i></i>                               |

| 0             |                | errupt requested by IMFA0 fl<br>errupt requested by IMFA0 is | -                         | (Initial value)                       |

|               |                |                                                              |                           |                                       |

|               |                | e match interrupt enable A1<br>t requested by IMFA1 flag is  |                           | ial value)                            |

|               |                | t requested by IMFA1 is ena                                  |                           | · · · · · · · · · · · · · · · · · · · |

|               |                | tch interrupt enable A2                                      |                           |                                       |

|               |                |                                                              | (1-1) (1-1) -             | hur)                                  |

|               | interrupt requ | uested by IMFA2 flag is disa                                 | bled (Initial va          | lue)                                  |

| 1 IMIA2       |                | uested by IMFA2 flag is disa<br>uested by IMFA2 is enabled   | died (Initial Va          |                                       |

| Pin<br>Name | Mode   | Reset | Hardware<br>Standby<br>Mode | Software Standby<br>Mode                                                                                                                                                                                                                                                                | Bus-Released<br>Mode                                                                                                                                                    | Program Execution<br>Mode                                                                                                                                                                                                   |

|-------------|--------|-------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P80         | 1 to 5 | Т     | Т                           | When DRAM space<br>is not selected <sup>*1</sup><br>(RFSHE=0)<br>Keep<br>(RFSHE=1)<br>Illegal setting<br>When DRAM space<br>is selected <sup>*2</sup><br>(RFSHE=0)<br>Keep<br>(RFSHE=1,<br>SRFMD=0, SSOE=0)<br>T<br>(RFSHE=1,<br>SRFMD=0, SSOE=1)<br>H<br>(RFSHE=1,<br>SRFMD=1)<br>RFSH |                                                                                                                                                                         | (RFSHE=0)<br>I/O port<br>(RFSHE=1)<br>RFSH                                                                                                                                                                                  |

|             | 6, 7   | Т     | Т                           | Кеер                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                       | I/O port                                                                                                                                                                                                                    |

| P81         | 1 to 5 | Τ     | Τ                           | When DRAM space<br>is selected <sup>*3</sup><br>(SSOE=0)<br>T<br>(SSOE=1)<br>H<br>When DRAM space<br>is selected <sup>*4</sup><br>Keep<br>Otherwise <sup>*5 *1</sup><br>(DDR=0)<br>T<br>(DDR=1, SSOE=0)<br>T<br>(DDR=1, SSOE=1)<br>H                                                    | When DRAM space<br>is selected <sup>*3</sup><br>T<br>When DRAM space<br>is selected <sup>*4</sup><br>Keep<br>Otherwise <sup>*1</sup><br>(DDR=0)<br>Keep<br>(DDR=1)<br>T | When DRAM space<br>is selected and RAS3<br>is output<br>$\overline{RAS}_3$<br>When DRAM space<br>is selected and RAS3<br>is<br>not output<br>I/O port<br>Otherwise<br>(DDR=0)<br>Input port<br>(DDR=1)<br>$\overline{CS}_3$ |

|             | 6, 7   | Т     | Т                           | Keep                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                       | I/O port                                                                                                                                                                                                                    |