Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1713-e-mv |

**TABLE 1-2:** PIC16(L)F1713/6 PINOUT DESCRIPTION

| Name                             | Function | Input<br>Type | Output<br>Type | Description                                  |

|----------------------------------|----------|---------------|----------------|----------------------------------------------|

| RA0/AN0/C1IN0-/C2IN0-/           | RA0      | TTL/ST        | CMOS           | General purpose I/O.                         |

| CLCINO <sup>(1)</sup>            | AN0      | AN            | _              | ADC Channel 0 input.                         |

|                                  | C1IN0-   | AN            | _              | Comparator C2 negative input.                |

|                                  | C2IN0-   | AN            | _              | Comparator C3 negative input.                |

|                                  | CLCIN0   | TTL/ST        | _              | Configurable Logic Cell source input.        |

| RA1/AN1/C1IN1-/C2IN1-/           | RA1      | TTL/ST        | CMOS           | General purpose I/O.                         |

| OPA1OUT/CLCIN1 <sup>(1)</sup>    | AN1      | AN            | _              | ADC Channel 1 input.                         |

|                                  | C1IN1-   | AN            |                | Comparator C1 negative input.                |

|                                  | C2IN1-   | AN            | _              | Comparator C2 negative input.                |

|                                  | OPA1OUT  | _             | AN             | Operational Amplifier 1 output.              |

|                                  | CLCIN1   | TTL/ST        | _              | Configurable Logic Cell source input.        |

| RA2/AN2/VREF-/C1IN0+/C2IN0+/     | RA2      | TTL/ST        | CMOS           | General purpose I/O.                         |

| DAC1OUT1                         | AN2      | AN            | _              | ADC Channel 2 input.                         |

|                                  | VREF-    | AN            | _              | ADC Negative Voltage Reference input.        |

|                                  | C1IN0+   | AN            | _              | Comparator C2 positive input.                |

|                                  | C2IN0+   | AN            | _              | Comparator C3 positive input.                |

|                                  | DAC1OUT1 | _             | AN             | Digital-to-Analog Converter output.          |

| RA3/AN3/VREF+/C1IN1+             | RA3      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | AN3      | AN            | _              | ADC Channel 3 input.                         |

|                                  | VREF+    | AN            | _              | ADC Voltage Reference input.                 |

|                                  | C1IN1+   | AN            | _              | Comparator C1 positive input.                |

| RA4/OPA1IN+/T0CKI <sup>(1)</sup> | RA4      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OPA1IN+  | AN            | _              | Operational Amplifier 1 non-inverting input. |

|                                  | T0CKI    | TTL/ST        | _              | Timer0 gate input.                           |

| RA5/AN4/OPA1IN-/DAC2OUT1/        | RA5      | TTL/ST        | CMOS           | General purpose I/O.                         |

| SS <sup>(1)</sup>                | AN4      | AN            | _              | ADC Channel 4 input.                         |

|                                  | OPA1IN-  | AN            | _              | Operational Amplifier 1 inverting input.     |

|                                  | DAC2OUT1 | _             | AN             | Digital-to-Analog Converter output.          |

|                                  | SS       | TTL/ST        | _              | Slave Select enable input.                   |

| RA6/OSC2/CLKOUT                  | RA6      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).        |

|                                  | CLKOUT   | _             | CMOS           | Fosc/4 output.                               |

| RA7/OSC1/CLKIN                   | RA7      | TTL/ST        | CMOS           | General purpose I/O.                         |

|                                  | OSC1     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).        |

|                                  | CLKIN    | TTL/ST        | _              | External clock input (EC mode).              |

| RB0/AN12/C2IN1+/ZCD/             | RB0      | TTL/ST        | CMOS           | General purpose I/O.                         |

| COGIN <sup>(1)</sup>             | AN12     | AN            | _              | ADC Channel 12 input.                        |

|                                  | C2IN1+   | AN            | _              | Comparator C2 positive input.                |

|                                  | ZCD      | AN            | _              | Zero-Cross Detection Current Source/Sink.    |

|                                  | COGIN    | TTL/ST        | _              | Complementary Output Generator input.        |

| Legend: AN = Analog input or o   |          |               |                |                                              |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output TTL = TTL compatible input

OD = Open-Drain ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$

HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

- 2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

- 3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-10.

TABLE 3-2: CORE REGISTERS

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| x0Ah or x8Ah | PCLATH |

| k0Bh or x8Bh | INTCON |

TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr  | Name     | Bit 7         | Bit 6          | Bit 5          | Bit 4         | Bit 3          | Bit 2           | Bit 1      | Bit 0    | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|-------|----------|---------------|----------------|----------------|---------------|----------------|-----------------|------------|----------|----------------------|---------------------------------|

| Banl  | k 2      |               |                |                |               |                |                 |            |          |                      |                                 |

| 10Ch  | LATA     | LATA7         | LATA6          | LATA5          | LATA4         | LATA3          | LATA2           | LATA1      | LATA0    | xxxx xxxx            | uu -uuu                         |

| 10Dh  | LATB     | LATB7         | LATB6          | LATB5          | LATB4         | LATB3          | LATB2           | LATB1      | LATB0    | xxxx xxxx            | uuuu                            |

| 10Eh  | LATC     | LATC7         | LATC6          | LATC5          | LATC4         | LATC3          | LATC2           | LATC1      | LATC0    | xxxx xxxx            | uuuu uuuu                       |

| 10Fh  | _        | Unimplement   | ted            |                |               |                |                 |            |          | _                    | _                               |

| 110h  | _        | Unimplement   | ted            |                |               |                |                 |            |          | _                    | _                               |

| 111h  | CM1CON0  | C10N          | C10UT          | _              | C1POL         | C1ZLF          | C1SP            | C1HYS      | C1SYNC   | 00-0 0100            | 00-0 0100                       |

| 112h  | CM1CON1  | C1INTP        | C1INTN         |                | C1PCH<2:0>    |                |                 | C1NCH<2:0> | •        | 0000 0000            | 0000 0000                       |

| 113h  | CM2CON0  | C2ON          | C2OUT          | _              | C2POL         | C2ZLF          | C2SP            | C2HYS      | C2SYNC   | 00-0 0100            | 00-0 0100                       |

| 114h  | CM2CON1  | C2INTP        | C2INTN         |                | C2PCH<2:0>    |                |                 | C2NCH<2:0> | •        | 0000 0000            | 0000 0000                       |

| 115h  | CMOUT    | _             | _              | _              | -             | ı              | _               | MC2OUT     | MC1OUT   | 00                   | 00                              |

| 116h  | BORCON   | SBOREN        | BORFS          | _              | -             | ı              | _               | _          | BORRDY   | 10q                  | uuu                             |

| 117h  | FVRCON   | FVREN         | FVRRDY         | TSEN           | TSRNG         | CDAFV          | /R<1:0>         | ADFV       | R<1:0>   | 0q00 0000            | 0000 00p0                       |

| 118h  | DAC1CON0 | DAC1EN        |                | DAC10E1        | DAC10E2       | DAC1PS         | SS<1:0>         |            | DAC1NSS  | 0-00 00-0            | 0-00 00-0                       |

| 119h  | DAC1CON1 |               |                |                | DAC1          | R<7:0>         |                 |            |          | 0000 0000            | 0000 0000                       |

| 11Ah  | DAC2CON0 | DAC2EN        | _              | DAC2OE1        | DAC2OE2       | DAC2PS         | SS<1:0>         | _          | DAC2NSS  | 0-00 00-0            | 0-00 00-0                       |

| 11Bh  | DAC2CON1 | _             | _              | _              |               |                | DAC2R<4:0       | >          |          | 0 0000               | 0 0000                          |

| 11Ch  | ZCD1CON  | ZCD1EN        | _              | ZCD10UT        | ZCD1POL       | _              | _               | ZCD1INTP   | ZCD1INTN | 0-x000               | 0-0000                          |

| 11Dh  | _        | Unimplemented |                |                |               |                |                 |            |          | _                    | _                               |

| 11Eh  | _        | Unimplemented |                |                |               |                |                 |            | _        | _                    |                                 |

| 11Fh  | _        | Unimplement   | ted            |                |               |                |                 |            |          | _                    | _                               |

| Banl  | k 3      | •             |                |                |               |                |                 |            |          |                      |                                 |

| 18Ch  | ANSELA   | _             | _              | ANSA5          | ANSA4         | ANSA3          | ANSA2           | ANSA1      | ANSA0    | 11 1111              | 1 1111                          |

| 18Dh  | ANSELB   | _             | _              | ANSB5          | ANSB4         | ANSB3          | ANSB2           | ANSB1      | ANSB0    | 11 1111              | 11                              |

| 18Eh  | ANSELC   | ANSC7         | ANSC6          | ANSC5          | ANSC4         | ANSC3          | ANSC2           | _          | ı        | 1111 11              | 1111 1111                       |

| 18Fh  | _        | Unimplement   | ted            |                |               |                |                 |            |          | _                    | _                               |

| 190h  | _        | Unimplement   | ted            |                |               |                |                 |            |          | _                    | _                               |

| 191h  | PMADRL   | Program Mer   | mory Address   | Register Low   | Byte          |                |                 |            |          | 0000 0000            | 0000 0000                       |

| 192h  | PMADRH   | _             | Program Mer    | mory Address   | Register High | Byte           |                 |            |          | 1000 0000            | 1000 0000                       |

| 193h  | PMDATL   | Program Mer   | mory Read Da   | ta Register Lo | w Byte        |                |                 |            |          | xxxx xxxx            | uuuu uuuu                       |

| 194h  | PMDATH   | _             | _              | Program Mer    | nory Read Da  | ta Register Hi | gh Byte         |            |          | xx xxxx              | uu uuuu                         |

| 195h  | PMCON1   | _             | CFGS           | LWLO           | FREE          | WRERR          | WREN            | WR         | RD       | -000 x000            | -000 q000                       |

| 196h  | PMCON2   | Program Mer   | mory Control F | Register 2     |               |                |                 |            |          | 0000 0000            | 0000 0000                       |

| 197h  | VREGCON  | _             | _              | _              | -             | ı              | _               | VREGPM     | Reserved | 01                   | 01                              |

| 198h  | _        | Unimplement   | ted            |                |               |                |                 |            |          | _                    | _                               |

| 199h  | RC1REG   | USART Rece    | eive Data Regi | ster           |               |                |                 |            |          | 0000 0000            | 0000 0000                       |

| 19Ah  | TX1REG   | USART Trans   | smit Data Reg  | ister          |               |                |                 |            |          | 0000 0000            | 0000 0000                       |

| 19Bh  | SP1BRGL  |               |                |                | SP1BF         | RG<7:0>        |                 |            |          | 0000 0000            | 0000 0000                       |

| 19Ch  | SP1BRGH  |               |                |                | SP1BR         | G<15:8>        |                 |            |          | 0000 0000            | 0000 0000                       |

| 19Dh  | RC1STA   | SPEN          | RX9            | SREN           | CREN          | ADDEN          | FERR            | OERR       | RX9D     | 0000 0000            | 0000 0000                       |

| 19Eh  | TX1STA   | CSRC          | TX9            | TXEN           | SYNC          | SENDB          | BRGH            | TRMT       | TX9D     | 0000 0010            | 0000 0010                       |

| 19Fh  | BAUD1CON | ABDOVF        | RCIDL          | _              | SCKP          | BRG16          | _               | WUE        | ABDEN    | 01-0 0-00            | 01-0 0-00                       |

| Legen | l .      | vn, u = uncha |                | e depends on   |               |                | d. read as '0'. |            |          | 1                    | 1 2 3                           |

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16(L)F1713/6.

### 5.13 Power Control (PCON) Register

The PCON register bits are shown in Register 5-2.

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

### 5.14 Register Definitions: Power Control

#### REGISTER 5-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | -   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            |            | bit 0      |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7 | STKOVF: Stack Overflow Flag bit                                                                   |

|-------|---------------------------------------------------------------------------------------------------|

|       | 1 = A Stack Overflow occurred                                                                     |

|       | 0 = A Stack Overflow has not occurred or cleared by firmware                                      |

| bit 6 | STKUNF: Stack Underflow Flag bit                                                                  |

|       | 1 = A Stack Underflow occurred                                                                    |

|       | 0 = A Stack Underflow has not occurred or cleared by firmware                                     |

| bit 5 | Unimplemented: Read as '0'                                                                        |

| bit 4 | RWDT: Watchdog Timer Reset Flag bit                                                               |

|       | 1 = A Watchdog Timer Reset has not occurred or set to '1' by firmware                             |

|       | 0 = A Watchdog Timer Reset has occurred (cleared by hardware)                                     |

| bit 3 | RMCLR: MCLR Reset Flag bit                                                                        |

|       | 1 = A $\overline{\text{MCLR}}$ Reset has not occurred or set to '1' by firmware                   |

|       | 0 = A MCLR Reset has occurred (cleared by hardware)                                               |

| bit 2 | RI: RESET Instruction Flag bit                                                                    |

|       | 1 = A RESET instruction has not been executed or set to '1' by firmware                           |

|       | 0 = A RESET instruction has been executed (cleared by hardware)                                   |

| bit 1 | POR: Power-on Reset Status bit                                                                    |

|       | 1 = No Power-on Reset occurred                                                                    |

|       | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)             |

| bit 0 | BOR: Brown-out Reset Status bit                                                                   |

|       | 1 = No Brown-out Reset occurred                                                                   |

|       | 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset |

occurs)

#### 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- · Operation

- · Interrupt Latency

- · Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

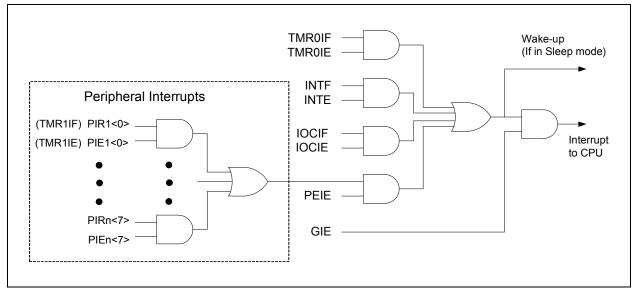

A block diagram of the interrupt logic is shown in Figure 7-1.

FIGURE 7-1: INTERRUPT LOGIC

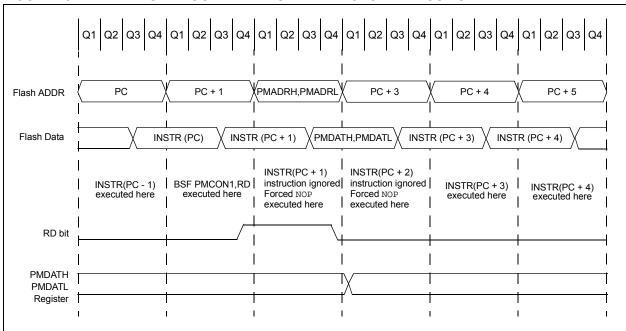

#### FIGURE 10-2: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

#### **EXAMPLE 10-1: FLASH PROGRAM MEMORY READ**

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL PMADRL

; Select Bank for PMCON registers

MOVLW

PROG_ADDR_LO

MOVWF

PMADRL

; Store LSB of address

MOVLW

PROG_ADDR_HI

MOVWF

PMADRH

; Store MSB of address

BCF

PMCON1,CFGS

; Do not select Configuration Space

BSF

PMCON1,RD

; Initiate read

NOP

; Ignored (Figure 10-1)

NOP

; Ignored (Figure 10-1)

MOVF

PMDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO

; Store in user location

MOVF

PMDATH,W

; Get MSB of word

MOVWF

PROG_DATA_HI

; Store in user location

```

## 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- · Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two  $\mathtt{NOP}$  instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two  $\mathtt{NOP}$  instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

FIGURE 10-3: FLASH PROGRAM

MEMORY UNLOCK

SEQUENCE FLOWCHART

TABLE 11-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|------------------|

| ANSELB  | _       | _       | ANSB5   | ANSB4   | ANSB3   | ANSB2   | ANSB1   | ANSB0   | 126              |

| INLVLB  | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 | 127              |

| LATB    | LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   | 125              |

| ODCONB  | ODB7    | ODB6    | ODB5    | ODB4    | ODB3    | ODB2    | ODB1    | ODB0    | 127              |

| PORTB   | RB7     | RB6     | RB5     | RB4     | RB3     | RB2     | RB1     | RB0     | 125              |

| SLRCONB | SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   | 127              |

| TRISB   | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  | 127              |

| WPUB    | WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   | 126              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

### 12.8 Register Definitions: PPS Input Selection

#### REGISTER 12-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION

| U-0   | U-0 | U-0 | R/W-q/u | R/W-q/u | R/W-q/u     | R/W-q/u | R/W-q/u |

|-------|-----|-----|---------|---------|-------------|---------|---------|

| _     | _   | _   |         |         | xxxPPS<4:0> |         |         |

| bit 7 |     |     |         |         |             |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = value depends on peripheral

bit 7-5 **Unimplemented:** Read as '0'

bit 4-3 **xxxPPS<4:3>:** Peripheral xxx Input PORTx Selection bits

See Table 12-1 for the list of available ports for each peripheral.

11 = Reserved. Do not use.

10 = Peripheral input is from PORTC

01 = Peripheral input is from PORTB

00 = Peripheral input is from PORTA

bit 2-0 xxxPPS<2:0>: Peripheral xxx Input PORTx Bit Selection bits

111 = Peripheral input is from PORTx Bit 7 (Rx7)

111 = Peripheral input is from PORTx Bit 6 (Rx6)

101 = Peripheral input is from PORTx Bit 5 (Rx5)

100 = Peripheral input is from PORTx Bit 4 (Rx4)

011 = Peripheral input is from PORTx Bit 3 (Rx3)

010 = Peripheral input is from PORTx Bit 2 (Rx2)

001 = Peripheral input is from PORTx Bit 1 (Rx1)

000 = Peripheral input is from PORTx Bit 0 (Rx0)

#### **TABLE 12-1:**

| Peripheral             | Register                     | PORTA    | PORTB | PORTC |

|------------------------|------------------------------|----------|-------|-------|

| PIN interrupt          | INTPPS                       | Х        | Х     |       |

| Timer0 clock           | TOCKIPPS                     | Х        | Х     |       |

| Timer1 clock           | T1CKIPPS                     | Х        |       | Х     |

| Timer1 gate            | T1GPPS                       |          | Х     | Х     |

| CCP1                   | CCP1PPS                      |          | Х     | Х     |

| CCP2                   | CCP2PPS                      |          | Х     | Х     |

| COG                    | COGINPPS                     |          | Х     | Х     |

| MSSP                   | SSPCLKPPS                    |          | Х     | Х     |

| MSSP                   | SSPDATPPS                    |          | Х     | Х     |

| MSSP                   | SSPSSPPS                     | Х        |       | Х     |

| EUSART                 | RXPPS                        |          | Х     | Х     |

| EUSART                 | CKPPS                        |          | Х     | Х     |

| All CLCs               | CLCIN0PPS                    | Х        |       | Х     |

| All CLCs               | CLCIN1PPS                    | Х        |       | Х     |

| All CLCs               | CLCIN2PPS                    |          | Х     | Х     |

| All CLCs               | CLCIN3PPS                    |          | Х     | Х     |

| Example: CCP1PPS = 0x0 | B selects RB3 as the input t | to CCP1. |       |       |

**Note:** Inputs are not available on all ports. A check in a port column of a peripheral row indicates that the port selection is valid for that peripheral. Unsupported ports will input a '0'.

### REGISTER 12-3: PPSLOCK: PPS LOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   |

|-------|-----|-----|-----|-----|-----|-----|-----------|

| _     | _   | _   | _   | _   | _   | _   | PPSLOCKED |

| bit 7 |     |     |     |     |     |     | bit 0     |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-1 **Unimplemented:** Read as '0' bit 0 **PPSLOCKED:** PPS Locked bit

1= PPS is locked. PPS selections can not be changed. 0= PPS is not locked. PPS selections can be changed.

### REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

bit 0 GxFSIM0: COGx Falling Event Input Source 0 Mode bit

<u>GxFIS0 = 1:</u>

- 1 = Pin selected with COGxPPS control high-to-low transition will cause a falling event after falling event phase delay

- 0 = Pin selected with COGxPPS control low level will cause an immediate falling event

GxFIS0 = 0:

Pin selected with COGxPPS control has no effect on falling event

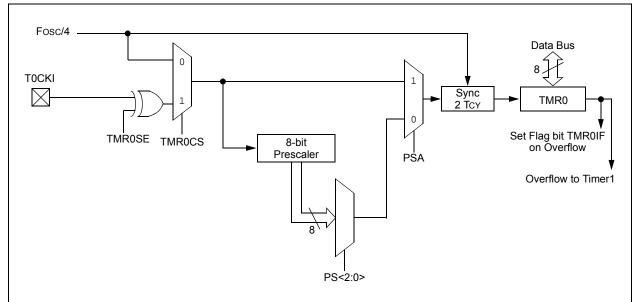

#### 25.0 TIMERO MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- · 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 25-1 is a block diagram of the Timer0 module.

### 25.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 25.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note:

The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 25.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

#### FIGURE 25-1: BLOCK DIAGRAM OF THE TIMER0

### 29.4 Register Definitions: CCP Control

#### REGISTER 29-1: CCPxCON: CCPx CONTROL REGISTER

| U-0   | U-0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----------|---------|---------|---------|---------|---------|

| _     | _   | DCxB<1:0> |         |         | CCPxI   | √<3:0>  |         |

| bit 7 |     |           |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits

Capture mode:

Unused

Compare mode:

Unused

PWM mode:

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

bit 3-0 CCPxM<3:0>: CCPx Mode Select bits

11xx = PWM mode

1011 = Compare mode: Auto-conversion Trigger (sets CCPxIF bit), starts ADC conversion if TRIGSEL = CCPx (see Register 21-3)

1010 = Compare mode: generate software interrupt only

1001 = Compare mode: clear output on compare match (set CCPxIF)

1000 = Compare mode: set output on compare match (set CCPxIF)

0111 = Capture mode: every 16th rising edge

0110 = Capture mode: every 4th rising edge

0101 = Capture mode: every rising edge

0100 = Capture mode: every falling edge

0011 = Reserved

0010 = Compare mode: toggle output on match

0001 = Reserved

0000 = Capture/Compare/PWM off (resets CCPx module)

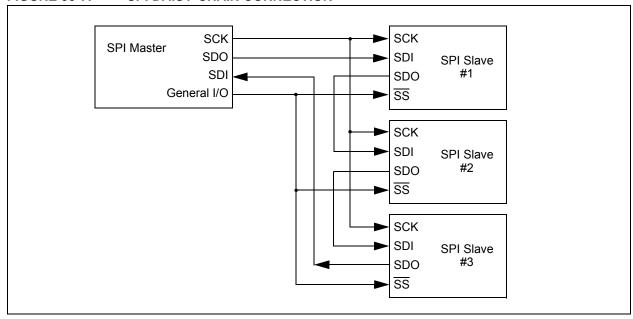

## 30.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100).

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode with \$\overline{SS}\$ pin control enabled (SSPCON1<3:0> = 0100), the SPI module will reset if the \$\overline{SS}\$ pin is set to VDD.

- 2: When the SPI is used in Slave mode with CKE set; the user must enable SS pin control.

- **3:** While operated in SPI Slave mode the SMP bit of the SSPSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

FIGURE 30-7: SPI DAISY-CHAIN CONNECTION

#### 30.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an I<sup>2</sup>C slave in 7-bit Addressing mode. Figure 30-14 and Figure 30-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish I<sup>2</sup>C communication.

- 1. Start bit detected.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit clear is received.

- The slave pulls SDA low sending an ACK to the master, and sets SSPIF bit.

- 5. Software clears the SSPIF bit.

- Software reads received address from SSPBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- Slave drives SDA low sending an ACK to the master, and sets SSPIF bit.

- 10. Software clears SSPIF.

- Software reads the received byte from SSPBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the master.

- Master sends Stop condition, setting P bit of SSPSTAT, and the bus goes idle.

### 30.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus™ that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for I<sup>2</sup>C communication. Figure 30-16 displays a module using both address and data holding. Figure 30-17 includes the operation with the SEN bit of the SSPCON2 register set

- 1. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPIF.

- Slave can look at the ACKTIM bit of the SSPCON3 register to <u>determine</u> if the SSPIF was after or before the ACK.

- Slave reads the address value from SSPBUF, clearing the BF flag.

- Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPIF is set after an ACK, not after a NACK.

- If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPIF.

Note: SSPIF is still set after the 9th falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSPIF not set

- 11. SSPIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an  $\overline{ACK}$  = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

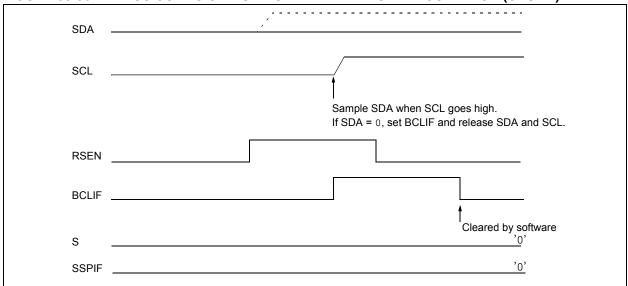

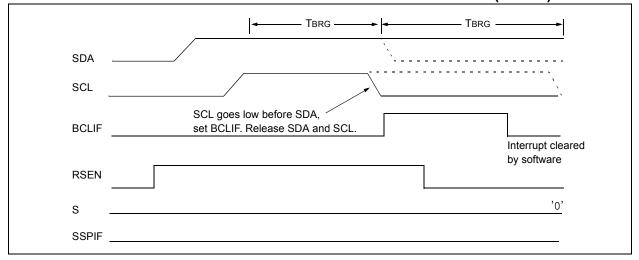

## 30.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 30-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 30-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 30-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

FIGURE 30-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

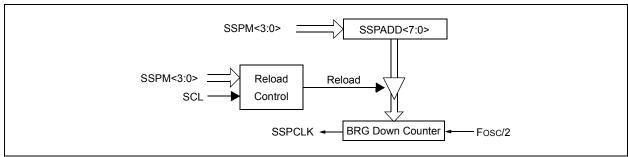

#### 30.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both  $I^2C$  and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPADD register (Register 30-6). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 30-40 triggers the value from SSPADD to be loaded into the BRG counter. This occurs twice for each oscillation of the module

clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 30-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### **EQUATION 30-1:**

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

#### FIGURE 30-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSPADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

TABLE 30-4: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 34-4 to ensure the system is designed to support IOL requirements.

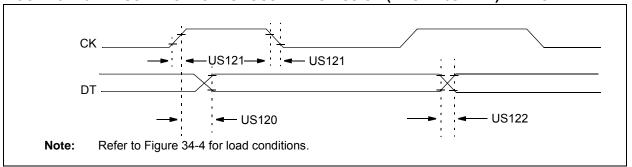

FIGURE 34-15: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 34-22: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                              |                                                 |      |      |                              |                                                  |

|---------------------------------------------------------|------------------------------|-------------------------------------------------|------|------|------------------------------|--------------------------------------------------|

| Param.<br>No.                                           | Symbol                       | Characteristic                                  | Min. | Max. | Units                        | Conditions                                       |

| US120 TCKH2DTV                                          | SYNC XMIT (Master and Slave) | _                                               | 80   | ns   | $3.0V \leq V_{DD} \leq 5.5V$ |                                                  |

|                                                         |                              | Clock high to data-out valid                    | _    | 100  | ns                           | $1.8V \le VDD \le 5.5V$                          |

| US121                                                   | TCKRF                        | Clock out rise time and fall time (Master mode) | _    | 45   | ns                           | $3.0 \text{V} \leq \text{VDD} \leq 5.5 \text{V}$ |

|                                                         |                              |                                                 | _    | 50   | ns                           | $1.8V \leq V \text{DD} \leq 5.5V$                |

| US122                                                   | TDTRF                        | Data-out rise time and fall time                | _    | 45   | ns                           | $3.0 \text{V} \leq \text{VDD} \leq 5.5 \text{V}$ |

|                                                         |                              |                                                 | _    | 50   | ns                           | $1.8V \leq V_{DD} \leq 5.5V$                     |

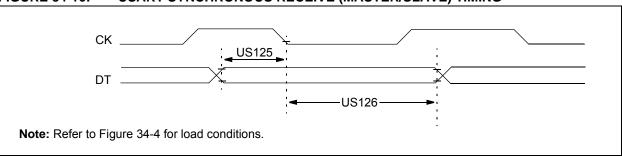

FIGURE 34-16: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

**TABLE 34-23: USART SYNCHRONOUS RECEIVE REQUIREMENTS**

| Standard Operating Conditions (unless otherwise stated) |          |                                                                   |      |      |       |            |

|---------------------------------------------------------|----------|-------------------------------------------------------------------|------|------|-------|------------|

| Param.<br>No.                                           | Symbol   | Characteristic                                                    | Min. | Max. | Units | Conditions |

| US125                                                   | TDTV2CKL | SYNC RCV (Master and Slave) Data-setup before CK ↓ (DT hold time) | 10   | _    | ns    |            |

| US126                                                   | TCKL2DTL | Data-hold after CK ↓ (DT hold time)                               | 15   | _    | ns    |            |

**Note:** Unless otherwise noted, VIN = 5V, FOSC = 300 kHz, CIN = 0.1  $\mu F$ , TA = 25°C.

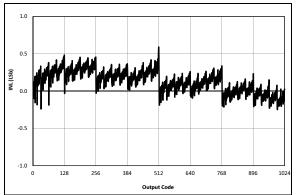

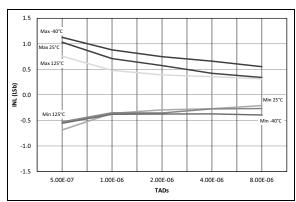

**FIGURE 35-79:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V,  $TAD = 1 \mu S$ ,  $25^{\circ}C$ .

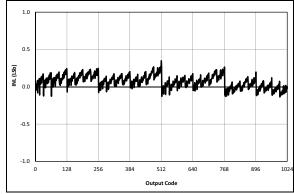

FIGURE 35-80: ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $4 \mu$ S, 25°C.

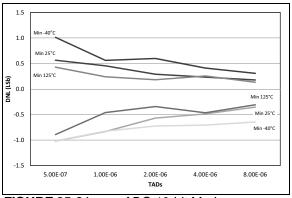

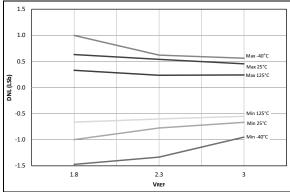

FIGURE 35-81: ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

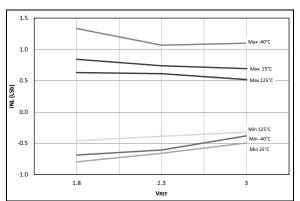

FIGURE 35-82: ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, VREF = 3.0V.

**FIGURE 35-83:** ADC 10-bit Mode, Single-Ended DNL, VDD = 3.0V,  $TAD = 1 \mu S$ .

**FIGURE 35-84:** ADC 10-bit Mode, Single-Ended INL, VDD = 3.0V, TAD = 1  $\mu$ S.

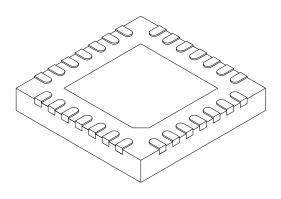

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**ote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | MILLIMETERS |      |      |

|-------------------------|--------|-------------|------|------|

| Dimension               | Limits | MIN         | NOM  | MAX  |

| Number of Pins          | Z      | 28          |      |      |

| Pitch                   | е      | 0.65 BSC    |      |      |

| Overall Height          | Α      | 0.80        | 0.90 | 1.00 |

| Standoff                | A1     | 0.00        | 0.02 | 0.05 |

| Terminal Thickness      | A3     | 0.20 REF    |      |      |

| Overall Width           | Ш      | 6.00 BSC    |      |      |

| Exposed Pad Width       | E2     | 3.65        | 3.70 | 4.20 |

| Overall Length          | О      | 6.00 BSC    |      |      |

| Exposed Pad Length      | D2     | 3.65        | 3.70 | 4.20 |

| Terminal Width          | b      | 0.23        | 0.30 | 0.35 |

| Terminal Length         | Г      | 0.50        | 0.55 | 0.70 |

| Terminal-to-Exposed Pad | K      | 0.20        | -    | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2