#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

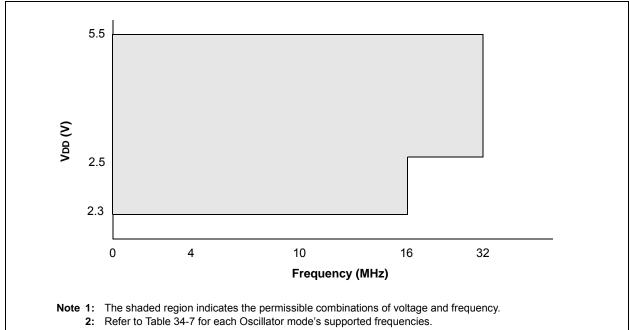

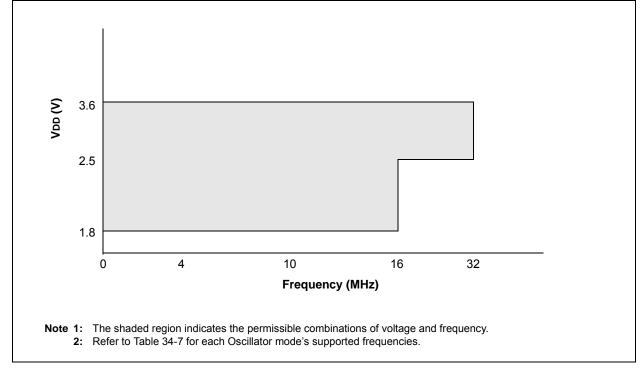

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1713-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

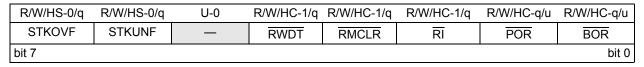

## 5.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

## 5.14 Register Definitions: Power Control

### REGISTER 5-2: PCON: POWER CONTROL REGISTER

| dware                | HS = Bit is set by hardware                           |

|----------------------|-------------------------------------------------------|

| W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '0' = Bit is cleared | q = Value depends on condition                        |

|                      | W = Writable bit<br>x = Bit is unknown                |

| bit 7 | STKOVF: Stack Overflow Flag bit                                                                   |

|-------|---------------------------------------------------------------------------------------------------|

|       | 1 = A Stack Overflow occurred                                                                     |

|       | 0 = A Stack Overflow has not occurred or cleared by firmware                                      |

| bit 6 | STKUNF: Stack Underflow Flag bit                                                                  |

|       | 1 = A Stack Underflow occurred                                                                    |

|       | 0 = A Stack Underflow has not occurred or cleared by firmware                                     |

| bit 5 | Unimplemented: Read as '0'                                                                        |

| bit 4 | RWDT: Watchdog Timer Reset Flag bit                                                               |

|       | 1 = A Watchdog Timer Reset has not occurred or set to '1' by firmware                             |

|       | 0 = A Watchdog Timer Reset has occurred (cleared by hardware)                                     |

| bit 3 | RMCLR: MCLR Reset Flag bit                                                                        |

|       | 1 = A $\overline{\text{MCLR}}$ Reset has not occurred or set to '1' by firmware                   |

|       | 0 = A MCLR Reset has occurred (cleared by hardware)                                               |

| bit 2 | RI: RESET Instruction Flag bit                                                                    |

|       | 1 = A RESET instruction has not been executed or set to '1' by firmware                           |

|       | 0 = A RESET instruction has been executed (cleared by hardware)                                   |

| bit 1 | POR: Power-on Reset Status bit                                                                    |

|       | 1 = No Power-on Reset occurred                                                                    |

|       | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)             |

| bit 0 | BOR: Brown-out Reset Status bit                                                                   |

|       | 1 = No Brown-out Reset occurred                                                                   |

|       | 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset |

|       | occurs)                                                                                           |

The PCON register bits are shown in Register 5-2.

#### 6.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 6-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 6-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 6-1.

Start-up delay specifications are located in the oscillator tables of **Section 34.0** "**Electrical Specifications**".

| R/W-0/0        | R/W-0/0                               | R-0/0                            | R-0/0           | R/W-0/0           | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|---------------------------------------|----------------------------------|-----------------|-------------------|------------------|------------------|--------------|

| TMR1GI         | F ADIF                                | RCIF                             | TXIF            | SSP1IF            | CCP1IF           | TMR2IF           | TMR1IF       |

| bit 7          |                                       |                                  |                 |                   |                  | •                | bit C        |

|                |                                       |                                  |                 |                   |                  |                  |              |

| Legend:        |                                       |                                  |                 |                   |                  |                  |              |

| R = Reada      | ıble bit                              | W = Writable                     | bit             | U = Unimpler      | mented bit, read | l as '0'         |              |

| u = Bit is u   | nchanged                              | x = Bit is unk                   | nown            | -n/n = Value a    | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is : | set                                   | ʻ0' = Bit is cle                 | ared            |                   |                  |                  |              |

|                |                                       |                                  |                 |                   |                  |                  |              |

| bit 7          |                                       | Timer1 Gate Inte                 | rrupt Flag bit  |                   |                  |                  |              |

|                | 1 = Interrup                          | t is pending<br>t is not pending |                 |                   |                  |                  |              |

| bit 6          | •                                     | og-to-Digital Con                | verter (ADC)    | Interrunt Elag h  | sit              |                  |              |

|                | 1 = Interrup                          |                                  |                 | interrupt i lag t |                  |                  |              |

|                |                                       | t is not pending                 |                 |                   |                  |                  |              |

| bit 5          | RCIF: USA                             | RT Receive Inter                 | rupt Flag bit   |                   |                  |                  |              |

|                | 1 = Interrup                          |                                  |                 |                   |                  |                  |              |

|                |                                       | t is not pending                 |                 |                   |                  |                  |              |

| bit 4          |                                       | RT Transmit Inte                 | rupt Flag bit   |                   |                  |                  |              |

|                | 1 = Interrup<br>0 = Interrup          | t is not pending                 |                 |                   |                  |                  |              |

| bit 3          | •                                     | nchronous Seria                  | I Port (MSSP    | ) Interrupt Flag  | bit              |                  |              |

|                | 1 = Interrup                          |                                  | ,               | , 1 0             |                  |                  |              |

|                | 0 = Interrup                          | t is not pending                 |                 |                   |                  |                  |              |

| bit 2          |                                       | CP1 Interrupt Fla                | ig bit          |                   |                  |                  |              |

|                | 1 = Interrup                          | t is pending<br>t is not pending |                 |                   |                  |                  |              |

| bit 1          | •                                     | mer2 to PR2 Inte                 | rrunt Elag hit  |                   |                  |                  |              |

|                | 1 = Interrup                          |                                  | inupi nag bit   |                   |                  |                  |              |

|                |                                       | t is not pending                 |                 |                   |                  |                  |              |

| bit 0          | TMR1IF: Tir                           | mer1 Overflow Ir                 | nterrupt Flag b | pit               |                  |                  |              |

|                | 1 = Interrup                          |                                  |                 |                   |                  |                  |              |

|                | 0 = Interrup                          | t is not pending                 |                 |                   |                  |                  |              |

| Note:          | Interrupt flag bits                   | are set when ar                  | interrupt       |                   |                  |                  |              |

|                | condition occurs,                     |                                  |                 |                   |                  |                  |              |

|                | its corresponding<br>Enable bit, GIE, |                                  |                 |                   |                  |                  |              |

|                | User software                         | should ens                       |                 |                   |                  |                  |              |

|                | appropriate inte                      |                                  | are clear       |                   |                  |                  |              |

|                | prior to enabling                     | an interrupt.                    |                 |                   |                  |                  |              |

## REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELC  | ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | -       | -       | 131                 |

| INLVLC  | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 132                 |

| LATC    | LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 130                 |

| ODCONC  | ODC7    | ODC6    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    | 132                 |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 130                 |

| SLRCONC | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 132                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 130                 |

| WPUC    | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 131                 |

TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

#### REGISTER 18-12: COGxBLKR: COG RISING EVENT BLANKING COUNT REGISTER

| U-0              | U-0   | R/W-x/u           | R/W-x/u                                                                 | R/W-x/u      | R/W-x/u          | R/W-x/u  | R/W-x/u |  |  |  |  |

|------------------|-------|-------------------|-------------------------------------------------------------------------|--------------|------------------|----------|---------|--|--|--|--|

| —                | —     |                   | GxBLKR<5:0>                                                             |              |                  |          |         |  |  |  |  |

| bit 7            |       |                   |                                                                         |              |                  |          | bit 0   |  |  |  |  |

|                  |       |                   |                                                                         |              |                  |          |         |  |  |  |  |

| Legend:          |       |                   |                                                                         |              |                  |          |         |  |  |  |  |

| R = Readable b   | oit   | W = Writable I    | bit                                                                     | U = Unimplen | nented bit, read | l as '0' |         |  |  |  |  |

| u = Bit is uncha | anged | x = Bit is unkn   | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset |              |                  |          |         |  |  |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | '0' = Bit is cleared q = Value depends on condition                     |              |                  |          |         |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-0 GxBLKR<5:0>: Rising Event Blanking Count Value bits

= Number of COGx clock periods to inhibit falling event inputs

#### REGISTER 18-13: COGxBLKF: COG FALLING EVENT BLANKING COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|--|--|--|

| —     | _   |         | GxBLKF<5:0> |         |         |         |         |  |  |  |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 GxBLKF<5:0>: Falling Event Blanking Count Value bits

= Number of COGx clock periods to inhibit rising event inputs

| Name     | Bit 7   | Bit 6   | Bit 5   | Bit 4      | Bit 3   | Bit 2       | Bit 1     | Bit 0   | Register<br>on Page |

|----------|---------|---------|---------|------------|---------|-------------|-----------|---------|---------------------|

| ANSELA   | _       | -       | ANSA5   | ANSA4      | ANSA3   | ANSA2       | ANSA1     | ANSA0   | 120                 |

| ANSELB   | _       | _       | ANSB5   | ANSB4      | ANSB3   | ANSB2       | ANSB1     | ANSB0   | 126                 |

| ANSELC   | ANSC7   | ANSC6   | ANSC5   | ANSC4      | ANSC3   | ANSC2       | —         | —       | 131                 |

| COG1PHR  | _       | _       |         |            | G1PH    | R<5:0>      |           |         | 201                 |

| COG1PHF  | _       | _       |         |            | G1PH    | F<5:0>      |           |         | 201                 |

| COG1BLKR | _       | _       |         |            | G1BLK   | (R<5:0>     |           |         | 200                 |

| COG1BLKF | _       | _       |         |            | G1BLK   | (F<5:0>     |           |         | 200                 |

| COG1DBR  | _       | _       |         |            | G1DB    | R<5:0>      |           |         | 199                 |

| COG1DBF  | _       | _       |         | G1DBF<5:0> |         |             |           |         |                     |

| COG1RIS  | G1RIS7  | G1RIS6  | G1RIS5  | G1RIS4     | G1RIS3  | G1RIS2      | G1RIS1    | G1RIS0  | 190                 |

| COG1RSIM | G1RSIM7 | G1RSIM6 | G1RSIM5 | G1RSIM4    | G1RSIM3 | G1RSIM2     | G1RSIM1   | G1RSIM0 | 191                 |

| COG1FIS  | G1FIS7  | G1FIS6  | G1FIS5  | G1FIS4     | G1FIS3  | G1FIS2      | G1FIS1    | G1FIS0  | 193                 |

| COG1FSIM | G1FSIM7 | G1FSIM6 | G1FSIM5 | G1FSIM4    | G1FSIM3 | G1FSIM2     | G1FSIM1   | G1FSIM0 | 194                 |

| COG1CON0 | G1EN    | G1LD    | —       | G1CS       | S<1:0>  |             | G1MD<2:0> |         | 188                 |

| COG1CON1 | G1RDBS  | G1FDBS  | _       | _          | G1POLD  | G1POLC      | G1POLB    | G1POLA  | 189                 |

| COG1ASD0 | G1ASE   | G1ARSEN | G1ASDI  | BD<1:0>    | G1ASD   | AC<1:0>     | —         | —       | 196                 |

| COG1ASD1 | _       |         | -       | _          | G1AS3E  | G1AS2E      | G1AS1E    | G1AS0E  | 197                 |

| COG1STR  | G1SDATD | G1SDATC | G1SDATB | G1SDATA    | G1STRD  | G1STRC      | G1STRB    | G1STRA  | 198                 |

| INTCON   | GIE     | PEIE    | T0IE    | INTE       | IOCIE   | TOIF        | INTF      | IOCIF   | 83                  |

| COG1PPS  | _       | —       | —       |            |         | COG1PPS<4:0 | >         |         | 136                 |

| PIE2     | OSFIE   | C2IE    | C1IE    | _          | BCL1IE  | TMR6IE      | TMR4IE    | CCP2IE  | 85                  |

| PIR2     | OSFIF   | C2IF    | C1IF    | —          | BCL1IF  | TMR6IF      | TMR4IF    | CCP2IF  | 88                  |

| RxyPPS   | _       | _       | _       |            | •       | RxyPPS<4:0> | •         | •       | 137                 |

### TABLE 18-2: SUMMARY OF REGISTERS ASSOCIATED WITH COG

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by COG

υ

C16(L)

)F1713/6

© 2013-2016 Microchip Technology Inc

## 23.6 Register Definitions: DAC Control

| R/W-0/0          | U-0                                                                      | R/W-0/0                                                    | R/W-0/0          | R/W-0/0         | R/W-0/0            | U-0              | R/W-0/0 |

|------------------|--------------------------------------------------------------------------|------------------------------------------------------------|------------------|-----------------|--------------------|------------------|---------|

| DAC1EN           |                                                                          | DAC10E1                                                    | DAC10E2          | DAC1P           | 'SS<1:0>           | _                | DAC1NSS |

| bit 7            |                                                                          | •                                                          | •                |                 |                    |                  | bit (   |

| Legend:          |                                                                          |                                                            |                  |                 |                    |                  |         |

| R = Readable b   | bit                                                                      | W = Writable b                                             | it               | U = Unimpleme   | ented bit, read as | '0'              |         |

| u = Bit is uncha | nged                                                                     | x = Bit is unkno                                           | wn               | -n/n = Value at | POR and BOR/V      | alue at all othe | Resets  |

| '1' = Bit is set |                                                                          | '0' = Bit is clear                                         | ed               |                 |                    |                  |         |

| bit 7            | <b>DAC1EN:</b> DAC<br>1 = DAC is en<br>0 = DAC is dis                    | abled                                                      |                  |                 |                    |                  |         |

| bit 6            | Unimplemente                                                             | d: Read as '0'                                             |                  |                 |                    |                  |         |

| bit 5            | 1 = DAC volta                                                            | C1 Voltage Outp<br>ge level is also a<br>ge level is disco | in output on the | •               |                    |                  |         |

| bit 4            | 1 = DAC volta                                                            | C1 Voltage Outp<br>ge level is also a<br>ge level is disco | in output on the | •               |                    |                  |         |

| bit 3-2          | DAC1PSS<1:0<br>11 = Reserve<br>10 = FVR Buf<br>01 = VREF+ pi<br>00 = VDD | fer2 output                                                | e Source Select  | bits            |                    |                  |         |

| bit 1            | Unimplemente                                                             | d: Read as '0'                                             |                  |                 |                    |                  |         |

| bit 0            | <b>DAC1NSS:</b> DA<br>1 = VREF- pin<br>0 = VSS                           | C1 Negative So                                             | urce Select bits |                 |                    |                  |         |

#### REGISTER 23-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

### REGISTER 23-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |  |

|---------|------------|---------|---------|---------|---------|---------|---------|--|--|--|--|--|

|         | DAC1R<7:0> |         |         |         |         |         |         |  |  |  |  |  |

| bit 7   |            |         |         |         |         |         | bit 0   |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 DAC1R<7:0>: DAC1 Voltage Output Select bits

### TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

| Name     | Bit 7      | Bit 6 | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1 | Bit 0   | Register<br>on page |

|----------|------------|-------|---------|---------|--------|---------|-------|---------|---------------------|

| DAC1CON0 | DAC1EN     | _     | DAC10E1 | DAC10E2 | DAC1PS | SS<1:0> |       | DAC1NSS | 249                 |

| DAC1CON1 | DAC1R<7:0> |       |         |         |        |         |       | 249     |                     |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

<sup>© 2013-2016</sup> Microchip Technology Inc.

The pull-up and pull-down resistor values are significantly affected by small variations of ZCPINV. Measuring ZCPINV can be difficult, especially when the waveform is relative to VDD. However, by combining Equations 28-2 and 28-3, the resistor value can be determined from the time difference between the ZCDx\_output high and low periods. Note that the time difference,  $\Delta T$ , is 4\*TOFFSET. The equation for determining the pull-up and pull-down resistor values from the high and low ZCDx\_output periods is shown in Equation 28-4. The ZCDx\_output signal can be directly observed on a pin by routing the ZCDx\_output signal through one of the CLCs.

### **EQUATION 28-4:**

$$R = RSERIES\left(\frac{VBIAS}{VPEAK\left(\sin\left(\pi Freq\frac{(\Delta T)}{2}\right)\right)} - 1\right)$$

R is pull-up or pull-down resistor.

VBIAS is VPULLUP when R is pull-up or VDD when R is pull-down.

$\Delta T$  is the ZCDOUT high and low period difference.

## 28.6 Handling VPEAK Variations

If the peak amplitude of the external voltage is expected to vary, the series resistor must be selected to keep the ZCD current source and sink below the design maximum range of  $\pm 600 \ \mu$ A and above a reasonable minimum range. A general rule of thumb is that the maximum peak voltage can be no more than six times the minimum peak voltage. To ensure that the maximum current does not exceed  $\pm 600 \ \mu$ A and the minimum is at least  $\pm 100 \ \mu$ A, compute the series resistance as shown in Equation 28-5. The compensating pull-up for this series resistance can be determined with Equation 28-3 because the pull-up value is independent from the peak voltage.

## EQUATION 28-5: SERIES R FOR V RANGE

$$RSERIES = \frac{VMAXPEAK + VMINPEAK}{7 \times 10^{-4}}$$

## 28.7 Operation During Sleep

The ZCD current sources and interrupts are unaffected by Sleep.

## 28.8 Effects of a Reset

The ZCD circuit can be configured to default to the active or inactive state on Power-on Reset (POR). When the ZCDDIS Configuration bit is cleared, the ZCD circuit will be active at POR. When the ZCDDIS Configuration bit is set, the ZCDxEN bit of the ZCDxCON register must be set to enable the ZCD module.

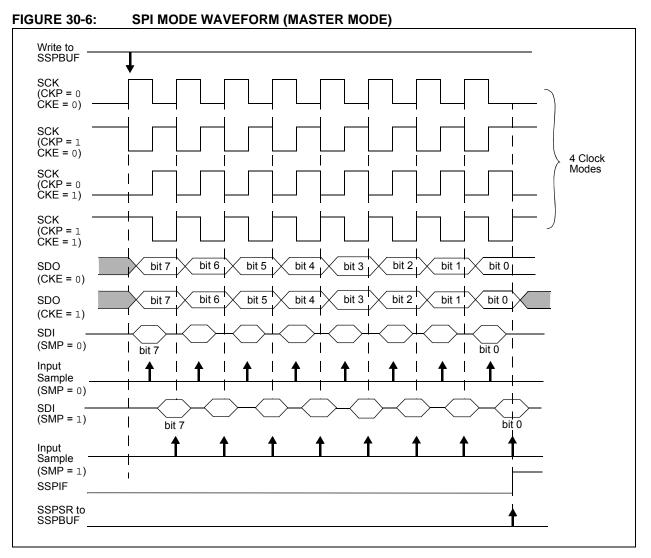

#### 30.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 30-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPCON3 register will enable writes to the SSPBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

## 30.8 Register Definitions: MSSP Control

## REGISTER 30-1: SSP1STAT: SSP STATUS REGISTER

| R/W-0/0           | R/W-0/0                                  | R-0/0                                                                                                               | R-0/0             | R-0/0                                    | R-0/0                | R-0/0                | R-0/0         |  |  |  |  |

|-------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------|----------------------|----------------------|---------------|--|--|--|--|

| SMP               | CKE                                      | D/A                                                                                                                 | Р                 | S                                        | R/W                  | UA                   | BF            |  |  |  |  |

| bit 7             |                                          |                                                                                                                     |                   |                                          |                      |                      | bit 0         |  |  |  |  |

|                   |                                          |                                                                                                                     |                   |                                          |                      |                      |               |  |  |  |  |

| Legend:           |                                          |                                                                                                                     |                   |                                          |                      |                      |               |  |  |  |  |

| R = Readable bi   |                                          | W = Writable b                                                                                                      |                   | •                                        | ented bit, read as   |                      |               |  |  |  |  |

| u = Bit is unchar | nged                                     | x = Bit is unkno                                                                                                    |                   | -n/n = Value a                           | t POR and BOR/       | /alue at all other F | Resets        |  |  |  |  |

| '1' = Bit is set  |                                          | '0' = Bit is clea                                                                                                   | red               |                                          |                      |                      |               |  |  |  |  |

| L:4 7             |                                          | lanut Camala b                                                                                                      |                   |                                          |                      |                      |               |  |  |  |  |

| bit 7             |                                          | Input Sample b                                                                                                      | It                |                                          |                      |                      |               |  |  |  |  |

|                   | <u>SPI Master mo</u><br>1 = Input data : | <u>de.</u><br>sampled at end d                                                                                      | of data output ti | ime                                      |                      |                      |               |  |  |  |  |

|                   |                                          | sampled at midd                                                                                                     |                   |                                          |                      |                      |               |  |  |  |  |

|                   | SPI Slave mod                            |                                                                                                                     |                   |                                          |                      |                      |               |  |  |  |  |

|                   | _                                        | cleared when SP                                                                                                     | l is used in Sla  | ve mode                                  |                      |                      |               |  |  |  |  |

|                   | In I <sup>2</sup> C Master c             |                                                                                                                     | for Standard Si   | beed mode (100                           | kHz and 1 MHz)       |                      |               |  |  |  |  |

|                   |                                          |                                                                                                                     |                   | mode (400 kHz)                           | _,                   |                      |               |  |  |  |  |

| bit 6             | CKE: SPI Cloc                            | k Edge Select bi                                                                                                    | t (SPI mode or    | lly)                                     |                      |                      |               |  |  |  |  |

|                   | In SPI Master of                         |                                                                                                                     |                   |                                          |                      |                      |               |  |  |  |  |

|                   |                                          |                                                                                                                     |                   | o Idle clock state<br>active clock state |                      |                      |               |  |  |  |  |

|                   | -                                        |                                                                                                                     |                   | active clock state                       |                      |                      |               |  |  |  |  |

|                   |                                          | In I <sup>2</sup> C™ mode only:<br>1 = Enable input logic so that thresholds are compliant with SMBus specification |                   |                                          |                      |                      |               |  |  |  |  |

|                   |                                          | Bus specific inp                                                                                                    |                   |                                          |                      |                      |               |  |  |  |  |

| bit 5             |                                          | ress bit (I <sup>2</sup> C mod                                                                                      |                   |                                          |                      |                      |               |  |  |  |  |

|                   |                                          |                                                                                                                     |                   | nsmitted was data<br>Insmitted was add   |                      |                      |               |  |  |  |  |

| bit 4             | P: Stop bit                              | lat the last byte                                                                                                   |                   |                                          | 1635                 |                      |               |  |  |  |  |

| Dit 4             | •                                        | This hit is clear                                                                                                   | ed when the M     | SSP module is d                          | isabled, SSPEN i     | s cleared )          |               |  |  |  |  |

|                   |                                          |                                                                                                                     |                   | last (this bit is '                      |                      | o olcarea.)          |               |  |  |  |  |

|                   |                                          | s not detected la                                                                                                   |                   | ,                                        | ,                    |                      |               |  |  |  |  |

| bit 3             | S: Start bit                             |                                                                                                                     |                   |                                          |                      |                      |               |  |  |  |  |

|                   |                                          |                                                                                                                     |                   |                                          | isabled, SSPEN i     | s cleared.)          |               |  |  |  |  |

|                   |                                          |                                                                                                                     |                   | d last (this bit is '                    | o' on Reset)         |                      |               |  |  |  |  |

|                   |                                          | s not detected la                                                                                                   |                   |                                          |                      |                      |               |  |  |  |  |

| bit 2             |                                          | te bit information                                                                                                  | •                 | .,                                       | match. This bit is o | any valid from the   | addraga match |  |  |  |  |

|                   | to the next Star                         | t bit, Stop bit, or                                                                                                 | not ACK bit.      | line last audiess                        |                      | only valid from the  | audress match |  |  |  |  |

|                   | In I <sup>2</sup> C Slave me             | ode:                                                                                                                |                   |                                          |                      |                      |               |  |  |  |  |

|                   | 1 = Read<br>0 = Write                    |                                                                                                                     |                   |                                          |                      |                      |               |  |  |  |  |

|                   | In I <sup>2</sup> C Master n             | node:                                                                                                               |                   |                                          |                      |                      |               |  |  |  |  |

|                   | 1 = Transmit i                           | s in progress                                                                                                       |                   |                                          |                      |                      |               |  |  |  |  |

|                   |                                          | s not in progress                                                                                                   |                   |                                          |                      |                      | I -           |  |  |  |  |

|                   | •                                        |                                                                                                                     |                   |                                          | will indicate if the | MSSP is in Idle m    | lode.         |  |  |  |  |

| bit 1             |                                          | ldress bit (10-bit                                                                                                  |                   |                                          | SSPADD register      |                      |               |  |  |  |  |

|                   |                                          | bes not need to b                                                                                                   | •                 |                                          | Sel ADD register     |                      |               |  |  |  |  |

| bit 0             | BF: Buffer Full                          | Status bit                                                                                                          |                   |                                          |                      |                      |               |  |  |  |  |

|                   | Receive (SPI a                           | nd I <sup>2</sup> C modes):                                                                                         |                   |                                          |                      |                      |               |  |  |  |  |

|                   | 1 = Receive co                           | mplete, SSPBU                                                                                                       |                   |                                          |                      |                      |               |  |  |  |  |

|                   |                                          | ot complete, SSP                                                                                                    | BOF is empty      |                                          |                      |                      |               |  |  |  |  |

|                   | <u>Transmit (I<sup>2</sup>C n</u>        | <u>node only):</u>                                                                                                  |                   | 11 <u>+ 017</u> + 0                      |                      |                      |               |  |  |  |  |

|                   | $\perp$ = Data transi                    | nit in prodress (d                                                                                                  | loes not includ   | e the ACK and S                          | top bits), SSPBUF    | - is full            |               |  |  |  |  |

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                   |            |                             |                |            |                             |                |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Foso                                                 | = 32.00    | 0 MHz                       | Fosc = 20.000 MHz |            | Fosc = 18.432 MHz           |                |            | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 26666                       | 300.0             | 0.00       | 16665                       | 300.0          | 0.00       | 15359                       | 300.0          | 0.00       | 9215                        |

| 1200   | 1200                                                 | 0.00       | 6666                        | 1200              | -0.01      | 4166                        | 1200           | 0.00       | 3839                        | 1200           | 0.00       | 2303                        |

| 2400   | 2400                                                 | 0.01       | 3332                        | 2400              | 0.02       | 2082                        | 2400           | 0.00       | 1919                        | 2400           | 0.00       | 1151                        |

| 9600   | 9604                                                 | 0.04       | 832                         | 9597              | -0.03      | 520                         | 9600           | 0.00       | 479                         | 9600           | 0.00       | 287                         |

| 10417  | 10417                                                | 0.00       | 767                         | 10417             | 0.00       | 479                         | 10425          | 0.08       | 441                         | 10433          | 0.16       | 264                         |

| 19.2k  | 19.18k                                               | -0.08      | 416                         | 19.23k            | 0.16       | 259                         | 19.20k         | 0.00       | 239                         | 19.20k         | 0.00       | 143                         |

| 57.6k  | 57.55k                                               | -0.08      | 138                         | 57.47k            | -0.22      | 86                          | 57.60k         | 0.00       | 79                          | 57.60k         | 0.00       | 47                          |

| 115.2k | 115.9k                                               | 0.64       | 68                          | 116.3k            | 0.94       | 42                          | 115.2k         | 0.00       | 39                          | 115.2k         | 0.00       | 23                          |

## TABLE 31-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz                                     |            | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 6666                        | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200                                                 | -0.02      | 1666                        | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |

| 2400   | 2401                                                 | 0.04       | 832                         | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |

| 9600   | 9615                                                 | 0.16       | 207                         | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |

| 10417  | 10417                                                | 0          | 191                         | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k                                               | 0.16       | 103                         | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 57.14k                                               | -0.79      | 34                          | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | —                | _          | _                           |

| 115.2k | 117.6k                                               | 2.12       | 16                          | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | _                | _          | _                           |

### 31.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSEL bit must be        |

|       | cleared for the receiver to function.      |

### 31.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

### 31.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 31.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

## 31.5.1.9 Synchronous Master Reception Setup:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

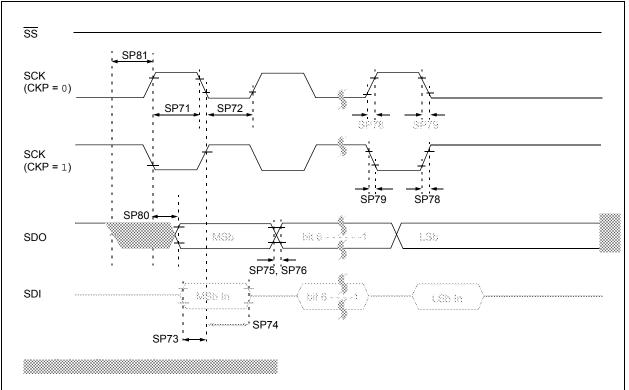

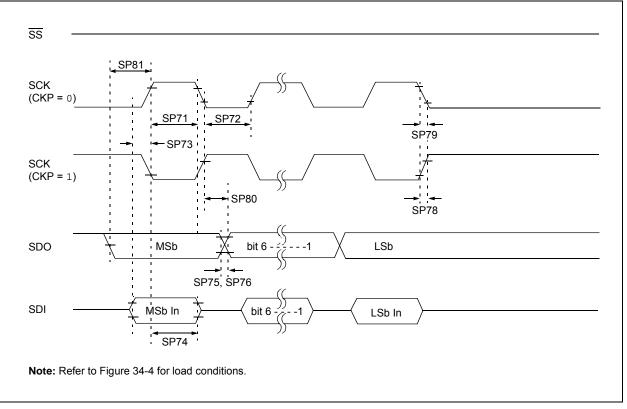

### FIGURE 34-18: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

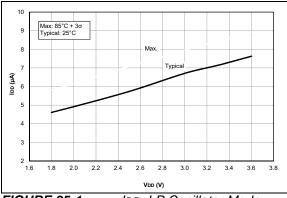

FIGURE 35-1: IDD, LP Oscillator Mode, Fosc = 32 kHz, PIC16LF1713/6 Only.

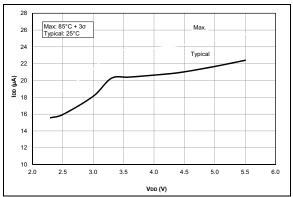

**FIGURE 35-2:** IDD, LP Oscillator Mode, Fosc = 32 kHz, PIC16F1713/6 Only.

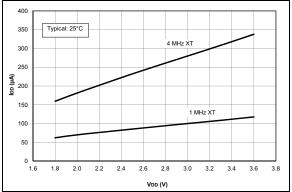

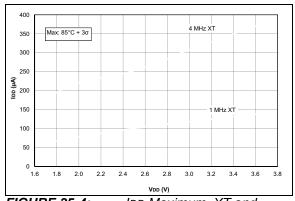

FIGURE 35-3: IDD Typical, XT and EXTRC Oscillator, PIC16LF1713/6 Only.

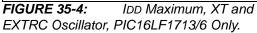

FIGURE 35-5: IDD Typical, XT and EXTRC Oscillator, PIC16F1713/6 Only.

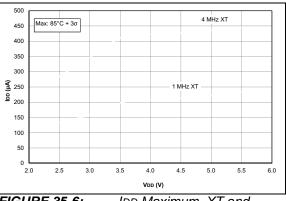

FIGURE 35-6: IDD Maximum, XT and EXTRC Oscillator, PIC16F1713/6 Only.

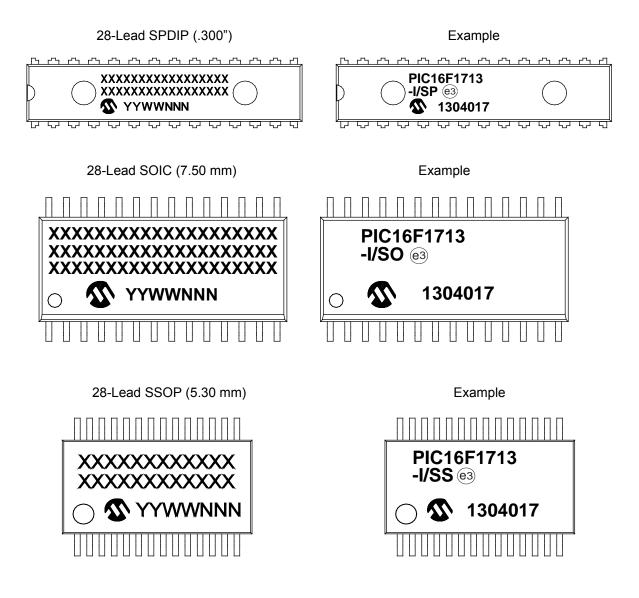

## **37.0 PACKAGING INFORMATION**

## 37.1 Package Marking Information

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carried                                | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>for customer-specific information.                                                                                                                                                                                                           |