#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1713-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 3-9:PIC16(L)F1713/6 MEMORY<br/>MAP, BANK 31

|         | Bank 31                            |                      |

|---------|------------------------------------|----------------------|

| F8Ch    |                                    |                      |

|         | Unimplemented<br>Read as '0'       |                      |

| FE3h    |                                    |                      |

| FE4h    | STATUS_SHAD                        |                      |

| FE5h    | WREG_SHAD                          |                      |

| FE6h    | BSR_SHAD                           |                      |

| FE7h    | PCLATH_SHAD                        |                      |

| FE8h    | FSR0L_SHAD                         |                      |

| FE9h    | FSR0H_SHAD                         |                      |

| FEAh    | FSR1L_SHAD                         |                      |

| FEBh    | FSR1H_SHAD                         |                      |

| FECh    | —                                  |                      |

| FEDh    | STKPTR                             |                      |

| FEEh    | TOSL                               |                      |

| FEFh    | TOSH                               |                      |

| FF0h    | _                                  |                      |

| FFFh    |                                    |                      |

| Legend: | = Unimplemented da<br>read as '0', | ta memory locations, |

# PIC16(L)F1713/6

### TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr | Name     | Bit 7       | Bit 6          | Bit 5          | Bit 4         | Bit 3          | Bit 2     | Bit 1      | Bit 0    | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------|----------|-------------|----------------|----------------|---------------|----------------|-----------|------------|----------|----------------------|---------------------------------|

| Banl | k 2      |             | •              | •              |               |                | •         | •          | •        | •                    | •                               |

| 10Ch | LATA     | LATA7       | LATA6          | LATA5          | LATA4         | LATA3          | LATA2     | LATA1      | LATA0    | XXXX XXXX            | uu -uuu                         |

| 10Dh | LATB     | LATB7       | LATB6          | LATB5          | LATB4         | LATB3          | LATB2     | LATB1      | LATB0    | xxxx xxxx            | uuuu                            |

| 10Eh | LATC     | LATC7       | LATC6          | LATC5          | LATC4         | LATC3          | LATC2     | LATC1      | LATC0    | xxxx xxxx            | uuuu uuuu                       |

| 10Fh | —        | Unimplement | ted            |                |               |                |           |            |          | _                    | _                               |

| 110h | —        | Unimplement | ted            |                |               |                |           |            |          | _                    | _                               |

| 111h | CM1CON0  | C10N        | C10UT          | _              | C1POL         | C1ZLF          | C1SP      | C1HYS      | C1SYNC   | 00-0 0100            | 00-0 0100                       |

| 112h | CM1CON1  | C1INTP      | C1INTN         |                | C1PCH<2:0>    |                |           | C1NCH<2:0> | >        | 0000 0000            | 0000 0000                       |

| 113h | CM2CON0  | C2ON        | C2OUT          | _              | C2POL         | C2ZLF          | C2SP      | C2HYS      | C2SYNC   | 00-0 0100            | 00-0 0100                       |

| 114h | CM2CON1  | C2INTP      | C2INTN         |                | C2PCH<2:0>    |                |           | C2NCH<2:0> | >        | 0000 0000            | 0000 0000                       |

| 115h | CMOUT    | _           | _              | _              | _             | _              | _         | MC2OUT     | MC10UT   | 00                   | 00                              |

| 116h | BORCON   | SBOREN      | BORFS          | _              | _             | _              | _         | _          | BORRDY   | 10q                  | uuu                             |

| 117h | FVRCON   | FVREN       | FVRRDY         | TSEN           | TSRNG         | CDAFV          | /R<1:0>   | ADFV       | 'R<1:0>  | 0q00 0000            | 0q00 0000                       |

| 118h | DAC1CON0 | DAC1EN      |                | DAC10E1        | DAC10E2       | DAC1P          | SS<1:0>   |            | DAC1NSS  | 0-00 00-0            | 0-00 00-0                       |

| 119h | DAC1CON1 |             |                |                | DAC1          | R<7:0>         |           |            |          | 0000 0000            | 0000 0000                       |

| 11Ah | DAC2CON0 | DAC2EN      | —              | DAC2OE1        | DAC2OE2       | DAC2PS         | SS<1:0>   | —          | DAC2NSS  | 0-00 00-0            | 0-00 00-0                       |

| 11Bh | DAC2CON1 | _           |                |                |               |                | DAC2R<4:0 | >          |          | 0 0000               | 0 0000                          |

| 11Ch | ZCD1CON  | ZCD1EN      | _              | ZCD10UT        | ZCD1POL       | _              | _         | ZCD1INTP   | ZCD1INTN | 0-x000               | 0-0000                          |

| 11Dh | —        | Unimplement | ted            | •              |               |                | •         | •          | •        | _                    | _                               |

| 11Eh | —        | Unimplement | ted            |                |               |                |           |            |          | _                    | _                               |

| 11Fh | —        | Unimplement | ted            |                |               |                |           |            |          | _                    | _                               |

| Banl | k 3      |             |                |                |               |                |           |            |          |                      |                                 |

| 18Ch | ANSELA   | —           | _              | ANSA5          | ANSA4         | ANSA3          | ANSA2     | ANSA1      | ANSA0    | 11 1111              | 1 1111                          |

| 18Dh | ANSELB   | _           | _              | ANSB5          | ANSB4         | ANSB3          | ANSB2     | ANSB1      | ANSB0    | 11 1111              | 11                              |

| 18Eh | ANSELC   | ANSC7       | ANSC6          | ANSC5          | ANSC4         | ANSC3          | ANSC2     | _          | _        | 1111 11              | 1111 1111                       |

| 18Fh | —        | Unimplement | ted            |                |               |                |           |            |          | —                    | _                               |

| 190h | —        | Unimplement | ted            |                |               |                |           |            |          | —                    | _                               |

| 191h | PMADRL   | Program Mer | mory Address   | Register Low   | Byte          |                |           |            |          | 0000 0000            | 0000 0000                       |

| 192h | PMADRH   | —           | Program Mer    | mory Address   | Register High | Byte           |           |            |          | 1000 0000            | 1000 0000                       |

| 193h | PMDATL   | Program Mer | mory Read Da   | ta Register Lo | w Byte        |                |           |            |          | xxxx xxxx            | uuuu uuuu                       |

| 194h | PMDATH   | —           | _              | Program Mer    | nory Read Da  | ta Register Hi | gh Byte   |            |          | xx xxxx              | uu uuuu                         |

| 195h | PMCON1   | _           | CFGS           | LWLO           | FREE          | WRERR          | WREN      | WR         | RD       | -000 x000            | -000 q000                       |

| 196h | PMCON2   | Program Mer | mory Control F | Register 2     |               |                | •         | •          | •        | 0000 0000            | 0000 0000                       |

| 197h | VREGCON  | —           | _              | _              | _             | _              | —         | VREGPM     | Reserved | 01                   | 01                              |

| 198h | —        | Unimplement | ted            | •              |               |                | •         | •          | •        | _                    | _                               |

| 199h | RC1REG   | USART Rece  | eive Data Regi | ster           |               |                |           |            |          | 0000 0000            | 0000 0000                       |

| 19Ah | TX1REG   | USART Tran  | smit Data Reg  | ister          |               |                |           |            |          | 0000 0000            | 0000 0000                       |

| 19Bh | SP1BRGL  |             |                |                | SP1BF         | RG<7:0>        |           |            |          | 0000 0000            | 0000 0000                       |

| 19Ch | SP1BRGH  |             |                |                | SP1BR         | G<15:8>        |           |            |          | 0000 0000            | 0000 0000                       |

| 19Dh | RC1STA   | SPEN        | RX9            | SREN           | CREN          | ADDEN          | FERR      | OERR       | RX9D     | 0000 0000            | 0000 0000                       |

| 19Eh | TX1STA   | CSRC        | TX9            | TXEN           | SYNC          | SENDB          | BRGH      | TRMT       | TX9D     | 0000 0010            | 0000 0010                       |

| 19Fh | BAUD1CON | ABDOVF      | RCIDL          | _              | SCKP          | BRG16          | —         | WUE        | ABDEN    | 01-0 0-00            | 01-0 0-00                       |

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16(L)F1713/6.

## 5.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 5-3 and Table 5-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | то | PD | Condition                          |  |

|--------|--------|------|-------|----|-----|-----|----|----|------------------------------------|--|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                     |  |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, TO is set on POR          |  |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, PD is set on POR          |  |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                    |  |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                          |  |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep             |  |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep       |  |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation |  |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep            |  |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed         |  |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)  |  |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1) |  |

TABLE 5-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 5-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

| ODB7<br>bit 7 | ODB6 | ODB5 | ODB4 | ODB3 | ODB2 | ODB1 | ODB0<br>bit 0 |

|---------------|------|------|------|------|------|------|---------------|

| bit 7         |      |      |      |      |      |      | bit (         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

ODB<7:0>: PORTB Open-Drain Enable bits

For RB<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

## REGISTER 11-15: SLRCONB: PORTB SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |  |

|----------------------|----------------------|-------------------------------------------------------|--|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |  |

bit 7-0 SLRB<7:0>: PORTB Slew Rate Enable bits

For RB<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### REGISTER 11-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLB<7:0>: PORTB Input Level Select bits

For RB<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

| U-0                  | U-0               | U-0              | R/W-0/u         | R/W-0/u        | R/W-0/u          | R/W-0/u          | R/W-0/u     |

|----------------------|-------------------|------------------|-----------------|----------------|------------------|------------------|-------------|

| _                    | —                 | —                |                 |                | RxyPPS<4:0>      |                  |             |

| pit 7                |                   |                  |                 |                |                  |                  | bi          |

|                      |                   |                  |                 |                |                  |                  |             |

| Legend:              |                   |                  |                 |                |                  |                  |             |

| R = Readab           | ole bit           | W = Writable     | e bit           | U = Unimplen   | nented bit, read | l as '0'         |             |

| u = Bit is unchanged |                   | x = Bit is unl   | known           | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set     |                   | '0' = Bit is cl  | eared           |                |                  |                  |             |

|                      | l lus incur la un | antadi Daad aa   | (o)             |                |                  |                  |             |

| bit 7-5              | -                 | ented: Read as   |                 | laction bita   | DODTA            |                  | DODTO       |

| bit 4-0              | 11xxx = R         | I:0>: Pin Rxy Ou | ilput Source Se | ection bits    | PORTA            | PORTB            | PORTC       |

|                      |                   | xy source is C2  |                 |                | х                |                  | Х           |

|                      |                   | xy source is C2  |                 |                | X                |                  | X           |

|                      |                   | xy source is DT  |                 |                |                  | Х                | Х           |

|                      |                   | xy source is TX  |                 |                |                  | Х                | Х           |

|                      | 10100 = R         |                  | OR              |                |                  |                  |             |

|                      | 10011 = R         |                  |                 |                |                  |                  |             |

|                      |                   | xy source is SD  | (1) مחא         |                |                  | N/               | V           |

|                      |                   | xy source is SC  |                 |                |                  | X<br>X           | X<br>X      |

|                      | 10000 - 10        |                  | NOOL            |                |                  | ~                | ~           |

|                      | 01111 <b>= R</b>  | xy source is PW  | /M4OUT          |                |                  | х                | Х           |

|                      |                   | xy source is PW  |                 |                |                  | Х                | Х           |

|                      |                   | xy source is CC  |                 |                |                  | Х                | Х           |

|                      |                   | xy source is CC  |                 |                |                  | Х                | Х           |

|                      |                   | xy source is CO  |                 |                |                  | Х                | Х           |

|                      |                   | xy source is CO  |                 |                |                  | Х                | Х           |

|                      |                   | xy source is CO  |                 |                |                  | X                | Х           |

|                      |                   | xy source is CO  |                 |                |                  | Х                | Х           |

|                      | 00111 <b>- D</b>  |                  | 1 out           |                |                  |                  | X           |

|                      |                   | xy source is LC  | _               |                |                  | X<br>X           | X           |

|                      |                   | xy source is LC  | _               |                | ×                | X                | X           |

|                      |                   | xy source is LC  | _               |                | X<br>X           |                  | X<br>X      |

|                      |                   | xy source is LC  |                 |                | ×                |                  | X           |

|                      |                   | xy source is NC  | O1_out          |                | X                |                  | χ           |

|                      | 00010 = R         |                  |                 |                |                  |                  |             |

|                      | 00001 = R         |                  |                 |                | Х                | х                | Х           |

|                      | 00000 = R         | xy source is LA  | іху             |                |                  |                  |             |

|                      | Example: F        | RC3PPS = 0x0D    | outputs CCP2    | on RC3         |                  |                  |             |

|                      | Outputs are       | e available only | on those ports  | indicated with |                  |                  |             |

|                      |                   |                  | -               |                |                  |                  |             |

## REGISTER 12-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER

a check.

**Note 1:** TRIS control is overridden by the peripheral as required.

| Name      | Bit 7 | Bit 6 | Bit 5 | Bit 4          | Bit 3          | Bit 2     | Bit 1 | Bit 0     | Register<br>on page |  |  |

|-----------|-------|-------|-------|----------------|----------------|-----------|-------|-----------|---------------------|--|--|

| PPSLOCK   | —     | —     | —     | —              | _              | —         | —     | PPSLOCKED | 138                 |  |  |

| INTPPS    | _     | _     | _     |                |                | INTPPS<4  | :0>   |           | 137                 |  |  |

| TOCKIPPS  | _     | _     | _     |                |                | T0CKIPPS< | 4:0>  |           | 137                 |  |  |

| T1CKIPPS  | _     | _     | _     |                |                | T1CKIPPS< | 4:0>  |           | 137                 |  |  |

| T1GPPS    | _     | _     | _     |                |                | T1GPPS<4  | :0>   |           | 137                 |  |  |

| CCP1PPS   | _     | _     | _     |                |                | CCP1PPS<  | 4:0>  |           | 137                 |  |  |

| CCP2PPS   | _     | _     | _     |                |                | CCP2PPS<  | 4:0>  |           | 137                 |  |  |

| COGINPPS  | _     | _     | _     |                | (              | COGINPPS  | <4:0> |           | 137                 |  |  |

| SSPCLKPPS | _     | _     | _     |                | S              | SPCLKPPS  | <4:0> |           | 137                 |  |  |

| SSPDATPPS | _     | _     | _     |                | S              | SPDATPPS  | <4:0> |           | 137                 |  |  |

| SSPSSPPS  | _     | _     | _     |                | 5              | SSPSSPPS  | <4:0> |           | 137                 |  |  |

| RXPPS     | _     | _     | _     |                |                | RXPPS<4   | :0>   |           | 137                 |  |  |

| CKPPS     | _     | _     | _     |                |                | CKPPS<4   | :0>   |           | 137                 |  |  |

| CLCIN0PPS | _     | _     | _     |                | (              | CLCIN0PPS | <4:0> |           | 137                 |  |  |

| CLCIN1PPS | _     | _     | _     |                | (              | CLCIN1PPS | <4:0> |           | 137                 |  |  |

| CLCIN2PPS | _     | _     |       |                | CLCIN2PPS<4:0> |           |       |           |                     |  |  |

| CLCIN3PPS | _     | _     | _     | CLCIN3PPS<4:0> |                |           |       |           |                     |  |  |

| RA0PPS    | _     | _     |       | RA0PPS<4:0>    |                |           |       |           |                     |  |  |

| RA1PPS    | _     | _     | _     | RA1PPS<4:0>    |                |           |       |           |                     |  |  |

| RA2PPS    | _     | _     | _     | RA2PPS<4:0>    |                |           |       |           |                     |  |  |

| RA4PPS    | _     | _     | _     | RA4PPS<4:0>    |                |           |       |           |                     |  |  |

| RA5PPS    | _     | _     | _     |                |                | RA5PPS<4  | :0>   |           | 137                 |  |  |

| RA6PPS    | _     | _     | _     |                |                | RA6PPS<4  | :0>   |           | 137                 |  |  |

| RA7PPS    | _     | _     | _     |                |                | RA7PPS<4  | :0>   |           | 137                 |  |  |

| RB0PPS    | _     | _     | _     |                |                | RB0PPS<4  | :0>   |           | 137                 |  |  |

| RB1PPS    | _     | _     | _     |                |                | RB1PPS<4  | :0>   |           | 137                 |  |  |

| RB2PPS    | _     | _     | _     |                |                | RB2PPS<4  | :0>   |           | 137                 |  |  |

| RB3PPS    | _     | _     | _     |                |                | RB3PPS<4  | :0>   |           | 137                 |  |  |

| RB4PPS    | _     | _     | _     |                |                | RB4PPS<4  | :0>   |           | 137                 |  |  |

| RB5PPS    | _     | _     | _     |                |                | RB5PPS<4  | :0>   |           | 137                 |  |  |

| RB6PPS    | _     | _     | _     | RB6PPS<4:0>    |                |           |       |           |                     |  |  |

| RB7PPS    | _     | _     | _     | RB7PPS<4:0>    |                |           |       |           |                     |  |  |

| RC0PPS    | _     | _     | _     | RC0PPS<4:0>    |                |           |       |           |                     |  |  |

| RC1PPS    | _     | _     |       |                |                | RC1PPS<4  | :0>   |           | 137                 |  |  |

| RC2PPS    |       | —     | —     |                |                | RC2PPS<4  | :0>   |           | 137                 |  |  |

| RC3PPS    | _     | —     | _     |                |                | RC3PPS<4  | :0>   |           | 137                 |  |  |

| RC4PPS    | _     | _     | _     |                |                | RC4PPS<4  | :0>   |           | 137                 |  |  |

| RC5PPS    | _     | _     | _     |                |                | RC5PPS<4  | :0>   |           | 137                 |  |  |

| RC6PPS    | _     | _     | _     |                |                | RC6PPS<4  | :0>   |           | 137                 |  |  |

| RC7PPS    | _     | _     | _     |                |                | RC7PPS<4  | :0>   |           | 137                 |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the DAC module.

## REGISTER 13-11: IOCEN: INTERRUPT-ON-CHANGE PORTE NEGATIVE EDGE REGISTER

| -         -         -         IOCEN3         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <th>U-0</th> <th>U-0</th> <th>U-0</th> <th>U-0</th> <th>R/W-0/0</th> <th>U-0</th> <th>U-0</th> <th>U-0</th> | U-0   | U-0 | U-0 | U-0 | R/W-0/0 | U-0 | U-0 | U-0   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|-----|---------|-----|-----|-------|

| bit 7 bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —     |     |     | —   | IOCEN3  |     |     | —     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 7 |     |     |     |         |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <ul> <li>IOCEN: Interrupt-on-Change PORTE Negative Edge Enable bits</li> <li>1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCEFx bit and IOCIF flag will be set upon detecting an edge.</li> <li>0 = Interrupt-on-Change disabled for the associated pin</li> </ul> |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                   |

| bit 2-0 | <ul> <li>be set upon detecting an edge.</li> <li>0 = Interrupt-on-Change disabled for the associated pin.</li> </ul>                                                                                                                                                                         |

## REGISTER 13-12: IOCEF: INTERRUPT-ON-CHANGE PORTE FLAG REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|------------|-----|-----|-------|

| —     | —   |     |     | IOCEF3     |     |     | —     |

| bit 7 |     |     |     |            |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <b>IOCEF:</b> Interrupt-on-Change PORTE Flag bits<br>1 = An enabled change was detected on the associated pin.<br>Set when IOCEPx = 1 and a rising edge was detected on REx, or when IOCENx = 1 and a falling edge |

|         | <ul> <li>was detected on REx.</li> <li>0 = No change was detected, or the user cleared the detected change.</li> </ul>                                                                                             |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                                                                                                         |

# 14.3 Register Definitions: FVR Control

## REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|-------------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAFVR<1:0> |         | ADFVI   | R<1:0>  |

| bit 7   | · · · · · ·           |                     |                      |             |         |         | bit 0   |

|         |                       |                     |                      |             |         |         |         |

| Legend:                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                             |                                                                                           |                                                                                                                                                                  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| R = Readable bit                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                             | W = Writable bit                                                                          | U = Unimplemented bit, read as '0'                                                                                                                               |  |  |  |  |

| u = Bit is un                                                                                                                                                                                       | ichanged                                                                                                                                                                                                                                                                                    | x = Bit is unknown                                                                        | -n/n = Value at POR and BOR/Value at all other Resets                                                                                                            |  |  |  |  |

| '1' = Bit is s                                                                                                                                                                                      | et                                                                                                                                                                                                                                                                                          | '0' = Bit is cleared                                                                      | q = Value depends on condition                                                                                                                                   |  |  |  |  |

| bit 7                                                                                                                                                                                               | 1 = Fixed                                                                                                                                                                                                                                                                                   | ixed Voltage Reference Ena<br>Voltage Reference is enable<br>Voltage Reference is disable | ed                                                                                                                                                               |  |  |  |  |

| bit 6 <b>FVRRDY:</b> Fixed Voltage Reference Ready Flag bit <sup>(1)</sup><br>1 = Fixed Voltage Reference output is ready for use<br>0 = Fixed Voltage Reference output is not ready or not enabled |                                                                                                                                                                                                                                                                                             |                                                                                           |                                                                                                                                                                  |  |  |  |  |

| bit 5                                                                                                                                                                                               | <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup><br>1 = Temperature Indicator is enabled<br>0 = Temperature Indicator is disabled                                                                                                                                               |                                                                                           |                                                                                                                                                                  |  |  |  |  |

| bit 4                                                                                                                                                                                               | <b>TSRNG:</b> Temperature Indicator Range Selection bit <sup>(3)</sup><br>1 = VOUT = VDD - 4VT (High Range)<br>0 = VOUT = VDD - 2VT (Low Range)                                                                                                                                             |                                                                                           |                                                                                                                                                                  |  |  |  |  |

| bit 3-2                                                                                                                                                                                             | 11 = Com<br>10 = Com<br>01 = Com                                                                                                                                                                                                                                                            | parator FVR Buffer Gain is 2                                                              | er Gain Selection bits<br>x, with output VCDAFVR = 4x VFVR <sup>(2)</sup><br>x, with output VCDAFVR = 2x VFVR <sup>(2)</sup><br>x, with output VCDAFVR = 1x VFVR |  |  |  |  |

| bit 1-0                                                                                                                                                                                             | ADFVR<1:0>: ADC FVR Buffer Gain Selection bit11 = ADC FVR Buffer Gain is 4x, with output VADFVR = 4x VFVR <sup>(2)</sup> 10 = ADC FVR Buffer Gain is 2x, with output VADFVR = 2x VFVR <sup>(2)</sup> 01 = ADC FVR Buffer Gain is 1x, with output VADFVR = 1x VFVR00 = ADC FVR Buffer is off |                                                                                           |                                                                                                                                                                  |  |  |  |  |

|                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                             | ays '1' on PIC16(L)F1713/6                                                                | •                                                                                                                                                                |  |  |  |  |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 15.0 "Temperature Indicator Module" for additional information.

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1         | Bit 0 | Register<br>on page |

|--------|-------|--------|-------|-------|-------------|-------|---------------|-------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR<1:0> |       | 0> ADFVR<1:0> |       | 151                 |

Legend: Shaded cells are not used with the Fixed Voltage Reference.

# 16.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Programmable Speed/Power optimization

- · PWM shutdown

- · Programmable and fixed voltage reference

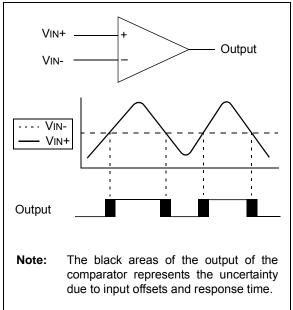

## 16.1 Comparator Overview

A single comparator is shown in Figure 16-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 16-1.

|  | TABLE 16-1: | AVAILABLE COMPARATORS |

|--|-------------|-----------------------|

|--|-------------|-----------------------|

| Device          | C1 | C2 |

|-----------------|----|----|

| PIC16(L)F1713/6 | •  | •  |

#### FIGURE 16-1: SINGLE COMPARATOR

## 19.1.5 CLCx SETUP STEPS

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 19-1).

- · Clear any associated ANSEL bits.

- Set all TRIS bits associated with inputs.

- · Clear all TRIS bits associated with outputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxPOLy bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the associated PIE registers.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

## 19.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR registers will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · LCxON bit of the CLCxCON register

- · CLCxIE bit of the associated PIE registers

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the associated PIR registers, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

## **19.3 Output Mirror Copies**

Mirror copies of all LCxCON output bits are contained in the CLCxDATA register. Reading this register reads the outputs of all CLCs simultaneously. This prevents any reading skew introduced by testing or reading the CLCxOUT bits in the individual CLCxCON registers.

## 19.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

## 19.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

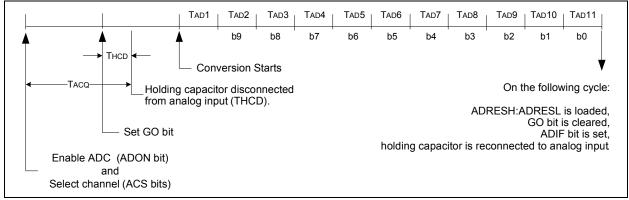

## TABLE 21-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) | Device Frequency (Fosc)     |                             |                             |                             |                             |                             |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                       |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(2)</sup>      |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(2)</sup>      | 64.0 μs <sup>(2)</sup>      |

| FRC                 | x11         | 1.0-6.0 μs <sup>(1,4)</sup> |

Legend: Shaded cells are outside of recommended range.

**Note 1:** See TAD parameter for FRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

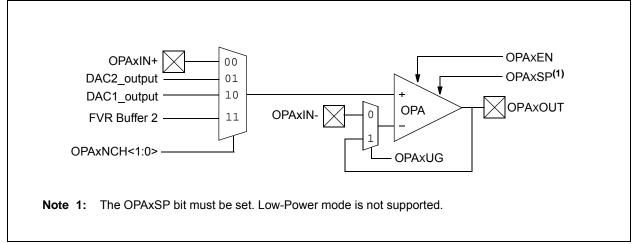

## 22.0 OPERATIONAL AMPLIFIER (OPA) MODULES

The Operational Amplifier (OPA) is a standard three-terminal device requiring external feedback to operate. The OPA module has the following features:

- External connections to I/O ports

- Low leakage inputs

- Factory Calibrated Input Offset Voltage

### 29.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register and the DCxBx bits of the CCPxCON register, with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIRx register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR1 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

## 29.3.3 TIMER2 TIMER RESOURCE

The PWM standard mode makes use of the 8-bit Timer2 timer resources to specify the PWM period.

#### 29.3.4 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 29-1.

#### EQUATION 29-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

**Note 1:** Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

Note: The Timer postscaler (see Section 27.1 "Timer2 Operation") is not used in the determination of the PWM frequency.

## 29.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 29-2 is used to calculate the PWM pulse width.

Equation 29-3 is used to calculate the PWM duty cycle ratio.

## EQUATION 29-2: PULSE WIDTH

Pulse Width = (CCPRxL:CCPxCON < 5:4>) •

TOSC • (TMR2 Prescale Value)

## EQUATION 29-3: DUTY CYCLE RATIO

Duty Cycle Ratio =  $\frac{(CCPRxL:CCPxCON < 5:4>)}{4(PR2 + 1)}$

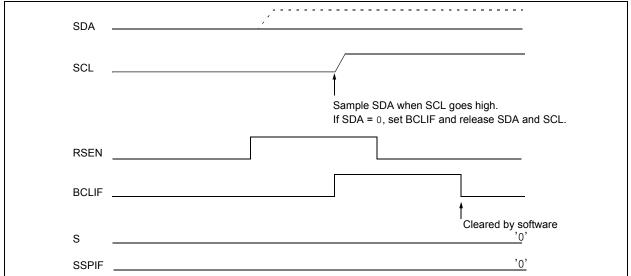

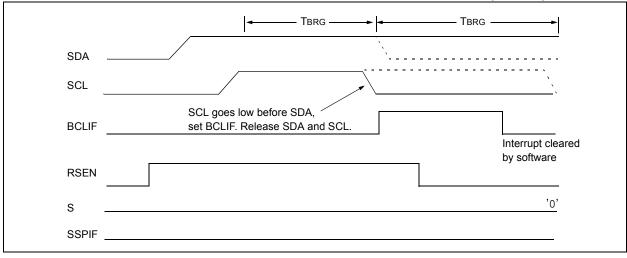

# 30.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSPADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 30-36). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 30-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

## FIGURE 30-36: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

## FIGURE 30-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

# 33.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 33-3 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 33.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 33-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| n     | FSR or INDF number. (0-1)                                                                                                                                                            |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                          |

#### TABLE 33-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-Out bit    |

| С     | Carry bit       |

| DC    | Digit Carry bit |

| Z     | Zero bit        |

| PD    | Power-Down bit  |

### TABLE 34-11: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET PARAMETERS<sup>(2)</sup>

| Standa       | Standard Operating Conditions (unless otherwise stated) |                                                          |              |              |              |        |                                                     |  |  |

|--------------|---------------------------------------------------------|----------------------------------------------------------|--------------|--------------|--------------|--------|-----------------------------------------------------|--|--|

| Param<br>No. | Sym.                                                    | Characteristic                                           | Min.         | Тур†         | Max.         | Units  | Conditions                                          |  |  |

| 30           | ТмсL                                                    | MCLR Pulse Width (low)                                   | 2            | —            | _            | μS     |                                                     |  |  |

| 31           | TWDTLP                                                  | Low-Power Watchdog Timer<br>Time-out Period              | 10           | 16           | 27           | ms     | V <sub>DD</sub> = 3.3V-5V<br>1:512 Prescaler used   |  |  |

| 32           | Tost                                                    | Oscillator Start-up Timer Period <sup>(1)</sup>          | _            | 1024         | _            | Tosc   |                                                     |  |  |

| 33*          | TPWRT                                                   | Power-up Timer Period, $\overline{PWRTE} = 0$            | 40           | 65           | 140          | ms     |                                                     |  |  |

| 34*          | Tioz                                                    | I/O high-impedance from MCLR Low or Watchdog Timer Reset |              | —            | 2.0          | μS     |                                                     |  |  |

| 35           | VBOR                                                    | Brown-out Reset Voltage                                  | 2.55         | 2.70         | 2.85         | V      | BORV = 0                                            |  |  |

|              |                                                         |                                                          | 2.30<br>1.80 | 2.45<br>1.90 | 2.60<br>2.10 | V<br>V | BORV = 1 (PIC16F1713/6)<br>BORV = 1 (PIC16LF1713/6) |  |  |

| 35A          | VLPBOR                                                  | Low-Power Brown-out                                      | 1.8          | 2.1          | 2.5          | V      | LPBOR = 1                                           |  |  |

| 36*          | VHYST                                                   | Brown-out Reset Hysteresis                               | 0            | 25           | 75           | mV     | $-40^\circ C \le TA \le +85^\circ C$                |  |  |

| 37*          | TBORDC                                                  | Brown-out Reset DC Response<br>Time                      | 1            | 3            | 35           | μS     | $VDD \leq VBOR$                                     |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

2: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

# PIC16(L)F1713/6

## TABLE 34-26: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param.<br>No. | Symbol                         | Characteristic        |              | ymbol Characteristic Min. |      | Min.                                 | Max.                                        | Units | Conditions |  |

|---------------|--------------------------------|-----------------------|--------------|---------------------------|------|--------------------------------------|---------------------------------------------|-------|------------|--|

| SP100* Thigh  |                                | Clock high time       | 100 kHz mode | 4.0                       |      | μS                                   | Device must operate at a minimum of 1.5 MHz |       |            |  |

|               |                                |                       | 400 kHz mode | 0.6                       | _    | μS                                   | Device must operate at a minimum of 10 MHz  |       |            |  |

|               |                                |                       | SSP module   | 1.5Tcy                    |      |                                      |                                             |       |            |  |

| SP101*        | TLOW                           | Clock low time        | 100 kHz mode | 4.7                       |      | μS                                   | Device must operate at a minimum of 1.5 MHz |       |            |  |

|               |                                |                       | 400 kHz mode | 1.3                       |      | μS                                   | Device must operate at a minimum of 10 MHz  |       |            |  |

|               |                                |                       | SSP module   | 1.5Tcy                    |      |                                      |                                             |       |            |  |

| SP102*        | P102* TR SDA and SCL rise time | SDA and SCL rise      | 100 kHz mode | _                         | 1000 | ns                                   |                                             |       |            |  |

|               |                                | 400 kHz mode          | 20 + 0.1Св   | 300                       | ns   | CB is specified to be from 10-400 pF |                                             |       |            |  |

| SP103*        | 03* TF SDA and SCL             | SDA and SCL fall      | 100 kHz mode | —                         | 250  | ns                                   |                                             |       |            |  |

|               |                                | time                  | 400 kHz mode | 20 + 0.1Св                | 250  | ns                                   | CB is specified to be from 10-400 pF        |       |            |  |

| SP106*        | THD:DAT                        | Data input hold time  | 100 kHz mode | 0                         | _    | ns                                   |                                             |       |            |  |

|               |                                |                       | 400 kHz mode | 0                         | 0.9  | μS                                   |                                             |       |            |  |

| SP107*        | TSU:DAT                        | Data input setup      | 100 kHz mode | 250                       |      | ns                                   | (Note 2)                                    |       |            |  |

|               |                                | time                  | 400 kHz mode | 100                       | _    | ns                                   |                                             |       |            |  |

| SP109*        | ΤΑΑ                            | Output valid from     | 100 kHz mode | —                         | 3500 | ns                                   | (Note 1)                                    |       |            |  |

|               |                                | clock                 | 400 kHz mode | —                         | _    | ns                                   |                                             |       |            |  |

| SP110*        | TBUF                           | Bus free time         | 100 kHz mode | 4.7                       |      | μS                                   | Time the bus must be free                   |       |            |  |

|               |                                |                       | 400 kHz mode | 1.3                       |      | μS                                   | before a new transmission<br>can start      |       |            |  |

| SP111         | Св                             | Bus capacitive loadir | ng           |                           | 400  | pF                                   |                                             |       |            |  |

\* These parameters are characterized but not tested.

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TSU:DAT  $\geq$  250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

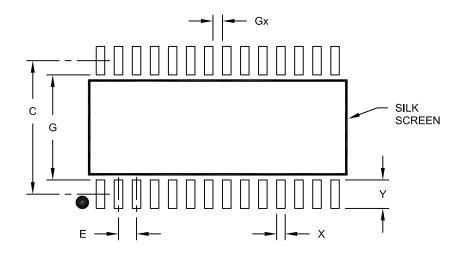

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units            |          |      | S    |  |