Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1713t-i-mv |

TABLE 3-8: PIC16(L)F1713/6 MEMORY MAP, BANK 28-30

| _             | Bank 28      | _            | Bank 29               | _            | Bank 30              |

|---------------|--------------|--------------|-----------------------|--------------|----------------------|

| E0Ch          | _            | E8Ch         | _                     | F0Ch         | _                    |

| E0Dh          | _            | E8Dh         |                       | F0Dh         |                      |

| E0Eh          |              | E8Eh         |                       | F0Eh         |                      |

| E0Fh          | PPSLOCK      | E8Fh         | _                     | F0Fh         | CLCDATA              |

| E10h          | INTPPS       | E90h         | RA0PPS                | F10h         | CLC1CON              |

| E11h          | T0CKIPPS     | E91h         | RA1PPS                | F11h         | CLC1POL              |

| E12h          | T1CKIPPS     | E92h         | RA2PPS                | F12h         | CLC1SEL0             |

| E13h          | T1GPPS       | E93h         | RA3PPS                | F13h         | CLC1SEL1             |

| E14h          | CCP1PPS      | E94h         | RA4PPS                | F14h         | CLC1SEL2             |

| E15h          | CCP2PPS      | E95h         | RA5PPS                | F15h         | CLC1SEL3             |

| E16h          |              | E96h         | RA6PPS                | F16h         | CLC1GLS0             |

| E17h          | COGINPPS     | E97h         | RA7PPS                | F17h         | CLC1GLS1             |

| E18h          | _            | E98h         | RB0PPS                | F18h         | CLC1GLS2             |

| E19h          | _            | E99h         | RB1PPS                | F19h         | CLC1GLS3             |

| E1Ah          |              | E9Ah         | RB2PPS                | F1Ah         | CLC2CON              |

| E1Bh          | _            | E9Bh         | RB3PPS                | F1Bh         | CLC2POL              |

| E1Ch          | _            | E9Ch         | RB4PPS <sup>(1)</sup> | F1Ch         | CLC2SEL0             |

| E1Dh          | _            | E9Dh         | RB5PPS <sup>(1)</sup> | F1Dh         | CLC2SEL1             |

| E1Eh          | _            | E9Eh         | RB6PPS <sup>(1)</sup> | F1Eh         | CLC2SEL2             |

| E1Fh          | _            | E9Fh         | RB7PPS <sup>(1)</sup> | F1Fh         | CLC2SEL3             |

| E20h          | SSPCLKPPS    | EA0h         | RC0PPS                | F20h         | CLC2GLS0             |

| E21h          | SSPDATPPS    | EA1h         | RC1PPS                | F21h         | CLC2GLS1             |

| E22h          | SSPSSPPS     | EA2h         | RC2PPS                | F22h         | CLC2GLS2             |

| E23h          |              | EA3h         | RC3PPS                | F23h         | CLC2GLS3             |

| E24h          | RXPPS        | EA4h         | RC4PPS                | F24h         | CLC3CON              |

| E25h          | CKPPS        | EA5h         | RC5PPS                | F25h         | CLC3POL              |

| E26h          | _            | EA6h         | RC6PPS <sup>(1)</sup> | F26h         | CLC3SEL0             |

| E27h          | _            | EA7h         | RC7PPS <sup>(1)</sup> | F27h         | CLC3SEL1             |

| E28h          | CLCIN0PPS    | EA8h         | _                     | F28h         | CLC3SEL2             |

| E29h          | CLCIN1PPS    | EA9h         |                       | F29h         | CLC3SEL3             |

| E2Ah          | CLCIN2PPS    | EAAh         | _                     | F2Ah         | CLC3GLS0             |

| E2Bh          | CLCIN3PPS    | EABh         | _                     | F2Bh         | CLC3GLS1             |

| E2Ch          | _            | EACh         | _                     | F2Ch         | CLC3GLS2             |

| E2Dh          |              | EADh         |                       | F2Dh         | CLC3GLS3             |

| E2Eh          | _            | EAEh         | _                     | F2Eh         | CLC4CON              |

| E2Fh          | <del>-</del> | EAFh         | <del>-</del>          | F2Fh         | CLC4POL              |

| E30h<br>E31h  | _            | EB0h<br>EB1h | _                     | F30h<br>F31h | CLC4SEL0<br>CLC4SEL1 |

| E3111<br>E32h |              | EB2h         | _                     | F3111        | CLC4SEL1<br>CLC4SEL2 |

| E3211         |              | EB3h         |                       | F33h         | CLC4SEL2<br>CLC4SEL3 |

| E34h          | _            | EB4h         | _                     | F34h         | CLC4GLS0             |

| E35h          |              | EB5h         |                       | F35h         | CLC4GLS1             |

| E36h          | _            | EB6h         | _                     | F36h         | CLC4GLS2             |

| E37h          | _            | EB7h         | _                     | F37h         | CLC4GLS3             |

| E38h          | _            | EB8h         | _                     | F38h         | _                    |

| E39h          | _            | EB9h         | _                     | F39h         | _                    |

| E3Ah          | _            | EBAh         | _                     | F3Ah         | _                    |

| E3Bh          | _            | EBBh         | _                     | F3Bh         |                      |

| E3Ch          | _            | EBCh         | _                     | F3Ch         | _                    |

| E3Dh          | _            | EBDh         | _                     | F3Dh         | _                    |

| E3Eh          | _            | EBEh         | _                     | F3Eh         | _                    |

| E3Fh          | _            | EBFh         | _                     | F3Fh         | _                    |

| E40h          |              | EC0h         |                       | F40h         |                      |

|               | _            |              | _                     |              | _                    |

| 1             |              | ı            |                       | ı I          |                      |

| E6Fh          |              | EEFh         |                       | F6Fh         |                      |

DS40001726C-page 26

## 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

## 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

#### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

| R/P-1              | R/P-1                | R/P-1 | R/P-1               | R/P-1  | R/P-1 |

|--------------------|----------------------|-------|---------------------|--------|-------|

| LVP <sup>(1)</sup> | DEBUG <sup>(2)</sup> | LPBOR | BORV <sup>(3)</sup> | STVREN | PLLEN |

| bit 13             |                      |       |                     |        | bit 8 |

| R/P-1  | U-1 | U-1 | U-1 | U-1 | R/P-1   | R/P-1 | R/P-1 |

|--------|-----|-----|-----|-----|---------|-------|-------|

| ZCDDIS | _   | _   | _   | _   | PPS1WAY | WRT<  | 1:0>  |

| bit 7  |     |     |     |     |         |       | bit 0 |

| Legend:              |                      |                                           |

|----------------------|----------------------|-------------------------------------------|

| R = Readable bit     | P = Programmable bit | U = Unimplemented bit, read as '1'        |

| '0' = Bit is cleared | '1' = Bit is set     | -n = Value when blank or after Bulk Erase |

bit 13 LVP: Low-Voltage Programming Enable bit<sup>(1)</sup>

1 = Low-voltage programming enabled

$0 = \text{High-voltage on } \overline{\text{MCLR}}$  must be used for programming

bit 12 **DEBUG**: In-Circuit Debugger Mode bit<sup>(2)</sup>

1 = In-Circuit Debugger disabled, ICSPCLK and ICSPDAT are general purpose I/O pins 0 = In-Circuit Debugger enabled, ICSPCLK and ICSPDAT are dedicated to the debugger

bit 11 LPBOR: Low-Power BOR Enable bit

1 = Low-Power Brown-out Reset is disabled 0 = Low-Power Brown-out Reset is enabled

bit 10 **BORV:** Brown-out Reset Voltage Selection bit<sup>(3)</sup>

1 = Brown-out Reset voltage (VBOR), low trip point selected.0 = Brown-out Reset voltage (VBOR), high trip point selected.

bit 9 STVREN: Stack Overflow/Underflow Reset Enable bit

1 = Stack Overflow or Underflow will cause a Reset0 = Stack Overflow or Underflow will not cause a Reset

bit 8 PLLEN: PLL Enable bit

1 = 4xPLL enabled 0 = 4xPLL disabled

bit 7 ZCDDIS: ZCD Disable bit

1 = ZCD disabled. ZCD can be enabled by setting the ZCDSEN bit of ZCDCON

0 = ZCD always enabled

bit 6-3 **Unimplemented:** Read as '1'

bit 2 PPS1WAY: PPSLOCK Bit One-Way Set Enable bit

1 = The PPSLOCK bit can only be set once after an unlocking sequence is executed; once PPSLOCK is set, all future changes to PPS registers are prevented

0 = The PPSLOCK bit can be set and cleared as needed (provided an unlocking sequence is executed)

bit 1-0 WRT<1:0>: Flash Memory Self-Write Protection bits

4 kW Flash memory

11 = Write protection off

10 = 000h to 1FFh write protected, 200h to FFFh may be modified by PMCON control

01 = 000h to 7FFh write protected, 800h to FFFh may be modified by PMCON control

00 = 000h to FFFh write protected, no addresses may be modified by PMCON control

Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

2: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

3: See VBOR parameter for specific trip point voltages.

#### 6.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- · Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

# 6.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by the value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 6-1.

# 6.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

#### 6.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the T1OSCEN control bit in the T1CON register. See Section 26.0 "Timer1 Module with Gate Control" for more information about the Timer1 peripheral.

# 6.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

# 6.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

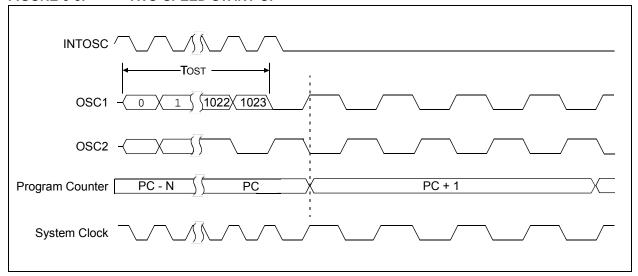

# 6.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- System clock is switched to external clock source.

# 6.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator.

FIGURE 6-8: TWO-SPEED START-UP

### REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

bit 0 GxFSIM0: COGx Falling Event Input Source 0 Mode bit

<u>GxFIS0 = 1:</u>

- 1 = Pin selected with COGxPPS control high-to-low transition will cause a falling event after falling event phase delay

- 0 = Pin selected with COGxPPS control low level will cause an immediate falling event

GxFIS0 = 0:

Pin selected with COGxPPS control has no effect on falling event

### 27.5 Register Definitions: Timer2 Control

#### REGISTER 27-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0/0      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|--------------|---------|---------|---------|---------|---------|---------|

| _     | T2OUTPS<3:0> |         |         | TMR2ON  | T2CKP   | S<1:0>  |         |

| bit 7 |              |         |         |         | bit 0   |         |         |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 **Unimplemented:** Read as '0'

bit 6-3 **T2OUTPS<3:0>:** Timer2 Output Postscaler Select bits

1111 = 1:16 Postscaler 1110 = 1:15 Postscaler 1101 = 1:14 Postscaler 1100 = 1:13 Postscaler 1011 = 1:12 Postscaler 1010 = 1:11 Postscaler 1001 = 1:10 Postscaler 1000 = 1:9 Postscaler 1011 = 1:8 Postscaler 1110 = 1:7 Postscaler 1110 = 1:6 Postscaler 1110 = 1:5 Postscaler 1110 = 1:4 Postscaler 1110 = 1:4 Postscaler 1110 = 1:4 Postscaler

0001 = 1:2 Postscaler 0000 = 1:1 Postscaler

bit 2 TMR2ON: Timer2 On bit

1 = Timer2 is on0 = Timer2 is off

bit 1-0 T2CKPS<1:0>: Timer2 Clock Prescale Select bits

11 = Prescaler is 64 10 = Prescaler is 16 01 = Prescaler is 4 00 = Prescaler is 1

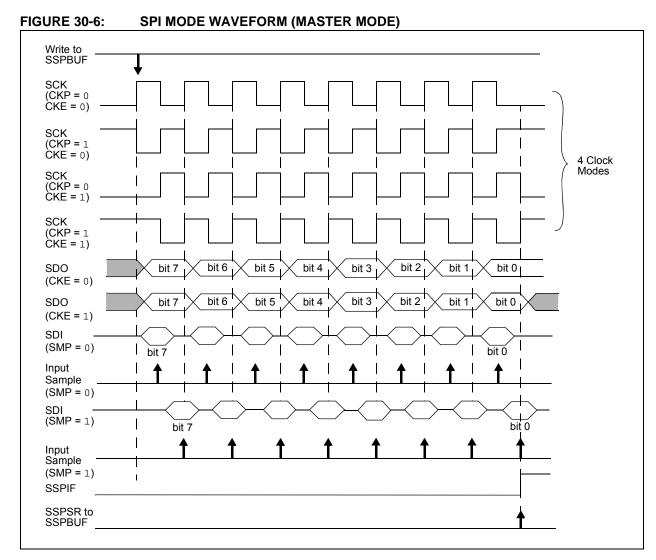

#### 30.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

**Daisy-Chain Configuration**

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 30-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPCON3 register will enable writes to the SSPBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

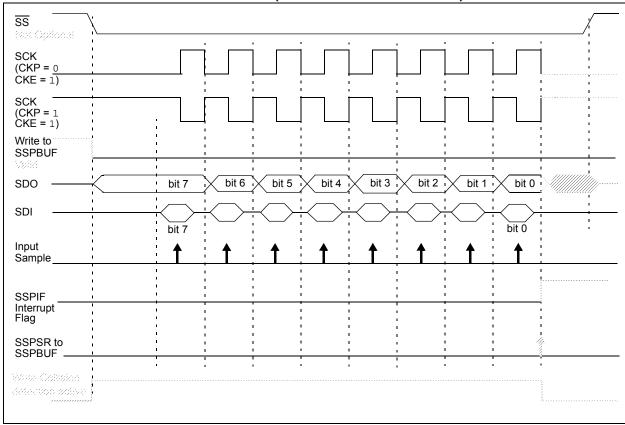

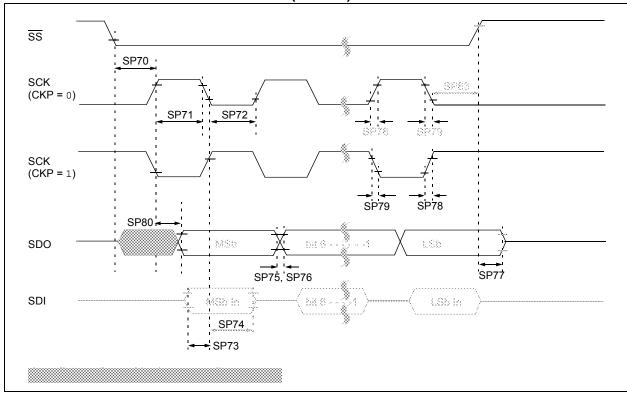

### FIGURE 30-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### 30.3 I<sup>2</sup>C MODE OVERVIEW

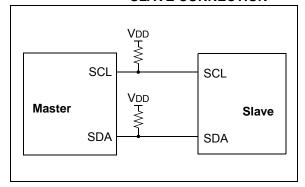

The Inter-Integrated Circuit (I<sup>2</sup>C) bus is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- · Serial Data (SDA)

Figure 30-11 shows the block diagram of the MSSP module when operating in I<sup>2</sup>C mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 30-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

### FIGURE 30-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop hits

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last  $\overline{ACK}$  bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last  $\overline{ACK}$  bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

#### 30.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 30.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

#### 30.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge ( $\overline{ACK}$ ) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{\text{ACK}}$  is placed in the ACKSTAT bit of the SSPCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPCON2 register is set/cleared to determine the response.

Slave hardware will generate an  $\overline{\mathsf{ACK}}$  response if the AHEN and DHEN bits of the SSPCON3 register are clear.

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPSTAT register or the SSPOV bit of the SSPCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

#### 30.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of SSPCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPIF additionally getting set upon detection of a Start, Restart, or Stop condition.

### 30.5.1 SLAVE MODE ADDRESSES

The SSPADD register (Register 30-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 30-5) affects the address matching process. See **Section 30.5.9 "SSP Mask Register"** for more information.

### 30.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

## 30.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPADD is updated to receive a high byte again. When SSPADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the  $R/\overline{W}$  bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

#### 30.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON1 register is set. The BOEN bit of the SSPCON3 register modifies this operation. For more information see Register 30-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPIF, must be cleared by software.

When the SEN bit of the SSPCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPCON1 register, except sometimes in 10-bit mode. See **Section 30.5.6.2** "10-bit **Addressing Mode**" for more detail.

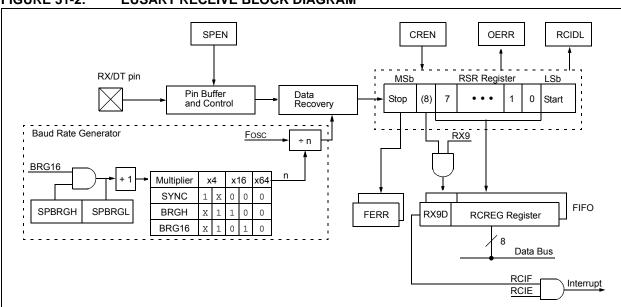

FIGURE 31-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- · Transmit Status and Control (TXSTA)

- · Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 31-1, Register 31-2 and Register 31-3, respectively.

The RX and CK input pins are selected with the RXPPS and CKPPS registers, respectively. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

#### RRF Rotate Right f through Carry

Syntax: [ label ] RRF f,d

Operands:  $0 \le f \le 127 \\ d \in [0,1]$

Operation: See description below

Status Affected: C

Description: The contents of register 'f' are rotated

one bit to the right through the Carry flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register. 'f'

placed back in register 'f'.

# SUBLW Subtract W from literal

Syntax: [ label ] SUBLW k

Operands:  $0 \le k \le 255$ Operation:  $k - (W) \rightarrow (W)$ Status Affected: C, DC, Z

Description: The W register is subtracted (2's

complement method) from the 8-bit literal 'k'. The result is placed in the W

register.

| C = 0  | W > k             |

|--------|-------------------|

| C = 1  | $W \leq k $       |

| DC = 0 | W<3:0> > k<3:0>   |

| DC = 1 | W<3:0> \le k<3:0> |

## SLEEP Enter Sleep mode

Syntax: [ label ] SLEEP

Operands: None

Operation:  $00h \rightarrow WDT$ ,

$0 \rightarrow \frac{\text{WDT}}{\text{TO}}$  prescaler,

$\begin{array}{c}

1 \to \overline{\mathsf{TO}}, \\

0 \to \overline{\mathsf{PD}}

\end{array}$

Status Affected:  $\overline{TO}$ ,  $\overline{PD}$

Description: The power-down Status bit,  $\overline{PD}$  is

cleared. Time-out Status bit,  $\overline{10}$  is set. Watchdog Timer and its prescaler are cleared.

The processor is put into Sleep mode

with the oscillator stopped.

### SUBWF Subtract W from f

Syntax: [ label ] SUBWF f,d

$\begin{array}{ll} \text{Operands:} & 0 \leq f \leq 127 \\ & d \in \left[0,1\right] \end{array}$

Operation:  $(f) - (W) \rightarrow (destination)$

Status Affected: C, DC, Z

Description: Subtract (2's complement method) W

register from register 'f'. If 'd' is '0', the

result is stored in the W

register. If 'd' is '1', the result is stored

back in register 'f.

| C = 0  | W > f               |

|--------|---------------------|

| C = 1  | $W \leq f \\$       |

| DC = 0 | W<3:0> > f<3:0>     |

| DC = 1 | $W<3:0> \le f<3:0>$ |

#### SUBWFB Subtract W from f with Borrow

Syntax: SUBWFB f {,d}

Operands:  $0 \le f \le 127$

$d \in \left[0,1\right]$

Operation:  $(f) - (W) - (\overline{B}) \rightarrow dest$

Status Affected: C, DC, Z

Description: Subtract W and the BORROW flag

(CARRY) from register 'f' (2's complement method). If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'.

### 34.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

|                                            | Т |           |   |      |

|--------------------------------------------|---|-----------|---|------|

|                                            | F | Frequency | Т | Time |

| Lowercase letters (pp) and their meanings: |   |           |   |      |

| pp |               |     |          |

|----|---------------|-----|----------|

| СС | CCP1          | osc | OSC1     |

| ck | CLKOUT        | rd  | RD       |

| cs | <del>CS</del> | rw  | RD or WR |

| di | SDI           | sc  | SCK      |

| do | SDO           | ss  | SS       |

| dt | Data in       | t0  | T0CKI    |

| io | I/O PORT      | t1  | T1CKI    |

| mc | MCLR          | wr  | WR       |

Uppercase letters and their meanings:

| S | <u> </u>                 |   |                |

|---|--------------------------|---|----------------|

| F | Fall                     | Р | Period         |

| Н | High                     | R | Rise           |

| 1 | Invalid (High-impedance) | V | Valid          |

| L | Low                      | Z | High-impedance |

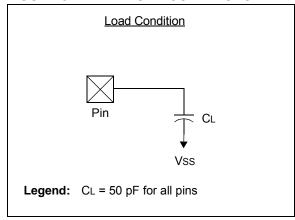

### FIGURE 34-4: LOAD CONDITIONS

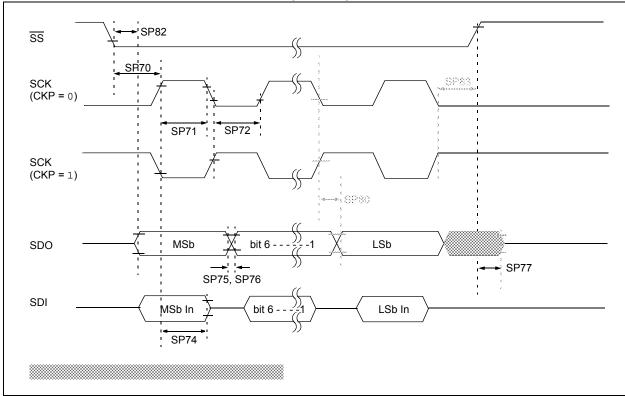

FIGURE 34-19: SPI SLAVE MODE TIMING (CKE = 0)

FIGURE 34-20: SPI SLAVE MODE TIMING (CKE = 1)

**Note:** Unless otherwise noted, VIN = 5V, FOSC = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

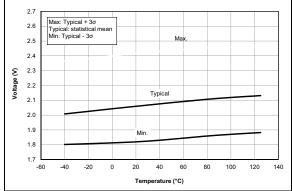

FIGURE 35-67: LPBOR Reset Voltage.

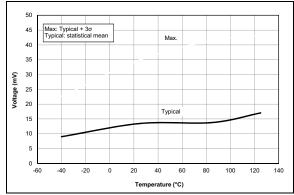

FIGURE 35-68: LPBOR Reset Hysteresis.

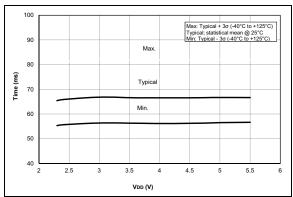

FIGURE 35-69: PWRT Period, PIC16F1713/6 Only.

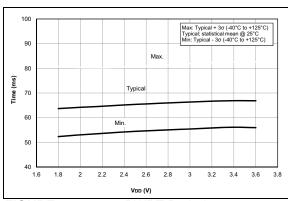

FIGURE 35-70: PWRT Period, PIC16LF1713/6 Only.

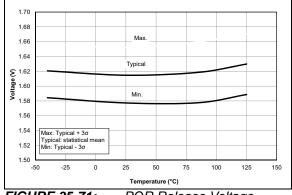

FIGURE 35-71: POR Release Voltage.

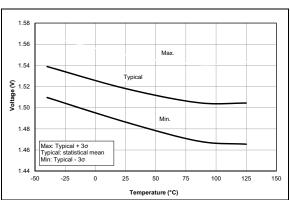

FIGURE 35-72: POR Rearm Voltage, NP Mode (VREGPM1 = 0), PIC16F1713/6 Only.

**Note:** Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

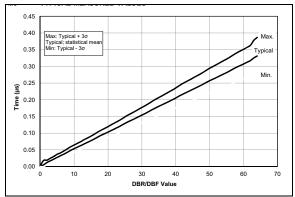

FIGURE 35-121: COG Deadband Delay Per Step, Typical Measured Values

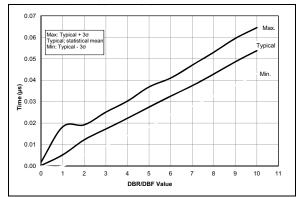

FIGURE 35-122: COG Deadband Delay Per Step, Zoomed to First 10 Codes, Typical Measured Values.

#### 36.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 36.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 36.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 36.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 36.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 36.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradeable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 36.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 36.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

#### 36.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.