Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1713t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** The entire Flash program memory will be erased when the code protection is turned off during an erase. When a Bulk Erase Program Memory Command is executed, the entire program Flash memory and configuration memory will be erased.

'1' = Bit is set

| R/W-1/1                                 | R/W-1/1                 | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |

|-----------------------------------------|-------------------------|---------|-------------------------------------------------------|---------|---------|---------|---------|--|

| SLRA7                                   | SLRA7 SLRA6 SLRA5 SLRA4 |         |                                                       |         | SLRA2   | SLRA1   | SLRA0   |  |

| bit 7                                   |                         |         |                                                       |         | •       | bit 0   |         |  |

| Levend                                  |                         |         |                                                       |         |         |         |         |  |

| Legend:                                 |                         |         |                                                       |         |         |         |         |  |

| R = Readable bit W = Writable bit       |                         | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |                         | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |         |  |

#### REGISTER 11-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

bit 7-0 SLRA<7:0>: PORTA Slew Rate Enable bits For RA<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

#### REGISTER 11-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

'0' = Bit is cleared

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 75-0 INLVLA<7:0>: PORTA Input Level Select bits For RA<7:0> pins, respectively 1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

| ANSC7 ANSC6 ANSC5 ANSC4 ANSC3 ANSC2 — — —<br>bit 7 bit | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0   |

|--------------------------------------------------------|---------|---------|---------|---------|---------|---------|-----|-------|

| bit 7 bit                                              | ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | —   | —     |

|                                                        | bit 7   |         |         |         |         |         |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 | <ul> <li>ANSC&lt;7:0&gt;: Analog Select between Analog or Digital Function on pins RC&lt;7:0&gt;, respectively<sup>(1)</sup></li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> </ul> |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1-0 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                      |

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 11-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1   | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| WPUC7     | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7 bit |         |         |         |         |         | bit 0   |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

**Note** 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

#### GxASDAC<1:0> '1 '0'**-**High-Z-01 reserved 11 00 HFINTOSC 10 COG\_clock COGxA Fosc 01 Fosc/4 GxSDATA 0 GxPOLA GxCS<1:0> **Rising Input Block** GxSTRA GxASDBD<1:0> NCO1\_out\_ src7 Push-Pull clock '1'<del>-</del> 11 src6 PWM3OUT-D Ω '0'<del>-</del> Reset Dominates src5 CCP2 High-Z-01 src4 CCP1-S Q rising\_event 00 R src3 LC1\_out. 1 COGxB C2OUTsrc2 RQ 1 C1OUT src1 L ... count\_en GxSDATB-0 COGINPPSsrc0 GxPOLB GxASDAC<1:0> GxSTRB Falling Input Block '1' 11 NCO1 out ----src7 clock '0' src6 PWM3OUT -High-Z-01 CCP2 src5 00 CCP1 src4 LC1\_out src3 falling\_event COGxC C2OUT src2 C10UT src1 GxSDATC-0 COGINPPS src0 count en GxPOLC GxSTRC GxASDBD<1:0> '1'<del>-</del> 11 '0'**-**10 GxEN 01 High-Z-00 1 COGxD COGINPPS GxAS0E 0 GxSDATD C10UT 0 Auto-shutdown source GxAS1E GxPOLD GxSTRD C2OUT GxAS2E LC2\_out GxASE SQ GxAS3E GxARSEN S D Q Write GxASE Low R

Set Dominates

### FIGURE 18-6:

Write GxASE High

#### REGISTER 18-6: COGxFSIM: COG FALLING EVENT SOURCE INPUT MODE REGISTER

bit 0

**GxFSIM0:** COGx Falling Event Input Source 0 Mode bit <u>GxFIS0 = 1:</u>

1 = Pin selected with COGxPPS control high-to-low transition will cause a falling event after falling event phase delay

0 = Pin selected with COGxPPS control low level will cause an immediate falling event

<u>GxFIS0 = 0:</u>

Pin selected with COGxPPS control has no effect on falling event

#### 21.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- · Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 21.4 "ADC Acquisition Requirements".

#### EXAMPLE 21-1: ADC CONVERSION

;This code block configures the ADC ; for polling, Vdd and Vss references, FRC ;oscillator and ANO input. ;Conversion start & polling for completion ; are included. BANKSEL ADCON1 ; B'11110000' ;Right justify, FRC MOVLW ;oscillator MOVWF ADCON1 ;Vdd and Vss Vref BANKSEL TRISA ; BSF TRISA,0 ;Set RA0 to input BANKSEL ANSEL ; BSF ANSEL,0 ;Set RA0 to analog BANKSEL WPUA BCF wpua,0 ;Disable weak ;pull-up on RA0 BANKSEL ADCON0 B'00000001' ;Select channel AN0 MOVLW MOVWF ADCON0 ; Turn ADC On CALL SampleTime ;Acquisiton delay BSF ADCON0, ADGO ;Start conversion ADCON0, ADGO ; Is conversion done? BTFSC GOTO \$-1 ;No, test again BANKSEL ADRESH ; ADRESH,W ;Read upper 2 bits MOVF RESULTHI ;store in GPR space MOVWE BANKSEL ADRESL ; MOVF ADRESL,W ;Read lower 8 bits MOVWF RESULTLO ;Store in GPR space

## PIC16(L)F1713/6

| Name     | Bit 7      | Bit 6        | Bit 5        | Bit 4    | Bit 3       | Bit 2   | Bit 1      | Bit 0   | Register<br>on Page |

|----------|------------|--------------|--------------|----------|-------------|---------|------------|---------|---------------------|

| ADCON0   | —          |              |              | CHS<4:0> |             |         | GO/DONE    | ADON    | 235                 |

| ADCON1   | ADFM       |              | ADCS<2:0>    |          |             | ADNREF  | ADPRE      | F<1:0>  | 236                 |

| ADCON2   |            | TRIGS        | TRIGSEL<3:0> |          |             | —       | —          | _       | 237                 |

| ADRESH   | ADC Result | Register Hig | lh           |          |             |         |            |         | 239                 |

| ADRESL   | ADC Result | Register Lov | N            |          |             |         |            |         | 239                 |

| ANSELA   | —          | —            | ANSA5        | ANSA4    | ANSA3       | ANSA2   | ANSA1      | ANSA0   | 120                 |

| ANSELB   | —          | _            | ANSB5        | ANSB4    | ANSB3       | ANSB2   | ANSB1      | ANSB0   | 126                 |

| ANSELC   | ANSC7      | ANSC6        | ANSC5        | ANSC4    | ANSC3       | ANSC2   |            |         | 131                 |

| INTCON   | GIE        | PEIE         | TMR0IE       | INTE     | IOCIE       | TMR0IF  | INTF       | IOCIF   | 83                  |

| PIE1     | TMR1GIE    | ADIE         | RCIE         | TXIE     | SSP1IE      | CCP1IE  | TMR2IE     | TMR1IE  | 84                  |

| PIR1     | TMR1GIF    | ADIF         | RCIF         | TXIF     | SSP1IF      | CCP1IF  | TMR2IF     | TMR1IF  | 87                  |

| TRISA    | TRISA7     | TRISA6       | TRISA5       | TRISA4   | TRISA3      | TRISA2  | TRISA1     | TRISA0  | 119                 |

| TRISB    | TRISB7     | TRISB6       | TRISB5       | TRISB4   | TRISB3      | TRISB2  | TRISB1     | TRISB0  | 125                 |

| TRISC    | TRISC7     | TRISC6       | TRISC5       | TRISC4   | TRISC3      | TRISC2  | TRISC1     | TRISC0  | 130                 |

| FVRCON   | FVREN      | FVRRDY       | TSEN         | TSRNG    | CDAFVR<1:0> |         | ADFVR<1:0> |         | 151                 |

| DAC1CON0 | DAC1EN     | _            | DAC10E1      | DAC10E2  | DAC1P       | SS<1:0> | —          | DAC1NSS | 249                 |

#### TABLE 21-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for the ADC module.

#### 26.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

#### 26.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OS-CEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

#### 26.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 26.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 26.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

#### 26.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 26.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 26-3 for timing details.

TABLE 26-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| 1          | 1      | 1   | Counts           |

## PIC16(L)F1713/6

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- · Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

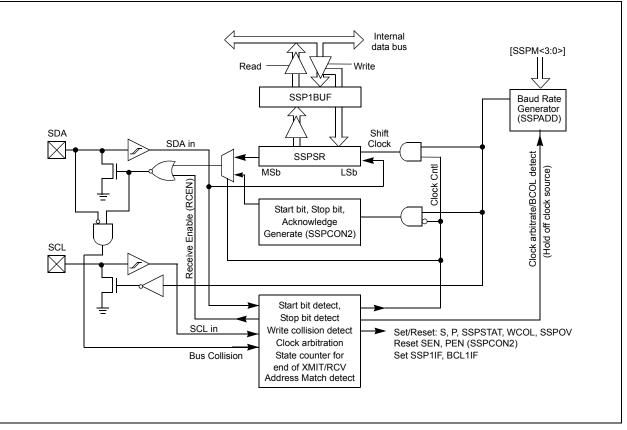

Figure 30-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 30-3 is a diagram of the  $I^2C$  interface module in Slave mode.

#### FIGURE 30-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Detect bit, BF of the SSPSTAT register, and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The Buffer Full bit, BF of the SSPSTAT register, indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the SSPSTAT register indicates the various Status conditions.

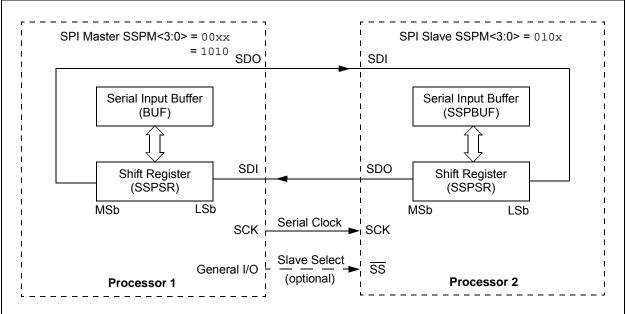

#### FIGURE 30-5: SPI MASTER/SLAVE CONNECTION

#### 30.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt, if enabled):

- Start condition detected

- Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

#### 30.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 30.7** "**Baud Rate Generator**" for more detail.

#### 30.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 30-25).

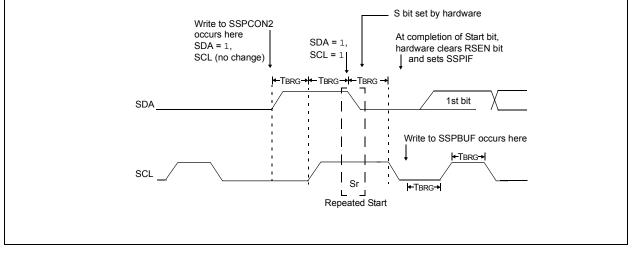

#### 30.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 30-27) occurs when the RSEN bit of the SSPCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPSTAT register will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

#### 30.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit

on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 30-28).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

| R-0/0            | R-1/1                            | U-0                                | R/W-0/0        | R/W-0/0          | U-0              | R/W-0/0           | R/W-0/0       |

|------------------|----------------------------------|------------------------------------|----------------|------------------|------------------|-------------------|---------------|

| ABDOVF           | RCIDL                            | —                                  | SCKP           | BRG16            | —                | WUE               | ABDEN         |

| bit 7            |                                  |                                    |                |                  |                  |                   | bit 0         |

|                  |                                  |                                    |                |                  |                  |                   |               |

| Legend:          |                                  |                                    |                |                  |                  |                   |               |

| R = Readable     | bit                              | W = Writable                       | bit            | U = Unimplei     | mented bit, rea  | d as '0'          |               |

| u = Bit is unch  | anged                            | x = Bit is unk                     | nown           | -n/n = Value     | at POR and BC    | OR/Value at all c | other Resets  |

| '1' = Bit is set |                                  | '0' = Bit is cle                   | ared           |                  |                  |                   |               |

|                  |                                  |                                    |                |                  |                  |                   |               |

| bit 7            |                                  | ito-Baud Deteo                     | t Overflow bit |                  |                  |                   |               |

|                  | Asynchronou                      |                                    | d              |                  |                  |                   |               |

|                  |                                  | d timer overflo<br>d timer did not |                |                  |                  |                   |               |

|                  | Synchronous                      |                                    | overnow        |                  |                  |                   |               |

|                  | Don't care                       |                                    |                |                  |                  |                   |               |

| bit 6            | RCIDL: Rece                      | ive Idle Flag b                    | it             |                  |                  |                   |               |

|                  | <u>Asynchronou</u>               | <u>s mode</u> :                    |                |                  |                  |                   |               |

|                  | 1 = Receiver                     |                                    |                |                  |                  |                   |               |

|                  |                                  |                                    | red and the re | ceiver is receiv | ving             |                   |               |

|                  | <u>Synchronous</u><br>Don't care | mode:                              |                |                  |                  |                   |               |

| bit 5            | Unimplemen                       | ted: Read as                       | 0'             |                  |                  |                   |               |

| bit 4            | SCKP: Synch                      | nronous Clock                      | Polarity Selec | t bit            |                  |                   |               |

|                  | Asynchronou                      | <u>s mode</u> :                    |                |                  |                  |                   |               |

|                  |                                  | inverted data t<br>non-inverted d  | •              |                  |                  |                   |               |

|                  | <u>Synchronous</u>               |                                    |                |                  |                  |                   |               |

|                  |                                  | ocked on rising                    |                |                  |                  |                   |               |

| hit 0            |                                  | ocked on fallin<br>it Baud Rate G  |                | CIOCK            |                  |                   |               |

| bit 3            |                                  | ud Rate Gene                       |                |                  |                  |                   |               |

|                  |                                  | id Rate Genera                     |                |                  |                  |                   |               |

| bit 2            |                                  | ted: Read as                       |                |                  |                  |                   |               |

| bit 1            | WUE: Wake-                       | up Enable bit                      |                |                  |                  |                   |               |

|                  | <u>Asynchronou</u>               | s mode:                            |                |                  |                  |                   |               |

|                  |                                  | is waiting for a natically clear a |                |                  | will be received | d, byte RCIF wil  | l be set. WUE |

|                  |                                  | is operating no                    |                | с.               |                  |                   |               |

|                  | Synchronous                      |                                    | j              |                  |                  |                   |               |

|                  | Don't care                       |                                    |                |                  |                  |                   |               |

| bit 0            | ABDEN: Auto                      | o-Baud Detect                      | Enable bit     |                  |                  |                   |               |

|                  | <u>Asynchronou</u>               | <u>s mode</u> :                    |                |                  |                  |                   |               |

|                  | 1 = Auto-Bau                     | ud Detect mod                      | e is enabled ( | clears when au   | to-baud is com   | plete)            |               |

|                  |                                  | ud Detect mod                      | e is disabled  |                  |                  |                   |               |

|                  | Synchronous                      | mode:                              |                |                  |                  |                   |               |

|                  | Don't care                       |                                    |                |                  |                  |                   |               |

#### REGISTER 31-3: BAUD1CON: BAUD RATE CONTROL REGISTER

|        |                |            |                             | -                | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRG        | <b>616 =</b> 0 |                             |                  |            |                             |

|--------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |                |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              | _          | _                           | _                |            | _                           |                   | _              | _                           | 300              | 0.16       | 207                         |

| 1200   | —              | —          | —                           | 1202             | 0.16       | 207                         | 1200              | 0.00           | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404           | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00           | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615           | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00           | 23                          | _                | _          | _                           |

| 10417  | 10417          | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53           | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231          | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k             | 0.00           | 11                          | _                | _          | _                           |

| 57.6k  | 55556          | -3.55      | 8                           | —                | _          | _                           | 57.60k            | 0.00           | 3                           | _                | _          | _                           |

| 115.2k | —              |            | —                           | _                | _          | —                           | 115.2k            | 0.00           | 1                           |                  | _          | _                           |

#### TABLE 31-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                   |            |                             |                |            |                             |                |            |                             |

|--------|----------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc           | : = 32.00                     | 0 MHz                       | Fosc = 20.000 MHz |            | Fosc = 18.432 MHz           |                |            | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00                          | 6666                        | 300.0             | -0.01      | 4166                        | 300.0          | 0.00       | 3839                        | 300.0          | 0.00       | 2303                        |

| 1200   | 1200           | -0.02                         | 3332                        | 1200              | -0.03      | 1041                        | 1200           | 0.00       | 959                         | 1200           | 0.00       | 575                         |

| 2400   | 2401           | -0.04                         | 832                         | 2399              | -0.03      | 520                         | 2400           | 0.00       | 479                         | 2400           | 0.00       | 287                         |

| 9600   | 9615           | 0.16                          | 207                         | 9615              | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00       | 71                          |

| 10417  | 10417          | 0.00                          | 191                         | 10417             | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16                          | 103                         | 19.23k            | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 57.14k         | -0.79                         | 34                          | 56.818            | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 117.6k         | 2.12                          | 16                          | 113.636           | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00       | 5                           |

|        |                |            |                             |                  | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRG        | <b>616 =</b> 1 |                             |                  |            |                             |

|--------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |                |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 299.9          | -0.02      | 1666                        | 300.1            | 0.04       | 832                         | 300.0             | 0.00           | 767                         | 300.5            | 0.16       | 207                         |

| 1200   | 1199           | -0.08      | 416                         | 1202             | 0.16       | 207                         | 1200              | 0.00           | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404           | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00           | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615           | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00           | 23                          | _                | _          | _                           |

| 10417  | 10417          | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53           | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19.23k         | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.20k            | 0.00           | 11                          | _                | _          | _                           |

| 57.6k  | 55556          | -3.55      | 8                           | _                | _          | _                           | 57.60k            | 0.00           | 3                           | _                | _          | _                           |

| 115.2k | —              | _          | _                           | _                | _          | _                           | 115.2k            | 0.00           | 1                           | _                | _          | _                           |

## PIC16(L)F1713/6

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                              |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$<br>are set.                          |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALLW                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                                                  |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                  |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRF             | Clear f                                                               |  |  |

|------------------|-----------------------------------------------------------------------|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |

| Status Affected: | Z                                                                     |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W register. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |

# CLRWClear WSyntax:[label] CLRWOperands:NoneOperation: $00h \rightarrow (W)$ <br/> $1 \rightarrow Z$ Status Affected:ZDescription:W register is cleared. Zero bit (Z) is<br/>set.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<6:3> $\rightarrow PC < 14:11>$                                                                                                                     |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                             |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                             |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                     |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Description:     | The contents of register 'f are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                     |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                          |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                 |  |  |

| Status Affected: | Z                                                                                                            |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |

| INCF             | Increment f                                                                                                                                                               |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |

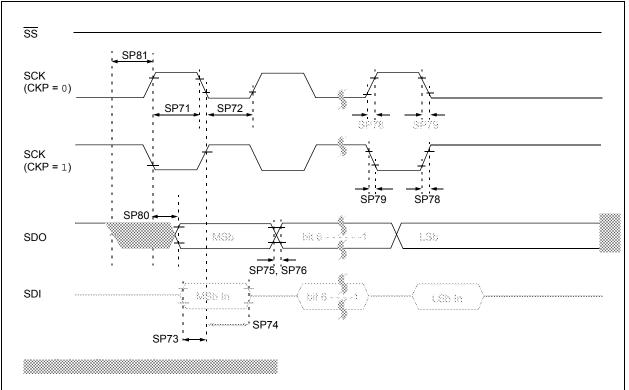

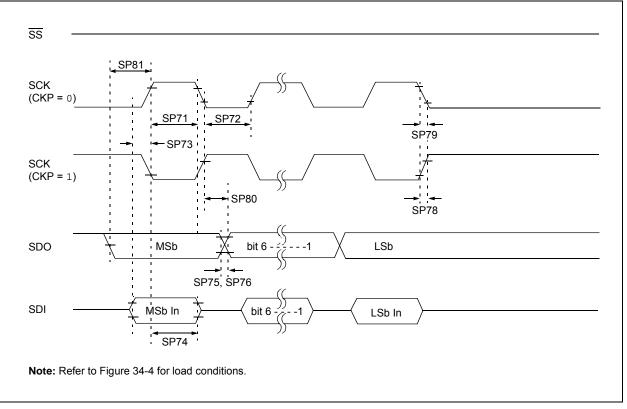

#### FIGURE 34-18: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

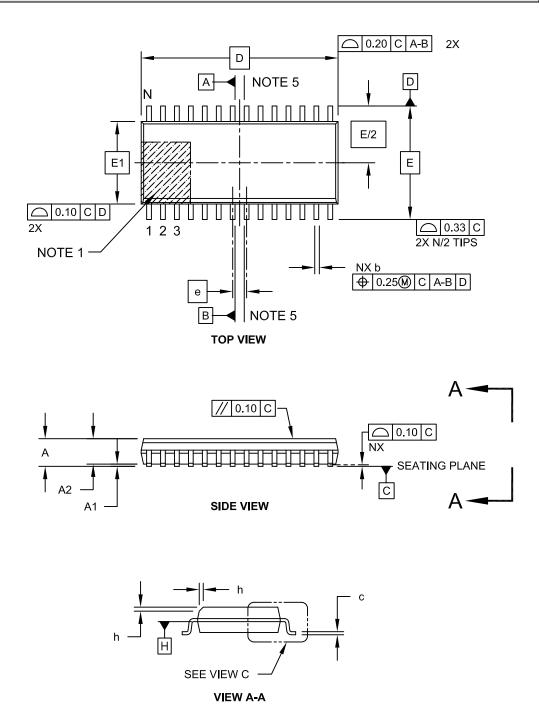

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

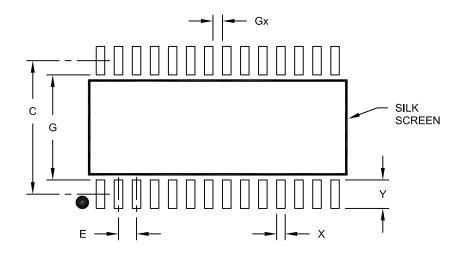

#### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension Limits         |             | MIN      | NOM  | MAX  |

| Contact Pitch            | E           | 1.27 BSC |      |      |

| Contact Pad Spacing      | С           |          | 9.40 |      |

| Contact Pad Width (X28)  | X           |          |      | 0.60 |

| Contact Pad Length (X28) | Y           |          |      | 2.00 |

| Distance Between Pads    | Gx          | 0.67     |      |      |

| Distance Between Pads    | G           | 7.40     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

#### THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support