Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

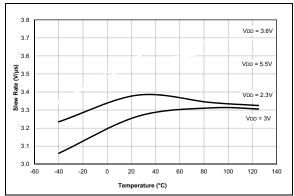

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1716-e-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## TABLE 3-4: PIC16(L)F1716 MEMORY MAP (BANKS 0-7)

|      | BANK 0                                     |      | BANK 1                                     |      | BANK 2                                     |      | BANK 3                                     |      | BANK 4                                     |      | BANK 5                                     |      | BANK 6                                     |      | BANK 7                                     |

|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|--------------------------------------------|

| 000h | Core Registers<br>(Table 3-2)              | 080h | Core Registers<br>(Table 3-2)              | 100h | Core Registers<br>(Table 3-2)              | 180h | Core Registers<br>(Table 3-2)              | 200h | Core Registers<br>(Table 3-2)              | 280h | Core Registers<br>(Table 3-2)              | 300h | Core Registers<br>(Table 3-2)              | 380h | Core Registers<br>(Table 3-2)              |

| 00Bh |                                            | 08Bh |                                            | 10Bh |                                            | 18Bh |                                            | 20Bh |                                            | 28Bh |                                            | 30Bh |                                            | 38Bh |                                            |

| 00Ch | PORTA                                      | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                                     | 20Ch | WPUA                                       | 28Ch | ODCONA                                     | 30Ch | SLRCONA                                    | 38Ch | INLVLA                                     |

| 00Dh | PORTB                                      | 08Dh | TRISB                                      | 10Dh | LATB                                       | 18Dh | ANSELB                                     | 20Dh | WPUB                                       | 28Dh | ODCONB                                     | 30Dh | SLRCONB                                    | 38Dh | INLVLB                                     |

| 00Eh | PORTC                                      | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | ANSELC                                     | 20Eh | WPUC                                       | 28Eh | ODCONC                                     | 30Eh | SLRCONC                                    | 38Eh | INLVLC                                     |

| 00Fh | _                                          | 08Fh | _                                          | 10Fh | _                                          | 18Fh | —                                          | 20Fh | —                                          | 28Fh | _                                          | 30Fh | _                                          | 38Fh | _                                          |

| 010h | PORTE                                      | 090h | TRISE                                      | 110h | _                                          | 190h | —                                          | 210h | WPUE                                       | 290h | _                                          | 310h | _                                          | 390h | INLVLE                                     |

| 011h | PIR1                                       | 091h | PIE1                                       | 111h | CM1CON0                                    | 191h | PMADRL                                     | 211h | SSP1BUF                                    | 291h | CCPR1L                                     | 311h | _                                          | 391h | IOCAP                                      |

| 012h | PIR2                                       | 092h | PIE2                                       | 112h | CM1CON1                                    | 192h | PMADRH                                     | 212h | SSP1ADD                                    | 292h | CCPR1H                                     | 312h | —                                          | 392h | IOCAN                                      |

| 013h | PIR3                                       | 093h | PIE3                                       | 113h | CM2CON0                                    | 193h | PMDATL                                     | 213h | SSP1MSK                                    | 293h | CCP1CON                                    | 313h | —                                          | 393h | IOCAF                                      |

| 014h | _                                          | 094h | —                                          | 114h | CM2CON1                                    | 194h | PMDATH                                     | 214h | SSP1STAT                                   | 294h | _                                          | 314h | —                                          | 394h | IOCBP                                      |

| 015h | TMR0                                       | 095h | OPTION_REG                                 | 115h | CMOUT                                      | 195h | PMCON1                                     | 215h | SSP1CON1                                   | 295h | _                                          | 315h | —                                          | 395h | IOCBN                                      |

| 016h | TMR1L                                      | 096h | PCON                                       | 116h | BORCON                                     | 196h | PMCON2                                     | 216h | SSP1CON2                                   | 296h | _                                          | 316h | —                                          | 396h | IOCBF                                      |

| 017h | TMR1H                                      | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | VREGCON <sup>(1)</sup>                     | 217h | SSP1CON3                                   | 297h | —                                          | 317h | —                                          | 397h | IOCCP                                      |

| 018h | T1CON                                      | 098h | OSCTUNE                                    | 118h | DAC1CON0                                   | 198h | _                                          | 218h | _                                          | 298h | CCPR2L                                     | 318h | —                                          | 398h | IOCCN                                      |

| 019h | T1GCON                                     | 099h | OSCCON                                     | 119h | DAC1CON1                                   | 199h | RC1REG                                     | 219h | _                                          | 299h | CCPR2H                                     | 319h | —                                          | 399h | IOCCF                                      |

| 01Ah | TMR2                                       | 09Ah | OSCSTAT                                    | 11Ah | DAC2CON0                                   | 19Ah | TX1REG                                     | 21Ah | _                                          | 29Ah | CCP2CON                                    | 31Ah | —                                          | 39Ah | _                                          |

| 01Bh | PR2                                        | 09Bh | ADRESL                                     | 11Bh | DAC2CON1                                   | 19Bh | SP1BRGL                                    | 21Bh | _                                          | 29Bh | _                                          | 31Bh | —                                          | 39Bh |                                            |

| 01Ch | T2CON                                      | 09Ch | ADRESH                                     | 11Ch | ZCD1CON                                    | 19Ch | SP1BRGH                                    | 21Ch | _                                          | 29Ch | _                                          | 31Ch | —                                          | 39Ch |                                            |

| 01Dh | _                                          | 09Dh | ADCON0                                     | 11Dh | —                                          | 19Dh | RC1STA                                     | 21Dh | _                                          | 29Dh | _                                          | 31Dh | —                                          | 39Dh | IOCEP                                      |

| 01Eh | _                                          | 09Eh | ADCON1                                     | 11Eh | —                                          | 19Eh | TX1STA                                     | 21Eh | —                                          | 29Eh | CCPTMRS                                    | 31Eh | —                                          | 39Eh | IOCEN                                      |

| 01Fh | —                                          | 09Fh | ADCON2                                     | 11Fh | —                                          | 19Fh | BAUD1CON                                   | 21Fh | —                                          | 29Fh | —                                          | 31Fh | —                                          | 39Fh | IOCEF                                      |

| 020h |                                            | 0A0h |                                            | 120h |                                            | 1A0h |                                            | 220h |                                            | 2A0h |                                            | 320h |                                            | 3A0h |                                            |

|      | General<br>Purpose<br>Register<br>80 Bytes |

| 06Fh |                                            | 0EFh |                                            | 16Fh |                                            | 1EFh |                                            | 26Fh |                                            | 2EFh |                                            | 36Fh |                                            | 3EFh |                                            |

| 070h |                                            | 0F0h |                                            | 170h |                                            | 1F0h |                                            | 270h |                                            | 2F0h |                                            | 370h |                                            | 3F0h |                                            |

|      | Common RAM<br>70h – 7Fh                    |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |

| 07Fh |                                            | 0FFh |                                            | 17Fh |                                            | 1FFh |                                            | 27Fh |                                            | 2FFh |                                            | 37Fh |                                            | 3FFh |                                            |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Unimplemented on PIC16(L)F1713/6.

### TABLE 3-6: PIC16(L)F1716 MEMORY MAP, BANK 8-23

|       | BANK 8                        |       | BANK 9                        |       | BANK 10                       |       | BANK 11                       |      | BANK 12                       |       | BANK 13                       |       | BANK 14                       |      | BANK 15                       |

|-------|-------------------------------|-------|-------------------------------|-------|-------------------------------|-------|-------------------------------|------|-------------------------------|-------|-------------------------------|-------|-------------------------------|------|-------------------------------|

| 400h  |                               | 480h  |                               | 500h  |                               | 580h  |                               | 600h |                               | 680h  |                               | 700h  |                               | 780h |                               |

|       | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |       | Core Registers<br>(Table 3-2) |      | Core Registers<br>(Table 3-2) |

| 40Bh  |                               | 48Bh  |                               | 50Bh  |                               | 58Bh  |                               | 60Bh |                               | 68Bh  |                               | 70Bh  |                               | 78Bh |                               |

| 40Ch  | —                             | 48Ch  | —                             | 50Ch  | —                             | 58Ch  | —                             | 60Ch | —                             | 68Ch  | —                             | 70Ch  | —                             | 78Ch | —                             |

| 40Dh  | —                             | 48Dh  | _                             | 50Dh  | —                             | 58Dh  | —                             | 60Dh | —                             | 68Dh  |                               | 70Dh  | —                             | 78Dh | —                             |

| 40Eh  | —                             | 48Eh  | —                             | 50Eh  | —                             | 58Eh  | —                             | 60Eh | —                             | 68Eh  | —                             | 70Eh  | —                             | 78Eh | —                             |

| 40Fh  | —                             | 48Fh  |                               | 50Fh  | _                             | 58Fh  |                               | 60Fh | —                             | 68Fh  | _                             | 70Fh  |                               | 78Fh | —                             |

| 410h  | _                             | 490h  |                               | 510h  | —                             | 590h  |                               | 610h | —                             | 690h  | —                             | 710h  |                               | 790h | —                             |

| 411h  | _                             | 491h  |                               | 511h  | OPA1CON                       | 591h  |                               | 611h | —                             | 691h  | COG1PHR                       | 711h  |                               | 791h | —                             |

| 412h  | —                             | 492h  | —                             | 512h  | —                             | 592h  | —                             | 612h | —                             | 692h  | COG1PHF                       | 712h  | —                             | 792h | —                             |

| 413h  | _                             | 493h  |                               | 513h  | _                             | 593h  |                               | 613h | _                             | 693h  | COG1BLKR                      | 713h  | _                             | 793h | _                             |

| 414h  | —                             | 494h  | —                             | 514h  | —                             | 594h  | —                             | 614h | —                             | 694h  | COG1BLKF                      | 714h  | —                             | 794h | —                             |

| 415h  | TMR4                          | 495h  |                               | 515h  | OPA2CON                       | 595h  |                               | 615h | —                             | 695h  | COG1DBR                       | 715h  | —                             | 795h | —                             |

| 416h  | PR4                           | 496h  | —                             | 516h  | —                             | 596h  | —                             | 616h | —                             | 696h  | COG1DBF                       | 716h  | —                             | 796h | —                             |

| 417h  | T4CON                         | 497h  |                               | 517h  | _                             | 597h  |                               | 617h | PWM3DCL                       | 697h  | COG1CON0                      | 717h  | _                             | 797h | _                             |

| 418h  | —                             | 498h  | NCO1ACCL                      | 518h  | —                             | 598h  | —                             | 618h | PWM3DCH                       | 698h  | COG1CON1                      | 718h  | —                             | 798h | —                             |

| 419h  | _                             | 499h  | NCO1ACCH                      | 519h  | _                             | 599h  |                               | 619h | PWM3CON                       | 699h  | COG1RIS                       | 719h  |                               | 799h | —                             |

| 41Ah  | —                             | 49Ah  | NCO1ACCU                      | 51Ah  | —                             | 59Ah  | —                             | 61Ah | PWM4DCL                       | 69Ah  | COG1RSIM                      | 71Ah  | —                             | 79Ah | —                             |

| 41Bh  | —                             | 49Bh  | NCO1INCL                      | 51Bh  | —                             | 59Bh  | —                             | 61Bh | PWM4DCH                       | 69Bh  | COG1FIS                       | 71Bh  | —                             | 79Bh | —                             |

| 41Ch  | TMR6                          | 49Ch  | NCO1INCH                      | 51Ch  |                               | 59Ch  | _                             | 61Ch | PWM4CON                       | 69Ch  | COG1FSIM                      | 71Ch  | —                             | 79Ch | _                             |

| 41Dh  | PR6                           | 49Dh  | NCO1INCU                      | 51Dh  | —                             | 59Dh  | —                             | 61Dh | —                             | 69Dh  | COG1ASD0                      | 71Dh  | —                             | 79Dh | —                             |

| 41Eh  | T6CON                         | 49Eh  | NCO1CON                       | 51Eh  | —                             | 59Eh  | _                             | 61Eh | _                             | 69Eh  | COG1ASD1                      | 71Eh  | —                             | 79Eh | _                             |

| 41Fh  | —                             | 49Fh  | NCO1CLK                       | 51Fh  | —                             | 59Fh  | —                             | 61Fh | —                             | 69Fh  | COG1STR                       | 71Fh  | —                             | 79Fh | —                             |

| 420h  |                               | 4A0h  |                               | 520h  |                               | 5A0h  |                               | 620h | General Purpose               | 6A0h  |                               | 720h  |                               | 7A0h |                               |

|       | General                       |       | General                       |       | General                       |       | General                       |      | Register                      |       |                               |       |                               |      |                               |

|       | Purpose                       |       | Purpose                       |       | Purpose                       |       | Purpose                       |      | 48 Bytes                      |       | Unimplemented                 |       | Unimplemented                 |      | Unimplemented                 |

|       | Register                      |       | Register                      |       | Register                      |       | Register                      | 64Fh | Unimplemented                 |       | Read as '0'                   |       | Read as '0'                   |      | Read as '0'                   |

|       | 80 Bytes                      |       | 80 Bytes                      |       | 80 Bytes                      |       | 80 Bytes                      |      | Read as '0'                   |       |                               |       |                               |      |                               |

| 46Fh  |                               | 4EFh  |                               | 56Fh  |                               | 5EFh  |                               | 66Fh |                               | 6EFh  |                               | 76Fh  |                               | 7EFh |                               |

| 470h  |                               | 4F0h  |                               | 570h  |                               | 5F0h  |                               | 670h |                               | 6F0h  |                               | 770h  |                               | 7F0h |                               |

|       | Accesses                      |       | Accesses                      |       | Accesses                      |       | Accesses                      |      | Accesses                      |       | Accesses                      |       | Accesses                      |      | Accesses                      |

|       | 70h – 7Fh                     |      | 70h – 7Fh                     |       | 70h – 7Fh                     |       | 70h – 7Fh                     |      | 70h – 7Fh                     |

| 47Fh  |                               | 4FFh  |                               | 57Fh  |                               | 5FFh  |                               | 67Fh |                               | 6FFh  |                               | 77Fh  |                               | 7FFh |                               |

|       | BANK 16                       |       | BANK 17                       |       | BANK 18                       |       | BANK 19                       |      | BANK 20                       |       | BANK 21                       |       | BANK 22                       |      | BANK 23                       |

| 800h  |                               | 880h  |                               | 900h  |                               | 980h  |                               | A00h |                               | A80h  |                               | B00h  |                               | B80h |                               |

|       | Core Registers                |       | Core Registers                |       | Core Registers                |       | Core Registers                |      | Core Registers                |       | Core Registers                |       | Core Registers                |      | Core Registers                |

|       | (Table 3-2)                   |       | (Table 3-2)                   |       | (Table 3-2)                   |       | (Table 3-2)                   |      | (Table 3-2)                   |       | (Table 3-2)                   |       | (Table 3-2)                   |      | (Table 3-2)                   |

| 80Bh  |                               | 88Bh  |                               | 90Bh  |                               | 98Bh  |                               | A0Bh |                               | A8Bh  |                               | B0Bh  |                               | B8Bh |                               |

| 80Ch  |                               | 88Ch  |                               | 90Ch  |                               | 98Ch  |                               | A0Ch |                               | A8Ch  |                               | B0Ch  |                               | B8Ch |                               |

| 00011 | Unimplemented                 | 00011 | Unimplemented                 | 30011 | Unimplemented                 | 30011 | Unimplemented                 | Auon | Unimplemented                 | AUCII | Unimplemented                 | DUCII | Unimplemented                 | Doon | Unimplemented                 |

|       | Read as '0'                   |      | Read as '0'                   |       | Read as '0'                   |       | Read as '0'                   |      | Read as '0'                   |

| 005   |                               | 000   |                               | 005   |                               |       |                               |      |                               |       |                               | DOC   |                               | DEEL |                               |

| 86Fh  |                               | 8EFh  |                               | 96Fh  |                               | 9EFh  |                               | A6Fh |                               | AEFh  |                               | B6Fh  |                               | BEFh |                               |

| 870h  |                               | 8F0h  |                               | 970h  |                               | 9F0h  |                               | A70h |                               | AF0h  |                               | B70h  |                               | BF0h |                               |

|       | Accesses                      |       | Accesses                      |       | Accesses                      |       | Accesses                      |      | Accesses                      |       | Accesses                      |       | Accesses                      |      | Accesses                      |

|       | 70h – 7Fh                     |      | 70h – 7Fh                     |       | 70h – 7Fh                     |       | 70h – 7Fh                     |      | 70h – 7Fh                     |

| 87Fh  |                               | 8FFh  |                               | 97Fh  |                               | 9FFh  |                               | A7Fh |                               | AFFh  |                               | B7Fh  |                               | BFFh |                               |

Legend: = Unimplemented data memory locations, read as '0'.

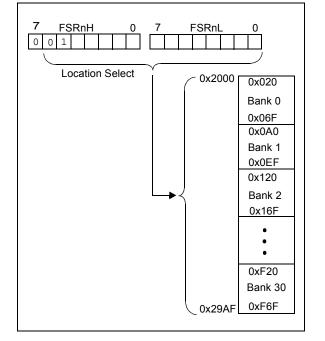

### 3.7.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

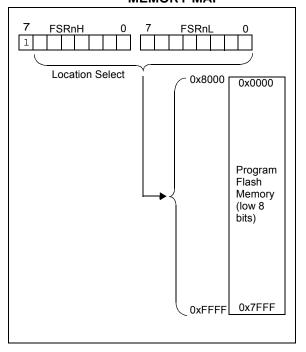

#### 3.7.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower eight bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

# PIC16(L)F1713/6

|        | •••    |       |       |       |           | •••••• |       | <b>—</b> ··· |                     |

|--------|--------|-------|-------|-------|-----------|--------|-------|--------------|---------------------|

| Name   | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2  | Bit 1 | Bit 0        | Register<br>on Page |

| OSCCON | SPLLEN |       | IRCF  | <3:0> |           | —      | SCS   | 75           |                     |

| STATUS | —      | _     | —     | TO    | PD        | Z      | DC    | С            | 19                  |

| WDTCON | —      | —     |       | ١     | WDTPS<4:0 | >      |       | SWDTEN       | 98                  |

TABLE 9-3:

SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

| TABLE 9-4:       | SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER |

|------------------|---------------------------------------------------|

| IADLE $3^{-4}$ . |                                                   |

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1    | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|----------|------------|---------|---------------------|

| CONFIG1 | 13:8 |         |         | FCMEN    | IESO      | CLKOUTEN | BOREN    | BOREN<1:0> |         | 47                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | F        | >          | 4/      |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

| <b>REGISTER 11-12:</b> | ANSELB: PORTB ANALOG SELECT REGISTER |

|------------------------|--------------------------------------|

|------------------------|--------------------------------------|

| U-0   | R/W-1/1           | R/W-1/1                                                          | R/W-1/1                                               | R/W-1/1                                                                                                                         | R/W-1/1                                                                                                                                                                                        | R/W-1/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------|-------------------|------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       | ANSB5             | ANSB4                                                            | ANSB3                                                 | ANSB2                                                                                                                           | ANSB1                                                                                                                                                                                          | ANSB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|       | ·                 |                                                                  | ·                                                     | •                                                                                                                               |                                                                                                                                                                                                | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|       |                   |                                                                  |                                                       |                                                                                                                                 |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|       |                   |                                                                  |                                                       |                                                                                                                                 |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| bit   | W = Writable      | bit                                                              | U = Unimplemented bit, read as '0'                    |                                                                                                                                 |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| anged | x = Bit is unkr   | nown                                                             | -n/n = Value at POR and BOR/Value at all other Resets |                                                                                                                                 |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|       | '0' = Bit is clea | ared                                                             |                                                       |                                                                                                                                 |                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|       | bit               | ANSB5       bit     W = Writable       anged     x = Bit is unkr | —     ANSB5     ANSB4       bit     W = Writable bit  | ANSB5     ANSB4     ANSB3       bit     W = Writable bit     U = Unimpler       anged     x = Bit is unknown     -n/n = Value a | —       ANSB5       ANSB4       ANSB3       ANSB2         bit       W = Writable bit       U = Unimplemented bit, read         anged       x = Bit is unknown       -n/n = Value at POR and BO | —       ANSB5       ANSB4       ANSB3       ANSB2       ANSB1         bit       W = Writable bit       U = Unimplemented bit, read as '0'         anged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all of the second |  |  |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSB<5:0>**: Analog Select between Analog or Digital Function on pins RB<5:4>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### REGISTER 11-13: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 WPUB<7:0>: Weak Pull-up Register bits

- 1 = Pull-up enabled

- 0 = Pull-up disabled

- Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| U-0            | U-0               | U-0              | R/W-0/u         | R/W-0/u        | R/W-0/u          | R/W-0/u          | R/W-0/u     |

|----------------|-------------------|------------------|-----------------|----------------|------------------|------------------|-------------|

| _              | —                 | —                |                 |                | RxyPPS<4:0>      |                  |             |

| pit 7          |                   |                  |                 |                |                  |                  | bi          |

|                |                   |                  |                 |                |                  |                  |             |

| Legend:        |                   |                  |                 |                |                  |                  |             |

| R = Readab     | ole bit           | W = Writable     | e bit           | U = Unimplen   | nented bit, read | l as '0'         |             |

| u = Bit is un  | changed           | x = Bit is unl   | known           | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is s | et                | '0' = Bit is cl  | eared           |                |                  |                  |             |

|                | l lus incur la un | antadi Daad aa   | (o)             |                |                  |                  |             |

| bit 7-5        | -                 | ented: Read as   |                 | laction bita   | DODTA            |                  | DODTO       |

| bit 4-0        | 11xxx = R         | I:0>: Pin Rxy Ou | ilput Source Se | ection bits    | PORTA            | PORTB            | PORTC       |

|                |                   | xy source is C2  |                 |                | х                |                  | Х           |

|                |                   | xy source is C2  |                 |                | X                |                  | X           |

|                |                   | xy source is DT  |                 |                |                  | Х                | Х           |

|                |                   | xy source is TX  |                 |                |                  | Х                | Х           |

|                | 10100 = R         |                  | OR              |                |                  |                  |             |

|                | 10011 = R         |                  |                 |                |                  |                  |             |

|                |                   | xy source is SD  | (1) مחא         |                |                  | N/               | V           |

|                |                   | xy source is SC  |                 |                |                  | X<br>X           | X<br>X      |

|                | 10000 - 10        |                  | NOOL            |                |                  | ~                | ~           |

|                | 01111 <b>= R</b>  | xy source is PW  | /M4OUT          |                |                  | х                | Х           |

|                |                   | xy source is PW  |                 |                |                  | Х                | Х           |

|                |                   | xy source is CC  |                 |                |                  | Х                | Х           |

|                |                   | xy source is CC  |                 |                |                  | Х                | Х           |

|                |                   | xy source is CO  |                 |                |                  | Х                | Х           |

|                |                   | xy source is CO  |                 |                |                  | Х                | Х           |

|                |                   | xy source is CO  |                 |                |                  | X                | Х           |

|                |                   | xy source is CO  |                 |                |                  | Х                | Х           |

|                | 00111 <b>- D</b>  |                  | 1 out           |                |                  |                  | X           |

|                |                   | xy source is LC  | _               |                |                  | X<br>X           | X           |

|                |                   | xy source is LC  | _               |                | ×                | X                | X           |

|                |                   | xy source is LC  | _               |                | X<br>X           |                  | X<br>X      |

|                |                   | xy source is LC  |                 |                | ×                |                  | X           |

|                |                   | xy source is NC  | O1_out          |                | X                |                  | χ           |

|                | 00010 = R         |                  |                 |                |                  |                  |             |

|                | 00001 = R         |                  |                 |                | Х                | х                | Х           |

|                | 00000 = R         | xy source is LA  | іху             |                |                  |                  |             |

|                | Example: F        | RC3PPS = 0x0D    | outputs CCP2    | on RC3         |                  |                  |             |

|                | Outputs are       | e available only | on those ports  | indicated with |                  |                  |             |

|                |                   |                  | -               |                |                  |                  |             |

### REGISTER 12-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER

a check.

**Note 1:** TRIS control is overridden by the peripheral as required.

#### 18.5.4 RISING EVENT DEAD-BAND

Rising event dead band delays the turn-on of the primary outputs from when complementary outputs are turned off. The rising event dead-band time starts when the rising\_ event output goes true.

See Section 18.5.1, Asynchronous Delay Chain Dead-band Delay and Section 18.5.2, Synchronous Counter Dead-band Delay for more information on setting the rising edge dead-band time.

#### 18.5.5 FALLING EVENT DEAD-BAND

Falling event dead band delays the turn-on of complementary outputs from when the primary outputs are turned off. The falling event dead-band time starts when the falling event output goes true.

See Section 18.5.1, Asynchronous Delay Chain Dead-band Delay and Section 18.5.2, Synchronous Counter Dead-band Delay for more information on setting the rising edge dead-band time.

#### 18.5.6 DEAD-BAND OVERLAP

There are two cases of dead-band overlap:

- Rising-to-falling

- Falling-to-rising

#### 18.5.6.1 Rising-to-Falling Overlap

In this case, the falling event occurs while the rising event dead-band counter is still counting. When this happens, the primary drives are suppressed and the dead-band extends by the falling event dead-band time. At the termination of the extended dead-band time, the complementary drive goes true.

#### 18.5.6.2 Falling-to-Rising Overlap

In this case, the rising event occurs while the falling event dead-band counter is still counting. When this happens, the complementary drive is suppressed and the dead-band extends by the rising event dead-band time. At the termination of the extended dead-band time, the primary drive goes true.

#### 18.6 Blanking Control

Input blanking is a function, whereby, the event inputs can be masked or blanked for a short period of time. This is to prevent electrical transients caused by the turn-on/off of power components from generating a false input event.

The COG contains two blanking counters: one triggered by the rising event and the other triggered by the falling event. The counters are cross coupled with the events they are blanking. The falling event blanking counter is used to blank rising input events and the rising event blanking counter is used to blank falling input events. Once started, blanking extends for the time specified by the corresponding blanking counter. Blanking is timed by counting COG\_clock periods from zero up to the value in the blanking count register. Use Equation 18-1 to calculate blanking times.

#### 18.6.1 FALLING EVENT BLANKING OF RISING EVENT INPUTS

The falling event blanking counter inhibits rising event inputs from triggering a rising event. The falling event blanking time starts when the rising event output drive goes false.

The falling event blanking time is set by the value contained in the COGxBLKF register (Register 18-13). Blanking times are calculated using the formula shown in Equation 18-1.

When the COGxBLKF value is zero, falling event blanking is disabled and the blanking counter output is true, thereby, allowing the event signal to pass straight through to the event trigger circuit.

#### 18.6.2 RISING EVENT BLANKING OF FALLING EVENT INPUTS

The rising event blanking counter inhibits falling event inputs from triggering a falling event. The rising event blanking time starts when the falling event output drive goes false.

The rising event blanking time is set by the value contained in the COGxBLKR register (Register 18-12).

When the COGxBLKR value is zero, rising event blanking is disabled and the blanking counter output is true, thereby, allowing the event signal to pass straight through to the event trigger circuit.

#### 18.6.3 BLANKING TIME UNCERTAINTY

When the rising and falling sources that trigger the blanking counters are asynchronous to the COG\_clock, it creates uncertainty in the blanking time. The maximum uncertainty is equal to one COG\_clock period. Refer to Equation 18-1 and Example 18-1 for more detail.

#### 18.7 Phase Delay

It is possible to delay the assertion of either or both the rising event and falling events. This is accomplished by placing a non-zero value in COGxPHR or COGxPHF phase-delay count register, respectively (Register 18-14 and Register 18-15). Refer to Figure 18-10 for COG operation with CCP1 and phase delay. The delay from the input rising event signal switching to the actual assertion of the events is calculated the same as the dead-band and blanking delays. Refer to Equation 18-1.

When the phase-delay count value is zero, phase delay is disabled and the phase-delay counter output is true, thereby, allowing the event signal to pass straight through to the complementary output driver flop.

<sup>© 2013-2016</sup> Microchip Technology Inc.

#### REGISTER 18-4: COGxRSIM: COG RISING EVENT SOURCE INPUT MODE REGISTER

bit 0

GxRSIM0: COGx Rising Event Input Source 0 Mode bit

<u>GxRIS0 = 1:</u>

- 1 = Pin selected with COGxPPS control low-to-high transition will cause a rising event after rising event phase delay

- 0 = Pin selected with COGxPPS control high level will cause an immediate rising event

<u>GxRIS0 = 0:</u>

Pin selected with COGxPPS control has no effect on rising event

# PIC16(L)F1713/6

#### TABLE 21-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) | Device Frequency (Fosc)     |                             |                             |                             |                               |                             |  |  |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|-----------------------------|--|--|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                         | 1 MHz                       |  |  |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>         | 2.0 μs                      |  |  |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                        | 4.0 μs                      |  |  |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                        | 8.0 μs <sup>(3)</sup>       |  |  |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                        | 16.0 μs <sup>(3)</sup>      |  |  |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>         | 32.0 μs <sup>(2)</sup>      |  |  |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <b><sup>(2)</sup></b> | 64.0 μs <sup>(2)</sup>      |  |  |  |

| FRC                 | x11         | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup> |  |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** See TAD parameter for FRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

### 27.5 Register Definitions: Timer2 Control

### REGISTER 27-1: T2CON: TIMER2 CONTROL REGISTER

| U-0             | R/W-0/0                                         | R/W-0/0           | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0 | R/W-0/0      |  |  |

|-----------------|-------------------------------------------------|-------------------|----------------|----------------|------------------|---------|--------------|--|--|

|                 |                                                 | T2OUTF            | PS<3:0>        |                | TMR2ON           | T2CKF   | 'S<1:0>      |  |  |

| bit 7           |                                                 |                   |                |                |                  |         | bit (        |  |  |

| Legend:         |                                                 |                   |                |                |                  |         |              |  |  |

| R = Readab      | le bit                                          | W = Writable      | hit            | U = Unimpler   | nented bit, read | as '0'  |              |  |  |

| u = Bit is un   |                                                 | x = Bit is unkr   |                | •              | at POR and BO    |         | other Resets |  |  |

| '1' = Bit is se | -                                               | '0' = Bit is clea |                |                |                  |         |              |  |  |

| 1 Ditio ot      |                                                 |                   |                |                |                  |         |              |  |  |

| bit 7           | Unimpleme                                       | nted: Read as '   | 0'             |                |                  |         |              |  |  |

| bit 6-3         | T2OUTPS<                                        | 3:0>: Timer2 Ou   | tput Postscale | er Select bits |                  |         |              |  |  |

|                 | 1111 <b>= 1</b> :16                             | Postscaler        |                |                |                  |         |              |  |  |

|                 | 1110 <b>= 1:15</b>                              | Postscaler        |                |                |                  |         |              |  |  |

|                 | 1101 <b>= 1:14</b>                              |                   |                |                |                  |         |              |  |  |

|                 | 1100 = 1:13 Postscaler                          |                   |                |                |                  |         |              |  |  |

|                 | 1011 = 1:12 Postscaler                          |                   |                |                |                  |         |              |  |  |

|                 | 1010 = 1:11 Postscaler                          |                   |                |                |                  |         |              |  |  |

|                 | 1001 = 1:10 Postscaler<br>1000 = 1:9 Postscaler |                   |                |                |                  |         |              |  |  |

|                 | 0111 = 1:8                                      |                   |                |                |                  |         |              |  |  |

|                 | 0110 = 1:7                                      |                   |                |                |                  |         |              |  |  |

|                 | 0101 = 1:6                                      |                   |                |                |                  |         |              |  |  |

|                 | 0100 = 1:5                                      |                   |                |                |                  |         |              |  |  |

|                 | 0011 = 1:4                                      |                   |                |                |                  |         |              |  |  |

|                 | 0010 = 1:3 I                                    | Postscaler        |                |                |                  |         |              |  |  |

|                 | 0001 = 1:2 I                                    | Postscaler        |                |                |                  |         |              |  |  |

|                 | 0000 <b>= 1:1  </b>                             | Postscaler        |                |                |                  |         |              |  |  |

| bit 2           | TMR2ON: T                                       | ïmer2 On bit      |                |                |                  |         |              |  |  |

|                 | 1 = Timer2<br>0 = Timer2                        |                   |                |                |                  |         |              |  |  |