Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

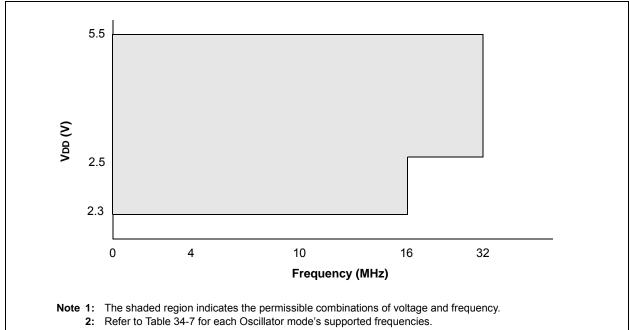

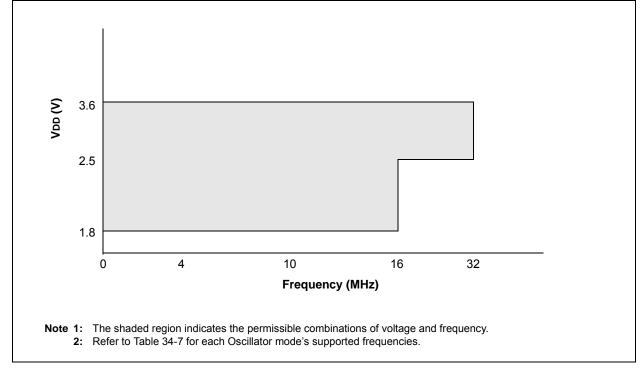

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1716t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode (4-20 MHz): device clock supplied to CLKIN pin

- 110 = ECM: External Clock, Medium Power mode (0.5-4 MHz): device clock supplied to CLKIN pin

- 101 = ECL: External Clock, Low-Power mode (0-0.5 MHz): device clock supplied to CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

- **Note 1:** The entire Flash program memory will be erased when the code protection is turned off during an erase. When a Bulk Erase Program Memory Command is executed, the entire program Flash memory and configuration memory will be erased.

## 11.6 Register Definitions: PORTC

### REGISTER 11-17: PORTC: PORTC REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-----------------------------------------|---------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| RC7                                     | RC6     | RC5                | RC4     | RC3                                                   | RC2     | RC1     | RC0     |  |  |

| bit 7                                   |         |                    |         |                                                       |         |         | bit 0   |  |  |

|                                         |         |                    |         |                                                       |         |         |         |  |  |

| Legend:                                 |         |                    |         |                                                       |         |         |         |  |  |

| R = Readable bit W = Writable bit       |         |                    | it      | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                    | wn      | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clear | red     |                                                       |         |         |         |  |  |

bit 7-0

RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup>

1 = Port pin is

VIH

0 = Port pin is

VIL

## REGISTER 11-18: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

## REGISTER 11-19: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

## 13.6 Register Definitions: Interrupt-on-Change Control

#### REGISTER 13-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCAP7  | IOCAP6  | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

IOCAP<7:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCAN7  | IOCAN6  | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **IOCAN<7:0>:** Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

| Legend:    |            |            |            |            |            |            |            |

|------------|------------|------------|------------|------------|------------|------------|------------|

| bit 7      |            |            |            |            |            |            | bit 0      |

| IOCAF7     | IOCAF6     | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| R/W/HS-0/0 |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

|                      | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| u = Bit is unchanged |                      |                                                       |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

**IOCAF<7:0>:** Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

#### REGISTER 13-4: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------------|---------|---------|---------|---------|---------|---------|---------|--|

| IOCBP7      | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2  | IOCBP1  | IOCBP0  |  |

| bit 7 bit 0 |         |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCBP<7:0>:** Interrupt-on-Change PORTB Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

## 18.2 Clock Sources

The COG\_clock is used as the reference clock to the various timers in the peripheral. Timers that use the COG\_clock include:

- Rising and falling dead-band time

- Rising and falling blanking time

- · Rising and falling event phase delay

Clock sources available for selection include:

- 8 MHz HFINTOSC (active during Sleep)

- Instruction clock (Fosc/4)

- System clock (Fosc)

The clock source is selected with the GxCS<1:0> bits of the COGxCON0 register (Register 18-1).

#### 18.3 Selectable Event Sources

The COG uses any combination of independently selectable event sources to generate the complementary waveform. Sources fall into two categories:

- · Rising event sources

- Falling event sources

The rising event sources are selected by setting bits in the COGxRIS register (Register 18-3). The falling event sources are selected by setting bits in the COGxFIS register (Register 18-5). All selected sources are 'OR'd together to generate the corresponding event signal. Refer to Figure 18-7.

### 18.3.1 EDGE VS. LEVEL SENSING

Event input detection may be selected as level or edge sensitive. The detection mode is individually selectable for every source. Rising source detection modes are selected with the COGxRSIM register (Register 18-4). Falling source detection modes are selected with the COGxFSIM register (Register 18-6). A set bit enables edge detection for the corresponding event source. A cleared bit enables level detection.

In general, events that are driven from a periodic source should be edge detected and events that are derived from voltage thresholds at the target circuit should be level sensitive. Consider the following two examples:

1. The first example is an application in which the period is determined by a 50% duty cycle clock and the COG output duty cycle is determined by a voltage level fed back through a comparator. If the clock input is level sensitive, duty cycles less than 50% will exhibit erratic operation.

2. The second example is similar to the first except that the duty cycle is close to 100%. The feedback comparator high-to-low transition trips the COG drive off, but almost immediately the period source turns the drive back on. If the off cycle is short enough, the comparator input may not reach the low side of the hysteresis band precluding an output change. The comparator output stays low and without a high-to-low transition to trigger the edge sense, the drive of the COG output will be stuck in a constant drive-on condition. See Figure 18-14.

#### FIGURE 18-14: EDGE VS LEVEL SENSE

| Rising (CCP1)   |

|-----------------|

| Falling (C1OUT) |

| C1IN- hyst I    |

| COGOUT          |

| Edge Sensitive  |

| Rising (CCP1)   |

| Falling (C1OUT) |

| C1IN- hyst [    |

| COGOUT          |

| Level Sensitive |

#### 18.3.2 RISING EVENT

The rising event starts the PWM output active duty cycle period. The rising event is the low-to-high transition of the rising\_event output. When the rising event phase delay and dead-band time values are zero, the primary output starts immediately. Otherwise, the primary output is delayed. The rising event source causes all the following actions:

- · Start rising event phase delay counter (if enabled).

- · Clear complementary output after phase delay.

- Start falling event input blanking (if enabled).

- · Start dead-band delay (if enabled).

- · Set primary output after dead-band delay expires.

#### 18.3.3 FALLING EVENT

The falling event terminates the PWM output active duty cycle period. The falling event is the high-to-low transition of the falling\_event output. When the falling event phase delay and dead-band time values are zero, the complementary output starts immediately. Otherwise, the complementary output is delayed. The falling event source causes all the following actions:

- Start falling event phase delay counter (if enabled).

- · Clear primary output.

- · Start rising event input blanking (if enabled).

- · Start falling event dead-band delay (if enabled).

- Set complementary output after dead-band delay expires.

## **19.6 Register Definitions: CLC Control**

| R/W-0/0         | U-0                                                                                                                 | R-0/0                                                                                                                                                          | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|------------------|-------------|--|--|--|--|

| LCxEN           |                                                                                                                     | LCxOUT                                                                                                                                                         | LCxINTP        | LCxINTN          | L                | CxMODE<2:0>      | >           |  |  |  |  |

| bit 7           |                                                                                                                     |                                                                                                                                                                |                |                  |                  |                  | bit C       |  |  |  |  |

|                 |                                                                                                                     |                                                                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

| Legend:         |                                                                                                                     |                                                                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

| R = Readabl     | le bit                                                                                                              | W = Writable                                                                                                                                                   | bit            | U = Unimpler     | nented bit, read | l as '0'         |             |  |  |  |  |

| u = Bit is und  | changed                                                                                                             | x = Bit is unkr                                                                                                                                                | nown           | -n/n = Value a   | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is se | et                                                                                                                  | '0' = Bit is cle                                                                                                                                               | ared           |                  |                  |                  |             |  |  |  |  |

|                 |                                                                                                                     |                                                                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

| bit 7           |                                                                                                                     | igurable Logic                                                                                                                                                 |                |                  |                  |                  |             |  |  |  |  |

|                 |                                                                                                                     | <ul> <li>1 = Configurable logic cell is enabled and mixing input signals</li> <li>0 = Configurable logic cell is disabled and has logic zero output</li> </ul> |                |                  |                  |                  |             |  |  |  |  |

| L:1 0           | -                                                                                                                   | -                                                                                                                                                              |                | i nas logic zero | σοιτραί          |                  |             |  |  |  |  |

| bit 6           | •                                                                                                                   | ted: Read as '                                                                                                                                                 |                | 1. 1.1.1         |                  |                  |             |  |  |  |  |

| bit 5           |                                                                                                                     | LCxOUT: Configurable Logic Cell Data Output bit                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

|                 | •                                                                                                                   | Read-only: logic cell output data, after LCxPOL; sampled from LCx_out wire.                                                                                    |                |                  |                  |                  |             |  |  |  |  |

| bit 4           |                                                                                                                     | LCxINTP: Configurable Logic Cell Positive Edge Going Interrupt Enable bit                                                                                      |                |                  |                  |                  |             |  |  |  |  |

|                 | <ul> <li>1 = CLCxIF will be set when a rising edge occurs on LCx_out</li> <li>0 = CLCxIF will not be set</li> </ul> |                                                                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

| bit 3           | <b>LCxINTN:</b> Configurable Logic Cell Negative Edge Going Interrupt Enable bit                                    |                                                                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

|                 | 1 = CLCxIF will be set when a falling edge occurs on LCx out                                                        |                                                                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

|                 | 0 = CLCxIF v                                                                                                        | 0 = CLCxIF will not be set                                                                                                                                     |                |                  |                  |                  |             |  |  |  |  |

| bit 2-0         | LCxMODE<2                                                                                                           | : <b>0&gt;:</b> Configura                                                                                                                                      | ble Logic Cell | Functional Mo    | de bits          |                  |             |  |  |  |  |

|                 |                                                                                                                     | 111 = Cell is 1-input transparent latch with S and R                                                                                                           |                |                  |                  |                  |             |  |  |  |  |

|                 |                                                                                                                     | 110 = Cell is J-K flip-flop with R                                                                                                                             |                |                  |                  |                  |             |  |  |  |  |

|                 |                                                                                                                     | 101 = Cell is 2-input D flip-flop with R<br>100 = Cell is 1-input D flip-flop with S and R                                                                     |                |                  |                  |                  |             |  |  |  |  |

|                 | 011 = Cell is                                                                                                       | •                                                                                                                                                              |                |                  |                  |                  |             |  |  |  |  |

|                 | 010 = Cell is                                                                                                       |                                                                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

|                 | 001 = Cell is                                                                                                       |                                                                                                                                                                |                |                  |                  |                  |             |  |  |  |  |

|                 | 000 = Cell is                                                                                                       | AND-OR                                                                                                                                                         |                |                  |                  |                  |             |  |  |  |  |

#### REGISTER 19-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

### REGISTER 19-6: CLCxSEL3: GENERIC CLCx DATA 4 SELECT REGISTER

| U-0                                     | U-0 | U-0               | R/W-x/u                                               | R/W-x/u                            | R/W-x/u     | R/W-x/u | R/W-x/u |  |  |

|-----------------------------------------|-----|-------------------|-------------------------------------------------------|------------------------------------|-------------|---------|---------|--|--|

| _                                       |     | —                 |                                                       |                                    | LCxD4S<4:0> |         |         |  |  |

| bit 7                                   |     |                   |                                                       |                                    |             |         | bit 0   |  |  |

|                                         |     |                   |                                                       |                                    |             |         |         |  |  |

| Legend:                                 |     |                   |                                                       |                                    |             |         |         |  |  |

| R = Readable b                          | pit | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |             |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |     | iown              | -n/n = Value at POR and BOR/Value at all other Resets |                                    |             |         |         |  |  |

| '1' = Bit is set                        |     | '0' = Bit is clea | ared                                                  |                                    |             |         |         |  |  |

|                                         |     |                   |                                                       |                                    |             |         |         |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 LCxD4S<4:0>: CLCx Data 4 Input Selection bits See Table 19-1.

| R/W-x/u          | R/W-x/u       | R/W-x/u                           | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |  |

|------------------|---------------|-----------------------------------|----------------|----------------|------------------|------------------|-------------|--|--|--|

| LCxG3D4T         | LCxG3D4N      | LCxG3D3T                          | LCxG3D3N       | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |  |  |  |

| bit 7            | ·             |                                   |                |                |                  |                  | bit (       |  |  |  |

|                  |               |                                   |                |                |                  |                  |             |  |  |  |

| Legend:          |               |                                   |                |                |                  |                  |             |  |  |  |

| R = Readable     | bit           | W = Writable                      | bit            | •              | nented bit, read |                  |             |  |  |  |

| u = Bit is uncha | anged         | x = Bit is unkr                   | nown           | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is set |               | '0' = Bit is clea                 | ared           |                |                  |                  |             |  |  |  |

| L:1 7            |               |                                   |                |                |                  |                  |             |  |  |  |

| bit 7            |               | Sate 3 Data 4 T                   | •              | ted) bit       |                  |                  |             |  |  |  |

|                  |               | gated into lcxg<br>not gated into |                |                |                  |                  |             |  |  |  |

| bit 6            |               | Gate 3 Data 4 I                   | 0              | ted) bit       |                  |                  |             |  |  |  |

|                  |               | gated into Icxo                   | •              |                |                  |                  |             |  |  |  |

|                  |               | not gated into                    |                |                |                  |                  |             |  |  |  |

| bit 5            | LCxG3D3T: O   | Gate 3 Data 3 T                   | rue (non-inver | rted) bit      |                  |                  |             |  |  |  |

|                  | 1 = Icxd3T is | gated into lcxg                   | <b>j</b> 3     |                |                  |                  |             |  |  |  |

|                  | 0 = Icxd3T is | not gated into                    | lcxg3          |                |                  |                  |             |  |  |  |

| bit 4            |               | Gate 3 Data 3 I                   | •              | rted) bit      |                  |                  |             |  |  |  |

|                  |               | gated into loxo                   |                |                |                  |                  |             |  |  |  |

|                  |               | not gated into                    | •              |                |                  |                  |             |  |  |  |

| bit 3            |               | Sate 3 Data 2 T                   | •              | rted) bit      |                  |                  |             |  |  |  |

|                  |               | gated into lcxg<br>not gated into |                |                |                  |                  |             |  |  |  |

| bit 2            |               | Gate 3 Data 2 I                   | •              | ted) bit       |                  |                  |             |  |  |  |

| SIL              |               | gated into Icxo                   | •              |                |                  |                  |             |  |  |  |

|                  |               | not gated into                    |                |                |                  |                  |             |  |  |  |

| bit 1            | LCxG3D1T: G   | Gate 3 Data 1 T                   | rue (non-inver | rted) bit      |                  |                  |             |  |  |  |

|                  | 1 = lcxd1T is | 1 = lcxd1T is gated into lcxg3    |                |                |                  |                  |             |  |  |  |

|                  | 0 = lcxd1T is | not gated into                    | lcxg3          |                |                  |                  |             |  |  |  |

| bit 0            | LCxG3D1N: (   | Gate 3 Data 1 I                   | Negated (inver | ted) bit       |                  |                  |             |  |  |  |

|                  |               | gated into lcxg                   | •              |                |                  |                  |             |  |  |  |

|                  | 0 = Icxd1N is | not gated into                    | lcxa3          |                |                  |                  |             |  |  |  |

## REGISTER 19-9: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

## 23.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 23.5 Effects of a Reset

A device Reset affects the following:

- · DAC is disabled.

- DAC output voltage is removed from the DAC10UT pin.

- The DAC1R<4:0> range select bits are cleared.

## 28.2 ZCD Logic Output

The ZCD module includes a Status bit, which can be read to determine whether the current source or sink is active. The ZCDxOUT bit of the ZCDxCON register is set when the current sink is active, and cleared when the current source is active. The ZCDxOUT bit is affected by the polarity bit.

## 28.3 ZCD Logic Polarity

The ZCDxPOL bit of the ZCDxCON register inverts the ZCDxOUT bit relative to the current source and sink output. When the ZCDxPOL bit is set, a ZCDxOUT high indicates that the current source is active, and a low output indicates that the current sink is active.

The ZCDxPOL bit affects the ZCD interrupts. See **Section 28.4 "ZCD Interrupts**".

### 28.4 ZCD Interrupts

An interrupt will be generated upon a change in the ZCD logic output when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in the ZCD for this purpose.

The ZCDIF bit of the PIR3 register will be set when either edge detector is triggered and its associated enable bit is set. The ZCDxINTP enables rising edge interrupts and the ZCDxINTN bit enables falling edge interrupts. Both are located in the ZCDxCON register.

To fully enable the interrupt, the following bits must be set:

- · ZCDIE bit of the PIE3 register

- ZCDxINTP bit of the ZCDxCON register (for a rising edge detection)

- ZCDxINTN bit of the ZCDxCON register (for a falling edge detection)

- PEIE and GIE bits of the INTCON register

Changing the ZCDxPOL bit will cause an interrupt, regardless of the level of the ZCDxEN bit.

The ZCDIF bit of the PIR3 register must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

### 28.5 Correcting for ZCPINV offset

The actual voltage at which the ZCD switches is the reference voltage at the non-inverting input of the ZCD op amp. For external voltage source waveforms, other than square waves, this voltage offset from zero causes the zero-cross event to occur either too early or too late. When the waveform is varying relative to Vss, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 28-2.

#### EQUATION 28-2: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{ZCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{VDD - ZCPINV}{VPEAK}\right)}{2\pi \bullet Freq}$$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to Vss. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the ZCPINV switching voltage. The pull-up or pull-down value can be determined with the equations shown in Equation 28-3 or Equation 28-4.

### EQUATION 28-3: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$R_{PULLUP} = \frac{R_{SERIES}(V_{PULLUP} - Z_{CPINV})}{2}$$

When External Signal is relative to VDD:

$$R_{PULLDOWN} = \frac{R_{SERIES}(ZCPINV)}{(VDD - ZCPINV)}$$

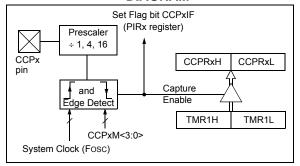

## 29.1 Capture Mode

The Capture mode function described in this section is available and identical for all CCP modules.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 29-1 shows a simplified diagram of the capture operation.

#### 29.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 29-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 29.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

### 29.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | (Fosc) should not be used in Capture    |  |  |  |  |  |  |

|       | mode. In order for Capture mode to      |  |  |  |  |  |  |

|       | recognize the trigger event on the CCPx |  |  |  |  |  |  |

|       | pin, Timer1 must be clocked from the    |  |  |  |  |  |  |

|       | instruction clock (Fosc/4) or from an   |  |  |  |  |  |  |

|       | external clock source.                  |  |  |  |  |  |  |

## 29.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 29-1 demonstrates the code to perform this function.

#### EXAMPLE 29-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point<br>;to CCPxCON                      |

|---------|-------------|-------------------------------------------------------------|

| CLRF    |             | ;Turn CCP module off                                        |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with<br>;the new prescaler                  |

| MOVWF   | CCPxCON     | ;move value and CCP ON<br>;Load CCPxCON with this<br>;value |

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 29-4).

#### 29.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 29-4.

#### EQUATION 29-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TABLE 29-1: | <b>EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (</b> | Fosc = 20 MHz) |

|-------------|--------------------------------------------------|----------------|

|             |                                                  | 1000 - 20 mmz  |

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 29-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

### 29.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 29.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 29.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

© 2013-2016 Microchip Technology Inc.

## 31.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 6.2.2.3 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 31.4.1** "**Auto-Baud Detect**"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

## 33.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                              |  |

|------------------|--------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                         |  |

| Operands:        | -32 ≤ k ≤ 31<br>n ∈ [ 0, 1]                                                                      |  |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                                  |  |

| Status Affected: | None                                                                                             |  |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair.    |  |

|                  | FSRn is limited to the range<br>0000h-FFFFh. Moving beyond these<br>bounds will cause the FSR to |  |

| ANDLW            | AND literal with W                                                                                              |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |  |

| Operands:        | $0 \leq k \leq 255$                                                                                             |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |  |

| Status Affected: | Z                                                                                                               |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |

| ADDLW            | Add literal and W                                                                                             |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |

| Operation:       | $(W) + k \to (W)$                                                                                             |  |

| Status Affected: | C, DC, Z                                                                                                      |  |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |  |

wrap-around.

| ANDWF            | AND W with f                                                                                                                                                    |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |

| Status Affected: | Z                                                                                                                                                               |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |

| ADDWF            | Add W and f                                                                                                                                                                     |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                      |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |  |

| Status Affected: | C, DC, Z                                                                                                                                                                        |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                              |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ASRF f {,d}                                                                                                                                                                                                        |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                                  |  |

| Operation:       | $(f<7>) \rightarrow dest<7>$<br>$(f<7:1>) \rightarrow dest<6:0>,$<br>$(f<0>) \rightarrow C,$                                                                                                                                        |  |

| Status Affected: | C, Z                                                                                                                                                                                                                                |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |  |

| ADDWFC | ADD W and CARRY bit to f |

|--------|--------------------------|

|--------|--------------------------|

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                            |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |  |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] RETFIE k                                                                                                                                                                                              |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |

| Cycles:          | 2                                                                                                                                                                                                               |  |  |

| Example:         | RETFIE                                                                                                                                                                                                          |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |  |  |

| RETURN           | Return from Subroutine                                                                                                                                |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] RETURN                                                                                                                                        |  |  |

| Operands:        | None                                                                                                                                                  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                  |  |  |

| Status Affected: | None                                                                                                                                                  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |  |  |

| RETLW            | Return with literal in W                                                                                                           | RLF              | Pototo Loft f through Corry                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                           |                  | Rotate Left f through Carry                                                                                                                                                       |

| Operands:        | $0 \le k \le 255$                                                                                                                  | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                          |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                       | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                |

| Status Affected: | None                                                                                                                               | Operation:       | See description below                                                                                                                                                             |

| Description:     | The W register is loaded with the 8-bit                                                                                            | Status Affected: | С                                                                                                                                                                                 |

| Description.     | literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is |

| Words:           | 1                                                                                                                                  |                  | stored back in register 'f'.                                                                                                                                                      |

| Cycles:          | 2                                                                                                                                  |                  | C Register f                                                                                                                                                                      |

| Example:         | CALL TABLE; W contains table                                                                                                       | Words:           | 1                                                                                                                                                                                 |

|                  | <pre>;offset value , W now has table value</pre>                                                                                   | Cycles:          | 1                                                                                                                                                                                 |

| TABLE            | •                                                                                                                                  | Example:         | RLF REG1,0                                                                                                                                                                        |

|                  | •                                                                                                                                  |                  | Before Instruction                                                                                                                                                                |

|                  | ADDWF PC ;W = offset<br>RETLW kl ;Begin table                                                                                      |                  | REG1 = 1110 0110                                                                                                                                                                  |

|                  | RETLW K1 /Begin table                                                                                                              |                  | C = 0                                                                                                                                                                             |

|                  | •                                                                                                                                  |                  | After Instruction                                                                                                                                                                 |

|                  | •                                                                                                                                  |                  | REG1 = 1110 0110                                                                                                                                                                  |

|                  | •                                                                                                                                  |                  | $W = 1100 \ 1100$<br>C = 1                                                                                                                                                        |

|                  | RETLW kn ; End of table                                                                                                            |                  | C = 1                                                                                                                                                                             |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                             |                  |                                                                                                                                                                                   |

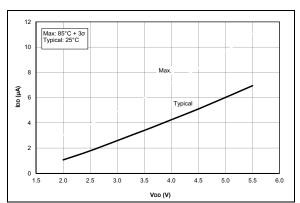

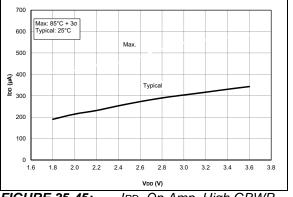

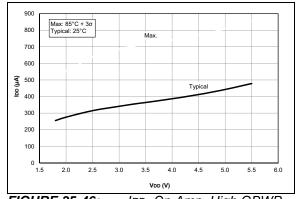

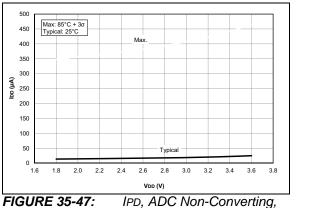

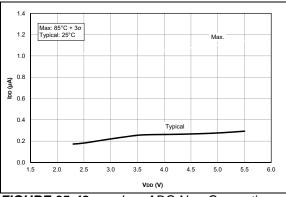

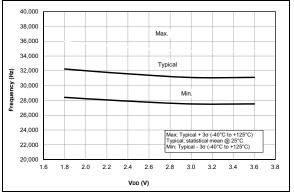

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1 µF, TA = 25°C.

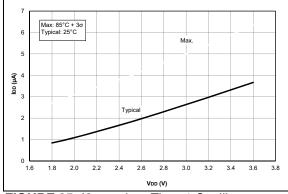

FIGURE 35-43: IPD, Timer1 Oscillator, Fosc = 32 kHz, PIC16LF1713/6 Only.

FIGURE 35-44: IPD, Timer1 Oscillator, Fosc = 32 kHz, PIC16F1713/6 Only.

FIGURE 35-45: IPD, Op Amp, High GBWP Mode (OPAxSP = 1), PIC16LF1713/6 Only.

FIGURE 35-46: IPD, Op Amp, High GBWP *Mode* (*OPAxSP* = 1), *PIC16F1713/6 Only*.

PIC16LF1713/6 Only.

FIGURE 35-48: IPD, ADC Non-Converting, PIC16F1713/6 Only.

(Au) aal

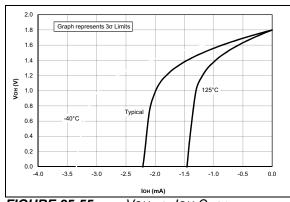

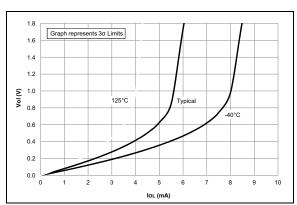

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

FIGURE 35-55: Voн vs. Ioн Over Temperature, VDD = 1.8V, PIC16LF1713/6 Only.

FIGURE 35-56: Vol. vs. Iol. Over Temperature, VDD = 1.8V, PIC16LF1713/6 Only.

FIGURE 35-57: LFINTOSC Frequency, PIC16LF1713/6 Only.

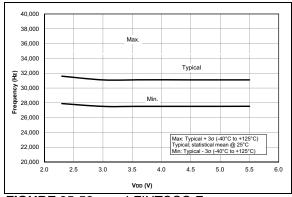

FIGURE 35-58: LFINTOSC Frequency, PIC16F1713/6 Only.

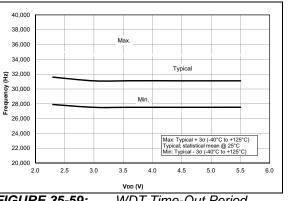

FIGURE 35-59: WDT Time-Out Period, PIC16F1713/6 Only.

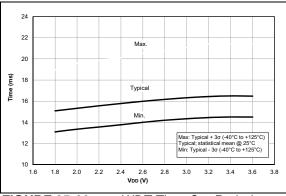

FIGURE 35-60: WDT Time-Out Period, PIC16LF1713/6 Only.