Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1716t-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-10.

| TABLE 3-2: CORE REGISTERS |

|---------------------------|

|---------------------------|

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| k0Ah or x8Ah | PCLATH |

| k0Bh or x8Bh | INTCON |

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| CLKIN <sup>(1)</sup><br>CLKOUT <sup>(2)</sup> | 1                                                           | Q1 Q2 Q3  Q4                                                        |                            | Tost(3)  |                 | Q1 Q2 Q3 Q4 | Q1  Q2  Q3  Q4<br> | Q1 Q2 Q3 Q4<br>~~~~~~<br>/ |

|-----------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------|----------------------------|----------|-----------------|-------------|--------------------|----------------------------|

| Interrupt flag                                | 1<br>                                                       | 1<br>F                                                              | /                          |          | Interrupt Laten | CV(4)       | · · ·              |                            |

|                                               | 1                                                           | I                                                                   | -                          | -        |                 |             | · •                |                            |

| GIE bit                                       |                                                             | 1                                                                   | Processor in               |          | 1               | <u> </u>    | 1 I                |                            |

| (INTCON reg.                                  | ),                                                          | ı                                                                   | Sleep                      |          | I.              | ı           | 1 1                |                            |

|                                               | ¦                                                           | ¦                                                                   |                            | — —      | !               | ¦_          | !— — —             |                            |

| Instruction Flow                              | ,1                                                          | 1                                                                   | 1                          |          | 1               | ı           |                    |                            |

| PC                                            | X PC                                                        | X PC + 1                                                            | X PC                       | + 2      | X PC + 2        | ( PC + 2    | X 0004h            | 0005h                      |

| Instruction {<br>Fetched                      | Inst(PC) = Sleep                                            | Inst(PC + 1)                                                        | 1<br>1<br>1                |          | Inst(PC + 2)    | 1<br>1<br>1 | Inst(0004h)        | Inst(0005h)                |

| Instruction {<br>Executed {                   | Inst(PC - 1)                                                | Sleep                                                               | 1<br>1<br>1                |          | Inst(PC + 1)    | Forced NOP  | Forced NOP         | Inst(0004h)                |

| 2:<br>3:                                      | "Two-Speed Cloc                                             | here for timing re<br>This delay does r<br><b>k Start-up Mode</b> " | ference.<br>not apply to E | C, RC ar |                 |             | -Speed Start-up (s |                            |

| Note 1:<br>2:<br>3:                           | External clock. Hig<br>CLKOUT is shown<br>Tost = 1024 Tosc. | here for timing re<br>This delay does r<br><b>k Start-up Mode</b> " | ference.<br>not apply to E | C, RC ar |                 |             |                    | ee Section (               |

#### FIGURE 8-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

DS40001726C-page 92

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELC  | ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | -       | -       | 131                 |

| INLVLC  | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 132                 |

| LATC    | LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 130                 |

| ODCONC  | ODC7    | ODC6    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    | 132                 |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 130                 |

| SLRCONC | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 132                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 130                 |

| WPUC    | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 131                 |

TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

# 14.3 Register Definitions: FVR Control

#### REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|-------------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAFVR<1:0> |         | ADFVI   | R<1:0>  |

| bit 7   | · · · · · ·           |                     |                      |             |         |         | bit 0   |

|         |                       |                     |                      |             |         |         |         |

| Legend:        |                                  |                                                                                                                                                        |                                                                                                                                                                  |

|----------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R = Readab     | ole bit                          | W = Writable bit                                                                                                                                       | U = Unimplemented bit, read as '0'                                                                                                                               |

| u = Bit is un  | ichanged                         | x = Bit is unknown                                                                                                                                     | -n/n = Value at POR and BOR/Value at all other Resets                                                                                                            |

| '1' = Bit is s | et                               | '0' = Bit is cleared                                                                                                                                   | q = Value depends on condition                                                                                                                                   |

| bit 7          | 1 = Fixed                        | ixed Voltage Reference Ena<br>Voltage Reference is enable<br>Voltage Reference is disable                                                              | ed                                                                                                                                                               |

| bit 6          | 1 = Fixed                        | Fixed Voltage Reference Re<br>Voltage Reference output is<br>Voltage Reference output is                                                               | ready for use                                                                                                                                                    |

| bit 5          | 1 = Tempe                        | nperature Indicator Enable b<br>erature Indicator is enabled<br>erature Indicator is disabled                                                          | <sub>)it</sub> (3)                                                                                                                                               |

| bit 4          | 1 = VOUT                         | emperature Indicator Range<br>= V⊡D - 4V⊤ (High Range)<br>= V⊡D - 2V⊤ (Low Range)                                                                      | Selection bit <sup>(3)</sup>                                                                                                                                     |

| bit 3-2        | 11 = Com<br>10 = Com<br>01 = Com | parator FVR Buffer Gain is 2                                                                                                                           | er Gain Selection bits<br>x, with output VCDAFVR = 4x VFVR <sup>(2)</sup><br>x, with output VCDAFVR = 2x VFVR <sup>(2)</sup><br>x, with output VCDAFVR = 1x VFVR |

| bit 1-0        | 11 = ADC<br>10 = ADC<br>01 = ADC | <b>:0&gt;:</b> ADC FVR Buffer Gain S<br>FVR Buffer Gain is 4x, with<br>FVR Buffer Gain is 2x, with<br>FVR Buffer Gain is 1x, with<br>FVR Buffer is off | output VADFVR = 4x VFVR <sup>(2)</sup><br>output VADFVR = 2x VFVR <sup>(2)</sup>                                                                                 |

|                |                                  | ays '1' on PIC16(L)F1713/6                                                                                                                             | •                                                                                                                                                                |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 15.0 "Temperature Indicator Module" for additional information.

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR<1:0> |       | ADFVF | ۲<1:0> | 151                 |

Legend: Shaded cells are not used with the Fixed Voltage Reference.

| R/W-0/0          | R/W-0/0                             | R/W-0/0                                 | R/W-0/0         | R/W-0/0         | R/W-0/0         | R/W-0/0         | R/W-0/0      |  |  |

|------------------|-------------------------------------|-----------------------------------------|-----------------|-----------------|-----------------|-----------------|--------------|--|--|

| CxINTP           | P CxINTN CxPCH<2:0> CxNCH<2:03      |                                         |                 |                 |                 |                 |              |  |  |

| bit 7            |                                     |                                         |                 |                 |                 |                 | bit C        |  |  |

|                  |                                     |                                         |                 |                 |                 |                 |              |  |  |

| Legend:          |                                     |                                         |                 |                 |                 |                 |              |  |  |

| R = Readable     | bit                                 | W = Writable                            | bit             | •               | nented bit, rea |                 |              |  |  |

| u = Bit is unch  | anged                               | x = Bit is unkr                         | iown            | -n/n = Value a  | at POR and BC   | OR/Value at all | other Resets |  |  |

| '1' = Bit is set |                                     | '0' = Bit is cle                        | ared            |                 |                 |                 |              |  |  |

| bit 7            | CxINTP: Co                          | mparator Interru                        | ipt on Positive | e Going Edge E  | nable bits      |                 |              |  |  |

|                  |                                     | F interrupt flag v<br>rupt flag will be |                 |                 |                 |                 |              |  |  |

| bit 6            |                                     | mparator Interru<br>F interrupt flag    |                 | • •             |                 | e CxOUT bit     |              |  |  |

|                  | 0 = No inter                        | rupt flag will be                       | set on a nega   | tive going edge | of the CxOUT    | bit             |              |  |  |

| bit 5-3          | CxPCH<2:0                           | Comparator I                            | Positive Input  | Channel Select  | bits            |                 |              |  |  |

|                  |                                     | connects to AG                          |                 |                 |                 |                 |              |  |  |

|                  |                                     | connects to FV                          |                 |                 |                 |                 |              |  |  |

|                  |                                     | connects to DA connects to DA           |                 |                 |                 |                 |              |  |  |

|                  |                                     | unconnected, i                          |                 |                 |                 |                 |              |  |  |

|                  |                                     | unconnected, i                          |                 |                 |                 |                 |              |  |  |

|                  |                                     | connects to Cx                          |                 |                 |                 |                 |              |  |  |

|                  | 000 = CxVP                          | connects to Cx                          | IN0+ pin        |                 |                 |                 |              |  |  |

| bit 2-0          | CxNCH<2:0                           | >: Comparator I                         | Negative Input  | t Channel Seleo | ct bits         |                 |              |  |  |

|                  | 111 = CxVN connects to AGND         |                                         |                 |                 |                 |                 |              |  |  |

|                  | 110 = CxVN connects to FVR Buffer 2 |                                         |                 |                 |                 |                 |              |  |  |

|                  |                                     | unconnected, i                          |                 |                 |                 |                 |              |  |  |

|                  |                                     | unconnected, i                          |                 |                 |                 |                 |              |  |  |

|                  |                                     | connects to Cx                          |                 |                 |                 |                 |              |  |  |

|                  |                                     | connects to Cx<br>connects to Cx        |                 |                 |                 |                 |              |  |  |

|                  | 001 - 0000                          |                                         |                 |                 |                 |                 |              |  |  |

## REGISTER 16-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

#### 17.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 17-4.

#### EQUATION 17-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2 + 1)]}{\log(2)}$  bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TABLE 17-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 M |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| <b>PWM Frequency</b>      | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 17-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 17.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 17.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 17.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

# 17.2 Register Definitions: PWM Control

| R/W-0/0          | U-0         | R-0/0             | R/W-0/0         | U-0             | U-0              | U-0              | U-0          |

|------------------|-------------|-------------------|-----------------|-----------------|------------------|------------------|--------------|

| PWMxEN           | _           | PWMxOUT           | PWMxPOL         | —               | —                | —                | —            |

| bit 7            |             | •                 |                 |                 |                  | •                | bit 0        |

|                  |             |                   |                 |                 |                  |                  |              |

| Legend:          |             |                   |                 |                 |                  |                  |              |

| R = Readable     | bit         | W = Writable      | bit             | U = Unimpler    | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged       | x = Bit is unkr   | nown            | -n/n = Value a  | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |             | '0' = Bit is clea | ared            |                 |                  |                  |              |

|                  |             |                   |                 |                 |                  |                  |              |

| bit 7            | PWMxEN: PV  | VM Module En      | able bit        |                 |                  |                  |              |

|                  | 1 = PWM mo  | dule is enable    | d               |                 |                  |                  |              |

|                  | 0 = PWM mo  | dule is disable   | d               |                 |                  |                  |              |

| bit 6            | Unimplemen  | ted: Read as '    | 0'              |                 |                  |                  |              |

| bit 5            | PWMxOUT: F  | WM module o       | utput level whe | en bit is read. |                  |                  |              |

| bit 4            | PWMxPOL: F  | PWMx Output F     | Polarity Select | bit             |                  |                  |              |

|                  |             | put is active lo  |                 |                 |                  |                  |              |

|                  | 0 = PWM out | tput is active hi | gh.             |                 |                  |                  |              |

| bit 3-0          | Unimplemen  | ted: Read as '    | 0'              |                 |                  |                  |              |

# REGISTER 17-1: PWMxCON: PWM CONTROL REGISTER

#### REGISTER 18-10: COGxDBR: COG RISING EVENT DEAD-BAND COUNT REGISTER

| U-0              | U-0   | R/W-x/u           | R/W-x/u    | R/W-x/u                                               | R/W-x/u          | R/W-x/u | R/W-x/u |  |  |  |  |  |

|------------------|-------|-------------------|------------|-------------------------------------------------------|------------------|---------|---------|--|--|--|--|--|

| _                | —     |                   | GxDBR<5:0> |                                                       |                  |         |         |  |  |  |  |  |

| bit 7            |       |                   |            |                                                       |                  |         | bit 0   |  |  |  |  |  |

|                  |       |                   |            |                                                       |                  |         |         |  |  |  |  |  |

| Legend:          |       |                   |            |                                                       |                  |         |         |  |  |  |  |  |

| R = Readable I   | bit   | W = Writable      | bit        | U = Unimplen                                          | nented bit, read | as '0'  |         |  |  |  |  |  |

| u = Bit is uncha | anged | x = Bit is unkr   | nown       | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |         |  |  |  |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | ared       | q = Value depends on condition                        |                  |         |         |  |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                  |

|---------|---------------------------------------------------------------------------------------------|

| bit 5-0 | GxDBR<5:0>: Rising Event Dead-band Count Value bits                                         |

|         | <u>GxRDBS = 0:</u>                                                                          |

|         | <ul> <li>Number of COGx clock periods to delay primary output after rising event</li> </ul> |

|         | <u>GxRDBS = 1:</u>                                                                          |

|         | - Number of dology obein element periode to dology primery output offer rising eyend        |

= Number of delay chain element periods to delay primary output after rising event

# REGISTER 18-11: COGxDBF: COG FALLING EVENT DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|-------|-----|---------|------------|---------|---------|---------|---------|--|--|--|

| —     | —   |         | GxDBF<5:0> |         |         |         |         |  |  |  |

| bit 7 |     |         |            |         |         |         | bit 0   |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-6 Unimplemented: Read as '0'

GxDBF<5:0>: Falling Event Dead-band Count Value bits

#### <u>GxFDBS = 0:</u>

bit 5-0

= Number of COGx clock periods to delay complementary output after falling event input

<u>GxFDBS = 1:</u>

= Number of delay chain element periods to delay complementary output after falling event input

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

## 30.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

## 30.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

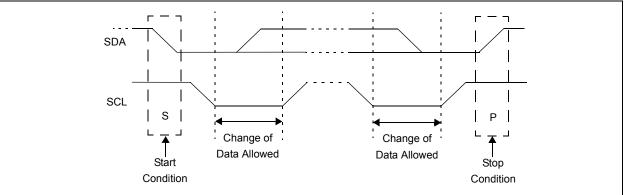

#### 30.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 30-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

#### 30.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

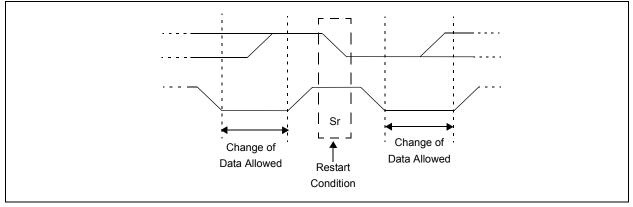

## 30.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 30-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

#### 30.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

## FIGURE 30-12: I<sup>2</sup>C START AND STOP CONDITIONS

# FIGURE 30-13: I<sup>2</sup>C RESTART CONDITION

#### 30.4.9 ACKNOWLEDGE SEQUENCE

The 9th SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{\text{ACK}}$  is placed in the ACKSTAT bit of the SSPCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the ACK value sent back to the transmitter. The ACKDT bit of the SSPCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPSTAT register or the SSPOV bit of the SSPCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

# 30.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of SSPCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 30.5.1 SLAVE MODE ADDRESSES

The SSPADD register (Register 30-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 30-5) affects the address matching process. See **Section 30.5.9** "**SSP Mask Register**" for more information.

## 30.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

#### 30.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPADD is updated to receive a high byte again. When SSPADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

# 30.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON1 register is set. The BOEN bit of the SSPCON3 register modifies this operation. For more information see Register 30-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPIF, must be cleared by software.

When the SEN bit of the SSPCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPCON1 register, except sometimes in 10-bit mode. See **Section 30.5.6.2 "10-bit Addressing Mode"** for more detail.

| Name      | Bit 7       | Bit 6           | Bit 5         | Bit 4         | Bit 3   | Bit 2       | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |

|-----------|-------------|-----------------|---------------|---------------|---------|-------------|--------|--------|-----------------------------|

| ANSELB    | -           |                 | ANSB5         | ANSB4         | ANSB3   | ANSB2       | ANSB1  | ANSB0  | 126                         |

| ANSELC    | ANSC7       | ANSC6           | ANSC5         | ANSC4         | ANSC3   | ANSC2       | _      | —      | 131                         |

| INTCON    | GIE         | PEIE            | TMR0IE        | INTE          | IOCIE   | TMR0IF      | INTF   | IOCIF  | 83                          |

| PIE1      | TMR1GIE     | ADIE            | RCIE          | TXIE          | SSP1IE  | CCP1IE      | TMR2IE | TMR1IE | 84                          |

| PIE2      | OSFIE       | C2IE            | C1IE          | _             | BCL1IE  | TMR6IE      | TMR4IE | CCP2IE | 85                          |

| PIR1      | TMR1GIF     | ADIF            | RCIF          | TXIF          | SSP1IF  | CCP1IF      | TMR2IF | TMR1IF | 87                          |

| PIR2      | OSFIF       | C2IF            | C1IF          | _             | BCL1IF  | TMR6IF      | TMR4IF | CCP2IF | 88                          |

| RxyPPS    | _           | _               | _             |               |         | RxyPPS<4:0> | •      |        | 137                         |

| SSPCLKPPS | _           | _               | _             |               | SS      | PCLKPPS<4   | :0>    |        | 136                         |

| SSPDATPPS | _           | _               | _             |               | SS      | PDATPPS<4   | :0>    |        | 136                         |

| SSP1ADD   |             |                 |               | ADD           | <7:0>   |             |        |        | 336                         |

| SSP1BUF   | Synchronous | s Serial Port F | Receive Buffe | r/Transmit Re | egister |             |        |        | 289*                        |

| SSP1CON1  | WCOL        | SSPOV           | SSPEN         | CKP           |         | SSPM        | <3:0>  |        | 333                         |

| SSP1CON2  | GCEN        | ACKSTAT         | ACKDT         | ACKEN         | RCEN    | PEN         | RSEN   | SEN    | 334                         |

| SSP1CON3  | ACKTIM      | PCIE            | SCIE          | BOEN          | SDAHT   | SBCDE       | AHEN   | DHEN   | 335                         |

| SSP1MSK   |             |                 |               | MSK           | <7:0>   |             |        |        | 336                         |

| SSP1STAT  | SMP         | CKE             | D/A           | P S R/W UA BF |         |             |        |        |                             |

| TRISB     | TRISB7      | TRISB6          | TRISB5        | TRISB4        | TRISB3  | TRISB2      | TRISB1 | TRISB0 | 125                         |

| TRISC     | TRISC7      | TRISC6          | TRISC5        | TRISC4        | TRISC3  | TRISC2      | TRISC1 | TRISC0 | 130                         |

# TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

\* Page provides register information.

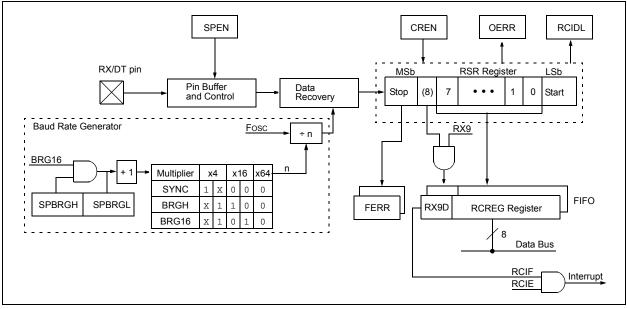

#### FIGURE 31-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 31-1, Register 31-2 and Register 31-3, respectively.

The RX and CK input pins are selected with the RXPPS and CKPPS registers, respectively. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

# 31.3 Register Definitions: EUSART Control

## REGISTER 31-1: TX1STA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-/0           | R/W-0/0                                                                                 | R/W-0/0                                               | R/W-0/0         | R/W-0/0         | R/W-0/0          | R-1/1            | R/W-0/0      |

|------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------|------------------|------------------|--------------|

| CSRC             | TX9                                                                                     | TXEN <sup>(1)</sup>                                   | SYNC            | SENDB           | BRGH             | TRMT             | TX9D         |

| bit 7            |                                                                                         |                                                       |                 |                 |                  |                  | bit (        |

|                  |                                                                                         |                                                       |                 |                 |                  |                  |              |

| Legend:          |                                                                                         |                                                       |                 |                 |                  |                  |              |

| R = Readable     |                                                                                         | W = Writable                                          |                 | -               | mented bit, read |                  |              |

| u = Bit is uncl  | •                                                                                       | x = Bit is unki                                       |                 | -n/n = Value    | at POR and BOF   | R/Value at all c | other Resets |

| '1' = Bit is set |                                                                                         | '0' = Bit is cle                                      | ared            |                 |                  |                  |              |

| bit 7            | <b>CSRC:</b> Clock<br><u>Asynchronou</u><br>Don't care<br><u>Synchronous</u>            |                                                       | bit             |                 |                  |                  |              |

|                  |                                                                                         | mode (clock ge<br>10de (clock fron                    |                 |                 | )                |                  |              |

| bit 6            | 1 = Selects                                                                             | ansmit Enable I<br>9-bit transmiss<br>8-bit transmiss | ion             |                 |                  |                  |              |

| bit 5            | <b>TXEN:</b> Trans<br>1 = Transmi<br>0 = Transmi                                        |                                                       | )               |                 |                  |                  |              |

| bit 4            | SYNC: EUS<br>1 = Synchro<br>0 = Asynchr                                                 |                                                       | ect bit         |                 |                  |                  |              |

| bit 3            | Asynchronou<br>1 = Send Sy                                                              | vnc Break on ne<br>eak transmissio                    | ext transmissio | n (cleared by ∣ | hardware upon o  | completion)      |              |

| bit 2            | BRGH: High<br>Asynchronou<br>1 = High spe<br>0 = Low spe<br>Synchronous<br>Unused in th | eed<br>eed<br><u>s mode:</u>                          | ect bit         |                 |                  |                  |              |

| bit 1            |                                                                                         | smit Shift Regist<br>pty                              | ter Status bit  |                 |                  |                  |              |

| bit 0            | TX9D: Ninth<br>Can be addr                                                              | bit of Transmit                                       | Data            |                 |                  |                  |              |

|        |                |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRC        | <b>616 =</b> 0 |                             |                |                    |                             |  |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc           | ; = 32.00  | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |                |                             | Fosc           | Fosc = 11.0592 MHz |                             |  |

|        | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | _              |            | _                           |                   |            | _                           | _                 | _              | _                           |                |                    | _                           |  |

| 1200   | _              | _          | —                           | 1221              | 1.73       | 255                         | 1200              | 0.00           | 239                         | 1200           | 0.00               | 143                         |  |

| 2400   | 2404           | 0.16       | 207                         | 2404              | 0.16       | 129                         | 2400              | 0.00           | 119                         | 2400           | 0.00               | 71                          |  |

| 9600   | 9615           | 0.16       | 51                          | 9470              | -1.36      | 32                          | 9600              | 0.00           | 29                          | 9600           | 0.00               | 17                          |  |

| 10417  | 10417          | 0.00       | 47                          | 10417             | 0.00       | 29                          | 10286             | -1.26          | 27                          | 10165          | -2.42              | 16                          |  |

| 19.2k  | 19.23k         | 0.16       | 25                          | 19.53k            | 1.73       | 15                          | 19.20k            | 0.00           | 14                          | 19.20k         | 0.00               | 8                           |  |

| 57.6k  | 55.55k         | -3.55      | 3                           | —                 | _          | _                           | 57.60k            | 0.00           | 7                           | 57.60k         | 0.00               | 2                           |  |

| 115.2k | —              | —          | —                           | _                 | —          | _                           | _                 | _              | _                           | —              | _                  | —                           |  |

#### TABLE 31-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                |            |                             |                  | SYNC       | <b>C =</b> 0, <b>BRG</b>    | l = 0, BRG        | <b>616 =</b> 0 |                             |                |                  |                             |  |

|--------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|----------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |                |                             | Fos            | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | _              | _          | _                           | 300              | 0.16       | 207                         | 300               | 0.00           | 191                         | 300            | 0.16             | 51                          |  |

| 1200   | 1202           | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00           | 47                          | 1202           | 0.16             | 12                          |  |

| 2400   | 2404           | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00           | 23                          | —              | _                | _                           |  |

| 9600   | 9615           | 0.16       | 12                          | —                | _          | _                           | 9600              | 0.00           | 5                           | —              | _                | _                           |  |

| 10417  | 10417          | 0.00       | 11                          | 10417            | 0.00       | 5                           | _                 | _              | _                           | _              | _                | _                           |  |

| 19.2k  | _              | _          | _                           | —                | _          | _                           | 19.20k            | 0.00           | 2                           | _              | _                | _                           |  |

| 57.6k  | —              | _          | —                           | —                | _          | —                           | 57.60k            | 0.00           | 0                           | —              | _                | —                           |  |

| 115.2k |                | _          | _                           | —                | _          | _                           | —                 | _              | _                           | —              | _                | —                           |  |

|        |                |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>G16 =</b> 0 |                             |                |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc           | = 32.00    | 0 MHz                       | Fosc           | = 20.00    | 0 MHz                       | Fosc           | : = 18.43      | 2 MHz                       | Fosc           | = 11.059   | 92 MHz                      |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —              | —          | _                           |                |            | _                           |                |                | _                           | _              | —          | _                           |

| 1200   | —              | —          | —                           | —              | _          | —                           | —              | —              | —                           | —              | —          | —                           |

| 2400   | —              | _          | _                           | _              | _          | _                           | _              | _              | _                           | —              | _          | _                           |

| 9600   | 9615           | 0.16       | 207                         | 9615           | 0.16       | 129                         | 9600           | 0.00           | 119                         | 9600           | 0.00       | 71                          |

| 10417  | 10417          | 0.00       | 191                         | 10417          | 0.00       | 119                         | 10378          | -0.37          | 110                         | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k         | 0.16       | 103                         | 19.23k         | 0.16       | 64                          | 19.20k         | 0.00           | 59                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 57.14k         | -0.79      | 34                          | 56.82k         | -1.36      | 21                          | 57.60k         | 0.00           | 19                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 117.64k        | 2.12       | 16                          | 113.64k        | -1.36      | 10                          | 115.2k         | 0.00           | 9                           | 115.2k         | 0.00       | 5                           |

|        |                |            |                             | SYNC = 0          | , BRGH     | = 1, BRG16                  | = 1 or SY         | NC = 1,    | BRG16 = 1                   |                    |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Foso           | = 32.00    | 0 MHz                       | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00       | 26666                       | 300.0             | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        |

| 1200   | 1200           | 0.00       | 6666                        | 1200              | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        |

| 2400   | 2400           | 0.01       | 3332                        | 2400              | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        |

| 9600   | 9604           | 0.04       | 832                         | 9597              | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         |

| 10417  | 10417          | 0.00       | 767                         | 10417             | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10433              | 0.16       | 264                         |

| 19.2k  | 19.18k         | -0.08      | 416                         | 19.23k            | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00       | 143                         |

| 57.6k  | 57.55k         | -0.08      | 138                         | 57.47k            | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00       | 47                          |

| 115.2k | 115.9k         | 0.64       | 68                          | 116.3k            | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00       | 23                          |

# TABLE 31-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                |            |                             | SYNC = 0       | , BRGH     | = 1, BRG16                  | = 1 or SY      | ′NC = 1,   | BRG16 = 1                   |                |            |                             |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686  | 4 MHz                       | Fos            | c = 1.000  | ) MHz                       |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00       | 6666                        | 300.0          | 0.01       | 3332                        | 300.0          | 0.00       | 3071                        | 300.1          | 0.04       | 832                         |

| 1200   | 1200           | -0.02      | 1666                        | 1200           | 0.04       | 832                         | 1200           | 0.00       | 767                         | 1202           | 0.16       | 207                         |

| 2400   | 2401           | 0.04       | 832                         | 2398           | 0.08       | 416                         | 2400           | 0.00       | 383                         | 2404           | 0.16       | 103                         |

| 9600   | 9615           | 0.16       | 207                         | 9615           | 0.16       | 103                         | 9600           | 0.00       | 95                          | 9615           | 0.16       | 25                          |

| 10417  | 10417          | 0          | 191                         | 10417          | 0.00       | 95                          | 10473          | 0.53       | 87                          | 10417          | 0.00       | 23                          |

| 19.2k  | 19.23k         | 0.16       | 103                         | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 47                          | 19.23k         | 0.16       | 12                          |

| 57.6k  | 57.14k         | -0.79      | 34                          | 58.82k         | 2.12       | 16                          | 57.60k         | 0.00       | 15                          | —              | _          | _                           |

| 115.2k | 117.6k         | 2.12       | 16                          | 111.1k         | -3.55      | 8                           | 115.2k         | 0.00       | 7                           | _              | _          | _                           |

| Name     | Bit 7   | Bit 6  | Bit 5  | Bit 4          | Bit 3         | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|----------|---------|--------|--------|----------------|---------------|------------|--------|--------|---------------------|

| ANSELB   | —       | —      | ANSB5  | ANSB4          | ANSB3         | ANSB2      | ANSB1  | ANSB0  | 126                 |

| ANSELC   | ANSC7   | ANSC6  | ANSC5  | ANSC4          | ANSC3         | ANSC2      |        | —      | 131                 |

| BAUD1CON | ABDOVF  | RCIDL  | _      | SCKP           | BRG16         | _          | WUE    | ABDEN  | 349                 |

| CKPPS    | —       |        | —      |                |               | CKPPS<4:0> |        |        | 136                 |

| INTCON   | GIE     | PEIE   | TMR0IE | INTE           | IOCIE         | TMR0IF     | INTF   | IOCIF  | 83                  |

| PIE1     | TMR1GIE | ADIE   | RCIE   | TXIE           | SSP1IE        | CCP1IE     | TMR2IE | TMR1IE | 84                  |

| PIR1     | TMR1GIF | ADIF   | RCIF   | TXIF           | SSP1IF        | CCP1IF     | TMR2IF | TMR1IF | 87                  |

| RC1STA   | SPEN    | RX9    | SREN   | CREN           | ADDEN         | FERR       | OERR   | RX9D   | 348                 |

| RxyPPS   | —       | _      | —      | RxyPPS<4:0> 13 |               |            |        | 137    |                     |

| TRISB    | TRISB7  | TRISB6 | TRISB5 | TRISB4         | TRISB3        | TRISB2     | TRISB1 | TRISB0 | 125                 |

| TRISC    | TRISC7  | TRISC6 | TRISC5 | TRISC4         | TRISC3        | TRISC2     | TRISC1 | TRISC0 | 130                 |

| TX1REG   |         |        | EUS    | ART Transm     | it Data Regis | ster       |        |        | 339*                |

| TX1STA   | CSRC    | TX9    | TXEN   | SYNC           | SENDB         | BRGH       | TRMT   | TX9D   | 347                 |

# TABLE 31-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave transmission.

\* Page provides register information.

| CALL             | Call Subroutine                                                                                                                                                                                                                         |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |  |  |  |  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                                        |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                    |  |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |  |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                                      |  |  |  |  |

| Operands:        | None                                                                                                                                                                                |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                              |  |  |  |  |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$<br>are set.                          |  |  |  |  |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |  |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |  |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |  |  |  |

| COMF             | Complement f                                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

| CLRF             | Clear f                                                               |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |  |

| DECF             | Decrement f                                                                                                                                       |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] DECF f,d                                                                                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |  |  |  |

| Status Affected: | Z                                                                                                                                                 |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W register. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |  |  |  |

# CLRWClear WSyntax:[label] CLRWOperands:NoneOperation: $00h \rightarrow (W)$ <br/> $1 \rightarrow Z$ Status Affected:ZDescription:W register is cleared. Zero bit (Z) is<br/>set.

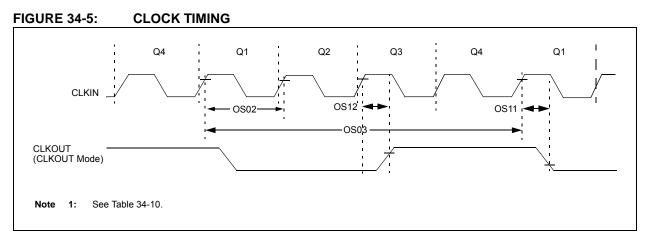

#### TABLE 34-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Param<br>No. | Sym.  | Characteristic                          | Min. | Тур†   | Max.   | Units | Conditions                |

|--------------|-------|-----------------------------------------|------|--------|--------|-------|---------------------------|

| OS01         | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | _      | 0.5    | MHz   | External Clock (ECL)      |

|              |       |                                         | DC   | —      | 4      | MHz   | External Clock (ECM)      |

|              |       |                                         | DC   | _      | 20     | MHz   | External Clock (ECH)      |

|              |       | Oscillator Frequency <sup>(1)</sup>     | _    | 32.768 | —      | kHz   | LP Oscillator             |

|              |       |                                         | 0.1  | _      | 4      | MHz   | XT Oscillator             |