Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1713-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-10.

| TABLE 3-2: CORE REGISTERS |

|---------------------------|

|---------------------------|

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| k0Ah or x8Ah | PCLATH |

| k0Bh or x8Bh | INTCON |

### TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                    | <u>E 3-11:</u>   | PECIAL        | FUNCTIO | IN REGIS | 51ER 501     |       | CONTINU     | <u>, 150)</u> | -         |                   |                                 |

|--------------------|------------------|---------------|---------|----------|--------------|-------|-------------|---------------|-----------|-------------------|---------------------------------|

| Addr               | Name             | Bit 7         | Bit 6   | Bit 5    | Bit 4        | Bit 3 | Bit 2       | Bit 1         | Bit 0     | Value on POR, BOR | Value on all<br>other<br>Resets |

| Bank               | (14-27           |               |         |          |              |       |             |               |           |                   |                                 |

| x0Ch/<br>x8Ch<br>  | _                | Unimplemented |         |          |              |       |             |               | _         | _                 |                                 |

| Bank               | 28               |               |         |          |              |       |             |               |           |                   |                                 |

| E0Ch               | 20               |               |         |          |              |       |             |               |           |                   |                                 |

| <br>E0Eh           | _                | Unimplemen    | ted     |          |              |       |             |               |           | —                 | —                               |

| E0Fh               | PPSLOCK          | —             | —       | _        | —            | —     | —           | _             | PPSLOCKED | 0                 | 0                               |

| E10h               | INTPPS           | —             | _       | -        |              |       | INTPPS<4:0  | >             |           | 0 1000            | u uuuu                          |

| E11h               | <b>T0CKIPPS</b>  | _             | _       | _        |              |       | T0CKIPPS<4: | )>            |           | 0 0100            | u uuuu                          |

| E12h               | T1CKIPPS         | _             | —       | —        |              | -     | T1CKIPPS<4: | )>            |           | 1 0000            | u uuuu                          |

| E13h               | T1GPPS           | _             | —       | —        |              |       | T1GPPS<4:0  | >             |           | 0 1101            | u uuuu                          |

| E14h               | CCP1PPS          | _             | _       | _        |              |       | CCP1PPS<4:  | )>            |           | 1 0010            | u uuuu                          |

| E15h               | CCP2PPS          | _             | —       | —        |              |       |             | 1 0001        | u uuuu    |                   |                                 |

| E16h               | _                | Unimplement   | ted     |          | CCP2PPS<4:0> |       |             |               |           | _                 | _                               |

| E17h               | COGINPPS         | —             | —       | —        |              | (     | COGINPPS<4  | 0>            |           | 0 1000            | u uuuu                          |

| E18h               | _                | Unimplement   | ted     |          | •            |       |             |               |           | _                 | _                               |

| E19h               |                  | Unimplement   | ted     |          |              |       |             |               |           | —                 | —                               |

| E1Ah<br>E1FH       | -                | Unimplemen    | ted     |          |              |       |             |               |           | —                 | _                               |

| E20h               | SSPCLKPPS        | _             | _       | _        |              | S     | SPCLKPPS<4  | :0>           |           | 1 0011            | u uuuu                          |

| E21h               | SSPDATPPS        | —             | —       |          |              | S     | SPDATPPS<4  | k:0>          |           | 1 0100            | u uuuu                          |

| E22h               | SSPSSPPS         | _             | —       | _        |              | 5     | SSPSSPPS<4  | 0>            |           | 0 0101            | u uuuu                          |

| E23h               |                  | Unimplemen    | ted     |          |              |       |             |               |           | _                 | _                               |

| E24h               | RXPPS            | —             | —       | _        | RXPPS<4:0>   |       |             |               |           | 1 0111            | u uuuu                          |

| E25h               | CKPPS            | -             | —       | —        |              |       |             | 1 0110        | u uuuu    |                   |                                 |

| E26h               |                  | Unimplement   | ted     |          |              |       |             |               |           | _                 | —                               |

| E27h               | —                | Unimplemen    | ted     |          | r            |       |             |               |           | —                 | —                               |

| E28h               | CLCIN0PPS        | —             | —       | —        |              | C     | LCIN0PPS<4  | :0>           |           | 0 0000            | u uuuu                          |

| E29h               | CLCIN1PPS        | -             | —       | —        |              | C     | LCIN1PPS<4  | :0>           |           | 0 0001            | u uuuu                          |

| E2Ah               | CLCIN2PPS        | —             | —       | —        |              | C     | LCIN2PPS<4  | :0>           |           | 0 1110            | u uuuu                          |

| E2Bh               | <b>CLCIN3PPS</b> | —             | —       | —        |              | C     | LCIN3PPS<4  | :0>           |           | 0 1111            | u uuuu                          |

| E2Ch<br>to<br>E6Fh | _                | Unimplemen    | ted     |          |              |       |             |               |           | _                 | —                               |

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16(L)F1713/6.

|                    |                                                                                                                                                                                                    | R/P-1                                                                                          | R/P-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/P-1                                  | R/P-1                                                  | R/P-1              | R/P-1        |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------|--------------------|--------------|

|                    |                                                                                                                                                                                                    | LVP <sup>(1)</sup>                                                                             | DEBUG <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LPBOR                                  | BORV <sup>(3)</sup>                                    | STVREN             | PLLEN        |

|                    |                                                                                                                                                                                                    | bit 13                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                        | _                  | bit 8        |

|                    |                                                                                                                                                                                                    |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                        |                    |              |

| R/P-1              | U-1                                                                                                                                                                                                | U-1                                                                                            | U-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-1                                    | R/P-1                                                  | R/P-1              | R/P-1        |

| ZCDDIS             | _                                                                                                                                                                                                  | _                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                      | PPS1WAY                                                | WRT                | <1:0>        |

| bit 7              |                                                                                                                                                                                                    |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | •                                                      | •                  | bit C        |

|                    |                                                                                                                                                                                                    |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                        |                    |              |

| Legend:            |                                                                                                                                                                                                    |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                        |                    |              |

| R = Readable       | bit                                                                                                                                                                                                | P = Programm                                                                                   | able bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U = Unimpleme                          | ented bit, read as                                     | ·'1'               |              |

| '0' = Bit is clea  | red                                                                                                                                                                                                | '1' = Bit is set                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -n = Value whe                         | n blank or after B                                     | ulk Erase          |              |

| bit 13             | 1 = Low-voltag                                                                                                                                                                                     | age Programmin<br>le programming o<br>ge on MCLR mus                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | gramming                               |                                                        |                    |              |

| bit 12             | 1 = In-Circuit D                                                                                                                                                                                   |                                                                                                | d, ICSPCLK and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        | eneral purpose I/<br>edicated to the de                |                    |              |

| bit 11             | 1 = Low-Power                                                                                                                                                                                      | Power BOR Enal<br>r Brown-out Res<br>r Brown-out Res                                           | et is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |                                                        |                    |              |

| bit 10             | <b>BORV:</b> Brown-out Reset Voltage Selection bit <sup>(3)</sup><br>1 = Brown-out Reset voltage (VBOR), low trip point selected.<br>0 = Brown-out Reset voltage (VBOR), high trip point selected. |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                        |                    |              |

| bit 9              | 1 = Stack Over                                                                                                                                                                                     | flow or Underflo                                                                               | erflow Reset Enal<br>w will cause a Re<br>w will not cause a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | set                                    |                                                        |                    |              |

| bit 8              | <b>PLLEN:</b> PLL E<br>1 = 4xPLL ena<br>0 = 4xPLL disa                                                                                                                                             | bled                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                        |                    |              |

| bit 7              | <b>ZCDDIS:</b> ZCD<br>1 = ZCD disabl<br>0 = ZCD alway                                                                                                                                              | led. ZCD can be                                                                                | enabled by settir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ng the ZCDSEN                          | bit of ZCDCON                                          |                    |              |

| bit 6-3            | Unimplemente                                                                                                                                                                                       |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                        |                    |              |

| bit 2              | -                                                                                                                                                                                                  |                                                                                                | Way Set Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit                                    |                                                        |                    |              |

|                    | future cha                                                                                                                                                                                         | anges to PPS reg                                                                               | isters are prever                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nted                                   | sequence is exec<br>ed an unlocking s                  |                    |              |

| bit 1-0            | WRT<1:0>: Fla<br><u>4 kW Flash me</u><br>11 = Write<br>10 = 000h<br>01 = 000h                                                                                                                      | ash Memory Self<br>e <u>mory</u><br>e protection off<br>n to 1FFh write p<br>n to 7FFh write p | -Write Protection<br>rotected, 200h to<br>rotected, 800h to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bits<br>FFFh may be m<br>FFFh may be m | odified by PMCO<br>odified by PMCO<br>iodified by PMCC | IN control         | ·            |

| <b>2:</b> Th<br>ar | ne <u>LVP bit</u> cannot<br>ne DEBUG bit in (<br>nd programmers.                                                                                                                                   | Configuration Wo                                                                               | ords is managed a construction of the construc | automatically by                       | device developm                                        | ent tools includin | ng debuggers |

### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

**3:** See VBOR parameter for specific trip point voltages.

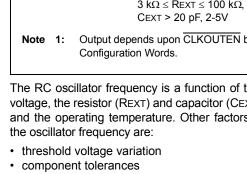

#### 6.2.1.6 External RC Mode

The external Resistor-Capacitor (EXTRC) mode supports the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required.

The RC circuit connects to OSC1. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

Figure 6-6 shows the external RC mode connections.

Vdd PIC<sup>®</sup> MCU REXT OSC1/CLKIN Internal Clock CEXT Vss OSC2/CLKOUT Fosc/4 or I/O(1) Recommended values: 10 k $\Omega \le REXT \le 100 \text{ k}\Omega$ , <3V  $3 \text{ k}\Omega \leq \text{Rext} \leq 100 \text{ k}\Omega, 3-5 \text{V}$ CEXT > 20 pF, 2-5V Output depends upon CLKOUTEN bit of the Note 1: Configuration Words.

FIGURE 6-6: EXTERNAL RC MODES

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting

· packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 6.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section 6.3 "Clock Switching" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 6-3).

- The **MFINTOSC** (Medium Frequency Internal 2. Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 6-3).

- The LFINTOSC (Low-Frequency Internal 3. Oscillator) is uncalibrated and operates at 31 kHz.

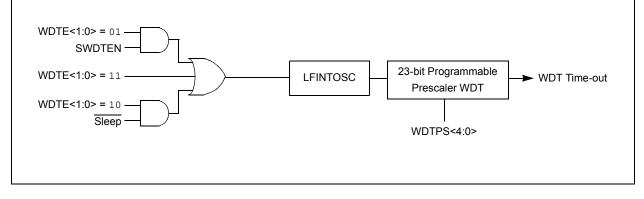

# 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

#### FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

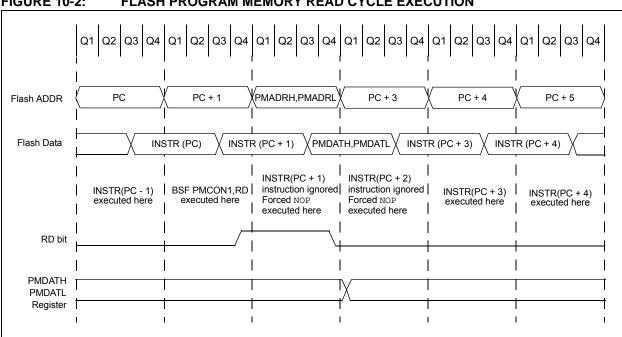

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

```

- \* memory at the memory address:

- PROG\_ADDR\_HI : PROG\_ADDR\_LO \* data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL | PMADRL       | ; | Select Bank for PMCON registers   |

|---------|--------------|---|-----------------------------------|

| MOVLW   | PROG_ADDR_LO | ; |                                   |

| MOVWF   | PMADRL       | ; | Store LSB of address              |

| MOVLW   | PROG ADDR HI | ; |                                   |

| MOVWF   | PMADRH       | ; | Store MSB of address              |

|         |              | - |                                   |

| BCF     | PMCON1,CFGS  | ; | Do not select Configuration Space |

|         | ,            |   | 5 1                               |

| BSF     | PMCON1,RD    | ; | Initiate read                     |

| NOP     |              | ; | Ignored (Figure 10-1)             |

| NOP     |              | ; | Ignored (Figure 10-1)             |

|         |              |   |                                   |

| MOVF    | PMDATL,W     | ; | Get LSB of word                   |

| MOVWF   | PROG DATA LO | ; | Store in user location            |

| MOTITE  |              |   | det MCD of and                    |

| MOVF    | PMDATH,W     | ; | Get MSB of word                   |

| MOVWF   | PROG_DATA_HI | ; | Store in user location            |

|         | —            |   |                                   |

|         |              |   |                                   |

#### **FIGURE 10-2:** FLASH PROGRAM MEMORY READ CYCLE EXECUTION

## 11.3 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

### 11.3.1 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

### 11.3.2 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

### 11.3.3 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

### 11.3.4 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 11.3.5 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 11.3.6 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information. Analog input functions, such as ADC and Op Amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

### 19.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.