Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1713-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"** for more information.

# 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 3.6 "Stack"** for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.7 "Indirect Addressing"** for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 33.0 "Instruction Set Summary"** for more details.

| 20Dh<br>20Eh<br>20Fh<br>210h<br>211h<br>212h<br>212h<br>213h<br>214h | 4<br>WPUA<br>WPUB<br>WPUC<br>           | WPUA7<br>WPUB7<br>WPUC7<br>Unimplement<br>—<br>Synchronous | —                                    | WPUA5<br>WPUB5<br>WPUC5 | WPUA4<br>WPUB4<br>WPUC4 | WPUA3<br>WPUB3 | WPUA2   | WPUA1  | WPUA0   | 1111 1111 | 11 1111   |

|----------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|--------------------------------------|-------------------------|-------------------------|----------------|---------|--------|---------|-----------|-----------|

| 20Dh<br>20Eh<br>20Fh<br>210h<br>211h<br>212h<br>212h<br>213h<br>214h | WPUB<br>WPUC<br>                        | WPUB7<br>WPUC7<br>Unimplement                              | WPUB6<br>WPUC6<br>ted                | WPUB5                   | WPUB4                   |                |         | WPUA1  | WPUA0   | 1111 1111 | 11 1111   |

| 20Eh<br>20Fh<br>210h<br>211h<br>212h<br>212h<br>213h<br>214h         | WPUC<br>—<br>WPUE<br>SSP1BUF<br>SSP1ADD | WPUC7<br>Unimplement                                       | WPUC6<br>ted                         |                         |                         | WPUB3          |         |        |         |           |           |

| 20Fh 210h 211h 212h 213h 213h 214h 214h 214h 214h 214h 214h 214h 214 |                                         | Unimplement                                                | ted —                                | WPUC5                   | WPUC4                   |                | WPUB2   | WPUB1  | WPUB0   | 1111 1111 | 1111      |

| 210h<br>211h<br>212h<br>213h<br>213h                                 | SSP1BUF<br>SSP1ADD                      |                                                            | —                                    |                         |                         | WPUC3          | WPUC2   | WPUC1  | WPUC0   | 1111 1111 | 1111 1111 |

| 211h<br>212h<br>213h<br>214h                                         | SSP1BUF<br>SSP1ADD                      |                                                            | —<br>Serial Port Re                  |                         |                         |                |         |        |         | —         | —         |

| 212h<br>213h<br>214h                                                 | SSP1ADD                                 | Synchronous                                                | Serial Port Re                       | _                       |                         | WPUE3          | _       | —      |         | 1         | 1         |

| 213h<br>214h                                                         |                                         |                                                            |                                      | eceive Buffer/1         | ransmit Regis           | ster           |         |        |         | XXXX XXXX | uuuu uuuu |

| 214h                                                                 | SSD1MSK                                 |                                                            |                                      |                         | ADD                     | )<7:0>         |         |        |         | XXXX XXXX | 0000 0000 |

|                                                                      |                                         |                                                            |                                      |                         | MSK                     | <<7:0>         |         |        |         | XXXX XXXX | 1111 1111 |

| 215h                                                                 | SSP1STAT                                | SMP                                                        | CKE                                  | D/A                     | Р                       | S              | R/W     | UA     | BF      | 0000 0000 | 0000 0000 |

| 21011                                                                | SSP1CON1                                | WCOL                                                       | SSPOV                                | SSPEN                   | CKP                     |                | SSPN    | /<3:0> |         | 0000 0000 | 0000 0000 |

| 216h                                                                 | SSP1CON2                                | GCEN                                                       | ACKSTAT                              | ACKDT                   | ACKEN                   | RCEN           | PEN     | RSEN   | SEN     | 0000 0000 | 0000 0000 |

| 217h                                                                 | SSP1CON3                                | ACKTIM                                                     | PCIE                                 | SCIE                    | BOEN                    | SDAHT          | SBCDE   | AHEN   | DHEN    | 0000 0000 | 0000 0000 |

| 218h                                                                 | _                                       | Unimplement                                                | ted                                  |                         |                         |                | I       |        |         | _         | _         |

| 21Fh                                                                 | _                                       |                                                            |                                      |                         |                         |                |         |        |         |           |           |

| Bank                                                                 |                                         | 0047                                                       | 0540                                 | 00.45                   | 0.5.4.4                 | 0040           | 0040    | 0044   | 0540    |           |           |

|                                                                      | ODCONA                                  | ODA7                                                       | ODA6                                 | ODA5                    | ODA4                    | ODA3           | ODA2    | ODA1   | ODA0    | 0000 0000 | 00 -000   |

|                                                                      | ODCONB                                  | ODB7                                                       | ODB6                                 | ODB5                    | ODB4                    | ODB3           | ODB2    | ODB1   | ODB0    | 0000 000- | 0000      |

| -                                                                    | ODCONC                                  | ODC7                                                       | ODC6                                 | ODC5                    | ODC4                    | ODC3           | ODC2    | ODC1   | ODC0    | 0000 0000 | 0000 0000 |

| 28Fh                                                                 |                                         | Unimplemented                                              |                                      |                         |                         |                |         |        |         | —         |           |

| 290h                                                                 |                                         |                                                            | Unimplemented                        |                         |                         |                |         |        |         | —         |           |

|                                                                      | CCPR1L                                  |                                                            | Capture/Compare/PWM Register 1 (LSB) |                         |                         |                |         |        |         | uuuu uuuu |           |

|                                                                      | CCPR1H                                  | Capture/Com                                                | npare/PWM Re                         | <b>.</b> .              | ,                       |                |         |        |         | XXXX XXXX | uuuu uuuu |

|                                                                      | CCP1CON                                 | _                                                          |                                      | DC1B                    | <1:0>                   |                | CCP1    | M<3:0> |         | 00 0000   | 00 0000   |

| 294h<br>                                                             | _                                       | Unimplement                                                | Unimplemented —                      |                         |                         |                |         |        |         | -         |           |

| 298h                                                                 | CCPR2L                                  | Capture/Com                                                | npare/PWM Re                         | egister 2 (LSB)         | )                       |                |         |        |         | XXXX XXXX | uuuu uuuu |

| 299h                                                                 | CCPR2H                                  | Capture/Com                                                | npare/PWM Re                         | egister 2 (MSB          | 5)                      |                |         |        |         | XXXX XXXX | uuuu uuuu |

| 29Ah                                                                 | CCP2CON                                 | _                                                          | _                                    | DC2B                    | <1:0>                   |                | CCP2    | M<3:0> |         | 00 0000   | 00 0000   |

| 29Bh                                                                 |                                         | l la incela en ant                                         | ka d                                 |                         |                         |                |         |        |         |           |           |

| 29Dh                                                                 | _                                       | Unimplement                                                | ted                                  |                         |                         |                |         |        |         | _         | _         |

| 29Eh                                                                 | CCPTMRS                                 | P4TSE                                                      | L<1:0>                               | P3TSE                   | L<1:0>                  | C2TSE          | :L<1:0> | C1TSE  | EL<1:0> | 0000 0000 | 0000 0000 |

| 29Fh                                                                 | _                                       | Unimplement                                                | ted                                  |                         |                         |                |         |        |         | _         | _         |

| Bank                                                                 | 6                                       | •                                                          |                                      |                         |                         |                |         |        |         | •         |           |

| 30Ch                                                                 | SLRCONA                                 | SLRA7                                                      | SLRA6                                | SLRA5                   | SLRA4                   | SLRA3          | SLRA2   | SLRA1  | SLRA0   | 1111 1111 | 00 -000   |

| 30Dh                                                                 | SLRCONB                                 | SLRB7                                                      | SLRB6                                | SLRB5                   | SLRB4                   | SLRB3          | SLRB2   | SLRB1  | SLRB0   | 1111 1111 | 0000      |

| 30Eh                                                                 | SLRCONC                                 | SLRC7                                                      | SLRC6                                | SLRC5                   | SLRC4                   | SLRC3          | SLRC2   | SLRC1  | SLRC0   | 1111 1111 | 0000 0000 |

| 30Fh<br>                                                             | _                                       | Unimplement                                                | ted                                  |                         |                         |                |         |        |         | _         | _         |

TABLE 3-11: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.Shaded locations are unimplemented, read as '0'.

Note 1: Unimplemented, read as '1'.

2: Unimplemented on PIC16(L)F1713/6.

# 5.3 Register Definitions: BOR Control

# REGISTER 5-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u     | R/W-0/u              | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-------------|----------------------|-----|-----|-----|-----|-----|--------|

| SBOREN      | BORFS <sup>(1)</sup> | —   | —   | —   | —   | —   | BORRDY |

| bit 7 bit 0 |                      |     |     |     |     |     |        |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit<br><u>If BOREN &lt;1:0&gt; in Configuration Words ≠ 01</u> :<br>SBOREN is read/write, but has no effect on the BOR.<br><u>If BOREN &lt;1:0&gt; in Configuration Words = 01</u> :<br>1 = BOR Enabled<br>0 = BOR Disabled                                                                                                                                                                                                            |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <ul> <li>BORFS: Brown-out Reset Fast Start bit<sup>(1)</sup></li> <li><u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u></li> <li>BORFS is Read/Write, but has no effect.</li> <li><u>If BOREN&lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</u></li> <li>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)</li> <li>0 = Band gap operates normally, and may turn off</li> </ul> |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 0   | <b>BORRDY:</b> Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                                                                            |

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

| R-1/q                       | R-0/q                                                                                                                                                                                              | R-q/q                                                                         | R-0/q          | R-0/q           | R-q/q                             | R-0/0             | R-0/q        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------|-----------------|-----------------------------------|-------------------|--------------|

| SOSCR                       | PLLR                                                                                                                                                                                               | OSTS                                                                          | HFIOFR         | HFIOFL          | MFIOFR                            | LFIOFR            | HFIOFS       |

| bit 7                       |                                                                                                                                                                                                    |                                                                               |                |                 |                                   |                   | bit          |

|                             |                                                                                                                                                                                                    |                                                                               |                |                 |                                   |                   |              |

| Legend:                     |                                                                                                                                                                                                    | $\lambda (-) \lambda (-) + c + c + c$                                         | L:4            |                 | nonted bit rece                   |                   |              |

| R = Readab<br>u = Bit is un |                                                                                                                                                                                                    | W = Writable<br>x = Bit is unki                                               |                |                 | nented bit, reac<br>at POR and BO |                   | othor Posote |

| '1' = Bit is s              | C C                                                                                                                                                                                                | '0' = Bit is cle                                                              |                | g = Condition   |                                   | rv value at all v |              |

| 1 - DIL 15 5                | ei                                                                                                                                                                                                 |                                                                               | areu           |                 | lai                               |                   |              |

| bit 7                       | If T1OSCEN<br>1 = Second                                                                                                                                                                           | condary Oscilla<br><u>I = 1</u> :<br>dary oscillator is<br>dary oscillator is | ready          |                 |                                   |                   |              |

|                             | If T1OSCEN                                                                                                                                                                                         | -                                                                             | -              | ady             |                                   |                   |              |

| bit 6                       | PLLR 4x PLL Ready bit<br>1 = 4x PLL is ready<br>0 = 4x PLL is not ready                                                                                                                            |                                                                               |                |                 |                                   |                   |              |

| bit 5                       | 1 = Runnin                                                                                                                                                                                         | llator Start-up Ti<br>ig from the clock<br>ig from an interr                  | defined by the |                 |                                   | guration Word     | S            |

| bit 4                       | HFIOFR: High-Frequency Internal Oscillator Ready bit<br>1 = HFINTOSC is ready<br>0 = HFINTOSC is not ready                                                                                         |                                                                               |                |                 |                                   |                   |              |

| bit 3                       | <b>HFIOFL:</b> High-Frequency Internal Oscillator Locked bit<br>1 = HFINTOSC is at least 2% accurate<br>0 = HFINTOSC is not 2% accurate                                                            |                                                                               |                |                 |                                   |                   |              |

| bit 2                       | 1 = MFINTO                                                                                                                                                                                         | edium Frequend<br>DSC is ready<br>DSC is not ready                            | -              | illator Ready b | it                                |                   |              |

| bit 1                       | LFIOFR: Low-Frequency Internal Oscillator Ready bit<br>1 = LFINTOSC is ready<br>0 = LFINTOSC is not ready                                                                                          |                                                                               |                |                 |                                   |                   |              |

| bit 0                       | <ul> <li>HINTOSC is not ready</li> <li>HFIOFS: High-Frequency Internal Oscillator Stable bit</li> <li>1 = HFINTOSC is at least 0.5% accurate</li> <li>0 = HFINTOSC is not 0.5% accurate</li> </ul> |                                                                               |                |                 |                                   |                   |              |

# REGISTER 6-2: OSCSTAT: OSCILLATOR STATUS REGISTER

# 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See Table 34-8: Oscillator Parameters for the LFINTOSC specification.

# 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

## 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 10        |        | Awake          | Active      |

| 10        | х      | Sleep          | Disabled    |

| 0.1       | 1      | V              | Active      |

| 01        | 0      | Х              | Disabled    |

| 00        | Х      | Х              | Disabled    |

#### TABLE 9-1: WDT OPERATING MODES

# 9.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

# 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- Device wakes up from Sleep

- Oscillator fail

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 9-2 for more information.

# 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 6.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See STATUS Register (Register 3-1) for more information.

# 11.3 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

# 11.3.1 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

# 11.3.2 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

# 11.3.3 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

# 11.3.4 INPUT THRESHOLD CONTROL

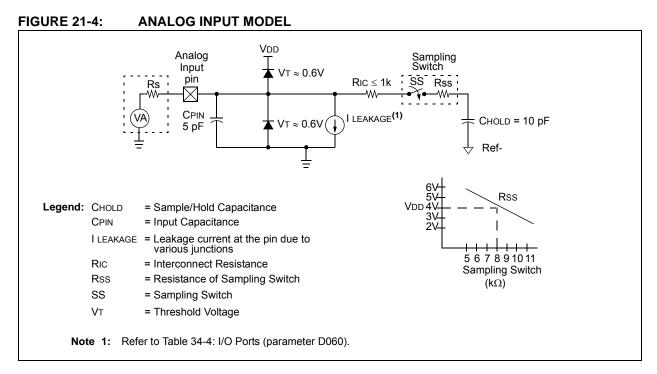

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

# 11.3.5 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

## 11.3.6 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information. Analog input functions, such as ADC and Op Amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

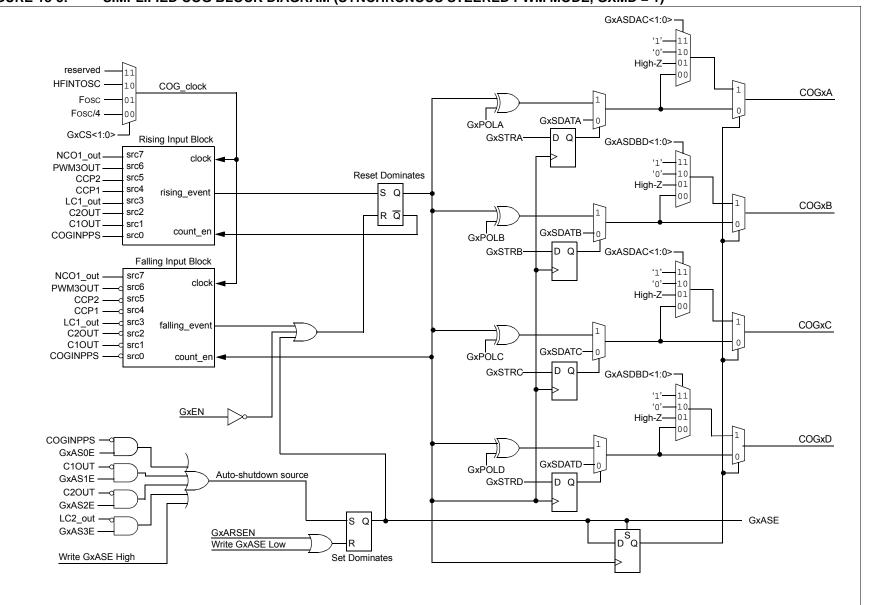

# FIGURE 18-3: SIMPLIFIED COG BLOCK DIAGRAM (SYNCHRONOUS STEERED PWM MODE, GXMD = 1)

DS40001726C-page 174

C16(L)F1713/6

| R/W-x/u          | R/W-x/u                                                              | R/W-x/u                            | R/W-x/u        | R/W-x/u              | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|----------------------------------------------------------------------|------------------------------------|----------------|----------------------|------------------|------------------|-------------|

| LCxG1D4T         | LCxG1D4N                                                             | LCxG1D3T                           | LCxG1D3N       | LCxG1D2T             | LCxG1D2N         | LCxG1D1T         | LCxG1D1N    |

| bit 7            |                                                                      |                                    |                |                      |                  |                  | bit 0       |

|                  |                                                                      |                                    |                |                      |                  |                  |             |

| Legend:          |                                                                      |                                    |                |                      |                  |                  |             |

| R = Readable b   | bit                                                                  | W = Writable                       | bit            | U = Unimpler         | nented bit, read | as '0'           |             |

| u = Bit is uncha | inged                                                                | x = Bit is unkn                    | iown           | -n/n = Value a       | at POR and BOI   | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                                      | '0' = Bit is clea                  | ared           |                      |                  |                  |             |

|                  |                                                                      |                                    |                |                      |                  |                  |             |

| bit 7            |                                                                      | Gate 1 Data 4 T                    | ,              | ted) bit             |                  |                  |             |

|                  |                                                                      | gated into lcxg<br>not gated into  |                |                      |                  |                  |             |

| bit 6            |                                                                      | Gate 1 Data 4 1                    | •              | tod) bit             |                  |                  |             |

| bit 0            |                                                                      | gated into lcxc                    | •              | ted) bit             |                  |                  |             |

|                  |                                                                      | not gated into                     |                |                      |                  |                  |             |

| bit 5            | LCxG1D3T: G                                                          | Gate 1 Data 3 T                    | rue (non-inver | ted) bit             |                  |                  |             |

|                  | 1 = Icxd3T is                                                        | gated into lcxg                    | 1              |                      |                  |                  |             |

|                  | 0 = Icxd3T is                                                        | not gated into                     | lcxg1          |                      |                  |                  |             |

| bit 4            |                                                                      | Gate 1 Data 3 M                    | •              | ted) bit             |                  |                  |             |

|                  |                                                                      | gated into loxo                    |                |                      |                  |                  |             |

| <b>h</b> it 0    |                                                                      | not gated into                     | •              | ted) bit             |                  |                  |             |

| bit 3            |                                                                      | Bate 1 Data 2 T<br>gated into lcxg | ,              | ted) bit             |                  |                  |             |

|                  |                                                                      | not gated into leve                |                |                      |                  |                  |             |

| bit 2            |                                                                      | Gate 1 Data 2 M                    | •              | ted) bit             |                  |                  |             |

|                  |                                                                      | gated into lcxg                    | •              | ,                    |                  |                  |             |

|                  | 0 = Icxd2N is                                                        | not gated into                     | lcxg1          |                      |                  |                  |             |

| bit 1            | LCxG1D1T: 0                                                          | Gate 1 Data 1 T                    | rue (non-inver | ted) bit             |                  |                  |             |

|                  | 1 = lcxd1T is gated into lcxg1                                       |                                    |                |                      |                  |                  |             |

| 1.1.0            |                                                                      | not gated into                     | •              | () 1. <sup>4</sup> ( |                  |                  |             |

| bit 0            |                                                                      | Gate 1 Data 1 N                    |                | ted) bit             |                  |                  |             |

|                  | 1 = Icxd1N is gated into Icxg1<br>0 = Icxd1N is not gated into Icxg1 |                                    |                |                      |                  |                  |             |

|                  |                                                                      | not gated into                     | 10/91          |                      |                  |                  |             |

# REGISTER 19-7: CLCxGLS0: GATE 1 LOGIC SELECT REGISTER

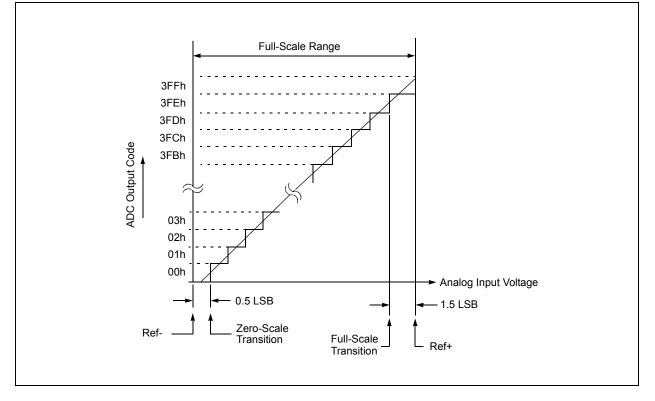

# 21.3 Register Definitions: ADC Control

# REGISTER 21-1: ADCON0: ADC CONTROL REGISTER 0

| U-0          | R/W-0/0                  | R/W-0/0                           | R/W-0/0             | R/W-0/0            | R/W-0/0         | R/W-0/0           | R/W-0/0      |

|--------------|--------------------------|-----------------------------------|---------------------|--------------------|-----------------|-------------------|--------------|

|              |                          |                                   | CHS<4:0>            |                    |                 | GO/DONE           | ADON         |

| bit 7        |                          |                                   |                     |                    |                 |                   | bit 0        |

|              |                          |                                   |                     |                    |                 |                   |              |

| Legend:      |                          |                                   |                     |                    |                 |                   |              |

| R = Reada    | able bit                 | W = Writable                      | bit                 | U = Unimpler       | nented bit, rea | d as '0'          |              |

| u = Bit is u | inchanged                | x = Bit is unkr                   | nown                | -n/n = Value a     | at POR and BC   | OR/Value at all o | other Resets |

| '1' = Bit is | set                      | '0' = Bit is cle                  | ared                |                    |                 |                   |              |

| bit 7        | Unimplomo                | ntadi Daad aa '                   | 0'                  |                    |                 |                   |              |

| bit 6-2      | -                        | nted: Read as '<br>Analog Channel |                     |                    |                 |                   |              |

| DIL 0-2      |                          | R (Fixed Voltage                  |                     | Ruffor 1 Output    | (2)             |                   |              |

|              |                          | C1 output <sup>(1)</sup>          | e Relefence) i      |                    |                 |                   |              |

|              | 11101 <b>= Te</b> r      | nperature Indica                  | ator <sup>(3)</sup> |                    |                 |                   |              |

|              | 11100 <b>= DA</b>        | C2_output <sup>(4)</sup>          |                     |                    |                 |                   |              |

|              | 11011 <b>= Re</b> s      | served. No char                   | nnel connecte       | d.                 |                 |                   |              |

|              | •                        |                                   |                     |                    |                 |                   |              |

|              | •                        |                                   |                     |                    |                 |                   |              |

|              | 10011 <b>= AN</b>        | 19                                |                     |                    |                 |                   |              |

|              | 10010 <b>= AN</b>        | 18                                |                     |                    |                 |                   |              |

|              | 10001 = AN               |                                   |                     |                    |                 |                   |              |

|              | 10000 = AN               |                                   |                     |                    |                 |                   |              |

|              | 01111 = AN<br>01110 = AN | -                                 |                     |                    |                 |                   |              |

|              | 01110 = AN<br>01101 = AN |                                   |                     |                    |                 |                   |              |

|              | 01100 = AN               |                                   |                     |                    |                 |                   |              |

|              | 01011 <b>= AN</b>        | 11                                |                     |                    |                 |                   |              |

|              | 01010 = AN               |                                   |                     |                    |                 |                   |              |

|              | 01001 = AN               |                                   |                     |                    |                 |                   |              |

|              | 01000 = AN               | ið<br>served. No chai             | nnol connocto       | d                  |                 |                   |              |

|              |                          | served. No cha                    |                     |                    |                 |                   |              |

|              |                          | served. No cha                    |                     |                    |                 |                   |              |

|              | 00100 = AN               | 4                                 |                     |                    |                 |                   |              |

|              | 00011 = AN               |                                   |                     |                    |                 |                   |              |

|              | 00010 = AN<br>00001 = AN |                                   |                     |                    |                 |                   |              |

|              | 00001 = AN               |                                   |                     |                    |                 |                   |              |

| bit 1        |                          | ADC Conversion                    | n Status bit        |                    |                 |                   |              |

|              |                          | version cycle ir                  |                     | tting this bit sta | rts an ADC cou  | version cycle     |              |

|              |                          | s automatically                   |                     |                    |                 |                   | eted.        |

|              |                          | version comple                    | -                   |                    |                 |                   |              |

| bit 0        | ADON: ADC                | Enable bit                        |                     |                    |                 |                   |              |

|              | 1 = ADC is e             |                                   |                     |                    |                 |                   |              |

|              | 0 = ADC is d             | lisabled and cor                  | nsumes no op        | erating current    |                 |                   |              |

|              | See Section 23.0         | -                                 | -                   | -                  | -               | more information  | on.          |

|              | See Section 14.0         | -                                 |                     |                    |                 |                   |              |

| 3:           | See Section 15.0         | =                                 |                     |                    |                 |                   |              |

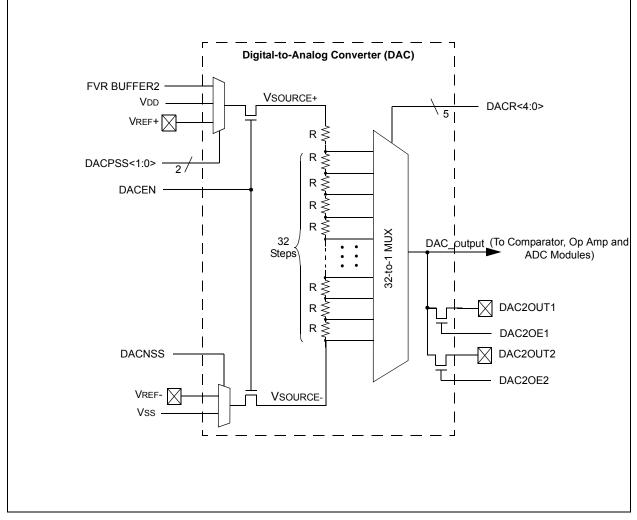

| 4:           | See Section 24.0         | ) "5-Bit Digital-                 | to-Analog Co        | onverter (DAC2     | 2) Module"for   | more informatio   | n.           |

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                  | R/W-0/0                                                     | R/W-0/0        | U-0            | R/W-0/0          | R/W-0/0             | R/W-0/0      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|----------------|------------------|---------------------|--------------|

| ADFM ADCS<2:0>   |                                                                                                                                                                                                                                                                          |                                                             |                | ADNREF         | ADPRE            | F<1:0>              |              |

| bit 7            |                                                                                                                                                                                                                                                                          |                                                             |                |                |                  |                     | bit 0        |

|                  |                                                                                                                                                                                                                                                                          |                                                             |                |                |                  |                     |              |

| Legend:          |                                                                                                                                                                                                                                                                          |                                                             |                |                |                  |                     |              |

| R = Readable     | e bit                                                                                                                                                                                                                                                                    | W = Writable                                                | bit            | U = Unimpler   | nented bit, read | l as '0'            |              |

| u = Bit is unc   | hanged                                                                                                                                                                                                                                                                   | x = Bit is unkr                                             | nown           | -n/n = Value a | at POR and BO    | R/Value at all      | other Resets |

| '1' = Bit is set | t                                                                                                                                                                                                                                                                        | '0' = Bit is clea                                           | ared           |                |                  |                     |              |

|                  |                                                                                                                                                                                                                                                                          |                                                             |                |                |                  |                     |              |

| bit 7            | 1 = Right ju<br>loaded.                                                                                                                                                                                                                                                  | Result Format<br>stified. Six Most<br>ified. Six Least      | Significant bi |                |                  |                     |              |

| bit 6-4          | ADCS<2:0>: ADC Conversion Clock Select bits<br>111 = FRC (clock supplied from an internal RC oscillator)<br>110 = Fosc/64<br>101 = Fosc/16<br>100 = Fosc/4<br>011 = FRC (clock supplied from an internal RC oscillator)<br>010 = Fosc/32<br>001 = Fosc/8<br>000 = Fosc/2 |                                                             |                |                |                  |                     |              |

| bit 3            | Unimpleme                                                                                                                                                                                                                                                                | nted: Read as '                                             | 0'             |                |                  |                     |              |

| bit 2            | ADNREF: A/D Negative Voltage Reference Configuration bit<br>1 = VREF- is connected to Vref- pin<br>0 = VREF- is connected to Vss                                                                                                                                         |                                                             |                |                |                  |                     |              |

| bit 1-0          | 11 = VREF+                                                                                                                                                                                                                                                               | <b>0&gt;:</b> ADC Positivities connected to is connected to | internal Fixed | Voltage Refere |                  | dule <sup>(1)</sup> |              |

specification exists. See Table 34-16: ADC Conversion Requirements for details.

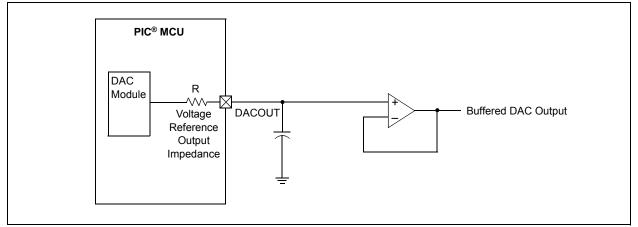

FIGURE 24-2:

**VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE**

# 30.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt, if enabled):

- Start condition detected

- Stop condition detected

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

# 30.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 30.7** "**Baud Rate Generator**" for more detail.

# 30.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 30-25).

# 31.6 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

# 31.6.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 31.5.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

## 31.6.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RCSTA and TXSTA Control registers must be configured for synchronous slave transmission (see Section 31.5.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                              |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$<br>are set.                          |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |  |  |

| Operation:       | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |  |  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |  |  |  |  |

| COMF                                                  | Complement f                                                                                                                                                |  |  |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                               | [label] COMF f,d                                                                                                                                            |  |  |  |  |  |  |

| Operands:                                             | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |  |  |

| Operation: $(\overline{f}) \rightarrow (destination)$ |                                                                                                                                                             |  |  |  |  |  |  |

| Status Affected:                                      | Z                                                                                                                                                           |  |  |  |  |  |  |

| Description:                                          | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |  |

| CLRF             | Clear f                                                               |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |  |

| DECF             | Decrement f                                                                                                                                       |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECF f,d                                                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                 |  |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W register. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |  |  |  |  |  |

# CLRWClear WSyntax:[label] CLRWOperands:NoneOperation: $00h \rightarrow (W)$ <br/> $1 \rightarrow Z$ Status Affected:ZDescription:W register is cleared. Zero bit (Z) is<br/>set.

# TABLE 34-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup> (CONTINUED)

| PIC16LF1713/6 |                        |      |                                  | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |        |       |            |                        |  |  |

|---------------|------------------------|------|----------------------------------|-------------------------------------------------------------------------|--------|-------|------------|------------------------|--|--|

| PIC16F1713/6  |                        |      | Low-Power Sleep Mode, VREGPM = 1 |                                                                         |        |       |            |                        |  |  |

| Param         | Device Characteristics |      | Truck                            | Max.                                                                    | Max.   | Units | Conditions |                        |  |  |

| No.           | Device Characteristics | Min. | Тур†                             | +85°C                                                                   | +125°C |       | VDD        | Note                   |  |  |

| D030          |                        | _    | 250                              | _                                                                       | _      | μA    | 1.8        | ADC Current (Note 3),  |  |  |

|               |                        | —    | 250                              |                                                                         |        | μA    | 3.0        | conversion in progress |  |  |

| D030          |                        | —    | 280                              |                                                                         | _      | μA    | 2.3        | ADC Current (Note 3),  |  |  |

|               |                        | —    | 280                              |                                                                         | _      | μA    | 3.0        | conversion in progress |  |  |

|               |                        | —    | 280                              |                                                                         |        | μA    | 5.0        | 7                      |  |  |

| D031          |                        | —    | 250                              | 650                                                                     | _      | μA    | 3.0        | Op Amp (High-power)    |  |  |

| D031          |                        | —    | 250                              | 650                                                                     | _      | μA    | 3.0        | Op Amp (High-power)    |  |  |

|               |                        | —    | 350                              | 850                                                                     | —      | μA    | 5.0        |                        |  |  |

| D032          |                        | —    | 250                              | 600                                                                     | _      | μA    | 1.8        | Comparator,            |  |  |

|               |                        | —    | 300                              | 650                                                                     | _      | μA    | 3.0        | CxSP = 0               |  |  |

| D032          |                        | —    | 280                              | 600                                                                     |        | μA    | 2.3        | Comparator,            |  |  |

|               |                        | —    | 300                              | 650                                                                     | _      | μA    | 3.0        | CxSP = 0               |  |  |

|               |                        | _    | 310                              | 650                                                                     | _      | μA    | 5.0        | VREGPM = 0             |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC clock source is FRC.

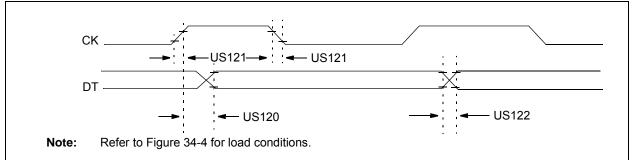

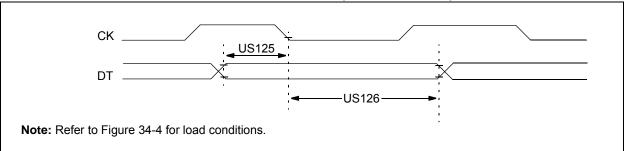

## TABLE 34-22: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS