Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

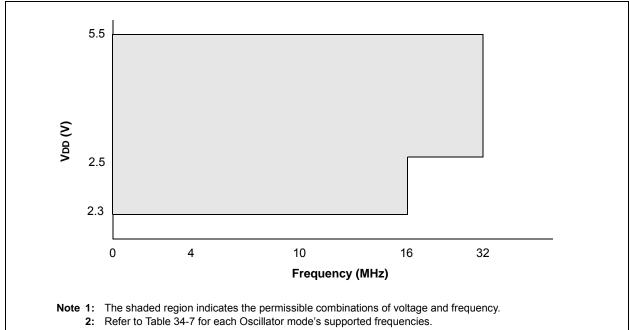

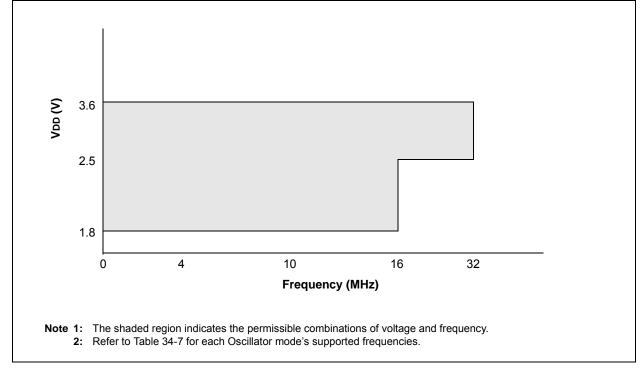

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1713-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-10.

| TABLE 3-2: CORE REGISTERS |

|---------------------------|

|---------------------------|

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| k0Ah or x8Ah | PCLATH |

| k0Bh or x8Bh | INTCON |

# TABLE 3-5: PIC16(L)F1713 MEMORY MAP, BANK 8-23

|               | BANK 8                        |              | BANK 9                        |              | BANK 10                       |              | BANK 11                       |              | BANK 12                       |              | BANK 13                       |              | BANK 14                       |              | BANK 15                       |

|---------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|

| 400h          | Core Registers<br>(Table 3-2) | 480h         | Core Registers<br>(Table 3-2) | 500h         | Core Registers<br>(Table 3-2) | 580h         | Core Registers<br>(Table 3-2) | 600h         | Core Registers<br>(Table 3-2) | 680h         | Core Registers<br>(Table 3-2) | 700h         | Core Registers<br>(Table 3-2) | 780h         | Core Registers<br>(Table 3-2) |

| 40Bh          |                               | 48Bh         |                               | 50Bh         |                               | 58Bh         |                               | 60Bh         |                               | 68Bh         |                               | 70Bh         |                               | 78Bh         |                               |

| 40Ch          | _                             | 48Ch         | _                             | 50Ch         | _                             | 58Ch         | _                             | 60Ch         | —                             | 68Ch         | —                             | 70Ch         | _                             | 78Ch         | _                             |

| 40Dh          | _                             | 48Dh         | _                             | 50Dh         | —                             | 58Dh         | —                             | 60Dh         | —                             | 68Dh         | —                             | 70Dh         |                               | 78Dh         | _                             |

| 40Eh          | _                             | 48Eh         | —                             | 50Eh         | —                             | 58Eh         | —                             | 60Eh         |                               | 68Eh         |                               | 70Eh         |                               | 78Eh         | _                             |

| 40Fh          | _                             | 48Fh         | —                             | 50Fh         | _                             | 58Fh         | _                             | 60Fh         | —                             | 68Fh         | —                             | 70Fh         | _                             | 78Fh         | _                             |

| 410h          | —                             | 490h         | —                             | 510h         | —                             | 590h         | —                             | 610h         | —                             | 690h         | —                             | 710h         | —                             | 790h         | —                             |

| 411h          | _                             | 491h         | _                             | 511h         | OPA1CON                       | 591h         |                               | 611h         | _                             | 691h         | COG1PHR                       | 711h         |                               | 791h         | _                             |

| 412h          | —                             | 492h         | —                             | 512h         | _                             | 592h         | _                             | 612h         | —                             | 692h         | COG1PHF                       | 712h         | _                             | 792h         | _                             |

| 413h          | _                             | 493h         | _                             | 513h         |                               | 593h         |                               | 613h         |                               | 693h         | COG1BLKR                      | 713h         |                               | 793h         |                               |

| 414h          | _                             | 494h         | _                             | 514h         |                               | 594h         |                               | 614h         |                               | 694h         | COG1BLKF                      | 714h         |                               | 794h         |                               |

| 415h          | TMR4                          | 495h         | _                             | 515h         | OPA2CON                       | 595h         |                               | 615h         | _                             | 695h         | COG1DBR                       | 715h         | _                             | 795h         |                               |

| 416h          | PR4                           | 496h         | _                             | 516h         |                               | 596h         |                               | 616h         | _                             | 696h         | COG1DBF                       | 716h         |                               | 796h         | _                             |

| 417h          | T4CON                         | 497h         | —                             | 517h         | —                             | 597h         | —                             | 617h         | PWM3DCL                       | 697h         | COG1CON0                      | 717h         |                               | 797h         | —                             |

| 418h          | —                             | 498h         | NCO1ACCL                      | 518h         | —                             | 598h         | —                             | 618h         | PWM3DCH                       | 698h         | COG1CON1                      | 718h         | —                             | 798h         | —                             |

| 419h          | —                             | 499h         | NCO1ACCH                      | 519h         |                               | 599h         |                               | 619h         | PWM3CON                       | 699h         | COG1RIS                       | 719h         | _                             | 799h         |                               |

| 41Ah          | —                             | 49Ah         | NCO1ACCU                      | 51Ah         |                               | 59Ah         |                               | 61Ah         | PWM4DCL                       | 69Ah         | COG1RSIM                      | 71Ah         | _                             | 79Ah         |                               |

| 41Bh          | _                             | 49Bh         | NCO1INCL                      | 51Bh         | _                             | 59Bh         | _                             | 61Bh         | PWM4DCH                       | 69Bh         | COG1FIS                       | 71Bh         | _                             | 79Bh         | _                             |

| 41Ch          | TMR6                          | 49Ch         | NCO1INCH                      | 51Ch         | _                             | 59Ch         | _                             | 61Ch         | PWM4CON                       | 69Ch         | COG1FSIM                      | 71Ch         | _                             | 79Ch         | _                             |

| 41Dh          | PR6                           | 49Dh         | NCO1INCU                      | 51Dh         |                               | 59Dh         |                               | 61Dh         | _                             | 69Dh         | COG1ASD0                      | 71Dh         |                               | 79Dh         |                               |

| 41Eh          | T6CON                         | 49Eh         | NCO1CON                       | 51Eh         |                               | 59Eh         |                               | 61Eh         | _                             | 69Eh         | COG1ASD1<br>COG1STR           | 71Eh         | _                             | 79Eh         |                               |

| 41Fh<br>420h  |                               | 49Fh<br>4A0h | NCO1CLK                       | 51Fh<br>520h |                               | 59Fh<br>5A0h |                               | 61Fh<br>620h |                               | 69Fh<br>6A0h | COGISTR                       | 71Fh<br>720h |                               | 79Fh<br>7A0h | —                             |

| 42011         |                               | 47 1011      |                               | 02011        |                               | 0/1011       |                               | 02011        |                               | 0/1011       |                               | 72011        |                               | ////         |                               |

|               | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |              | Unimplemented<br>Read as '0'  |

| 46Fh          |                               | 4EFh         |                               | 56Fh         |                               | 5EFh         |                               | 66Fh         |                               | 6EFh         |                               | 76Fh         |                               | 7EFh         |                               |

| 470h          |                               | 4F0h         |                               | 570h         |                               | 5F0h         |                               | 670h         |                               | 6F0h         |                               | 770h         |                               | 7F0h         |                               |

|               | Accesses                      | -            | Accesses                      |              | Accesses                      | -            | Accesses                      |

|               | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |              | 70h – 7Fh                     |

| 47Fh          |                               | 4FFh         |                               | 57Fh         |                               | 5FFh         |                               | 67Fh         |                               | 6FFh         |                               | 77Fh         | -                             | 7FFh         |                               |

| 4/11/1        |                               | 41111        |                               | 5/111        |                               | 51111        |                               | 0/111        |                               | 01111        |                               | 77111        |                               |              |                               |

|               | BANK 16                       |              | BANK 17                       |              | BANK 18                       |              | BANK 19                       |              | BANK 20                       |              | BANK 21                       |              | BANK 22                       |              | BANK 23                       |

| 800h          |                               | 880h         |                               | 900h         |                               | 980h         |                               | A00h         |                               | A80h         |                               | B00h         |                               | B80h         |                               |

|               | Core Registers                |              | Core Registers                |              | Core Registers                |              | Core Registers                |              | Core Registers                |              | Core Registers                |              | Core Registers                |              | Core Registers                |

|               | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |              | (Table 3-2)                   |

| 80Bh          |                               | 88Bh         |                               | 90Bh         |                               | 98Bh         |                               | A0Bh         |                               | A8Bh         |                               | B0Bh         |                               | B8Bh         |                               |

| 80Ch          |                               | 88Ch         |                               | 90Ch         |                               | 98Ch         |                               | A0Ch         |                               | A8Ch         |                               | B0Ch         |                               | B8Ch         |                               |

|               | Unimplemented                 |              | Unimplemented                 |              | Unimplemented                 |              | Unimplemented                 |              | Unimplemented                 |              | Unimplemented                 |              | Unimplemented                 |              | Unimplemented                 |

|               | Read as '0'                   |              | Read as '0'                   |              | Read as '0'                   |              | Read as '0'                   |              | Read as '0'                   |              | Read as '0'                   |              | Read as '0'                   |              | Read as '0'                   |

| 06 <b>5</b> 6 |                               | 000          |                               | OCEN         |                               | 9EFh         |                               | A6Fh         |                               | AEFh         |                               | DOCH         |                               | BEFh         |                               |

| 86Fh          |                               | 8EFh         |                               | 96Fh         |                               |              |                               |              |                               |              |                               | B6Fh         |                               |              |                               |

| 870h          | A                             | 8F0h         | A                             | 970h         | A                             | 9F0h         | A                             | A70h         | A                             | AF0h         | A                             | B70h         | A                             | BF0h         | A                             |

|               | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |              | Accesses<br>70h – 7Fh         |

|               | 7011 – 7FN                    |              | /011 – /FN                    |              | 700 – 7FN                     |

| 87Fh          |                               | 8FFh         |                               | 97Fh         |                               | 9FFh         |                               | A7Fh         |                               | AFFh         |                               | B7Fh         |                               | BFFh         |                               |

Legend: = Unimplemented data memory locations, read as '0'.

TABLE 3-9:PIC16(L)F1713/6 MEMORY<br/>MAP, BANK 31

|         | Bank 31                            |                      |

|---------|------------------------------------|----------------------|

| F8Ch    |                                    |                      |

|         | Unimplemented<br>Read as '0'       |                      |

| FE3h    |                                    |                      |

| FE4h    | STATUS_SHAD                        |                      |

| FE5h    | WREG_SHAD                          |                      |

| FE6h    | BSR_SHAD                           |                      |

| FE7h    | PCLATH_SHAD                        |                      |

| FE8h    | FSR0L_SHAD                         |                      |

| FE9h    | FSR0H_SHAD                         |                      |

| FEAh    | FSR1L_SHAD                         |                      |

| FEBh    | FSR1H_SHAD                         |                      |

| FECh    | —                                  |                      |

| FEDh    | STKPTR                             |                      |

| FEEh    | TOSL                               |                      |

| FEFh    | TOSH                               |                      |

| FF0h    | _                                  |                      |

| FFFh    |                                    |                      |

| Legend: | = Unimplemented da<br>read as '0', | ta memory locations, |

# 6.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaled output of the 16 MHz HFINTOSC, 500 kHz MFINTOSC, and 31 kHz LFINTOSC connect to a multiplexer (see Figure 6-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4x PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

# 6.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4x PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4x PLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4x PLL cannot be disabled by software and the SPLLEN option will not be available.

The 4x PLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4x PLL with the internal oscillator.

# 6.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 6.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by the value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 6-1.

#### 6.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

# 6.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 26.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 6.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

# 6.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

| U-0             | U-0        | R/W-0/0           | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|-----------------|------------|-------------------|-----------------|------------------|------------------|----------------|--------------|

| _               | _          |                   |                 | TUN              | <5:0>            |                |              |

| bit 7           | 4          |                   |                 |                  |                  |                | bit 0        |

|                 |            |                   |                 |                  |                  |                |              |

| Legend:         |            |                   |                 |                  |                  |                |              |

| R = Readabl     | e bit      | W = Writable      | bit             | U = Unimplen     | nented bit, read | d as '0'       |              |

| u = Bit is und  | hanged     | x = Bit is unkr   | nown            | -n/n = Value a   | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is se | t          | '0' = Bit is clea | ared            |                  |                  |                |              |

|                 |            |                   |                 |                  |                  |                |              |

| bit 7-6         | Unimpleme  | nted: Read as '   | 0'              |                  |                  |                |              |

| bit 5-0         | TUN<5:0>:  | Frequency Tunir   | ng bits         |                  |                  |                |              |

|                 | 100000 = N | /linimum frequer  | ncy             |                  |                  |                |              |

|                 | •          |                   |                 |                  |                  |                |              |

|                 | •          |                   |                 |                  |                  |                |              |

|                 | 111111 =   |                   |                 |                  |                  |                |              |

|                 | 000000 = 0 | Scillator module  | e is running at | the factory-cali | brated frequen   | су             |              |

|                 | 000001 =   |                   |                 |                  |                  |                |              |

|                 | •          |                   |                 |                  |                  |                |              |

|                 | •          |                   |                 |                  |                  |                |              |

|                 | 011110 =   |                   |                 |                  |                  |                |              |

|                 | 011111 = N | /laximum freque   | ency            |                  |                  |                |              |

# REGISTER 6-3: OSCTUNE: OSCILLATOR TUNING REGISTER

| TABLE 6-2: | SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES |  |

|------------|----------------------------------------------------|--|

|            |                                                    |  |

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4    | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|--------|-------|----------|---------|--------|--------|--------|---------------------|

| OSCCON  | SPLLEN |        | IRCF  | <3:0>    |         | —      | SCS    | 75     |                     |

| OSCSTAT | SOSCR  | PLLR   | OSTS  | HFIOFR   | HFIOFL  | MFIOFR | LFIOFR | HFIOFS | 76                  |

| OSCTUNE | _      | _      |       | TUN<5:0> |         |        |        |        |                     |

| PIR2    | OSFIF  | C2IF   | C1IF  | _        | BCL1IF  | TMR6IF | TMR4IF | CCP2IF | 88                  |

| PIE2    | OSFIE  | C2IE   | C1IE  | _        | BCL1IE  | TMR6IE | TMR4IE | CCP2IE | 85                  |

| T1CON   | TMR1C  | S<1:0> | T1CKP | S<1:0>   | T10SCEN | T1SYNC | _      | TMR10N | 265                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 6-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|------------|---------|---------|---------------------|

| CONFIG1 | 13:8 |         |         | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |         | —       | 47                  |

|         | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | TE<1:0>  | FOSC<2:0   |         |         | 47                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

| REGISTER 10-5: | PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| U-1           | R/W-0/0            | R/W-0/0                                   | R/W/HC-0/0         | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0           | R/S/HC-0/0           | R/S/HC-0/0       |

|---------------|--------------------|-------------------------------------------|--------------------|---------------------------|-------------------|----------------------|------------------|

| (1)           | CFGS               | LWLO <sup>(3)</sup>                       | FREE               | WRERR                     | WREN              | WR                   | RD               |

| bit 7         |                    |                                           |                    |                           |                   |                      | bit (            |

|               |                    |                                           |                    |                           |                   |                      |                  |

| Legend:       |                    |                                           |                    |                           |                   |                      |                  |

| R = Reada     |                    | W = Writable b                            |                    | U = Unimpleme             | -                 |                      | _                |

|               | n only be set      | x = Bit is unkno                          |                    |                           |                   | /alue at all other F | Resets           |

| '1' = Bit is  | set                | '0' = Bit is clear                        | red                | HC = Bit is clear         | red by hardware   | •                    |                  |

| h:4 7         |                    | tod. Deed as (1)                          |                    |                           |                   |                      |                  |

| bit 7         | •                  | ted: Read as '1'                          |                    |                           |                   |                      |                  |

| bit 6         |                    | guration Select bit<br>Configuration, Use |                    |                           |                   |                      |                  |

|               |                    | Flash program me                          |                    | ID Registers              |                   |                      |                  |

| bit 5         |                    | Write Latches On                          | -                  |                           |                   |                      |                  |

|               |                    | addressed progra                          |                    | e latch is loaded/u       | pdated on the r   | next WR comman       | d                |

|               |                    | ressed program m                          |                    | h is loaded/update        | ed and a write of | all program memo     | ory write latche |

|               |                    | itiated on the next                       |                    |                           |                   |                      |                  |

| bit 4         | •                  | am Flash Erase Ei                         |                    |                           |                   |                      |                  |

|               |                    | s an erase operati<br>s a write operatior |                    |                           | rdware cleared    | upon completion)     |                  |

| bit 3         |                    | gram/Erase Error                          |                    | Command                   |                   |                      |                  |

| DIL J         |                    | n indicates an imp                        |                    | or erase sequence         | e attempt or te   | rmination (bit is s  | et automatical   |

|               |                    | et attempt (write '                       |                    |                           |                   | (                    |                  |

|               | 0 = The prog       | gram or erase ope                         | ration complete    | d normally                |                   |                      |                  |

| bit 2         | 0                  | am/Erase Enable                           |                    |                           |                   |                      |                  |

|               |                    | rogram/erase cyc                          |                    | -1                        |                   |                      |                  |

|               |                    | programming/eras                          | ing of program i   | lash                      |                   |                      |                  |

| bit 1         | WR: Write Co       |                                           | rogrom/orogo o     | noration                  |                   |                      |                  |

|               |                    | a program Flash p<br>ration is self-timed |                    |                           | re once operatio  | on is complete       |                  |

|               |                    | bit can only be se                        |                    |                           |                   |                      |                  |

|               | 0 = Program        | /erase operation t                        | to the Flash is co | omplete and inact         | ive               |                      |                  |

| bit 0         | RD: Read Co        |                                           |                    |                           |                   |                      |                  |

|               |                    | a program Flash r                         | ead. Read takes    | s one cycle. RD is        | cleared in hard   | ware. The RD bit     | can only be se   |

|               |                    | red) in software.<br>t initiate a progran | n Flash read       |                           |                   |                      |                  |

| Note 1:       | Unimplemented bit, |                                           |                    |                           |                   |                      |                  |

| NOLE 1.<br>2. | The WRERR hit is   |                                           | w bardwara wh      | on a program mor          | nony write or or  | no operation is at   | artad (MD = 1    |

- 2: The WRERR bit is automatically set by hardware when a program memory write or erase operation is started (WR = 1).

- **3:** The LWLO bit is ignored during a program memory erase operation (FREE = 1).

# 11.1 PORTA Registers

#### 11.1.1 DATA REGISTER

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 11-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 11-1 shows how to initialize PORTA.

Reading the PORTA register (Register 11-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

#### 11.1.2 DIRECTION CONTROL

The TRISA register (Register 11-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

# 11.1.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 11-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.1.4 SLEW RATE CONTROL

The SLRCONA register (Register 11-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 11.1.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 11-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

# 11.1.6 ANALOG CONTROL

The ANSELA register (Register 11-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### EXAMPLE 11-1: INITIALIZING PORTA

| <pre>; This code example illustrates<br/>; initializing the PORTA register. The<br/>; other ports are initialized in the same<br/>; manner.<br/>BANKSEL PORTA ;<br/>CLRF PORTA ; Init PORTA<br/>BANKSEL LATA ; Data Latch<br/>CLRF LATA ;<br/>BANKSEL ANSELA ;<br/>CLRF ANSELA ;digital I/O<br/>BANKSEL TRISA ;<br/>MOVLW B'00111000' ;Set RA&lt;5:3&gt; as inputs<br/>MOVWF TRISA ; and set RA&lt;2:0&gt; as<br/>;outputs</pre> |                                                                |                                                                   |                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| CLRF PORTA ; Init PORTA<br>BANKSEL LATA ; Data Latch<br>CLRF LATA ;<br>BANKSEL ANSELA ;<br>CLRF ANSELA ;<br>CLRF ANSELA ;digital I/O<br>BANKSEL TRISA ;<br>MOVLW B'00111000' ;Set RA<5:3> as inputs<br>MOVWF TRISA ;and set RA<2:0> as                                                                                                                                                                                           | ; initia<br>; other                                            | alizing the P<br>ports are in                                     | ORTA register. The                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  | CLRF<br>BANKSEL<br>CLRF<br>BANKSEL<br>CLRF<br>BANKSEL<br>MOVLW | PORTA<br>LATA<br>LATA<br>ANSELA<br>ANSELA<br>TRISA<br>B'00111000' | <pre>;Init PORTA ;Data Latch ; ; ;digital I/O ; ;Set RA&lt;5:3&gt; as inputs ;and set RA&lt;2:0&gt; as</pre> |

## 17.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- 7. Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the desired pin PPS control bits.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- **2:** For operation with other peripherals only, disable PWMx pin outputs.

# 17.1.10 SETUP FOR PWM OPERATION TO OTHER DEVICE PERIPHERALS

The following steps should be taken when configuring the module for PWM operation to be used by other device peripherals:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- 7. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

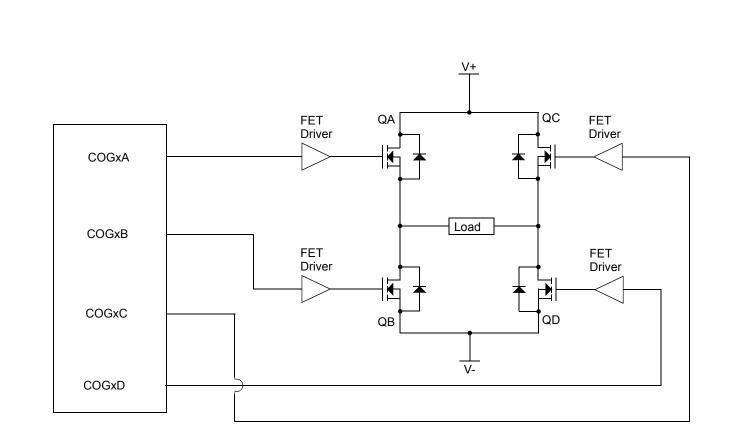

# FIGURE 18-1: EXAMPLE OF FULL-BRIDGE APPLICATION

DS40001726C-page 170

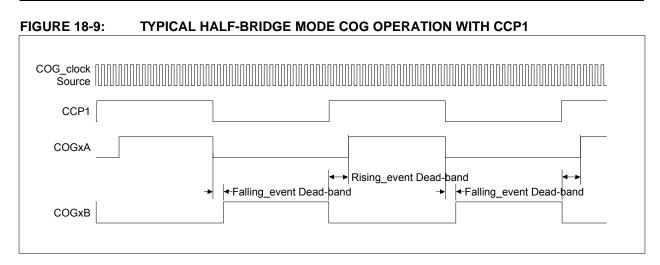

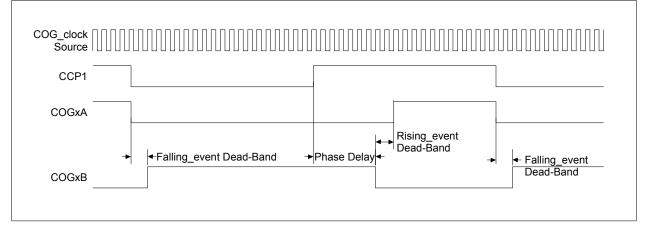

#### FIGURE 18-10: HALF-BRIDGE MODE COG OPERATION WITH CCP1 AND PHASE DELAY

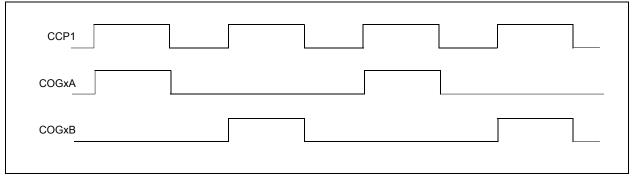

#### FIGURE 18-11: PUSH-PULL MODE COG OPERATION WITH CCP1

| R/W-0/0         | R/W-0/0                  | R/W-0/0                 | R/W-0/0          | R/W-0/0                           | R/W-0/0           | U-0              | U-0          |

|-----------------|--------------------------|-------------------------|------------------|-----------------------------------|-------------------|------------------|--------------|

| GxASE           | GxARSEN                  | GxASD                   | 3D<1:0>          | GxASD                             | AC<1:0>           | —                | —            |

| bit 7           |                          |                         |                  |                                   |                   |                  | bit 0        |

|                 |                          |                         |                  |                                   |                   |                  |              |

| Legend:         |                          |                         |                  |                                   |                   |                  |              |

| R = Readabl     | e bit                    | W = Writable            | bit              | U = Unimpleme                     | ented bit, read a | ıs '0'           |              |

| u = Bit is und  | changed                  | x = Bit is unkr         | nown             | -n/n = Value at                   | POR and BOR/      | Value at all oth | ner Resets   |

| '1' = Bit is se | et                       | '0' = Bit is clea       | ared             | q = Value depe                    | ends on conditio  | n                |              |

|                 |                          |                         |                  |                                   |                   |                  |              |

| bit 7           | GxASE: Auto              | o-Shutdown Eve          | ent Status bit   |                                   |                   |                  |              |

|                 |                          | in the shutdown         |                  |                                   |                   |                  |              |

|                 | 0 = COG is e             | either not in the       | shutdown stat    | te or will exit the               | shutdown state    | on the next ris  | sing event   |

| bit 6           |                          | Auto-Restart En         | able bit         |                                   |                   |                  |              |

|                 |                          | tart is enabled         |                  |                                   |                   |                  |              |

|                 |                          | tart is disabled        |                  |                                   |                   |                  |              |

| bit 5-4         |                          |                         |                  | to-shutdown Ov                    |                   |                  |              |

|                 |                          |                         |                  | COGxD when s                      |                   |                  |              |

|                 | •                        |                         |                  | COGxD when sl<br>/hen shutdown is |                   | е                |              |

|                 |                          |                         |                  | ig polarity, is pla               |                   | and COGxD w      | hen shutdown |

|                 | is activ                 |                         |                  | .g p =,, , . = p                  |                   |                  |              |

| bit 3-2         | GxASDAC<1                | <b>1:0&gt;:</b> COGxA a | nd COGxC Au      | to-shutdown Ov                    | erride Level Sel  | ect bits         |              |

|                 | 11 = A logic             | '1' is placed or        | COGxA and        | COGxC when sh                     | nutdown is active | e                |              |

|                 | 0                        |                         |                  | COGxC when sh                     |                   | e                |              |

|                 |                          |                         |                  | hen shutdown is                   |                   |                  |              |

|                 | 00 = The ina<br>is activ |                         | ie pin, includin | g polarity, is pla                | cea on COGxA      | and COGxC w      | nen shutdown |

| bit 1-0         | Unimplemen               | <b>ted:</b> Read as '   | n'               |                                   |                   |                  |              |

# REGISTER 18-7: COGxASD0: COG AUTO-SHUTDOWN CONTROL REGISTER 0

bit 1-0 Unimplemented: Read as '0'

# REGISTER 18-14: COGxPHR: COG RISING EDGE PHASE DELAY COUNT REGISTER

| U-0     | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|-----|---------|---------|---------|---------|---------|---------|

| —       | _   |         |         | GxPH    | R<5:0>  |         |         |

| bit 7   |     |         |         |         |         |         | bit 0   |

|         |     |         |         |         |         |         |         |

| Legend: |     |         |         |         |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 5-0

bit 5-0

GxPHR<5:0>: Rising Edge Phase Delay Count Value bits

= Number of COGx clock periods to delay rising edge event

#### REGISTER 18-15: COGxPHF: COG FALLING EDGE PHASE DELAY COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   |         |         | GxPH    | F<5:0>  |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

GxPHF<5:0>: Falling Edge Phase Delay Count Value bits

= Number of COGx clock periods to delay falling edge event

# 26.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 26-1 displays the Timer1 enable selections.

| TABLE 26-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 26.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 26-2 displays the clock source selections.

#### 26.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- C1 or C2 comparator input to Timer1 gate

#### 26.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- Note: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

# TABLE 26-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | T10SCEN | Clock Source                   |

|-------------|---------|--------------------------------|

| 11          | х       | LFINTOSC                       |

| 10          | 0       | External Clocking on T1CKI Pin |

| 01          | x       | System Clock (Fosc)            |

| 00          | x       | Instruction Clock (Fosc/4)     |

# 29.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by FOSC/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

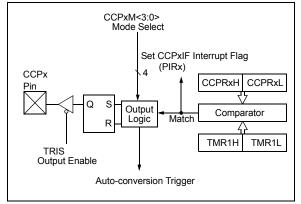

# 29.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- · Toggle the CCPx output

- Set the CCPx output

- Clear the CCPx output

- Generate an Auto-conversion Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 29-2 shows a simplified diagram of the compare operation.

#### FIGURE 29-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 29.2.1 CCPX PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 29.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Compare    |

|       | mode. In order for Compare mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, TImer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 29.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### 29.2.4 AUTO-CONVERSION TRIGGER

When Auto-conversion Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- · Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Auto-conversion Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Auto-conversion Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

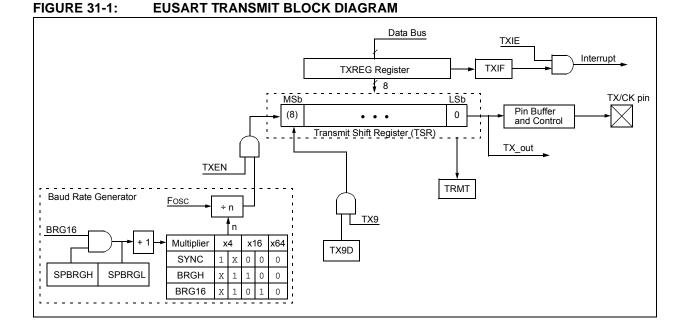

# 31.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

#### · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- · Input buffer overrun error detection

- · Received character framing error detection

- · Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 31-1 and Figure 31-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

Configurable Logic Cell (CLC)

## FIGURE 31-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

| ana 31 - Xee    | 838887                                  | reconside in Sc     | te white the t                                | Ador: 68 is ex                          | 99.<br>    |                       |                                       |                   |                |                                  |

|-----------------|-----------------------------------------|---------------------|-----------------------------------------------|-----------------------------------------|------------|-----------------------|---------------------------------------|-------------------|----------------|----------------------------------|

| 1222/12222      | /////////////////////////////////////// |                     |                                               |                                         | 7777777777 |                       |                                       |                   |                |                                  |

| 200,001         | ······                                  |                     |                                               |                                         | ····:<br>: |                       |                                       |                   | ad of Şicteres | 9                                |

| 2000            |                                         |                     |                                               | ,                                       |            |                       | ;<br>;<br>                            |                   | ~~~ ,<br>      |                                  |

| 6073366 juur    |                                         |                     | '/ <i>///////////////////////////////////</i> |                                         |            |                       |                                       |                   |                | ,<br>                            |

| - waxes bee l   | ·····                                   | ·····               |                                               | ·/·····<br>· · · ·                      | ······     | •                     | · · · · · · · · · · · · · · · · · · · | ······<br>· · · · | , L.           | ·····                            |

| i chacki e<br>B | ्या व्या व्या<br>संबद्ध विष्ठारक        | na a a a<br>XX ming | in na na na na<br>T                           | n internet internet.<br>A second second | an an a    | t has not have n<br>t |                                       |                   |                | - Asto-Oleanad<br>- Asto-Oleanad |

(i) The SUSSARY remains in His while the Vicili hit is ad

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

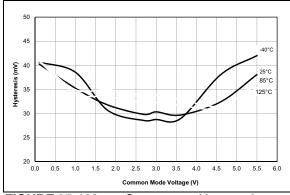

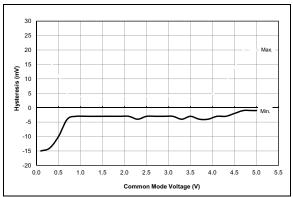

**FIGURE 35-103:** Comparator Hysteresis, NP Mode (CxSP = 1), VDD = 5.5V, Typical Measured Values, PIC16F1713/6 Only.

**FIGURE 35-105:** Comparator Offset, NP Mode (CxSP = 1), VDD = 5.5V, Typical Measured Values From -40°C to 125°C, PIC16F1713/6 Only.

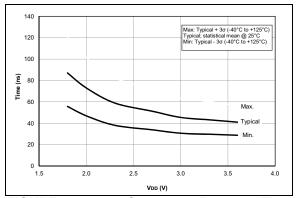

**FIGURE 35-107:** Comparator Response Time Over Voltage, NP Mode (CxSP = 1), Typical Measured Values, PIC16F1713/6 Only.

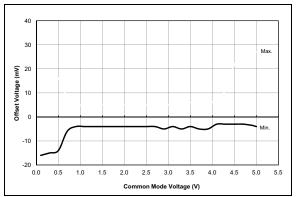

**FIGURE 35-104:** Comparator Offset, NP Mode (CxSP = 1), VDD = 5.0V, Typical Measured Values at 25°C, PIC16F1713/6 Only.

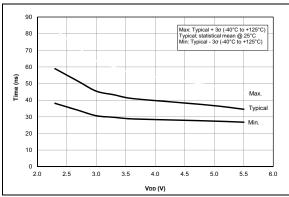

**FIGURE 35-106:** Comparator Response Time Over Voltage, NP Mode (CxSP = 1), Typical Measured Values, PIC16LF1713/6 Only.

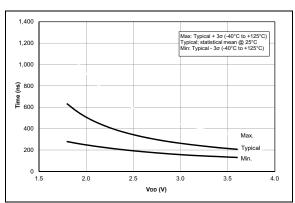

**FIGURE 35-108:** Comparator Output Filter Delay Time Over Temp., NP Mode (CxSP = 1), Typical Measured Values, PIC16LF1713/6 Only.