#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1713-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Value on all Value on Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Addr Name other POR, BOR Resets Bank 10 50Ch Unimplemented 510h OPA1SP 511h **OPA1CON** OPA1EN OPA1UG OPA1PCH<1:0> 00-0 --00 00-0 --00 512h Unimplemented 514h 515h OPA2CON OPA2EN OPA2SP OPA2UG \_ OPA2PCH<1:0> 00-0 --00 00-0 --00 516h Unimplemented 51Fh Bank 11 58Ch Unimplemented to 59Fh Bank 12 60Ch to Unimplemented 616h 617h PWM3DCL PWM3DC<1:0> \_ xx--\_\_\_\_ uu--\_\_\_ **PWM3DCH** 618h PWM3DCH<7:0> XXXX XXXX uuuu uuuu 619h PWM3CON **PWM3EN** PWM3OUT PWM3POL 0-x0 ----11-1111 ----61Ah PWM4DCL PWM4DCL<1:0> xx--\_\_\_\_ uu--\_\_\_ 61Bh PWM4DCH PWM4DCH<7:0> XXXX XXXX uuuu uuuu 61Ch PWM4CON PWM4EN PWM4OUT PWM4POL 0-x0 ---u-uu ---61Dh Unimplemented 61Fh Bank 13 68Ch Unimplemented to 690h 691h COG1PHR COG Rising Edge Phase Delay Count Register \_ \_ --xx xxxx -uu uuuu 692h COG1PHF COG Falling Edge Phase Delay Count Register -uu uuuu --xx xxxx 693h COG1BLKR COG Rising Edge Blanking Count Register --xx xxxx -uu uuuu COG1BLKF 694h COG Falling Edge Blanking Count Register --uu uuuu --xx xxxx 695h COG1DBR \_ \_ COG Rising Edge Dead-band Count Register --xx xxxx -uu uuuu 696h COG1DBF COG Falling Edge Dead-band Count Register -xx xxxx -uu uuuu 697h COG1CON0 G1EN G1LD G1CS<1:0> G1MD<2:0> 00-0 0000 00-0 0000 698h COG1CON1 G1RDBS G1FDBS \_ G1POLD G1POLC G1POLB G1POLA 00--00--0000 \_ 0000 699h COG1RIS G1RIS7 G1RIS6 G1RIS5 G1RIS4 G1RIS3 G1RIS2 G1RIS1 G1RIS0 0000 0000 -000 0000 69Ah COG1RSIM G1RSIM7 0000 0000 -000 0000 G1RSIM6 G1RSIM5 G1RSIM4 G1RSIM3 G1RSIM2 G1RSIM1 G1RSIM0 69Bh COG1FIS G1FIS7 G1FIS6 0000 0000 -000 0000 G1FIS5 G1FIS4 G1FIS3 G1FIS2 G1FIS1 G1FIS0 COG1FSIM 69Ch G1FSIM7 G1FSIM6 G1FSIM5 G1FSIM4 G1FSIM3 G1FSIM2 G1FSIM1 G1FSIM0 0000 0000 -000 0000 69Dh COG1ASD0 G1ASE G1ARSEN G1ASDBD<1:0> G1ASDAC<1:0> 0001 01--0001 01-COG1ASD1 G1AS1E 69Eh \_ G1AS3E G1AS2E G1AS0E \_\_\_\_ 0000 0000 69Fh COG1STR 0000 0001 0000 0001 G1SDATD G1SDATC G1SDATB G1SDATA G1STRD G1STRC G1STRB G1STRA

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-11:**

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved Shaded locations are unimplemented, read as '0'. Note

1: Unimplemented, read as '1'

2: Unimplemented on PIC16(L)F1713/6.

### 6.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 6-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 6-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 6-1.

Start-up delay specifications are located in the oscillator tables of **Section 34.0** "**Electrical Specifications**".

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|--------|---------|--------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 83                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |        |        | 256                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | CCP1IE  | TMR2IE | TMR1IE | 84                  |

| PIE2       | OSFIE   | C2IE   | C1IE   | _      | BCL1IE | TMR6IE  | TMR4IE | CCP2IE | 85                  |

| PIE3       |         | NCOIE  | COGIE  | ZCDIE  | CLC4IE | CLC3IE  | CLC2IE | CLC1IE | 86                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | CCP1IF  | TMR2IF | TMR1IF | 87                  |

| PIR2       | OSFIF   | C2IF   | C1IF   | _      | BCL1IF | TMR6IF  | TMR4IF | CCP2IF | 88                  |

| PIR3       | _       | NCOIF  | COGIF  | ZCDIF  | CLC4IF | CLC3IF  | CLC2IF | CLC1IF | 89                  |

# TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

### 11.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when it is in Analog mode.

# 11.3 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

# 11.3.1 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

# 11.3.2 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

# 11.3.3 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

# 11.3.4 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

# 11.3.5 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

### 11.3.6 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information. Analog input functions, such as ADC and Op Amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

# REGISTER 13-7: IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCCP7  | IOCCP6  | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 IOCCP<7:0>: Interrupt-on-Change PORTC Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 13-8: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCCN7  | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **IOCCN<7:0>:** Interrupt-on-Change PORTC Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

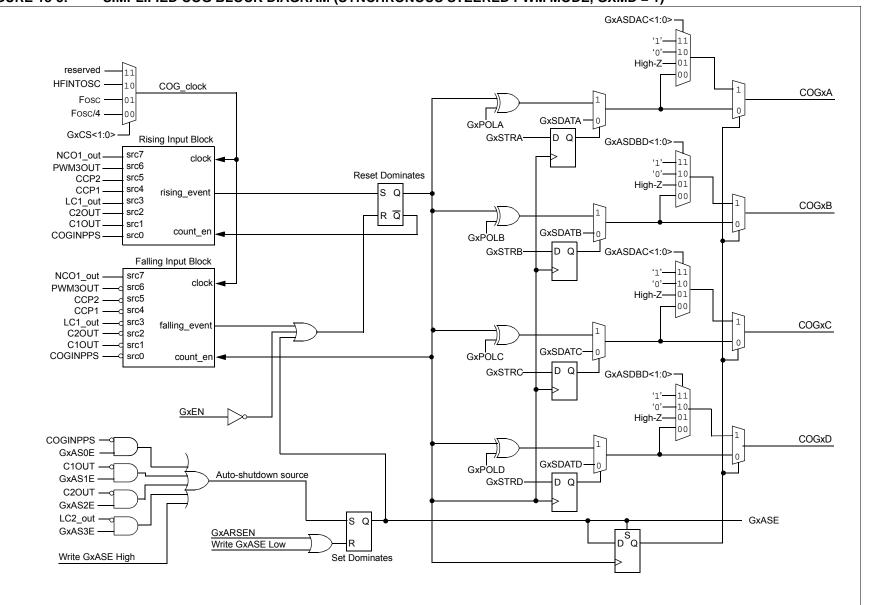

# 18.0 COMPLEMENTARY OUTPUT GENERATOR (COG) MODULE

The primary purpose of the Complementary Output Generator (COG) is to convert a single output PWM signal into a two output complementary PWM signal. The COG can also convert two separate input events into a single or complementary PWM output.

The COG PWM frequency and duty cycle are determined by a rising event input and a falling event input. The rising event and falling event may be the same source. Sources may be synchronous or asynchronous to the COG\_clock.

The rate at which the rising event occurs determines the PWM frequency. The time from the rising event input to the falling event input determines the duty cycle.

A selectable clock input is used to generate the phase delay, blanking, and dead-band times. Dead-band time can also be generated with a programmable time delay, which is independent from all clock sources.

Simplified block diagrams of the various COG modes are shown in Figure 18-2 through Figure 18-6.

The COG module has the following features:

- Six modes of operation:

- Steered PWM mode

- Synchronous Steered PWM mode

- Forward Full-Bridge mode

- Reverse Full-Bridge mode

- Half-Bridge mode

- Push-Pull mode

- Selectable COG\_clock clock source

- · Independently selectable rising event sources

- Independently selectable falling event sources

- Independently selectable edge or level event sensitivity

- Independent output polarity selection

- Phase delay with independent rising and falling delay times

- Dead-band control with:

- independent rising and falling event dead-band times

- Synchronous and asynchronous timing

- Blanking control with independent rising and falling event blanking times

- Auto-shutdown control with:

- Independently selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control (high, low, off, and Hi-Z)

## 18.1 Fundamental Operation

#### 18.1.1 STEERED PWM MODES

In steered PWM mode, the PWM signal derived from the input event sources is output as a single phase PWM which can be steered to any combination of the four COG outputs. Outputs are selected by setting the GxSTRA through GxSTRD bits of the COGxSTR register (Register 18-9). When the steering bits are cleared, then the output data is the static level determined by the GxSDATA through GxSDATD bits of the COGxSTR register. Output steering takes effect on the instruction cycle following the write to the COGxSTR register.

Synchronous steered PWM mode is identical to the steered PWM mode except that changes to the output steering take effect on the first rising event after the COGxSTR register write. Static output data is not synchronized.

Steering mode configurations are shown in Figure 18-2 and Figure 18-3.

Steered PWM and synchronous steered PWM modes are selected by setting the GxMD bits of the COGxCON0 register (Register 18-1) to '000' and '001' respectively.

### 18.1.2 FULL-BRIDGE MODES

In both Forward and Reverse Full-Bridge modes, two of the four COG outputs are active and the other two are inactive. Of the two active outputs, one is modulated by the PWM input signal and the other is on at 100% duty cycle. When the direction is changed, the dead-band time is inserted to delay the modulated output. This gives the unmodulated driver time to shut down, thereby, preventing shoot-through current in the series connected power devices.

In Forward Full-Bridge mode, the PWM input modulates the COGxD output and drives the COGA output at 100%.

In Reverse Full-Bridge mode, the PWM input modulates the COGxB output and drives the COGxC output at 100%.

The full-bridge configuration is shown in Figure 18-4. Typical full-bridge waveforms are shown in Figure 18-12 and Figure 18-13.

Full-Bridge Forward and Full-Bridge Reverse modes are selected by setting the GxMD bits of the COGxCON0 register to '010' and '011', respectively.

# FIGURE 18-3: SIMPLIFIED COG BLOCK DIAGRAM (SYNCHRONOUS STEERED PWM MODE, GXMD = 1)

| R/W-0/0          | R/W-0/0                                                                                                                                             | R/W-0/0                                                     | R/W-0/0          | R/W-0/0        | R/W-0/0           | R/W-0/0   | R/W-0/0     |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|----------------|-------------------|-----------|-------------|--|

| GxFIS7           | GxFIS6                                                                                                                                              | GxFIS5                                                      | GxFIS4           | GxFIS3         | GxFIS2            | GxFIS1    | GxFIS0      |  |

| bit 7            |                                                                                                                                                     |                                                             |                  |                |                   |           | bit 0       |  |

|                  |                                                                                                                                                     |                                                             |                  |                |                   |           |             |  |

| Legend:          |                                                                                                                                                     |                                                             |                  |                |                   |           |             |  |

| R = Readable     |                                                                                                                                                     | W = Writable                                                |                  | •              | nented bit, reac  |           |             |  |

| u = Bit is uncha | anged                                                                                                                                               | x = Bit is unkr                                             |                  |                | at POR and BO     |           | ther Resets |  |

| '1' = Bit is set |                                                                                                                                                     | '0' = Bit is cle                                            | ared             | q = Value dep  | pends on condit   | ion       |             |  |

| h:+ 7            |                                                                                                                                                     |                                                             |                  | 7 Frabla bit   |                   |           |             |  |

| bit 7            |                                                                                                                                                     | Gx Falling Ever<br>out is enabled a                         | •                |                |                   |           |             |  |

|                  |                                                                                                                                                     | but is enabled a<br>but has no effec                        |                  |                |                   |           |             |  |

| bit 6            | GxFIS6: CO                                                                                                                                          | Gx Falling Ever                                             | t Input Source   | e 6 Enable bit |                   |           |             |  |

|                  | 1 = PWM3 o                                                                                                                                          | output is enable                                            | d as a falling e | event input    |                   |           |             |  |

|                  | 0 = PWM3 h                                                                                                                                          | as no effect on                                             | the falling eve  | ent            |                   |           |             |  |

| bit 5            |                                                                                                                                                     | Gx Falling Ever                                             | •                |                |                   |           |             |  |

|                  |                                                                                                                                                     | utput is enabled                                            |                  |                |                   |           |             |  |

| L:1 4            |                                                                                                                                                     | utput has no eff                                            |                  | •              |                   |           |             |  |

| bit 4            |                                                                                                                                                     | Gx Falling Ever                                             | •                |                |                   |           |             |  |

|                  |                                                                                                                                                     | enabled as a fa<br>as no effect on t                        |                  |                |                   |           |             |  |

| bit 3            | GxFIS3: CO                                                                                                                                          | Gx Falling Ever                                             | t Input Source   | e 3 Enable bit |                   |           |             |  |

|                  |                                                                                                                                                     | utput is enabled                                            |                  |                |                   |           |             |  |

|                  | 0 = CLC1 ou                                                                                                                                         | utput has no effe                                           | ect on the falli | ng event       |                   |           |             |  |

| bit 2            | GxFIS2: CO                                                                                                                                          | Gx Falling Ever                                             | t Input Source   | e 2 Enable bit |                   |           |             |  |

|                  |                                                                                                                                                     | ator 2 output is                                            |                  |                |                   |           |             |  |

|                  | 0 = Comparator 2 output has no effect on the falling event                                                                                          |                                                             |                  |                |                   |           |             |  |

| bit 1            | GxFIS1: COGx Falling Event Input Source 1 Enable bit                                                                                                |                                                             |                  |                |                   |           |             |  |

|                  | <ul> <li>1 = Comparator 1 output is enabled as a falling event input</li> <li>0 = Comparator 1 output has no effect on the falling event</li> </ul> |                                                             |                  |                |                   |           |             |  |

| bit 0            | •                                                                                                                                                   | <b>GxFIS0:</b> COGx Falling Event Input Source 0 Enable bit |                  |                |                   |           |             |  |

|                  |                                                                                                                                                     | cted with COGx                                              | •                |                | led as falling ev | ent input |             |  |

|                  | 0 = Pin selec                                                                                                                                       |                                                             |                  | <b>U</b>       | <b>J</b> -        |           |             |  |

# REGISTER 18-5: COGxFIS: COG FALLING EVENT INPUT SELECTION REGISTER

| Name      | Bit 7        | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 5          | Bit 4          | Bit 3  | Bit 2       | Bit 1   | Bit 0  | Register<br>on Page |

|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|--------|-------------|---------|--------|---------------------|

| CCP1CON   | —            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DC1B           | <1:0>          |        | CCP1        | ∕l<3:0> |        | 284                 |

| CCPR1L    | Capture/Corr | pare/PWM R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | egister 1 (LSB | )              |        |             |         |        | 281*                |

| CCPTMRS   | P4TSE        | L<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P3TSE          | L<1:0>         | C2TSE  | L<1:0>      | C1TSE   | L<1:0> | 272                 |

| INTCON    | GIE          | PEIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TMR0IE         | INTE           | IOCIE  | TMR0IF      | INTF    | IOCIF  | 83                  |

| PIE1      | TMR1GIE      | ADIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RCIE           | TXIE           | SSP1IE | CCP1IE      | TMR2IE  | TMR1IE | 84                  |

| PIE2      | OSFIE        | C2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C1IE           | _              | BCL1IE | TMR6IE      | TMR4IE  | CCP2IE | 85                  |

| PIR1      | TMR1GIF      | ADIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RCIF           | TXIF           | SSP1IF | CCP1IF      | TMR2IF  | TMR1IF | 87                  |

| PIR2      | OSFIF        | C2IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C1IF           | _              | BCL1IF | TMR6IF      | TMR4IF  | CCP2IF | 88                  |

| PR2       | Timer2 Perio | d Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                |        |             |         |        | 268*                |

| ANSELB    | —            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ANSB5          | ANSB4          | ANSB3  | ANSB2       | ANSB1   | ANSB0  | 126                 |

| ANSELC    | ANSC7        | ANSC6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ANSC5          | ANSC4          | ANSC3  | ANSC2       | _       | —      | 131                 |

| TRISB     | TRISB7       | TRISB6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TRISB5         | TRISB4         | TRISB3 | TRISB2      | TRISB1  | TRISB0 | 125                 |

| TRISC     | TRISC7       | TRISC6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TRISC5         | TRISC4         | TRISC3 | TRISC2      | TRISC1  | TRISC0 | 130                 |

| RxyPPS    | —            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —              |                |        | RxyPPS<4:0> | •       |        | 137                 |

| CCP1PPS   | —            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —              |                | C      | CP1PPS<4:0  | >       |        | 136                 |

| CCP2PPS   | —            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —              | — CCP2PPS<4:0> |        |             |         |        | 136                 |

| T2CON     | —            | T2OUTPS<3:0> TMR2ON T2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |                |        | T2CKP       | S<1:0>  | 270    |                     |

| TMR2      | Timer2 Modu  | ule Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                |        |             |         |        | 268                 |

| La second |              | University of the section of the sec |                |                |        |             |         |        |                     |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP. \* Page provides register information.

# 30.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

## 30.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

# 30.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

# 30.4.3 SDA AND SCL PINS

Selection of any  $I^2C$  mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

- Note 1: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

- 2: Any device pin can be selected for SDA and SCL functions with the PPS peripheral. These functions are bidirectional. The SDA input is selected with the SSPDATPPS registers. The SCL input is selected with the SSPCLKPPS registers. Outputs are selected with the RxyPPS registers. It is the user's responsibility to make the selections so that both the input and the output for each function is on the same pin.

#### 30.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

# TABLE 30-2: I<sup>2</sup>C BUS TERMS

| TABLE 30-2:         | I <sup>2</sup> C BUS TERMS                                                                                                                                                                       |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                                      |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                   |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                    |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                    |

| Slave               | The device addressed by the master.                                                                                                                                                              |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                              |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                           |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                     |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                     |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPADD.                                                                                                               |

| Write Request       | Slave receives a matching<br>address with R/W bit clear, and is<br>ready to clock in data.                                                                                                       |

| Read Request        | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                    |