Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1713t-i-ml |

#### REGISTER 6-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| R-1/q | R-0/q | R-q/q | R-0/q  | R-0/q  | R-q/q  | R-0/0  | R-0/q  |

|-------|-------|-------|--------|--------|--------|--------|--------|

| SOSCR | PLLR  | OSTS  | HFIOFR | HFIOFL | MFIOFR | LFIOFR | HFIOFS |

| bit 7 |       |       |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Conditional

bit 7 SOSCR: Secondary Oscillator Ready bit

<u>If T10SCEN = 1</u>:

1 = Secondary oscillator is ready0 = Secondary oscillator is not ready

If T1OSCEN = 0:

1 = Secondary clock source is always ready

bit 6 PLLR 4x PLL Ready bit

1 = 4x PLL is ready

0 = 4x PLL is not ready

bit 5 OSTS: Oscillator Start-up Timer Status bit

1 = Running from the clock defined by the FOSC<2:0> bits of the Configuration Words

0 = Running from an internal oscillator (FOSC<2:0> = 100)

bit 4 HFIOFR: High-Frequency Internal Oscillator Ready bit

1 = HFINTOSC is ready

0 = HFINTOSC is not ready

bit 3 HFIOFL: High-Frequency Internal Oscillator Locked bit

1 = HFINTOSC is at least 2% accurate 0 = HFINTOSC is not 2% accurate

bit 2 MFIOFR: Medium Frequency Internal Oscillator Ready bit

1 = MFINTOSC is ready

0 = MFINTOSC is not ready

bit 1 LFIOFR: Low-Frequency Internal Oscillator Ready bit

1 = LFINTOSC is ready0 = LFINTOSC is not ready

bit 0 **HFIOFS:** High-Frequency Internal Oscillator Stable bit

1 = HFINTOSC is at least 0.5% accurate 0 = HFINTOSC is not 0.5% accurate

### 11.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when it is in Analog mode.

### 11.2 Register Definitions: PORTA

#### **REGISTER 11-1: PORTA: PORTA REGISTER**

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|---------|---------|-------|---------|---------|---------|

| RA7     | RA6     | RA5     | RA4     | RA3   | RA2     | RA1     | RA0     |

| bit 7   |         |         |         |       |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup>

1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-2: TRISA: PORTA TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

#### REGISTER 11-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 SLRA<7:0>: PORTA Slew Rate Enable bits

For RA<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

#### REGISTER 11-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 75-0 INLVLA<7:0>: PORTA Input Level Select bits

For RA<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change0 = TTL input used for PORT reads and interrupt-on-change

#### REGISTER 13-7: IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCCP7  | IOCCP6  | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-0 **IOCCP<7:0>:** Interrupt-on-Change PORTC Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-8: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCCN7  | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 IOCCN<7:0>: Interrupt-on-Change PORTC Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 13-11: IOCEN: INTERRUPT-ON-CHANGE PORTE NEGATIVE EDGE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|---------|-----|-----|-------|

| _     | _   | _   | _   | IOCEN3  | _   | _   | _     |

| bit 7 |     |     |     |         |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 Unimplemented: Read as '0'

bit 3 IOCEN: Interrupt-on-Change PORTE Negative Edge Enable bits

${\tt 1}$  = Interrupt-on-Change enabled on the pin for a negative going edge. IOCEFx bit and IOCIF flag will

be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 2-0 **Unimplemented:** Read as '0'

#### REGISTER 13-12: IOCEF: INTERRUPT-ON-CHANGE PORTE FLAG REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W/HS-0/0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|------------|-----|-----|-------|

| _     | _   | _   | _   | IOCEF3     | _   | _   | _     |

| bit 7 |     |     |     |            |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared HS - Bit is set in hardware

bit 7-4 **Unimplemented:** Read as '0'

bit 3 **IOCEF:** Interrupt-on-Change PORTE Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCEPx = 1 and a rising edge was detected on REx, or when IOCENx = 1 and a falling edge

was detected on REx.

0 = No change was detected, or the user cleared the detected change.

bit 2-0 **Unimplemented:** Read as '0'

#### 16.11 Register Definitions: Comparator Control

#### REGISTER 16-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0 | R-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-0/0 | R/W-0/0 |

|---------|-------|-----|---------|---------|---------|---------|---------|

| CxON    | CxOUT | _   | CxPOL   | CxZLF   | CxSP    | CxHYS   | CxSYNC  |

| bit 7   |       |     |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 CxON: Comparator Enable bit

1 = Comparator is enabled

0 = Comparator is disabled and consumes no active power

bit 6 **CxOUT:** Comparator Output bit

If CxPOL = 1 (inverted polarity):

1 = CxVP < CxVN0 = CxVP > CxVN

If CxPOL = 0 (non-inverted polarity):

1 = CxVP > CxVN 0 = CxVP < CxVN

bit 5 **Unimplemented:** Read as '0'

bit 4 CxPOL: Comparator Output Polarity Select bit

1 = Comparator output is inverted0 = Comparator output is not inverted

bit 3 CxZLF: Comparator Zero Latency Filter Enable bit

1 = Comparator output is filtered0 = Comparator output is unfiltered

bit 2 CxSP: Comparator Speed/Power Select bit

1 = Comparator operates in normal power, higher speed mode

0 = Comparator operates in low-power, low-speed mode

bit 1 CxHYS: Comparator Hysteresis Enable bit

1 = Comparator hysteresis enabled

0 = Comparator hysteresis disabled

bit 0 CxSYNC: Comparator Output Synchronous Mode bit

1 = Comparator output to Timer1 and I/O pin is synchronous to changes on Timer1 clock source. Output updated on the falling edge of Timer1 clock source.

0 = Comparator output to Timer1 and I/O pin is asynchronous.

TABLE 21-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock P         | eriod (TAD) | Device Frequency (Fosc)     |                             |                             |                             |                             |                             |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz                      | 20 MHz                      | 20 MHz 16 MHz               |                             | 4 MHz                       | 1 MHz                       |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(2)</sup>      |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(2)</sup>      | 64.0 μs <sup>(2)</sup>      |  |

| FRC                 | x11         | 1.0-6.0 μs <sup>(1,4)</sup> |  |

Legend: Shaded cells are outside of recommended range.

Note 1: See TAD parameter for FRC source typical TAD value.

- 2: These values violate the required TAD time.

- 3: Outside the recommended TAD time.

- 4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock Fosc. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

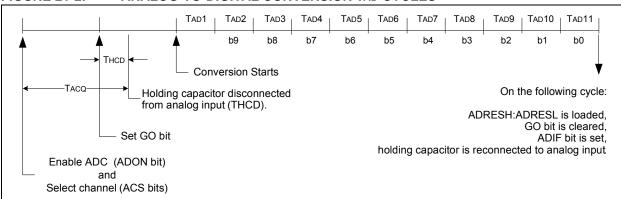

FIGURE 21-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 21.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

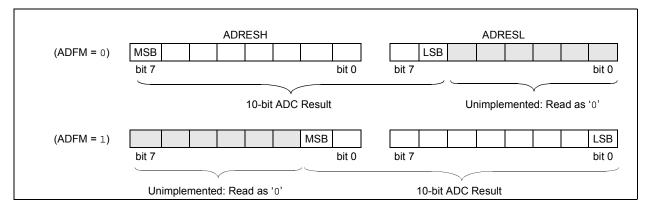

#### 21.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 21-3 shows the two output formats.

#### FIGURE 21-3: 10-BIT ADC CONVERSION RESULT FORMAT

#### 21.3 **Register Definitions: ADC Control**

#### REGISTER 21-1: ADCON0: ADC CONTROL REGISTER 0

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|----------|---------|---------|---------|---------|

| _     |         |         | CHS<4:0> |         |         | GO/DONE | ADON    |

| bit 7 |         |         |          |         |         |         | bit 0   |

Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared

bit 7 Unimplemented: Read as '0' bit 6-2 CHS<4:0>: Analog Channel Select bits 11111 = FVR (Fixed Voltage Reference) Buffer 1 Output(2) 11110 = DAC1\_output<sup>(1)</sup> 11101 = Temperature Indicator (3) 11100 = DAC2\_output<sup>(4)</sup> 11011 = Reserved. No channel connected. 10011 **= AN19** 10010 = AN1810001 = AN17 10000 = AN16 01111 = AN1501110 = AN14 01101 = AN13 01100 = AN12 01011 = AN1101010 = AN10 01001 = AN901000 = AN800111 = Reserved. No channel connected. 00110 = Reserved. No channel connected. 00101 = Reserved. No channel connected. 00100 = AN400011 = AN300010 = AN200001 **= AN1** 00000 = AN0GO/DONE: ADC Conversion Status bit bit 1

1 = ADC conversion cycle in progress. Setting this bit starts an ADC conversion cycle. This bit is automatically cleared by hardware when the ADC conversion has completed.

0 = ADC conversion completed/not in progress

bit 0 ADON: ADC Enable bit

1 = ADC is enabled

0 = ADC is disabled and consumes no operating current

Note 1: See Section 23.0 "8-Bit Digital-to-Analog Converter (DAC1) Module" for more information.

- 2: See Section 14.0 "Fixed Voltage Reference (FVR)" for more information.

- 3: See Section 15.0 "Temperature Indicator Module" for more information.

- 4: See Section 24.0 "5-Bit Digital-to-Analog Converter (DAC2) Module"for more information.

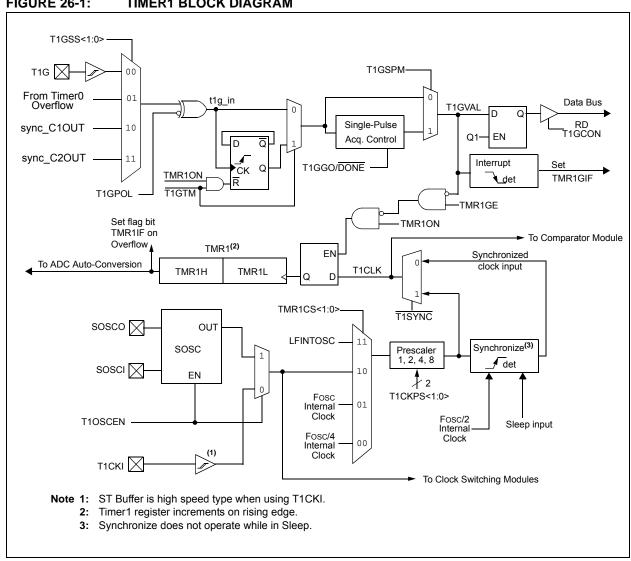

### TIMER1 MODULE WITH GATE **CONTROL**

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- · 2-bit prescaler

- · Dedicated 32 kHz oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- · Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Auto-conversion Trigger (with CCP)

- · Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-pulse mode

- · Gate Value Status

- · Gate Event Interrupt

Figure 26-1 is a block diagram of the Timer1 module.

#### **FIGURE 26-1: TIMER1 BLOCK DIAGRAM**

#### 26.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 26-1 displays the Timer1 enable selections.

TABLE 26-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

#### 26.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 26-2 displays the clock source selections.

#### 26.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

#### 26.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

Note:

In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- Write to TMR1H or TMR1L

- · Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low

TABLE 26-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | T10SCEN | Clock Source                   |  |  |

|-------------|---------|--------------------------------|--|--|

| 11          | х       | LFINTOSC                       |  |  |

| 10          | 0       | External Clocking on T1CKI Pin |  |  |

| 01          | х       | /stem Clock (Fosc)             |  |  |

| 00          | x       | Instruction Clock (Fosc/4)     |  |  |

#### 29.1 Capture Mode

The Capture mode function described in this section is available and identical for all CCP modules.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 29-1 shows a simplified diagram of the capture operation.

#### 29.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Note:

If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

# FIGURE 29-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 29.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 29.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 29.1.4 CCP PRESCALER

Note:

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 29-1 demonstrates the code to perform this function.

### EXAMPLE 29-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point ;to CCPxCON |

|---------|-------------|-------------------------------------|

| CLRF    | CCPxCON     | ;Turn CCP module off                |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with                |

|         |             | ;the new prescaler                  |

|         |             | ;move value and CCP ON              |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this             |

|         |             | ;value                              |

TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name      | Bit 7       | Bit 6           | Bit 5         | Bit 4                                           | Bit 3                            | Bit 2     | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |

|-----------|-------------|-----------------|---------------|-------------------------------------------------|----------------------------------|-----------|--------|--------|-----------------------------|

| ANSELB    | _           | _               | ANSB5         | ANSB4                                           | ANSB4 ANSB3 ANSB2 ANSB1          |           |        |        | 126                         |

| ANSELC    | ANSC7       | ANSC6           | ANSC5         | ANSC4 ANSC3 ANSC2 — —                           |                                  |           |        |        | 131                         |

| INTCON    | GIE         | PEIE            | TMR0IE        | INTE IOCIE TMR0IF INTF IOCIF                    |                                  |           |        |        | 83                          |

| PIE1      | TMR1GIE     | ADIE            | RCIE          | TXIE                                            | TXIE SSP1IE CCP1IE TMR2IE TMR1IE |           |        |        |                             |

| PIE2      | OSFIE       | C2IE            | C1IE          | _                                               | BCL1IE                           | TMR6IE    | TMR4IE | CCP2IE | 85                          |

| PIR1      | TMR1GIF     | ADIF            | RCIF          | TXIF                                            | TXIF SSP1IF CCP1IF TMR2IF TMR1IF |           |        |        | 87                          |

| PIR2      | OSFIF       | C2IF            | C1IF          | <ul> <li>BCL1IF TMR6IF TMR4IF CCP2IF</li> </ul> |                                  |           |        |        | 88                          |

| RxyPPS    | _           | _               | _             | RxyPPS<4:0>                                     |                                  |           |        |        | 137                         |

| SSPCLKPPS | _           | _               | _             |                                                 | SS                               | PCLKPPS<4 | 0>     |        | 136                         |

| SSPDATPPS | _           | _               | _             |                                                 | SS                               | PDATPPS<4 | :0>    |        | 136                         |

| SSP1ADD   |             |                 |               | ADD                                             | <7:0>                            |           |        |        | 336                         |

| SSP1BUF   | Synchronous | s Serial Port F | Receive Buffe | r/Transmit Re                                   | egister                          |           |        |        | 289*                        |

| SSP1CON1  | WCOL        | SSPOV           | SSPEN         | CKP                                             |                                  | SSPM      | <3:0>  |        | 333                         |

| SSP1CON2  | GCEN        | ACKSTAT         | ACKDT         | ACKEN                                           | RCEN                             | PEN       | RSEN   | SEN    | 334                         |

| SSP1CON3  | ACKTIM      | PCIE            | SCIE          | BOEN SDAHT SBCDE AHEN DHEN                      |                                  |           |        | 335    |                             |

| SSP1MSK   |             |                 |               | MSK<7:0>                                        |                                  |           |        | 336    |                             |

| SSP1STAT  | SMP         | CKE             | D/Ā           | Р                                               | S                                | R/W       | UA     | BF     | 332                         |

| TRISB     | TRISB7      | TRISB6          | TRISB5        | TRISB4                                          | TRISB3                           | TRISB2    | TRISB1 | TRISB0 | 125                         |

| TRISC     | TRISC7      | TRISC6          | TRISC5        | TRISC4                                          | TRISC3                           | TRISC2    | TRISC1 | TRISC0 | 130                         |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

<sup>\*</sup> Page provides register information.

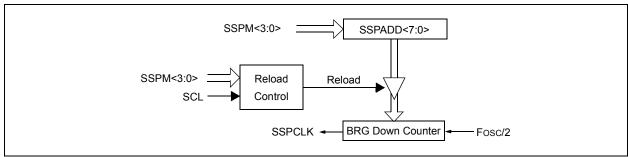

#### 30.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both  $I^2C$  and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSPADD register (Register 30-6). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 30-40 triggers the value from SSPADD to be loaded into the BRG counter. This occurs twice for each oscillation of the module

clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 30-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD.

#### **EQUATION 30-1:**

$$FCLOCK = \frac{FOSC}{(SSPxADD + 1)(4)}$$

#### FIGURE 30-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSPADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

TABLE 30-4: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 34-4 to ensure the system is designed to support IOL requirements.

#### **FIGURE 31-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION**

#### **FIGURE 31-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP**

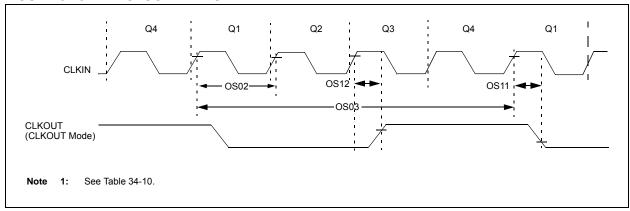

FIGURE 34-5: CLOCK TIMING

TABLE 34-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

|  | ns (unless otherwise stated) |

|--|------------------------------|

|  |                              |

|  |                              |

| Param<br>No. | Sym.  | Characteristic                          | Min. | Тур†   | Max.     | Units | Conditions                |

|--------------|-------|-----------------------------------------|------|--------|----------|-------|---------------------------|

| OS01         | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC   | _      | 0.5      | MHz   | External Clock (ECL)      |

|              |       |                                         | DC   | _      | 4        | MHz   | External Clock (ECM)      |

|              |       |                                         | DC   | _      | 20       | MHz   | External Clock (ECH)      |

|              |       | Oscillator Frequency <sup>(1)</sup>     | _    | 32.768 | _        | kHz   | LP Oscillator             |

|              |       |                                         | 0.1  | _      | 4        | MHz   | XT Oscillator             |

|              |       |                                         | 1    | _      | 4        | MHz   | HS Oscillator             |

|              |       |                                         | 1    | _      | 20       | MHz   | HS Oscillator, VDD > 2.7V |

|              |       |                                         | DC   | _      | 4        | MHz   | EXTRC, VDD > 2.0V         |

| OS02         | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27   | _      | $\infty$ | μS    | LP Oscillator             |

|              |       |                                         | 250  | _      | $\infty$ | ns    | XT Oscillator             |

|              |       |                                         | 50   | _      | $\infty$ | ns    | HS Oscillator             |

|              |       |                                         | 50   | _      | $\infty$ | ns    | External Clock (EC)       |

|              |       | Oscillator Period <sup>(1)</sup>        | _    | 30.5   | _        | μS    | LP Oscillator             |

|              |       |                                         | 250  | _      | 10,000   | ns    | XT Oscillator             |

|              |       |                                         | 50   | _      | 1,000    | ns    | HS Oscillator             |

|              |       |                                         | 250  | _      | _        | ns    | EXTRC                     |

| OS03         | TCY   | Instruction Cycle Time <sup>(1)</sup>   | 125  | Tcy    | DC       | ns    | Tcy = 4/Fosc              |

| OS04*        | TosH, | External CLKIN High,                    | 2    | _      | _        | μS    | LP Oscillator             |

|              | TosL  | External CLKIN Low                      | 100  | _      | _        | ns    | XT Oscillator             |

|              |       |                                         | 20   | _      | _        | ns    | HS Oscillator             |

| OS05*        | TosR, | External CLKIN Rise,                    | 0    | _      | $\infty$ | ns    | LP Oscillator             |

|              | TosF  | External CLKIN Fall                     | 0    | _      | $\infty$ | ns    | XT Oscillator             |

|              |       |                                         | 0    | l —    | $\infty$ | ns    | HS Oscillator             |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support