Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1713t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-2: PIC16(L)F1713/6 PINOUT DESCRIPTION

| Name                             | Function | Input<br>Type | Output<br>Type | Description                                  |  |  |

|----------------------------------|----------|---------------|----------------|----------------------------------------------|--|--|

| RA0/AN0/C1IN0-/C2IN0-/           | RA0      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

| CLCINO <sup>(1)</sup>            | AN0      | AN            |                | ADC Channel 0 input.                         |  |  |

|                                  | C1IN0-   | AN            |                | Comparator C2 negative input.                |  |  |

|                                  | C2IN0-   | AN            | _              | Comparator C3 negative input.                |  |  |

|                                  | CLCIN0   | TTL/ST        |                | Configurable Logic Cell source input.        |  |  |

| RA1/AN1/C1IN1-/C2IN1-/           | RA1      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

| DPA1OUT/CLCIN1 <sup>(1)</sup>    | AN1      | AN            | _              | ADC Channel 1 input.                         |  |  |

|                                  | C1IN1-   | AN            | —              | Comparator C1 negative input.                |  |  |

|                                  | C2IN1-   | AN            | _              | Comparator C2 negative input.                |  |  |

|                                  | OPA1OUT  | _             | AN             | Operational Amplifier 1 output.              |  |  |

|                                  | CLCIN1   | TTL/ST        | —              | Configurable Logic Cell source input.        |  |  |

| RA2/AN2/VREF-/C1IN0+/C2IN0+/     | RA2      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

| DAC1OUT1                         | AN2      | AN            |                | ADC Channel 2 input.                         |  |  |

|                                  | VREF-    | AN            | —              | ADC Negative Voltage Reference input.        |  |  |

|                                  | C1IN0+   | AN            | _              | Comparator C2 positive input.                |  |  |

|                                  | C2IN0+   | AN            | _              | Comparator C3 positive input.                |  |  |

|                                  | DAC10UT1 | _             | AN             | Digital-to-Analog Converter output.          |  |  |

| RA3/AN3/VREF+/C1IN1+             | RA3      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                  | AN3      | AN            | _              | ADC Channel 3 input.                         |  |  |

|                                  | VREF+    | AN            |                | ADC Voltage Reference input.                 |  |  |

|                                  | C1IN1+   | AN            | _              | Comparator C1 positive input.                |  |  |

| RA4/OPA1IN+/T0CKI <sup>(1)</sup> | RA4      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                  | OPA1IN+  | AN            |                | Operational Amplifier 1 non-inverting input. |  |  |

|                                  | TOCKI    | TTL/ST        | _              | Timer0 gate input.                           |  |  |

| RA5/AN4/OPA1IN-/DAC2OUT1/        | RA5      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

| <u>SS(1)</u>                     | AN4      | AN            |                | ADC Channel 4 input.                         |  |  |

|                                  | OPA1IN-  | AN            |                | Operational Amplifier 1 inverting input.     |  |  |

|                                  | DAC2OUT1 | _             | AN             | Digital-to-Analog Converter output.          |  |  |

|                                  | SS       | TTL/ST        |                | Slave Select enable input.                   |  |  |

| RA6/OSC2/CLKOUT                  | RA6      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                  | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).        |  |  |

|                                  | CLKOUT   |               | CMOS           | Fosc/4 output.                               |  |  |

| RA7/OSC1/CLKIN                   | RA7      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

|                                  | OSC1     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).        |  |  |

|                                  | CLKIN    | TTL/ST        |                | External clock input (EC mode).              |  |  |

| RB0/AN12/C2IN1+/ZCD/             | RB0      | TTL/ST        | CMOS           | General purpose I/O.                         |  |  |

| COGIN <sup>(1)</sup>             | AN12     | AN            | —              | ADC Channel 12 input.                        |  |  |

|                                  | C2IN1+   | AN            | —              | Comparator C2 positive input.                |  |  |

|                                  | ZCD      | AN            | —              | Zero-Cross Detection Current Source/Sink.    |  |  |

|                                  | COGIN    | TTL/ST        | _              | Complementary Output Generator input.        |  |  |

HV = High Voltage XTAL = Crystal levels

**Note 1:** Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

## 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Flash Program Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

Note 1: The method to access Flash memory through the PMCON registers is described in Section 10.0 "Flash Program Memory Control".

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

**TABLE 3-1:**

Indirect Addressing

## 3.1 **Program Memory Organization**

The enhanced mid-range core has a 15-bit program counter capable of addressing a 32K x 14 program memory space. Table 3-1 and Table 3-2 show the memory sizes implemented for the PIC16(L)F1713/6 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

## 3.2 High Endurance Flash

This device has a 128-byte section of high-endurance program Flash memory (PFM) in lieu of data EEPROM. This area is especially well suited for nonvolatile data storage that is expected to be updated frequently over the life of the end product. See Section 10.2 "Flash **Program Memory Overview**" for more information on writing data to PFM. See Section 3.2.1.2 "Indirect Read with FSR" for more information about using the FSR registers to read byte data stored in PFM.

| Device        | Program Memory Space<br>(Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |  |

|---------------|---------------------------------|--------------------------------|-------------------------------------------------------------|--|

| PIC16(L)F1713 | 4,096                           | FFFh                           | F80h-FFFh                                                   |  |

| PIC16(L)F1716 | 16,384                          | 3FFFh                          | 3F80h-3FFFh                                                 |  |

Note 1: High-endurance Flash applies to the low byte of each address in the range.

DEVICE SIZES AND ADDRESSES

| IGURE 6-7:                                                 | INTERNAL OSCILLATOR SWITCH TIMING                                              |

|------------------------------------------------------------|--------------------------------------------------------------------------------|

| HEINTOSC/<br>NEINTOSC<br>HEINTOSC/<br>MEINTOSC<br>LEINTOSC | LFINTOSC (FBCM and WOY disablad)<br><br>Clarbur Time 2- cycla Sync Running<br> |

| IRCF <3:0>                                                 | $\neq 0$ $X = 0$                                                               |

| System Clock                                               |                                                                                |

| NEINTOSCI<br>MENETOSC                                      | LENVICISC (ENDer FISCH or WOY spanied)                                         |

| HFINTOSC/<br>MEINTOSC                                      | 2-typia Symp     Pureling                                                      |

| LFINTOSC                                                   |                                                                                |

| IRCF <3:0>                                                 | $\neq 0$ $X = 0$                                                               |

| System Clock                                               |                                                                                |

| LEINTOSC -+                                                | NFINTOSCANFINTOSC                                                              |

| HENTOSO/<br>MENTOSO                                        |                                                                                |

| 8908 ×3998                                                 |                                                                                |

| System Clook                                               |                                                                                |

|                                                            |                                                                                |

## 6.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 6.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by the value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bits of the OSCCON register. The user can monitor the OSTS bit of the OSCSTAT register to determine the current system clock source.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 6-1.

#### 6.3.2 OSCILLATOR START-UP TIMER STATUS (OSTS) BIT

The Oscillator Start-up Timer Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the secondary oscillator.

## 6.3.3 SECONDARY OSCILLATOR

The secondary oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the SOSCO and SOSCI device pins.

The secondary oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 26.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 6.3.4 SECONDARY OSCILLATOR READY (SOSCR) BIT

The user must ensure that the secondary oscillator is ready to be used before it is selected as a system clock source. The Secondary Oscillator Ready (SOSCR) bit of the OSCSTAT register indicates whether the secondary oscillator is ready to be used. After the SOSCR bit is set, the SCS bits can be configured to select the secondary oscillator.

## 6.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PLLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

## 11.3 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

## 11.3.1 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

## 11.3.2 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

## 11.3.3 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

## 11.3.4 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 11.3.5 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 11.3.6 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information. Analog input functions, such as ADC and Op Amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

## REGISTER 12-3: PPSLOCK: PPS LOCK REGISTER

| U-0              | U-0    | U-0                | U-0  | U-0                                               | U-0              | U-0      | R/W-0/0        |

|------------------|--------|--------------------|------|---------------------------------------------------|------------------|----------|----------------|

| _                | _      | —                  | —    | —                                                 | —                | _        | PPSLOCKED      |

| bit 7            |        |                    |      |                                                   |                  |          | bit 0          |

|                  |        |                    |      |                                                   |                  |          |                |

| Legend:          |        |                    |      |                                                   |                  |          |                |

| R = Readable     | e bit  | W = Writable I     | oit  | U = Unimplem                                      | nented bit, read | d as '0' |                |

| u = Bit is unc   | hanged | x = Bit is unknown |      | -n/n = Value at POR and BOR/Value at all other Re |                  |          | l other Resets |

| '1' = Bit is set | t      | '0' = Bit is clea  | ared |                                                   |                  |          |                |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

1= PPS is locked. PPS selections can not be changed.

0= PPS is not locked. PPS selections can be changed.

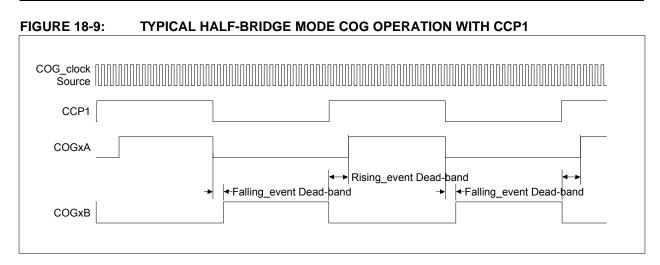

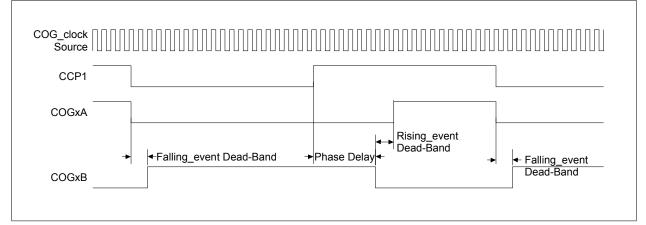

#### FIGURE 18-10: HALF-BRIDGE MODE COG OPERATION WITH CCP1 AND PHASE DELAY

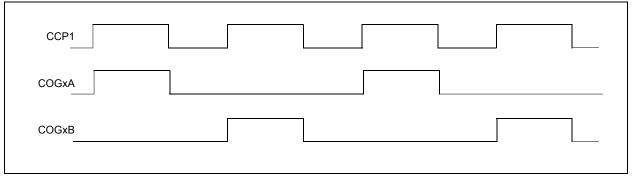

#### FIGURE 18-11: PUSH-PULL MODE COG OPERATION WITH CCP1

## REGISTER 20-6: NCOxINCL: NCOx INCREMENT REGISTER – LOW BYTE<sup>(1)</sup>

| R/W-0/0        | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0         | R/W-0/0         | R/W-0/0 | R/W-1/1 |

|----------------|---------|------------------|---------|-----------------|-----------------|---------|---------|

|                |         |                  | NCOxIN  | IC<7:0>         |                 |         |         |

| bit 7          |         |                  |         |                 |                 |         | bit 0   |

|                |         |                  |         |                 |                 |         |         |

| Legend:        |         |                  |         |                 |                 |         |         |

| P = Poodable b | vit     | M = M/ritable bi | t       | II – I Inimpien | nented hit read | as 'O'  |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxINC<7:0>: NCOx Increment, Low Byte

Note 1: Write the NCOxINCH register first, then the NCOxINCL register. See Section 20.1.4 "Increment Registers" for more information.

## **REGISTER 20-7:** NCOxINCH: NCOx INCREMENT REGISTER – HIGH BYTE<sup>(1)</sup>

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCOxIN  | C<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxINC<15:8>: NCOx Increment, High Byte

Note 1: Write the NCOxINCH register first, then the NCOxINCL register. See Section 20.1.4 "Increment Registers" for more information.

## REGISTER 20-8: NCOxINCU: NCOx INCREMENT REGISTER – UPPER BYTE<sup>(1)</sup>

| U/0   | U/0 | U/0 | U/0 | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|----------------|---------|---------|---------|

| —     |     |     |     | NCOxINC<19:16> |         |         |         |

| bit 7 |     |     |     |                |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCOxINC<19:16>: NCOx Increment, Upper Byte

Note 1: Write the NCOxINCH register first, then the NCOxINCL register. See Section 20.1.4 "Increment Registers" for more information.

## TABLE 21-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock Period (TAD) |           | Device Frequency (Fosc)     |                             |                             |                             |                             |                             |

|------------------------|-----------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| ADC<br>Clock Source    | ADCS<2:0> | 32 MHz                      | 20 MHz                      | 16 MHz                      | 8 MHz                       | 4 MHz                       | 1 MHz                       |

| Fosc/2                 | 000       | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 2.0 μs                      |

| Fosc/4                 | 100       | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                      | 4.0 μs                      |

| Fosc/8                 | 001       | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                      | 8.0 μs <sup>(3)</sup>       |

| Fosc/16                | 101       | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                      | 16.0 μs <sup>(3)</sup>      |

| Fosc/32                | 010       | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 32.0 μs <sup>(2)</sup>      |

| Fosc/64                | 110       | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <sup>(2)</sup>      | 64.0 μs <sup>(2)</sup>      |

| FRC                    | x11       | 1.0-6.0 μs <sup>(1,4)</sup> |

Legend: Shaded cells are outside of recommended range.

**Note 1:** See TAD parameter for FRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

4: The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the FRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

## 23.4 Operation During Sleep

The DAC continues to function during Sleep. When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DAC1CON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 23.5 Effects of a Reset

A device Reset affects the following:

- · DAC is disabled.

- DAC output voltage is removed from the DAC10UT pin.

- The DAC1R<4:0> range select bits are cleared.

## 24.6 Register Definitions: DAC2 Control

| R/W-0/0          | U-0                                                                        | R/W-0/0                          | R/W-0/0          | R/W-0/0                       | R/W-0/0            | U-0              | R/W-0/0 |

|------------------|----------------------------------------------------------------------------|----------------------------------|------------------|-------------------------------|--------------------|------------------|---------|

| DAC2EN           | _                                                                          | DAC2OE1                          | DAC2OE2          | DAC2P                         | 'SS<1:0>           | —                | DAC2NSS |

| bit 7            |                                                                            |                                  |                  |                               |                    |                  | bit C   |

| Legend:          |                                                                            |                                  |                  |                               |                    |                  |         |

| R = Readable     | bit                                                                        | W = Writable b                   | it               | U = Unimpleme                 | ented bit, read as | ʻ0'              |         |

| u = Bit is unch  | anged                                                                      | x = Bit is unkno                 | wn               | -n/n = Value at               | POR and BOR/V      | alue at all othe | Resets  |

| '1' = Bit is set |                                                                            | '0' = Bit is clear               | ed               |                               |                    |                  |         |

| bit 7<br>bit 6   | DAC2EN: DAC<br>1 = DAC is ena<br>0 = DAC is dis<br>Unimplemente            | abled<br>abled<br>d: Read as '0' |                  |                               |                    |                  |         |

| bit 5            | 1 = DAC voltage                                                            |                                  | in output on the | DAC2OUT1 pin<br>e DAC2OUT1 pi |                    |                  |         |

| bit 4            | 1 = DAC voltage                                                            |                                  | in output on the | DAC2OUT2 pin<br>e DAC2OUT2 pi |                    |                  |         |

| bit 3-2          | DAC2PSS<1:0:<br>11 = Reserver<br>10 = FVR Buf<br>01 = VREF+ pi<br>00 = VDD | fer2 output                      | e Source Select  | bits                          |                    |                  |         |

| bit 1            | Unimplemente                                                               | d: Read as '0'                   |                  |                               |                    |                  |         |

| bit 0            | <b>DAC2NSS:</b> DAV<br>1 = VREF-<br>0 = VSS                                | C2 Negative So                   | urce Select bits |                               |                    |                  |         |

#### REGISTER 24-1: DAC2CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

### REGISTER 24-2: DAC2CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | —   |         |         | DAC2R<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DAC2R<4:0>: DAC Voltage Output Select bits

## TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC2 MODULE

| Name     | Bit 7  | Bit 6 | Bit 5   | Bit 4      | Bit 3        | Bit 2 | Bit 1 | Bit 0   | Register<br>on page |

|----------|--------|-------|---------|------------|--------------|-------|-------|---------|---------------------|

| DAC2CON0 | DAC2EN | _     | DAC2OE1 | DAC2OE2    | DAC2PSS<1:0> |       | _     | DAC2NSS | 253                 |

| DAC2CON1 | _      |       | _       | DAC2R<4:0> |              | 253   |       |         |                     |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

| Name    | Bit 7                         | Bit 6          | Bit 5                           | Bit 4      | Bit 3  | Bit 2  | Bit 1       | Bit 0  | Register<br>on Page |

|---------|-------------------------------|----------------|---------------------------------|------------|--------|--------|-------------|--------|---------------------|

|         |                               |                | DCOD                            | -1.0>      |        |        | 1 < 2 . 0 > |        | 0                   |

| CCP2CON | —                             |                | DC2B                            | <1:0>      |        | CCPZI  | √<3:0>      |        | 284                 |

| INTCON  | GIE                           | PEIE           | TMR0IE                          | INTE       | IOCIE  | TMR0IF | INTF        | IOCIF  | 83                  |

| PIE1    | TMR1GIE                       | ADIE           | RCIE                            | TXIE       | SSP1IE | CCP1IE | TMR2IE      | TMR1IE | 84                  |

| PIR1    | TMR1GIF                       | ADIF           | RCIF                            | TXIF       | SSP1IF | CCP1IF | TMR2IF      | TMR1IF | 87                  |

| PR2     | Timer2 Module Period Register |                |                                 |            |        |        | 268*        |        |                     |

| T2CON   | _                             |                | T2OUTPS<3:0> TMR2ON T2CKPS<1:0> |            |        |        | 270         |        |                     |

| TMR2    | Holding Re                    | gister for the | e 8-bit TMR2                    | 2 Register |        |        |             |        | 268*                |

TABLE 27-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 29-4).

#### 29.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 29-4.

#### EQUATION 29-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TABLE 29-1: | <b>EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (</b> | Fosc = 20 MHz) |

|-------------|--------------------------------------------------|----------------|

|             |                                                  | 1000 - 20 mmz  |

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 29-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 29.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 29.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 29.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

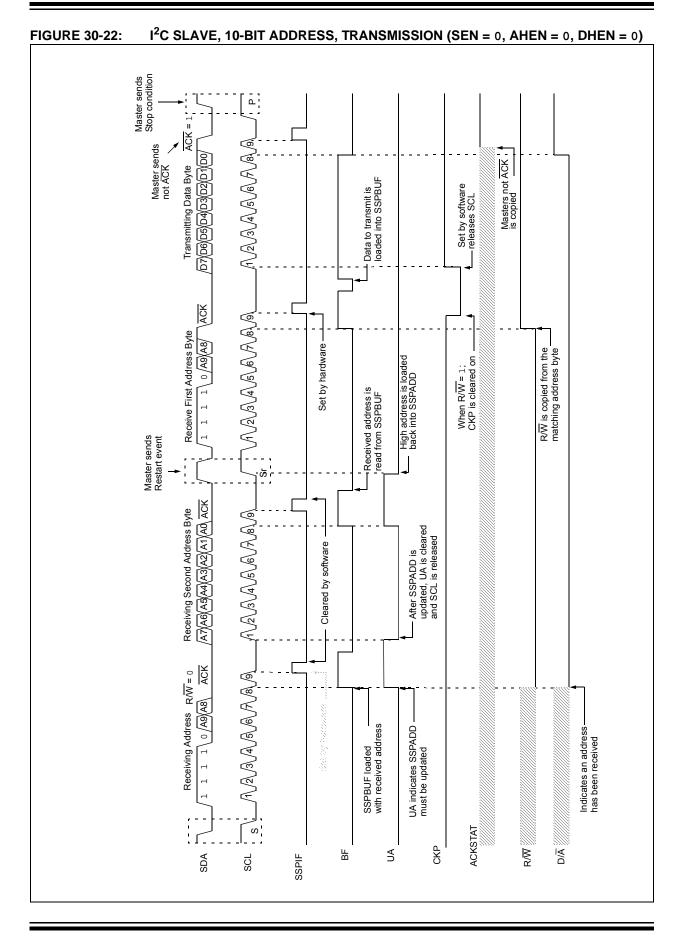

## 30.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception (Figure 30-29) is enabled by programming the Receive Enable bit, RCEN bit of the SSP1CON2 register.

| Note: | The MSSP module must be in an Idle      |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPCON2 register.

#### 30.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 30.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

## 30.6.7.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 30.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPCON2 register.

- 2. SSPIF is set by hardware on completion of the Start.

- 3. SSPIF is cleared by software.

- 4. User writes SSPBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all eight bits are transmitted. Transmission begins as soon as SSPBUF is written to.

- 6. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 7. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 8. User sets the RCEN bit of the SSPCON2 register and the master clocks in a byte from the slave.

- 9. After the eighth falling edge of SCL, SSPIF and BF are set.

- 10. Master clears SSPIF and reads the received byte from SSPUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Master's ACK is clocked out to the slave and SSPIF is set.

- 13. User clears SSPIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

## 31.5 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 31.5.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

## 31.5.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

## 31.5.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

### 31.5.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

## 31.5.1.4 Synchronous Master Transmission Setup:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 31.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1 µF, TA = 25°C.

FIGURE 35-43: IPD, Timer1 Oscillator, Fosc = 32 kHz, PIC16LF1713/6 Only.

FIGURE 35-44: IPD, Timer1 Oscillator, Fosc = 32 kHz, PIC16F1713/6 Only.

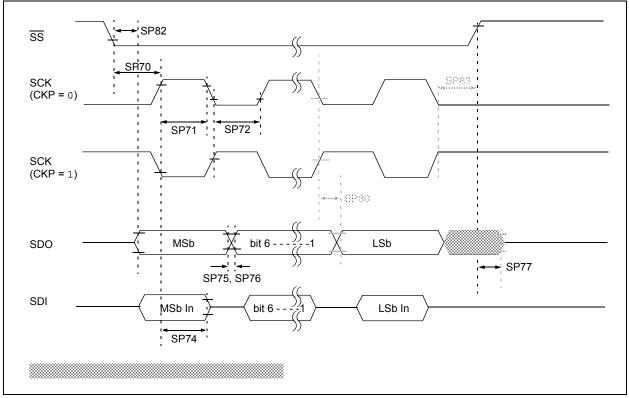

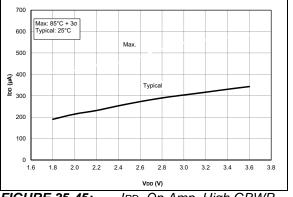

FIGURE 35-45: IPD, Op Amp, High GBWP Mode (OPAxSP = 1), PIC16LF1713/6 Only.

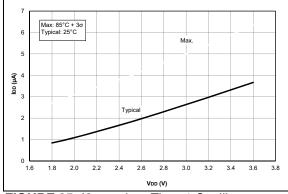

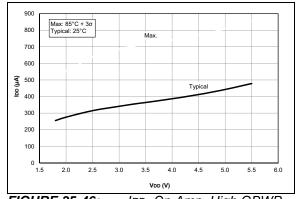

FIGURE 35-46: IPD, Op Amp, High GBWP *Mode* (*OPAxSP* = 1), *PIC16F1713/6 Only*.

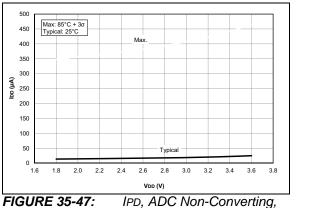

PIC16LF1713/6 Only.

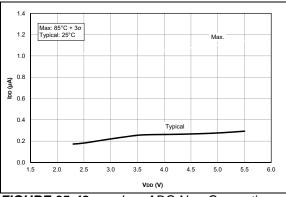

FIGURE 35-48: IPD, ADC Non-Converting, PIC16F1713/6 Only.

(Au) aal